# Modelling and Simulation Based Analysis of Random Dopant Fluctuation in DG JLFET under Quantum Confinement

Submitted in partial fulfilment of the requirements for the award of the Degree of

# MASTER OF ENGINEERING IN ELECTRONICS & TELE-COMMUNICATIONENGG.

By

#### **RAUNAK ROY**

Class Roll No: 002110702003

Exam Roll No: M4ETC23001

University Registration No.: 160203 of 2021-2022

Under the Guidance of

Prof. Chayanika Bose

Jadavpur University 2023

DECLARATION

I hereby declare that the thesis entitled "Modelling and Simulation Based

Analysis of Random Dopant Fluctuation in DG JLFET under Quantum

Confinement" submitted by me, for the award of the degree of Master of Engineering

in Electronics & Tele-Communication Enguneering of Jadavpur University is a

record of bonafide work carried out by me under the supervision of Prof. Chayanika

Bose.

I further declare that the work reported in this thesis has not been submitted and will

not be submitted, either in part or in full, for the award of any other degree or diploma

in this institute or any other institute or university.

Raunak Roy Signature of the Candidate

Place: Jadavpur

Date: 11/09/2023

2

#### CERTIFICATE

This is to certify that the thesis entitled "Modelling and Simulation Based Analysis of Random Dopant Fluctuation in DG JLFET under Quantum Confinement" submitted by Raunak Roy having Reg. No. 160203, Class Roll No. 002110702003 and Exam Roll No. M4ETC23001 of Jadavpur University for the award of the degree of MASTER OF ENGINEERING in ELECTRONICS & TELE-COMMUNICATION, is a record of bonafide work carried out by him under my supervision, as per the code of academic and research ethics.

The contents of this report have not been submitted and will not be submitted either in part or in full, for the award of any other degree or diploma in this institute or any other institute of university. The thesis fulfils the requirements and regulations of the University and in my opinion meets the necessary standards for submission.

CB850 11.09.23

Prof. Chayanika Bose

Professor (Retd.)

Electronics & Tele-communication Engineering Department Jadavpur University Kolkata-700 032

The thesis is satisfactory / unsatisfactory

**Internal Examiner**

**External Examiner**

Approved by

Manolosk Binuss HOD 12/09/23

Department of Electronics & Tele-Communication Engineering

MANOTOSH BISWAS Professor and Head Electronics and Telecommunication Engineering

Jadavpur University, Kolkata - 32

Jadavpur University, Faculty of Engineering & Technology

Faculty of Engineering & Technology JADAVPUR UNIVERSITY KOLKATA-700 032

#### **ABSTRACT**

Moore's Law has been observed in the Microelectronics and Semiconductor Industries since 1970. Trend of downscaling transistors smaller and smaller to make processors work faster than before with implementation of VLSI (Very Large Scale Integration), ULSI (Ultra Large Scale Integration), GLSI (Giga Large Scale Integration) techniques require fabrication of nano-scale transistors. This presents significant challenges in term of developing new device structures and manufacturing processes. Because of the laws of diffusion and the statistical nature of the distribution of the dopant atoms in the semiconductor and rise of other Short Channel Effects, formation of ultra shallow junctions with high doping concentration gradients in Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) has become an increasingly difficult challenge for the semiconductor industry.

J.P. Collinge proposed an idea of using Junctionless transistors (also called gated resistor) for fabrication of nanoscale transistors. Junctionless transistors commonly known as JLFET (Junctionless Field Effect Transistor) have no junctions since a homogeneous highly doped substrate is used with Gate Oxide deposition over JLFET to control the current flow. These devices have full CMOS functionality and are made using silicon nanowires.

Since inception of JLFET in Semiconductor Industries, numerous researches and simulations on its fabrication techniques, device characteristics, etc. have been performed by Researchers.. But analytical models of JLFET under various short channel effects like Quantum Confinement and Random Dopant Fluctuations (RDF) needs more emphasis.

In our project, we have proposed an analytical model regarding impact of Quantum Confinement and RDF in Threshold Voltage and other parameters of an ultra short channel DG (Dual Gate) SMG (Single Material Gate) JLFET. We have incorporated Quantum Confinement effects on 3D JLFET into our model and derived threshold voltage for short channel JLFET. In addition, we have introduced a new approach that would give insights regarding impact of dopant atoms on threshold voltage in terms of their lattice site occupancies, and thus, RDF has been included in our model. The dependence of threshold voltage on different physical parameters of JLFET has also been investigated.

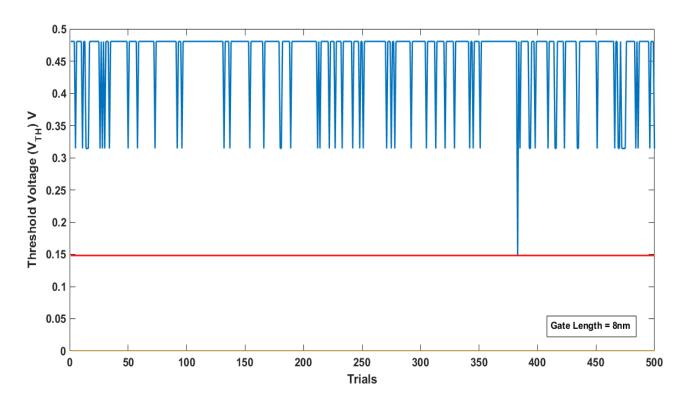

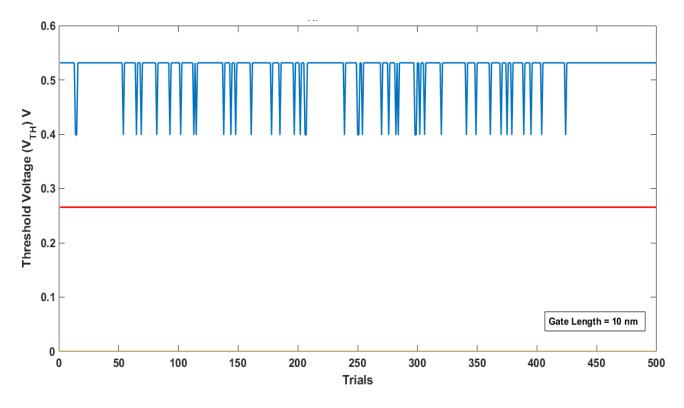

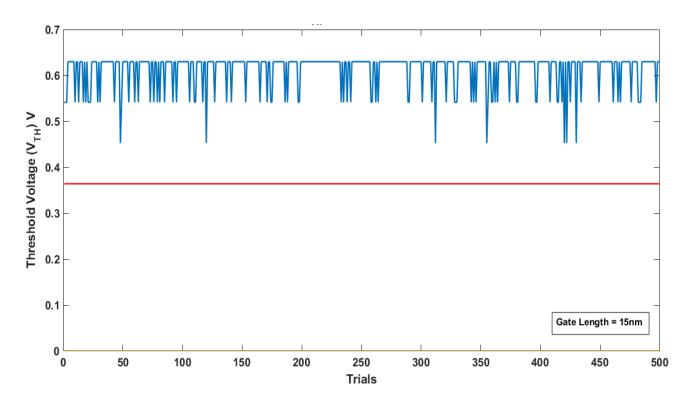

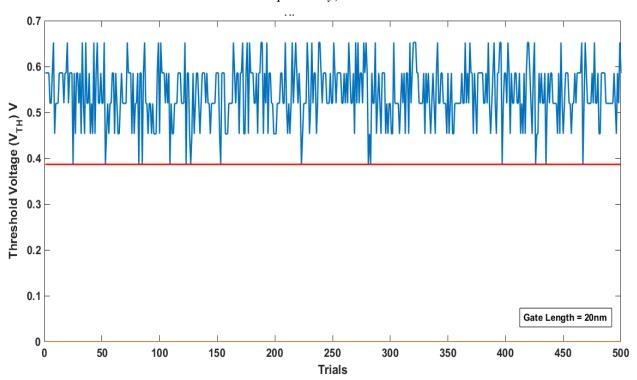

We have also simulated ultra short channel DG SMG JLFET using Silvaco TCAD Atlas with inclusion of Quantum Confinement Effects and compared simulation results obtained with the results predicted by our model, providing plausible explanations for any deviation from simulation results. The influence of RDF on the threshold voltage has been investigated through model simulation, where randomization of number has been included to account for the random factor regarding positional occupancy of dopant atoms.

Finally we incorporate both RDF and Quantum Confinement effects simultaneously in our model and observe fluctuations in threshold voltage for different channel lengths, and also provide statistical interpretation of its behavior.

#### **ACKNOWLEDGEMENTS**

This is a great opportunity to express my gratitude and respect to all the persons who have supported me in their own way, during my thesis work.

At the very outset, I want to thank and express my sincere gratitude to my guide **Dr. Chayanika Bose**, Professor of Department of Electronics & Tele-Communication Engineering , Jadavpur University , for guiding and motivating me throughout my thesis work. I am grateful for her constant support, perseverance and encouragement in fulfilment of this thesis.

I also extend my heartfelt gratitude to my friends and faculty members of Department of Electronics & Tele-Communication Engineering for their support.

Above all, I am grateful to my parents who have always been my guiding light.

Raunale Roy 11/09/2023

Raunak Roy

Class Roll: 002110702003

Exam roll: M4ETC23001

Electronics And Tele-Communication Engg. Dept.

Jadavpur University

Kolkata

# CONTENTS

| Declar  | ration |                                                              | 2        |

|---------|--------|--------------------------------------------------------------|----------|

| Certifi | icate  |                                                              | 3        |

| Abstra  | act    |                                                              | 4        |

| Ackno   | wledge | ement                                                        | 5        |

| 1.      | Intro  | duction                                                      | 12       |

|         | 1.1    | Thesis Objective                                             | 13       |

|         | 1.2    | Organization of the Thesis                                   | 13       |

| 2.      | Litera | ature Survey                                                 | 15       |

|         | 2.1    | Device Structure of JLFET                                    | 15       |

|         | 2.     | 1.1 Single Gate JLFET                                        | 15       |

|         | 2.     | 1.2 Double Gate JLFET                                        | 16       |

|         | 2.     | 1.3 Tri Gate JLFET                                           | 16       |

|         | 2.     | 1.4 Gate-All-Around JLT or GAAFET                            | 16       |

|         | 2.2    | Conduction Mechanism of JLFET                                | 17       |

|         | 2.     | 2.1 Physics of JLFET under different regions of operation    | 17       |

|         | 2.     | 2.2 Subthreshold Conduction Path of JLFET                    | 20       |

|         | 2.3    | Threshold Voltage of JLFET                                   | 21       |

|         | 2.     | 3.1 Variation of Threshold Voltage                           | 21       |

|         | 2.     | 3.2 Sensitivity of Threshold Voltage with fabrication parame | eters 22 |

|         | 2.4    | Fabrication of JLFET                                         | 23       |

|         | 2.5    | I-V Characteristic Curve of JLFET                            | 23       |

|         | 2.6    | Mobility of Charge Carriers in JLFET                         | 24       |

|         | 2.7    | Comparative Study between JLFETs and MOSFETs                 | 25       |

|         | 2.8    | Adverse effects of high level doping in JLFET                | 28       |

|         | 2.     | 8.1 Mobility Degradation                                     | 28       |

|         | 2.     | 8.2 Random Dopant Fluctuations (RDF)                         | 28       |

|         | 2.9    | Work Progress in JLFET                                       | 30       |

|         | 2.10   | Work Ahead                                                   | 35       |

| 3.      | Devic  | ce Simulation of JLFET                                       | 36       |

|         | 3.1    | Results and Discussion                                       | 37       |

|        | 3.2                                                                        | Conclusion                                                  | 57      |  |  |

|--------|----------------------------------------------------------------------------|-------------------------------------------------------------|---------|--|--|

| 4.     | Form                                                                       | ulation of Threshold Voltage in a JLFET                     | 58      |  |  |

|        | 4.1                                                                        | Derivation of Classical Threshold Voltage                   | 58      |  |  |

|        | 4.2                                                                        | Results and Discussion                                      | 64      |  |  |

|        | 4.3                                                                        | Conclusion                                                  | 67      |  |  |

| 5.     | Form                                                                       | ulation of Threshold Voltage for a Uniformly Doped short    | channel |  |  |

|        | JLFE'                                                                      | Т                                                           | 68      |  |  |

|        | 5.1                                                                        | Formulation of Threshold Voltage using a new model          | 68      |  |  |

|        | 5.2                                                                        | Results and Discussion                                      | 72      |  |  |

|        | 5.3                                                                        | Conclusion                                                  | 74      |  |  |

| 6.     | Form                                                                       | ulation of Threshold Voltage of JLFET under Quantum Confine | ment    |  |  |

|        |                                                                            | 75                                                          |         |  |  |

|        | 6.1                                                                        | Derivation of Threshold Voltage of Quantum Confined JLFET   | 75      |  |  |

|        | 6.2                                                                        | Results and Discussion                                      | 83      |  |  |

|        | 6.3                                                                        | Conclusion                                                  | 86      |  |  |

| 7.     | Analysis of Random Dopant Fluctuation and its impact on Threshold Voltage  |                                                             |         |  |  |

|        | of JLI                                                                     | FET                                                         | 87      |  |  |

|        | 7.1                                                                        | Derivation of Threshold Voltage under RDF using new Model   | 87      |  |  |

|        | 7.2                                                                        | Introducing Random Factor for Model Simulation under        | 89      |  |  |

|        |                                                                            | RDFeffects                                                  |         |  |  |

|        | 7.3                                                                        | Results and Discussion                                      | 91      |  |  |

|        | 7.4                                                                        | Conclusion                                                  | 95      |  |  |

| 8.     | Analysis of Random Dopant Fluctuations and its impact on Threshold Voltage |                                                             |         |  |  |

|        | of JLI                                                                     | FET under Quantum Confinement                               | 96      |  |  |

|        | 8.1                                                                        | Inclusion of RDF and QuantumConfinement Effect in new Model | 96      |  |  |

|        | 8.2                                                                        | Results and Discussion                                      | 97      |  |  |

|        | 8.3                                                                        | Conclusion                                                  | 101     |  |  |

| 9.     | Concl                                                                      | usion and Future Work                                       | 102     |  |  |

|        | 9.1                                                                        | Conclusion                                                  | 102     |  |  |

|        | 9.2                                                                        | Future Work                                                 | 103     |  |  |

| Refere | ence                                                                       |                                                             | 104     |  |  |

|        |                                                                            |                                                             |         |  |  |

## **List of Figures:**

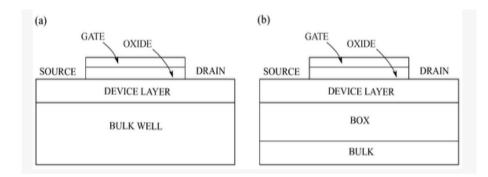

- 2.1 Cross-sectional view of: (a) Single Gate junctionless transistor (SGJLT) (b) SGJLT with SOI structure

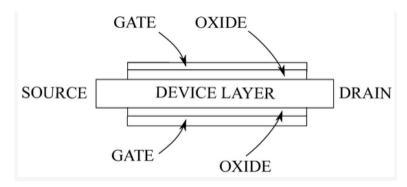

- 2.2 Cross-sectional view of a double gate junctionless transistor

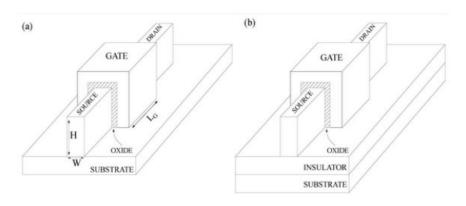

- 2.3 3D TG JLFET structure: (a) bulk (b) SOI

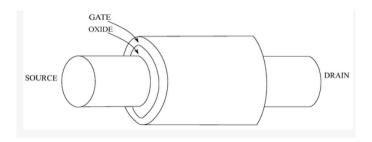

- 2.4 Three-dimensional (3D) structure of a cylindrical junctionless GAAFET

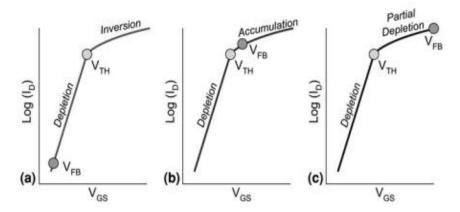

- 2.5 Drain current (log scale) as a function of gate voltage in (a) an inversion-mode MOSFET; (b) an accumulation-mode MOSFET and (c) a heavily-doped JLFET

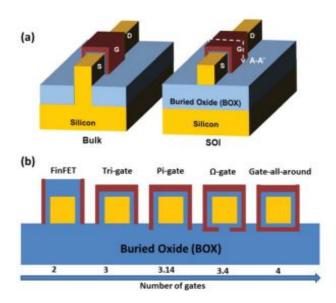

- 2.6 Schematic of (a) bulk and SOI multi-gate FETS, and (b) cross-section of different multi-gate FETS and their corresponding effective number of gates

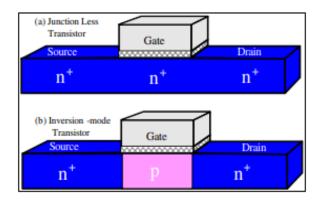

- 2.7 Longitudinal cross sections showing the doping profiles in: (a) a junctionless device, (b) an inversion-mode transistor.

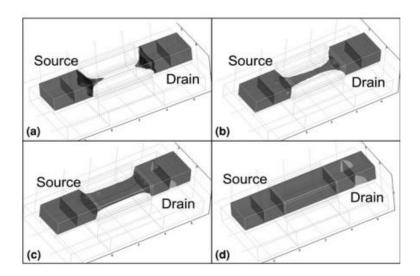

- 2.8 Electron concentration contour plots in an n-type junctionless transistor for  $V_{DS} = 50$  mV.  $a)V_G < V_{TH}$ ;  $b)V_G = V_{TH}$ ;  $c)V_G > V_{TH}$ ;  $d)V_G = V_{FB} >> V_{TH}$

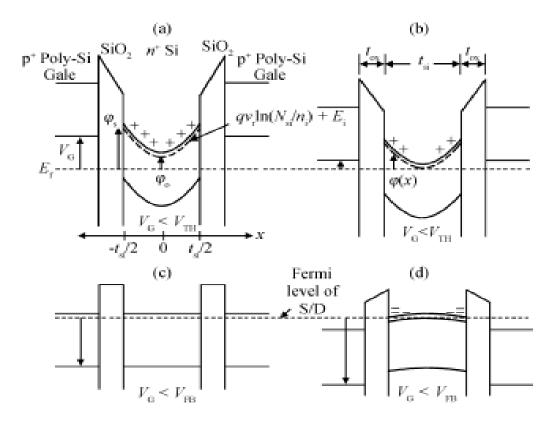

- 2.9 Schematic band diagrams for a symmetric DG-JLFET. (a) Fully depleted and downwardly bent channel in the sub threshold mode. Partially depleted and downwardly bent channel in the bulk current mode. (c) Flattened channel in the flat band mode. (d) Upwardly bent channel in the accumulation

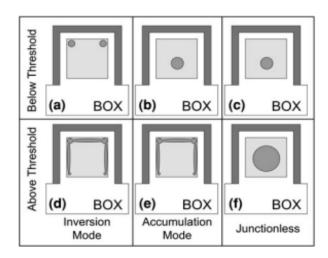

- 2.10 Location of conduction path in the different devices. Subthreshold conduction path in a) inversion-mode, b) accumulation-mode and c) junctionless devices. Conduction channels above threshold in d) inversion-mode, e) accumulation-mode and f) junctionless devices

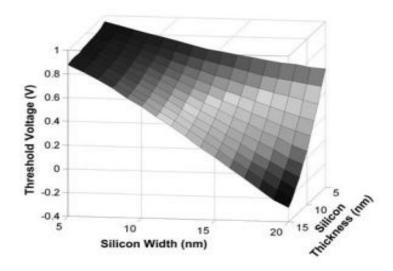

- 2.11 Long-channel  $V_{TH}$  defined as peak in  $dg_m/dV_G$  for  $T_{ox} = 0.5$  nm and  $N_D = 2 \times 10^{19}$  cm<sup>-3</sup>

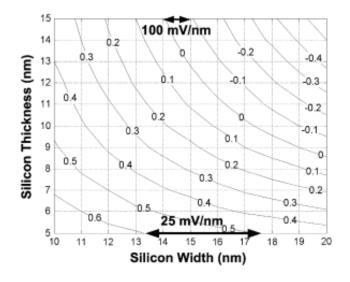

- 2.12 Contour plot of threshold voltage in an n-channel junctionless device with  $T_{ox} = 1$  nm and  $N_D = 2x \ 10^{19} \ cm^{-3}$ , as a function of nanowire thickness and width

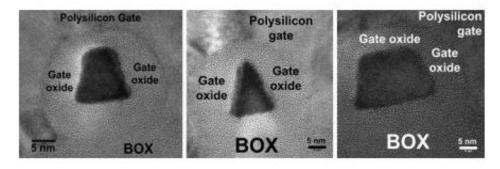

- 2.13 TEM cross section of a junctionless transistors with increasing width from left to right

- 2.14 Drain current versus gate voltage for N and P- type junctionless gated resistors and a trigate inversion-mode, N-channel MOSFET.  $N_D = 1 \times 10^{19} \text{ cm}^{-3}$  in the junctionless device.  $L = 1 \mu m$ .

- 2.15 Mobility in heavily doped junctionless transistors and in regular trigate MOSFETs with doped and undoped channels, as a function of temperature

- 2.16 Illustration of effective channel length in an inversion-mode device (a) and (b) a junctionless transistor.

- 2.17Scattering of source and drain doping impurities in the channel of (a) a long-channel and (b) a short-channel inversion-mode MOSFETs; (c) long-channel and (d) short-channel junctionless devices

- 2.18 Measured subthreshold slope versus temperature in a junctionless gated resistor and an inversion-mode trigate MOSFET

- 2.19 Electron mobility in silicon as a function of donor doping atom concentration and as a function of electric field in the channel. The latter curve shows the mobility/ field for several key technology nodes

- 2.20 Primary sources of variation in a nanoscale device

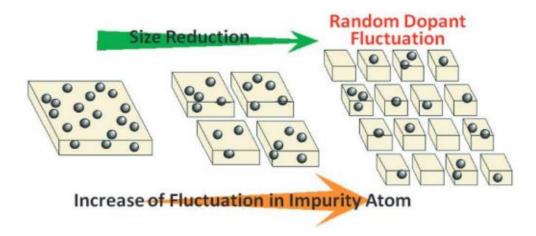

- 2.21 Appearance of RDF increases with reduction in size of semiconductor bulk

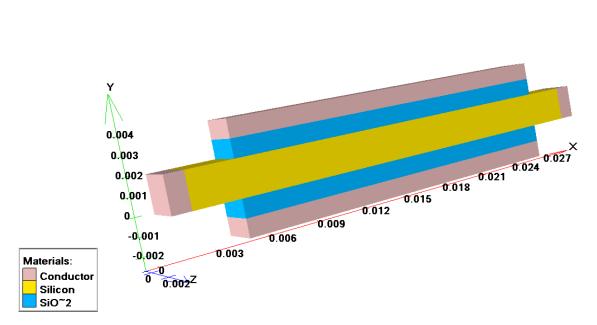

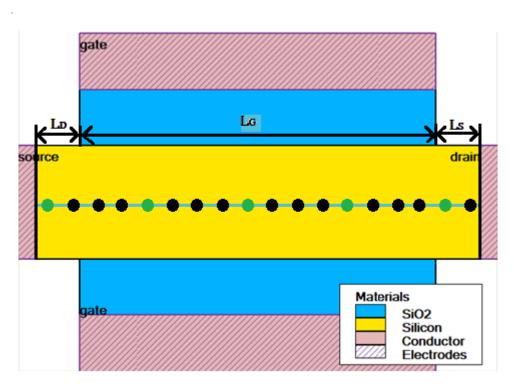

- 3.1 3D Device Structure of DG SMG JLFET

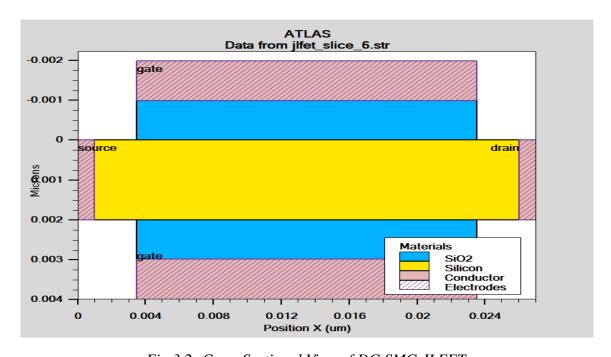

- 3.2 Cross Sectional View of DG SMG JLFET

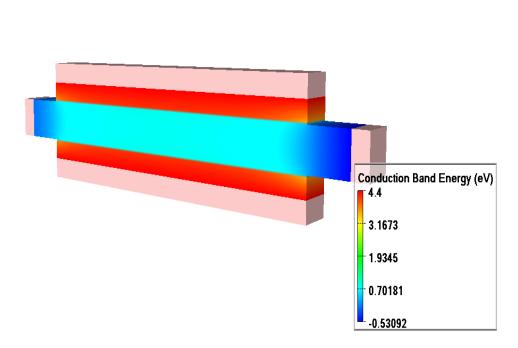

- 3.3 Conduction Band Energy in JLFET under Depletion Mode (3D View)

- 3.4Conduction Band Energy in JLFET (Cross Sectional view) under Depletion Mode

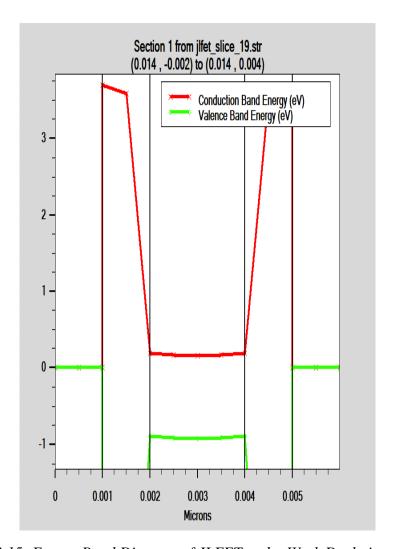

- 3.5 Energy Band Diagram of JLFET under Depletion Mode

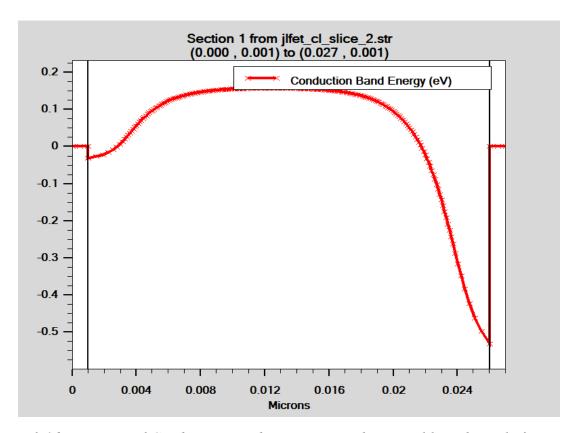

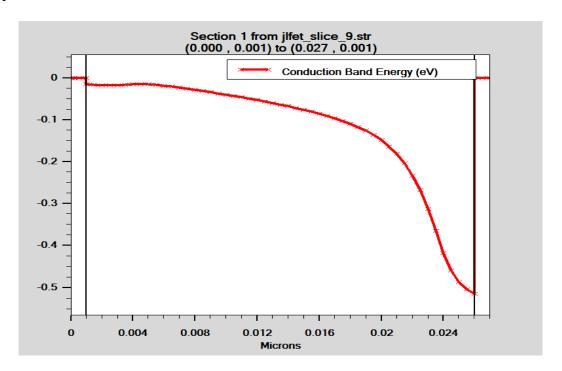

- 3.6 Variation of Conduction Band Energy across the central line channel of JLFET under Depletion Mode

- 3.7 Charge Concentration in JLFET under Depletion Mode

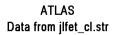

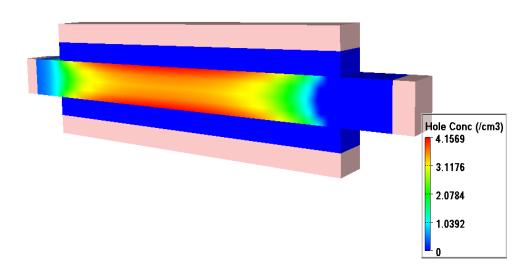

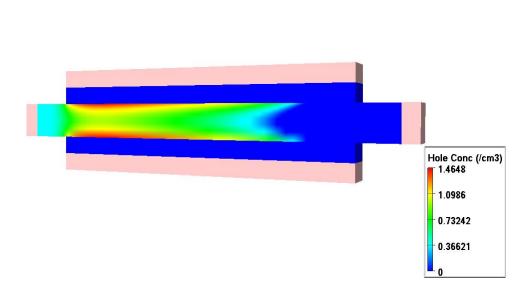

- 3.8 Hole Concentration in JLFET under Depletion Mode

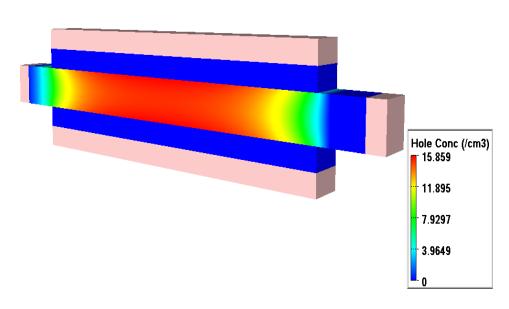

- 3.9 Hole Concentration in JLFET across the central line channel region of JLFET under Depletion Mode

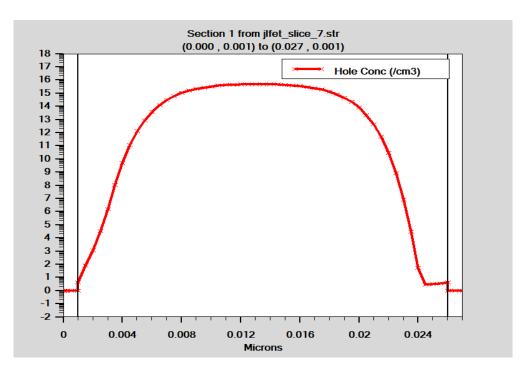

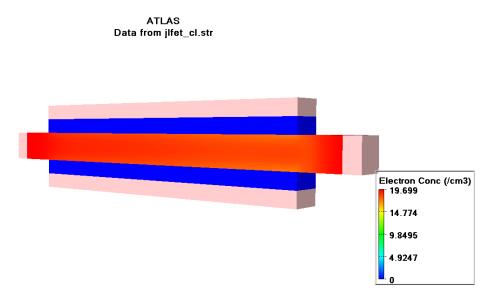

- 3.10 Electron Concentration in JLFET under Depletion Mode

- 3.11 Electron Concentration across central line channel region of JLFET under Depletion Mode

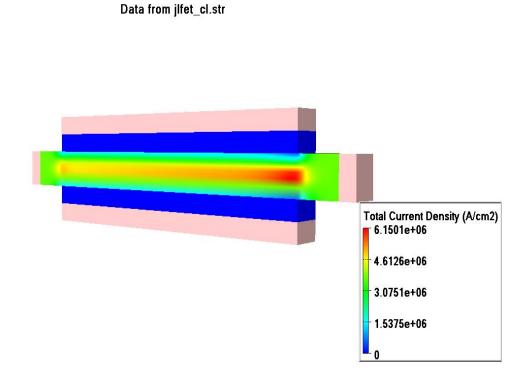

- 3.12 Current Density in JLFET under depletion mode

- 3.13 Conduction Band Energy in JLFET under Weak Depletion Mode (3D View)

- 3.14 Conduction Band Energy in JLFET under Weak Depletion Mode. (Cross Sectional view)

- 3.15Energy Band Diagram of JLFETunder Weak Depletion Mode

- 3.16 Variation of Conduction Band Energy across the central line channel of JLFET under Weak Depletion Mode

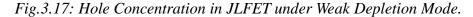

- 3.17 Hole Concentration in JLFET under Weak Depletion Mode

- 3.18 Hole Concentration across the central line channel region of JLFET under Weak Depletion Mode (Horizontal Section)

- 3.19 Hole Concentration across the central line channel region of JLFET under Weak Depletion Mode (Vertical Section)

- 3.20 Electron Concentration in JLFET under Weak Depletion Mode

- 3.21 Electron Concentration across central line channel region of JLFET under Weak Depletion Mode

- 3.22 Current Density in JLFET under Weak Depletion Mode

- 3.23 Conduction Band Energy in JLFET under Weak Accumulation Mode (Cross Sectional view)

- 3.24 Energy Band Diagram of JLFET under Weak Accumulation Mode

- 3.25 Variation of Conduction Band Energy across the central line channel of JLFET under Weak Accumulation Mode

- 3.26 Hole Concentration in JLFET under Weak Accumulation Mode

- 3.27 Electron Concentration in JLFET under Weak Accumulation Mode

- 3.28 Current Density in JLFET under weak accumulation mode (3D View)

- 3.29 Current Density in JLFET under Weak Accumulation Mode (Cross Sectional View)

- 3.30 Conduction Band Energy in JLFET (Cross Sectional view) under Accumulation Mode

- 3.31 Conduction Band Energy of JLFET under Accumulation Mode

- 3.32 Charge Concentration in JLFET under Accumulation Mode

- 3.33 Current Density in JLFET under Accumulation Mode

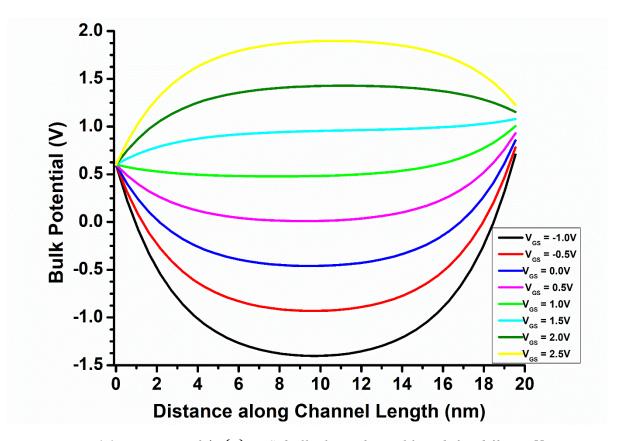

- 4.1 Variation of  $\psi_B(y)$  in Si bulk along channel length for different  $V_G$

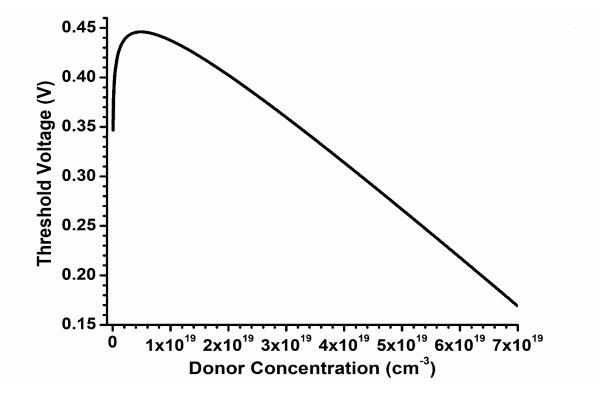

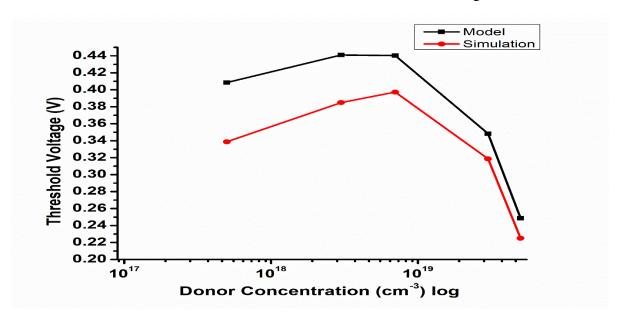

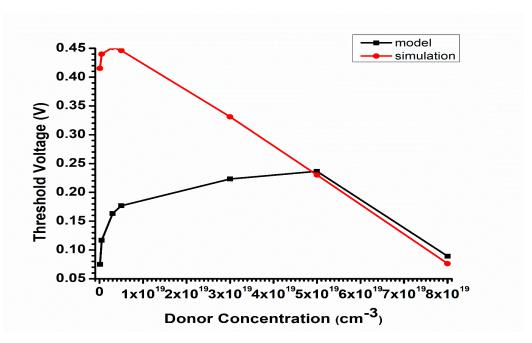

- 4.2  $V_{TH}$  variation with  $N_D$  for  $t_{ox} = 1$ nm,  $L_G = 20$ nm,  $t_{Si} = 2$ nm

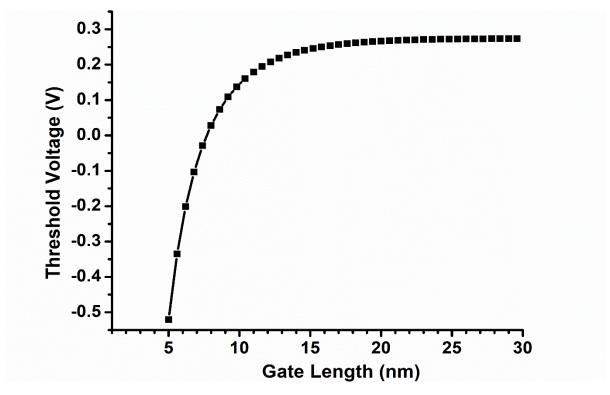

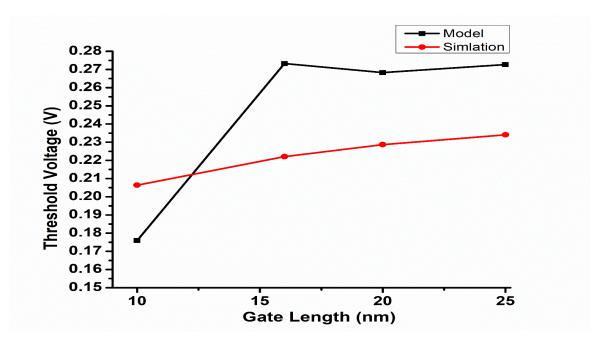

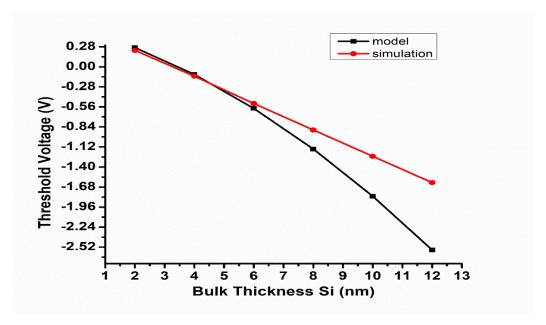

- 4.3 Variation of  $V_{TH}$  with  $L_G$  for  $t_{ox} = 1$ nm,  $N_D = 5x10^{19}$  cm<sup>-3</sup>,  $t_{Si} = 2$ nm

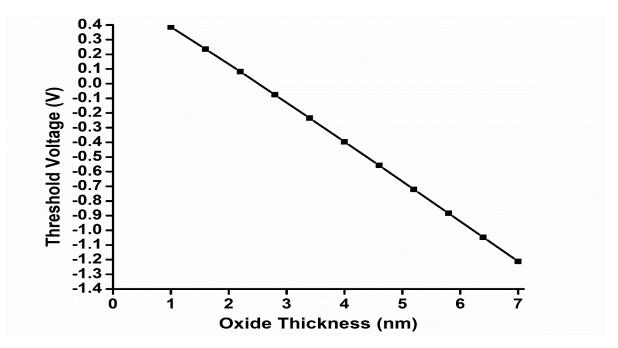

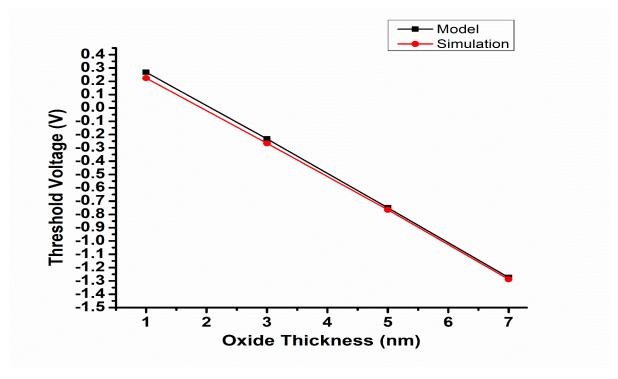

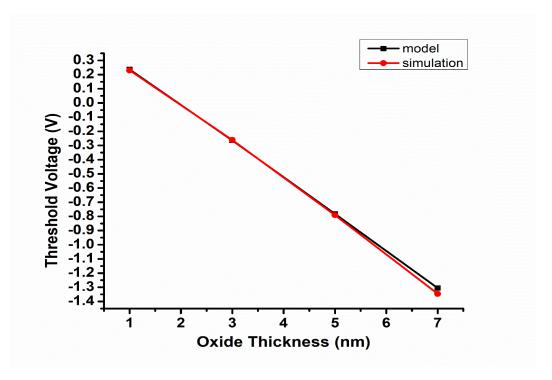

- 4.4  $V_{TH}$  variation with  $t_{ox}$  for  $N_D = 5x10^{19}$  cm<sup>-3</sup>,  $L_G = 20$ nm,  $t_{Si} = 2$ nm

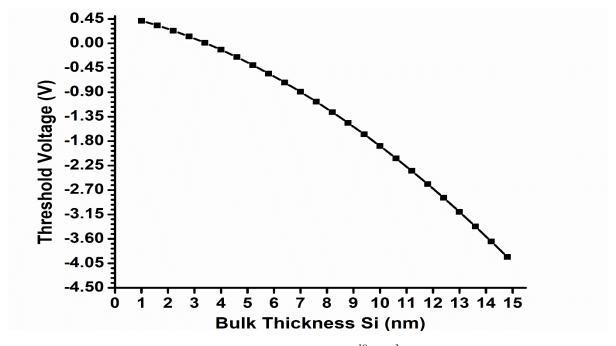

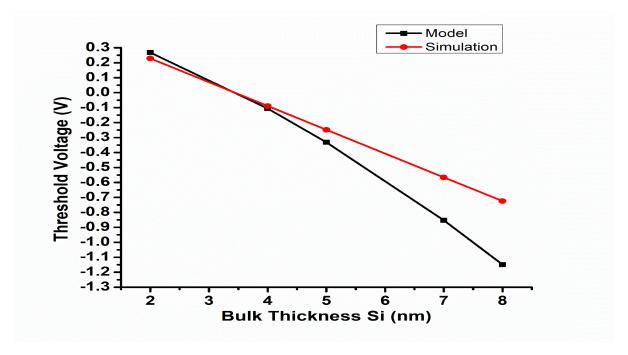

- 4.5  $V_{TH}$  variation with  $t_{Si}$  for  $N_D=5x10^{19}~cm^{-3}$  ,  $L_G=20nm$  ,  $t_{ox}=1nm$

- 5.1 Model showing dopant atoms (green ) spaced uniformly and occupying the lattice sites (black) along the central line of Si bulk in DG JLFET.

- 5.2  $V_{TH}$  variation with  $N_D$  for  $t_{ox} = 1$ nm,  $L_G = 20$ nm,  $t_{Si} = 2$ nm

- 5.3  $V_{TH}$  variation with  $L_G$  for  $t_{ox} = 1$ nm,  $N_D = 5x10^{19}$  cm<sup>-3</sup>,  $t_{Si} = 2$ nm

- 5.4  $V_{TH}$  variation with  $t_{ox}$  for  $L_G = 20$ nm,  $N_D = 5x10^{19}$  cm<sup>-3</sup>,  $t_{Si} = 2$ nm

- 5.5  $V_{TH}$  variation with  $t_{Si}$  for  $t_{ox} = 1$ nm,  $N_D = 5x10^{19}$  cm<sup>-3</sup>,  $L_G = 20$ nm.

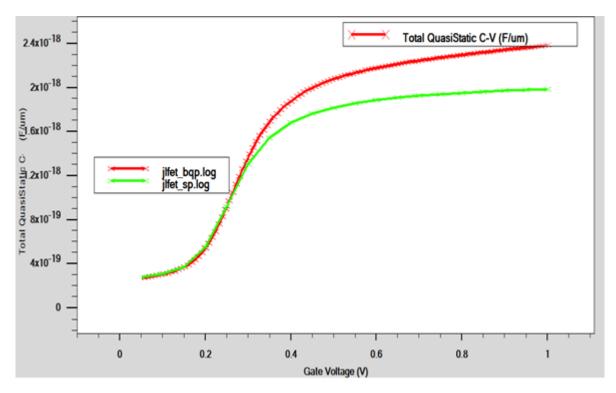

- 6.1 Total quasi-static CV showing the closest match between BQP and SP for BQP parameters , $\gamma = 0.36$  ,  $\alpha = 0.16$ .

- 6.2  $V_{TH}$  variation with  $N_D$  under Quantum Confinement for  $t_{ox}=1$ nm,  $L_G=20$ n,  $t_{Si}=2$ nm.

- 6.3  $V_{TH}$  variation with  $t_{Si}$  under Quantum Confinement for  $t_{ox} = 1$ nm,  $N_D = 5x10^{19}$  cm<sup>-3</sup> and  $L_G = 20$ nm.

- 6.4  $V_{TH}$  variation with  $t_{ox}$  under Quantum Confinement for  $L_G = 20$ nm,  $N_D = 5x10^{19}$  cm<sup>-3</sup>,  $t_{Si} = 2$ nm

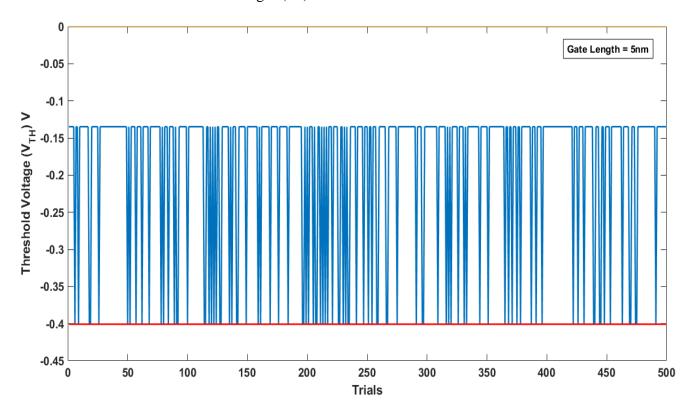

- 7.1 500 trials of measurement of Threshold Voltage and its fluctuations due to RDF in 5nm Channel Length JLFET (blue and red line represent  $V_{TH}$  with and without RDF respectively)

- 7.2 500 trials of measurement of Threshold Voltage and its fluctuations due to RDF in 8nm Channel Length JLFET (blue and red line represent  $V_{TH}$  with and without RDF respectively)

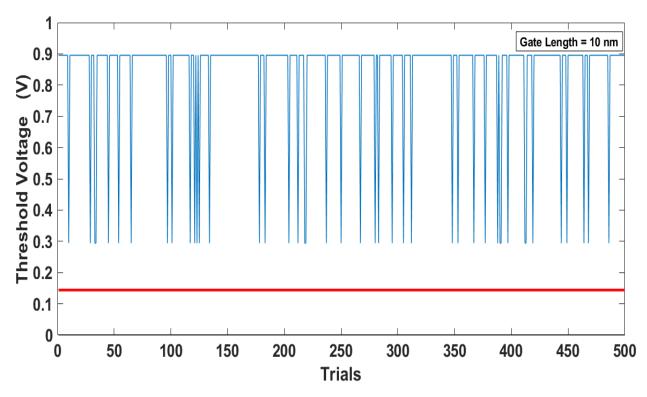

- 7.3 500 trials of measurement of Threshold Voltage and its fluctuations due to RDF in 10nm Channel Length JLFET (blue and red line represent  $V_{TH}$  with and without RDF respectively)

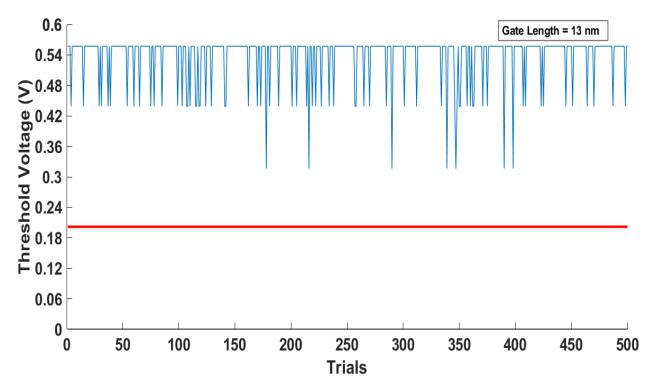

- 7.4 500 trials of measurement of Threshold Voltage and its fluctuations due to RDF in 15nm Channel Length JLFET (blue and red line represent  $V_{TH}$  with and without RDF respectively)

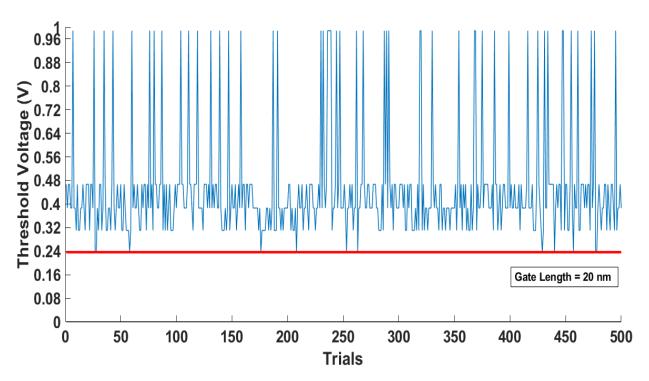

- 7.5 500 trials of measurement of Threshold Voltage and its fluctuations due to RDF in 20nm Channel Length JLFET (blue and red line represent  $V_{TH}$  with and without RDF respectively)

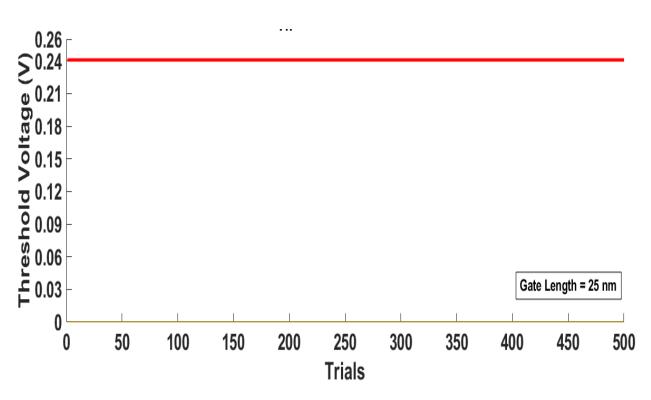

- 7.6 500 trials of measurement of Threshold Voltage and its fluctuations due to RDF in 25nm Channel Length JLFET (blue and red line represent  $V_{TH}$  with and without RDF respectively)

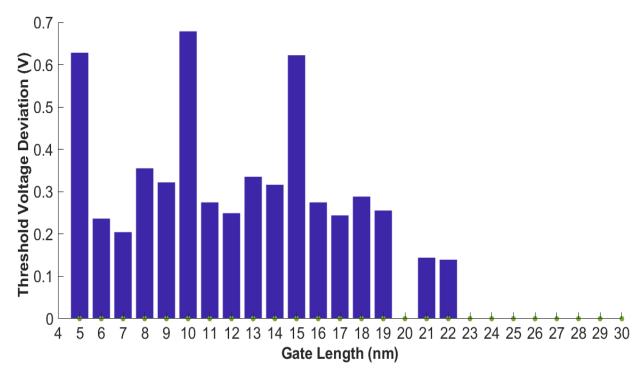

- 7.7 Deviation of  $V_{TH}$  under RDF for different  $L_G$  in JLFET

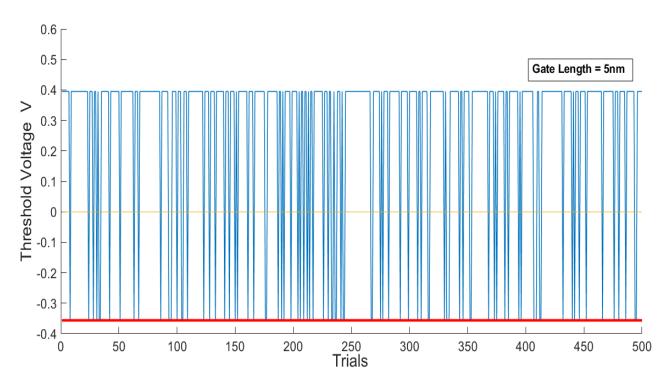

- 8.1 500 trials of measurement of Threshold Voltage under Quantum Confinement and its fluctuations due to RDF in JLFET of 5nm Channel Length (blue and red line represent  $V_{TH}$  with and without RDF respectively)

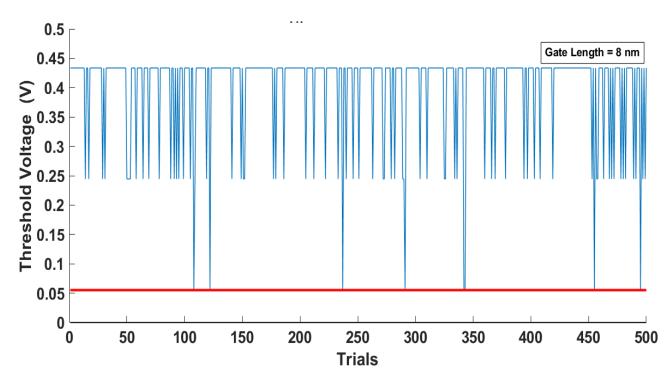

- 8.2 500 trials of measurement of Threshold Voltage under Quantum Confinement and its fluctuations due to RDF in JLFET of 8nm Channel Length (blue and red line represent  $V_{TH}$  with and without RDF respectively)

- 8.3 500 trials of measurement of Threshold Voltage under Quantum Confinement and its fluctuations due to RDF in JLFET of 10nm Channel Length (blue and red line represent  $V_{TH}$  with and without RDF respectively)

- 8.4 500 trials of measurement of Threshold Voltage under Quantum Confinement and its fluctuations due to RDF in JLFET of 13nm Channel Length JLFET (blue and red line represent  $V_{TH}$  with and without RDF respectively)

- 8.5 500 trials of measurement of Threshold Voltage under Quantum Confinement and its fluctuations due to RDF in JLFET of 20nm Channel Length JLFET (blue and red line represent  $V_{TH}$  with and without RDF respectively)

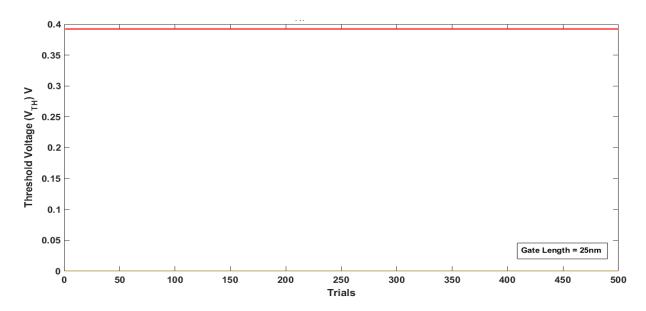

- 8.6 500 trials of measurement of Threshold Voltage under Quantum Confinement and its fluctuations due to RDF in JLFET of 25nm Channel Length (blue and red line represent  $V_{TH}$  with and without RDF respectively)

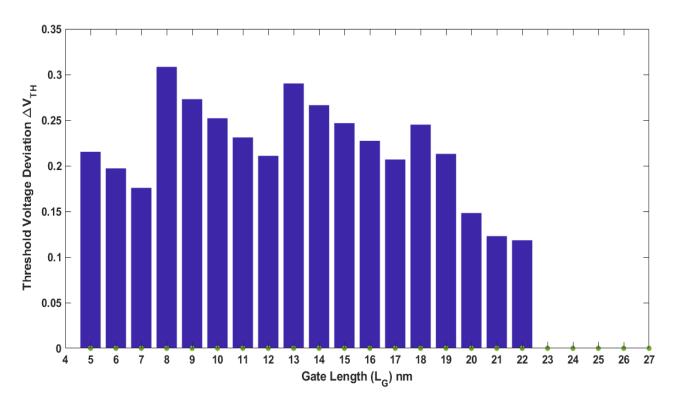

- 8.7 Deviation of  $V_{TH}$  under Quantum Confinement and RDF for different  $L_G$  in JLFET

# Chapter 1

## Introduction

Trends in the microelectronics industry require the fabrication of smaller and smaller components, resulting in transistor sizes down to the nano-scale. This presents significant challenges in term of developing new device architectures and manufacturing processes. Over the past decades, the size of MOSFETs has continually been scaled down leading to MOSFET with effective channel length less than ten nanometers. A classical MOS transistor comprises two PN junctions called the source junction and the drain junction. The effective channel length is the distance that separates these two junctions, and the source and drain junctions are separated by a region with opposite doping type. The formation of such junctions involves extremely high doping concentration gradients, and very low thermal budget processing must be used. Flash annealing techniques are currently used to heat silicon for a very short time period in order to minimize diffusion; but even in total absence of diffusion, ion implantation and other doping techniques do not achieve perfectly abrupt junctions with infinite concentration gradients. Therefore it would be suitable to use a transistor device structure that overcomes the above-mentioned problems .

Because of the laws of diffusion and the statistical nature of the distribution of the doping atoms in the semiconductor, the formation of ultra shallow junctions with high doping concentration gradients has become an increasingly difficult challenge for the semiconductor industry. Junctionless transistors (also called gated resistor) have no junctions and no doping concentration gradients. These devices have full CMOS functionality and are made using silicon nanowires. The key to fabricating a Junctionless gated resistor is the formation of a semiconductor layer that is thin and narrow enough to allow for full depletion of carriers when the device is turned OFF. The semiconductor alsoneeds to be heavily doped to allow for a decent amount of current flow when the device is turned ON.Incorporating these two together imposes the use of nanoscale dimensions and high doping concentration.

JLFETs contain the same doping concentration of a single doping species across the semiconductor region, and thus have been proposed as one of the promising alternatives over

conventional fin field-effect transistors (FinFET), which are more complicated to process and costlier to manufacture. Moreover, it is expected that the JLFETs can maintain scaling down of complementary metal-oxide-semiconductor (CMOS) technology owing to restrained short channel effects (SCEs) by increased effective channel length. In addition, to improve device characteristics like ON-state current, adopting new channel materials is a favorable technique.

#### 1.1 Thesis Objective

In this thesis, we study device physics of DG JLFET and impact of Random Dopant Fluctuations in its Threshold Voltage. Our main objective is to model threshold voltage of a short channel DG JLFET with inclusion of RDF and Quantum Confinement Effects. Using this model, we would observe behavior of threshold voltage with change in different physical parameters of DG JLFET and we could also make a comparison with Simulation results for verification and validation of our model. Observing fluctuations in Threshold Voltage due to RDF and understanding RDF in terms of lattice occupancy of dopant atoms is also a priority in this thesis.

#### 1.2. Organization of the Thesis

The present thesis has been organized as follows:

- Chapter 2 gives a vividexplanation of device physics of JLFET. Device fabrication and different types of JLFET have also been explained. Concept of RDF along with recent findings and work progress of JLFET have been described in this chapter.

- Chapter 3 includes simulation of DG JLFET and analysis of JLFET under different modes of operation based on the simulation results.

- Chapter 4 focuses on classical approach for the derivation of threshold voltage of DG

JLFET and influence of various physical parameters on it.

- Chapter 5 gives a section for current derivation in JLFET and also exhibits family of I-V curves for different physical parameters of JLFET and also gives explanation for their characteristic behavior.

- Chapter 6 proposes a new model for threshold voltage formulation based on the positional occupancy of dopant atoms and also makes a comparison with the simulation results.

- Chapter 7 incorporates Quantum Confinement effects in the proposed model and compares analytical results with respective simulation results.

- Chapter 8 includes the phenomenon of RDF in the proposed model to show the resulting fluctuations in threshold voltage under consideration.

- Chapter 9 finally fulfills our thesis objective by incorporating RDF and Quantum Confinement Effects in our proposed model and observing fluctuations of threshold voltage.

- Chapter 10 provides Conclusions and future scopes for the present work.

# Chapter 2

# **Literature Survey**

#### 2.1.Device Structure of JLFET

The Lilienfield transistor, like modern metal oxide semiconductor (MOS) devices, is a field-effect device. A thin semiconductor film is put on top of a narrow insulator layer, which is deposited on top of a metal electrode. The device's gate is made up of the latter metal electrode. Through operation, current can flow in the resistor between two contact electrodes, similar to how drain current flows in a conventional MOSFET between the source and drain. The Lilienfield device is a simple resistor in which the introduction of a gate voltage causes the carriers in the semiconductor layer to be depleted, changing its conductivity. In an ideal scenario, it should be feasible to deplete the semiconductor layer of carriers completely, resulting in a quasi-infinite resistance to the device. Unlike all other types of transistors, the Lilienfield transistor does not have a junction.

The Lilienfield transistor is a gated transistor with a gate that regulates carrier density and therefore current flow.

#### 2.1.1.SINGLE GATE JLFET

the single gate JLT has two types of structures: bulk and SOI (Fig.2.1). Because the bulk structure can be doped and biased, it gives more control over the device's characteristics.

When compared to SOI, bulk junctionless transistors have a lower effective thickness and the bulk SGJLT has better analog performance than the SOI structure, with better output transconductance, output resistance, early voltage, and inherent gain.

Fig2.1: Cross-sectional view of: (a) Single Gate junctionless transistor (SGJLT) (b) SGJLT with SOI structure.

#### 2.1.2.DOUBLE GATE JLFET

The structure of a double gate junctionless transistor is shown in fig 2.2

Fig2.2: Cross-sectional view of a double gate junctionless transistor.

Double Gate JLFET provides more control than SG-JLLFET on the mobility and conduction of electrons in N+ doped channel of JLFET under different modes of operation.

#### 2.1.3.TRI-GATE JLFET

Bulk and SOI structures of Tri-gated JLFET is shown in fig 2.3.

Fig. 2.3: 3D TG JLFET structure: (a) bulk (b) SOI.

#### 2.1.4.GATE-ALL-AROUND JLT or GAAFET

A model of a cylindrical junctionless Gate -All-Around transistor is shown in Fig 2.4.

Fig. 2.4: Three-dimensional (3D) structure of a cylindrical junctionless GAAFET.

#### 2.2. Conduction Mechanism in JLFET

#### 2.2.1. Physics of JLFET under different regions of operation

MOSFETs (including accumulation-mode FETs) are normally off devices, as the drain junction is reverse biased and blocks any current flow if no channel is created between source and drain. To turn the device on, the gate voltage is increased in order to create an inversion channel.

The junctionless transistor, on the other hand, is basically a normally on device where the work function difference between the gate electrode and the silicon nanowire shifts the flatband voltage and the threshold voltage to positive values. When the device is turned on and in flatband conditions, it basically behaves as a resistor and the electric field perpendicular to current flow is basically equal to zero in the "bulk" channel.

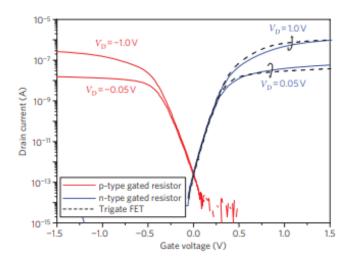

Figure 2.5 shows the drain current as a function of gate voltage in pi-gated SOI MOSFETs (Fig.2.6) in inversion-mode "N+PN+" (fig 2.7.a), accumulation-mode "N+NN+" and heavily doped junctionless "N+N+N+" transistor(fig 2.7.b).

- Below threshold the inversion-mode device is depleted (either fully or partially) and the flatband voltage is situated below the threshold voltage, at a gate voltage at which the device is off (Fig.2.5a). Below flatband, the body is p-type neutral. Above threshold, the body of the channel is depleted and a surface inversion layer is formed.

- Below threshold accumulation-mode devices are fully depleted. Threshold is reached when the gate voltage is increased in such a way that a portion of the channel region is no longer depleted. At that point, the channel region is technically partially depleted. As gate voltage is further increased, flat-band is reached: the channel region is now neutral (i.e. no longer depleted, even partially). Further increasing the gate voltage creates a surface accumulation channel (Fig.2.5b).

- The heavily doped junctionless transistor is fully depleted below threshold. As gate voltage is increased, the electron concentration in the channel increases, and threshold is reached when the peak electron concentration in the channel reaches the doping concentration  $N_D$ . Further increasing the gate voltage increases the "diameter" of the region where  $n=N_D$ , until the entire cross section of the device becomes neutral (i.e. no longer depleted, even partially), at which point flatband is reached (Fig.2.5c). It is possible to further increase the gate voltage

to create accumulation channels, but this is probably not desirable, as the high doping concentration in the channel already insures a large current drive.

Fig.2.5: Drain current (log scale) as a function of gate voltage in (a) an inversion-mode MOSFET; (b) an accumulation-mode MOSFET and (c) a heavily-doped JLFET

Fig.2.6: Schematic of (a) bulk and SOI multi-gate FETS, and (b) cross-section of different multi-gate FETS and their corresponding effective number of gates.

Fig.2.7: Longitudinal cross sections showing the doping profiles in: (a) a junctionless device, (b) an inversion-mode transistor.

Below threshold, the junctionless channel is depleted of electrons, and the current varies exponentially with gate voltage (Fig.2.8a). At threshold, a neutral silicon filament forms between source and drain (Fig.2.8b). The cross-section of filament increases when gate voltage is increased (Fig.2.8c) until depletion disappears and the device is in flatband condition (Fig.2.8d). Fig 2.9 shows band diagram of DG JLFET for different regions of operation.

Fig.2.8: Electron concentration contour plots in an n-type junctionless transistor for  $V_{DS} = 50 \text{ mV. } a)V_G < V_{TH}$ ;  $b)V_G = V_{TH} c)V_G > V_{TH}$ ;  $d)V_G = V_{FB} >> V_{TH}$ .

Fig. 2.9: Schematic band diagrams for a symmetric DG-JLFET. (a) Fully depleted and downwardly bent channel in the sub threshold mode. Partially depleted and downwardly bent channel in the bulk current mode. (c) Flattened channel in the flat band mode. (d) Upwardly bent channel in the accumulation.

#### 2.2.2.Subthreshold Conduction Path of JLFET

Unlike accumulation-mode and inversion-mode devices the channel of junctionless transistors is in the bulk of the nanowire (i.e. it is not a surface channel). As a result, carriers in the channel are exposed to a low electric field in the directions to current flow. This strongly reduces the degradation of mobility when gate voltage is increased in the on state [5]. Figure 2.10 shows the position of the channel in both subthreshold operation and above threshold. In an inversion-mode device, subthreshold conduction mainly takes place in the top corners of the device (Fig.2.10a). Above threshold, surface channels are formed on three sides of the nanowire, with carrier concentration peaks in the corners Fig. 10d). In an accumulation-mode transistor, the subthreshold current flows through the bulk of the device, near the center or the back of the nanowire (Fig.2.10b). When the device is turned on, a small current flows through the body of the nanowire, but this current typically amounts for less than ten percents of the overall current drive. Most of the current flows in surface and corner

accumulation channels, like in an inversionmode device (Fig.2.10e). In the junctionless device the subthreshold current flows in the center of the nanowire, as in the accumulation-mode device (Fig.2.10c). When threshold is reached, the channel leaves full depletion and a neutral ("undepleted") channel forms between source and drain, in the center of the device (Fig.2.10f). Thus, the junctionless transistor is partially depleted when it is turned on.

Fig.2.10: Location of conduction path in the different devices. Subthreshold conduction path in a) inversion-mode, b) accumulation-mode and c) junctionless devices. Conduction channels above threshold in d) inversion-mode, e) accumulation-mode and f) junctionless devices.

## 2.3. Threshold Voltage of JLFET

#### 2.3.1. Variation of Threshold Voltage

The threshold voltage of junctionless devices depends on silicon film thickness, width of the nanowire, doping concentration and gate oxide thickness (Fig.2.11). One can easily obtain different threshold voltages by varying the width of the nanowires, if doping concentration is kept constant, which may be useful for producing devices with multiple values of  $V_{TH}$  on a chip. Figure 2.11 shows the variation of threshold voltage in a long-channel junctionless device as a function of silicon width ( $W_{si}$ ) and thickness ( $T_{si}$ ). The EOT is 0.5 nm and the doping concentration is 2 x  $10^{19}$  cm<sup>-3</sup>. Threshold voltage can be varied from 1 to -0.2 V by varying  $W_{si}$  from 5 to 20 nm and  $T_{si}$  from 5 to 15 nm.

Fig. 2.11: Long-channel  $V_{TH}$  defined as peak in  $\frac{dg_m}{dV_G}$  for  $T_{ox} = 0.5$  nm and  $N_D = 2 \times 10^{19}$  cm<sup>-3</sup>

#### 2.3.2. Sensitivity of Threshold Voltage with fabrication parameters

It is important to evaluate the sensitivity of  $V_{TH}$  variations with fabrication parameters. Figure 2.12 shows the results of such an analysis. If one of the dimensions ( $T_{si}$  or  $W_{si}$ ) is small enough, the variations of the other dimension do not impact too much the threshold voltage. For example, if the silicon thickness is 5 nm, the variation  $\Delta V_{TH}/\Delta W_{si}$  is equal to 25 mV/nm. At the same time, the variation of threshold voltage  $\Delta V_{TH}/\Delta T_{si}$  is equal to 100 mV/nm. Since thin-film SOI wafers with a  $\sigma T_{Si}$ <0.2 nm can nowadays be produced , threshold voltage variations on the order of  $\sigma V_{TH}$ <35 mV can be expected at wafer level, provided a lithography width control of 0.5 nm. The use of a thinner EOT decreases the sensitivity of  $V_{TH}$  on dimensions.

Fig.2.12: Contour plot of threshold voltage in an n-channel junctionless device with  $T_{ox} = 1$  nm and  $N_D = 2x \ 10^{19} \ cm^{-3}$ , as a function of nanowire thickness and width.

# 2.4. Fabrication of JLFET

Junctionless gated resistor devices were made using standard SOI wafers. The SOI layer was thinned down to 15 nm and patterned into nanoribbons using e-beam lithography. Using a combination of plasma lateral overetch and gate oxidation, the thickness of the nanowires was reduced to nm, and their width was reduced to dimensions as small as 5 nm. Ion implantation was used to dope the devices uniformly  $N^+$  or  $P^+$  with a concentration of 1 x  $10^{19} - 5 \times 10^{19}$  cm<sup>-3</sup>, which is a typical LDD doping concentration, to realize N-channel and P-channel devices, respectively.

Figure 2.13 shows the TEM cross-section of a several devices with different widths. Due to processing parameters the cross-section of the devices is not a rectangle, but rather a trapezium or even a triangle. Devices with a silicon thickness of approximately 10 nm and a width ranging from 5 to 30 nm were made.

Fig.2.13: TEM cross section of a junctionless transistors with increasing width from left to right

#### 2.5.I-V Characteristic Curve of JLFET

Junctionless transistors have excellent on–off switching behavior and an on/ off ratio larger than  $10^5$  for  $V_{DD}$ =0.5 V (Fig.2.14). The off current could not be measured as it is lower than 1 fA, which is the sensitivity limit of the measuring apparatus.

Fig.2.14: Drain current versus gate voltage for N - and P- type junctionless gated resistors and a trigate inversion-mode, N-channel MOSFET.  $N_D = 1 \times 10^{19} \text{ cm}^{-3}$  in the junctionless device.  $L = 1 \mu m$ .

## 2.6. Mobility of charge carriers in JLFET

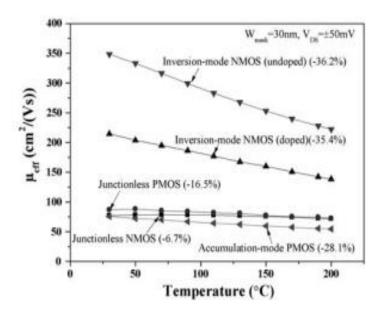

Mobility in junctionless devices is largely dominated by ionized impurity scattering, and acoustic phonons seem to have little effect on mobility. Figure 2.15 shows the mobility, measured from the peak of transconductance as a function of gate voltage, in trigate SOI MOSFETs and in junctionless transistors. The inversion-mode trigate devices have either an undoped channel ( $N_A = 5 x 10^{15} \ cm^{-3}$ ) or a doped channel ( $N_A = 5 x 10^{17} \ cm^{-3}$ ). In the undoped devices the peak mobility is 350 cm² /Vs at room temperature, but drops by 36% as temperature is increased to 200C. The doped devices have a lower room-temperature mobility (220 cm² /Vs) which also drops by approximately 36% as temperature is increased to 200C. The heavily doped ( $N_D = 2 x 10^{19} \ cm^{-3}$ ) junctionless devices have a much lower room-temperature mobility: 80 cm² /Vs. However, the mobility decreases <7% as temperature is increased to 200C. This clearly illustrated the fact that mobility is limited by ionized impurity scattering and is relatively insensitive to phonon scattering in heavily doped junctionless transistors.

Fig.2.15: Mobility in heavily doped junctionless transistors and in regular trigate MOSFETs with doped and undoped channels, as a function of temperature.

#### 2.7. Comparative study between JLFETs and MOSFETs

- Current Drive: In junctionless transistors, the electric field perpendicular to the current flow is substantially lower than in ordinary inversion mode or accumulation-mode field-effect transistors. Because this electric field reduces inversion channel mobility in metal-oxide semiconductor transistors, junctionless transistors may have a benefit in terms of current drive for manometer-scale complementary metal-oxide semiconductor applications. When quantum confinement is present, this observation still holds true. A Junction transistor's large carriers in the channel region act as a barrier to carrier scattering, but a Junctionless transistor does not have this problem, resulting in a high current drive.

- Structural Complexity at deep sub-micron level: A classical MOS transistor comprises two PN junctions called the source junction and the drain junction. The formation of such junctions involves extremely high doping concentration gradients, and very low thermal budget processing must be used. Flash annealing techniques are currently used to heat silicon for a very short time period in order to minimize diffusion, but even in total absence of diffusion, ion implantation and other doping techniques do not achieve perfectly abrupt junctions with infinite concentration gradients. The formation of ultrashallow junctions with high doping concentration gradients has become an increasingly difficult challenge for the semiconductor industry. On the other hand "Junctionless transistors (also called gated resistor) have

- no junctions and no doping concentration gradients. These devices have full CMOS functionality and are made using silicon nanowires.

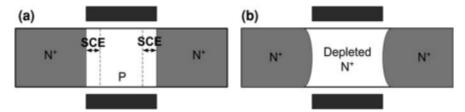

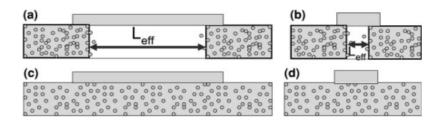

- Short Channel Effects(SCE): In a "regular", inversion-mode trigate device, assuming the distance between the source and drain junctions is exactly equal to the physical gate length (Fig.2.4a), the presence of PN+ junctions creates a reduction of the effective gate length, resulting in a shortchannel effect (SCE). This effect has been quantified using the voltage-doping transformation model (VDT). The VDT can be used to translate the effects of shrinking device parameters such as gate length or drain voltage into electrical parameters. The decrease of threshold voltage with decreased gate length is a well-known short-channel effect called the "threshold voltage roll-off". The SCE is illustrated in Fig.2.16 (a) for an inversion-mode transistor. In a junctionless device in the off state, the electrostatic squeezing effect causes the distance between the non-depleted source and drain regions to be larger than the physical gate length (Fig.2.16 b). This is a beneficial factor that reduces short-channel effects and can possibly reduce source-to drain direct tunneling in very short-channel devices.

Fig. 2.16: Illustration of effective channel length in an inversion-mode device (a) and (b) a junctionless transistor.

• Robustness against doping fluctuations: With the statistical distribution of doping impurities is the variation of effective channel length, L<sub>eff</sub>, defined as the distance between the source junction and the drain junction. This is illustrated in Fig.2.17, the statistical nature of the doping atom distribution at the source and drain junctions causes the effective channel length to fluctuate from device to device. These fluctuations are inherent to the ion implant and diffusion processes. Furthermore, dopants from the source and drain can scatter in the channel region and influence the threshold voltage. In the junctionless device, there is no gradient of doping concentration between source, channel and drain. The effective channel length can no longer be

defined as the distance between two junctions. The effective gate length is basically equal to the physical gate length, although it may be somewhat longer when the device is turned off.

Fig.2.17: Scattering of source and drain doping impurities in the channel of (a) a long-channel and (b) a short-channel inversion-mode MOSFETs; (c) long-channel and (d) short-channel junctionless devices

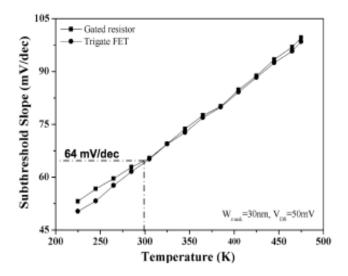

• **Subthreshold Slope:** The subthreshold slope at room temperature JLFET is 64 mV/decade, and it remains very close to the "ideal" value of  $(kT/q) \ln(10)$  over the temperature range 225–475 K. Figure 2.18 shows the evolution of subthreshold slope, SS (in mV/decade) at  $V_{DS}$ =50 mV in a N-channel inversion-mode trigate MOSFET and a junctionless gated resistor. The subthreshold slope of both devices follows the following law: SS = n  $(kT/q) \ln(10)$  with n = 1.066, which is very close to the lowest theoretical limit (n = 1).

Fig. 2.18: Measured subthreshold slope versus temperature in a junctionless gated resistor and an inversion-mode trigate MOSFET.

#### 2.8. Adverse effects of high level doping in JLFET

#### 2.8.1. Mobility Degradation:

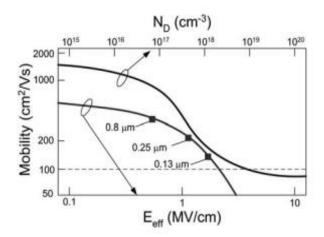

The effect of the high channel doping concentration of junctionless gated resistors is on carrier mobility. It is well known that ionized impurity scattering degrades carrier mobility. The electron mobility in silicon is shown in Fig.2.19 as a function of donor atom concentration,  $N_D$ . The mobility drops from 1,400 cm<sup>2</sup> /Vs in lightly doped silicon to 80 cm<sup>2</sup> /Vs for  $N_D$ =10<sup>19</sup> cm<sup>-3</sup> .

Channel mobility in inversion-mode devices is affected by the (vertical) electric field in the channel,  $E_{\rm eff}$ . Since  $E_{\rm eff}$  increases when the effective oxide thickness, EOT, is reduced, surface channel mobility has steadily decreased in successive technology nodes and would now be well below  $100~{\rm cm^2}$ /Vs at the 45-nm node, if it wasn't for the introduction of strained silicon technology.

Fig.2.19: Electron mobility in silicon as a function of donor doping atom concentration and as a function of electric field in the channel. The latter curve shows the mobility/field for several key technology nodes.

#### **2.8.2.Random Dopant Fluctuations(RDF):**

Doping fluctuations are a serious problem in nanoscale devices. Even in the so called "undoped" channels the doping concentration is not equal to zero but to a value of a few  $10^{15}$  cm<sup>-3</sup>. This means that there a chance of approximately one in a thousand to find a (boron) doping atom in a device with a channel volume of  $10 \times 10 \times 10 \text{ nm}^3$ .

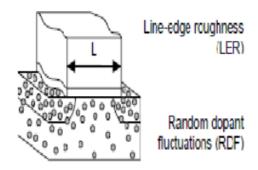

Random dopant fluctuation (RDF) is a type of process variation caused by changes in the concentration of implanted impurities. RDF in the channel region of MOSFET transistors can change the transistor's characteristics, particularly the threshold voltage. Because the total amount of dopants in contemporary process methods is lower, and the insertion or removal of a few impurity atoms can drastically modify transistor's electrical characteristics, and thus RDF has a stronger effect. RDF is a type of local process variation in which two identical transistors on a same silicon die with similar dopant concentrations may have considerably different dopant concentrations. Fig 2.20 depicts the variations in the structure of a scaled device.

Fig.2.20: Primary sources of variation in a nanoscale device

These variations interact with one another, affecting every aspect of circuit performance. The RDF effect is primarily a random effect. The uncertainty in charge location and numbers, such as the discrete placement of dopant atoms in the channel region that follow a Poisson distribution, causes this well-known phenomenon. The overall number of channel dopants reduces as the device size shrinks, resulting in a wider fluctuation in dopant quantities and a considerable impact on threshold voltage shown in the Fig 2.21.

Fig. 2.21: Appearance of RDF increases with reduction in size of semiconductor bulk.

Variability of junctionless field-effect transistor (JL-FET) performance due to random dopant fluctuation (RDF) is projected to be a serious problem when scaled to nanoscale dimensions as the total number of dopant atoms becomes increasingly discretized. While line edge roughness (LER)-induced variability was already shown to be significant for junctionlessFinFETs(JL-FinFETs) at even small rootmean-square amplitudes (LER), there has not been an equivalent study on the effect of RDF for such devices.

#### 2.9. Work Progress in JLFET:

Few of the extensive research reports on JLFET are mentioned in the following list:

- The idea of JLFET was first published in a patent filled by Polish-American physicist and inventor Julius E. Lilienfeld in, "Method and Apparatus for Controlling Electric Currents," in 1926 in which he proposed a three-electrode structure using copper-sulfide semiconductor material. Lilienfeld Transistor is the basic structure of the evolved JLFET.[69]

- First physical design of JLFET was patented in 2009 by Prof. J.P. Colinge in the paper entitled "Junctionless Transistor" communicated about the proposed novel device and all the limitations that are associated with FET structures when they are scaled sown to 10nm. The proposed device named as Junctionless FET or gate resistor, has simpler fabrication and involves fewer steps as compared to that of MOSFET.[2]

- Lee et. al. in 2010 studied the junctionless transistor for deep submicron technology node. They have simulated both inversion mode  $(N-P^+ N)$  and accumulated mode junctionless  $(N^+ N^+ N^+)$  transistor and concluded that junctionless FET have improved short channel characteristics.[1]

- In the 2010 papers by Colinge et al and Lee et al. , first reports of electrically measured JNTs(Junctionless Nanowire Transistors) in Si channel were shown, including both n-type and p-type transfer and output characteristics for L = 1  $\mu$ m, W= 20 nm.[6]

- Important early reports on the JNT in 2010 include the work by Colinge et al, where the electric field perpendicular to the current flow is found to be significantly lower in junctionless transistors which may be another advantage for this device type. In addition, the same group reported how the JNT can be fabricated to yield low subthreshold slopes in combination with impact ionization effects. [5]

- In the following year of 2010, many research reports were documented. Renan DoriaTrevisoli et al. presented a physically based analytical model for the threshold voltage in junctionless nanowire transistors (JNTs). The model was based on the solution of the two-dimensional Poisson equation and included the dependence on JNT width, height and doping concentration. The quantum confinement was also taken into consideration in the model formulation. [62]

- In 2012, Park, Chan-Hoon et al. fabricated n-channel junctionless nanowire transistors with gate lengths in the range of 20–250 nm, and have compared their electrical performances with conventional inversion-mode nanowire transistors. The junctionless tri-gate transistor with a gate length of 20 nm showed excellent electrical characteristics with a high I<sub>on</sub>/I<sub>off</sub> ratio (>106), good subthreshold slope (~79 mV/dec), and low drain-induced barrier lowering (~10 mV/V). The simpler fabrication process without junction formation results in improved short-channel characteristics compared to the inversion-mode devices, and also makes the junctionless nanowire transistor a promising candidate for sub 22-nm technology nodes.[63]

- In the same year of 2012, Razavi et al investigated two important device metrics, intrinsic gate-delay and energy-delay product of triple-gate junctionless nanowire transistors (JNTs) with gate lengths from 22 nm down to 15 nm, for different channel doping concentrations and compare them with those of triple-gate inversion-mode (EVI) nanowire field-effect transistors. Our study shows although intrinsic gate-delay is larger in junctionless devices compared to those of EVI devices, since the 16 switching energy is smaller in JNTs, energy-delay product is almost identical for both junctionless and IM devices.[64]

- In the same year, Ting-Kuo Kang investigated the piezoresistive effect in n-type silicon nanowires on silicon-on-insulator wafers, also called junctionless nanowire transistors (JNTs). A marked change in the subthreshold drain current for strained JNTs was observed that could be attributed to strain-induced interface state modification, due to an increase in the interface state for tensile strain or a decrease in the trap activation energy for compressive strain. Through many long-time cycles of compressive and released strain, the electromechanical response of subthreshold IDS with time was found, supporting piezo-resistance effect. [65]

- Duarte et al. formulated a compact model of quantum electron density at the subthreshold region is derived for junctionless (JL) double-gate (DG) FETs. The proposed quantum model is obtained under two different quantum confinement conditions. One is for a case of a thick channel and a heavily doped channel, where quantum confinement effects (QCEs) are modeled by a 1-D quantum harmonic oscillator. The other is for a case of a thin channel, where QCEs are modeled by the use of a 1-D quantum well surrounded by high potential barriers and an energy correction term coming from the depletion charge. It is shown that, regardless of the channel thickness, the quantum confinement is higher in JL than in inversion-mode (IM) DG FETs.[66]

- In the following year,Razavi and Fagas evaluated the performance of III-V inversionmode and junctionless nanowire field-effect transistors using quantum simulations. Specifically they modelled InAs, GaSb, and GaAs devices. One of the main conclusions of that modelling work was that III-V junctionless nanowire transistors are more immune to short-channel effects than conventional inversionmode III-V nanowire field-effect transistors.[15]

- In the year of 2014, Yu et al. reported p-type JNT with a Ge channel fabricated by a CMOS compatible top-down process . At that time the transistors exhibited the lowest Subthreshold Slope to date for Ge junctionless devices. The devices with a gate length of 3  $\mu$ m exhibited a subthreshold slope of 216 mV/dec with an  $I_{on}/I_{off}$  current ratio of 1.2×103 at  $V_D$  = -1V and DIBL of 87 mV. The process consisted of electron beam lithography and reactive ion etch for patterning, a GeO<sub>2</sub> passivation step, ALD-based Al<sub>2</sub>O<sub>3</sub> deposition, and gate formation and metallization thereafter.[11]

- In 2014 Song et al. reported the first experimental demonstration of III-V based JNTs using a gate-all-around architecture based on GaAs. The fabricated devices were scaled down to nanowire widths of 9 nm and gate lengths of 80 nm. The authors stressed that the electrical performance of the devices was particularly promising for low power RF applications.[16]

- In 2015,Sun et al. fabricated JNTs on ultra-thin-body germanium-on-insulator substrates using a simple Si-compatible top-down process. The devices with gate lengths and widths less than 100 nm, exhibited  $I_{on}/I_{off}$  ratios of ~ 105 with a 1 V supply voltage .[12]

- In parallel to the development of the Ge JNTs, many groups worked on the evaluation and demonstration of III-V based JNTs.In 2015 Leung et al. performed a very extensive device performance analysis based on TCAD, of In<sub>0.53</sub>Ga<sub>0.47</sub>As channel JNTs. For example, n-type In<sub>0.53</sub>Ga<sub>0.47</sub>As has some advantages over ptype In<sub>0.53</sub>Ga<sub>0.47</sub>Asand Si in terms of JNT sensitivity to process variations. They also studied the impact of random dopant variation on it.[17]

- In the same year of 2015, Asthana Pranav Kumar et al. presented a GaSb/InAsjunctionless tunnel FET and investigate its static device characteristics. The proposed structure presents tremendous performance at a very low supply voltage of 0.4 V ,at a 17 temperature of 300 K, gate length of 20 nm, HfO<sub>2</sub> gate dielectric thickness of 2 nm, film thickness of 10 nm, low-k spacer thickness of 10 nm. The key idea was to the present device architecture, which can be exploited as a digital switching device for sub 20 nm technology. Numerical simulations resulted in an I<sub>OFF</sub> of ~8 × 10<sup>-17</sup> A/μm, I<sub>ON</sub> of ~9 μA/μm, I<sub>ON</sub>/I<sub>OFF</sub> of ~1 × 10<sup>11</sup>, subthreshold slope of 9.33 mV/dec and DIBL of ~87 mV/V.[67]

- Djara et al. reported device performance of a tri-gate In<sub>0.53</sub>Ga<sub>0.47</sub>As-on-insulator (InGaAs-OI) JNT architecture. The fabricated devices had a 20-nm-thick In<sub>0.53</sub>Ga<sub>0.47</sub>Asn channel doped to 10<sup>18</sup>/cm<sup>3</sup>. The authors of that work highlighted that the tri-gate InGaAs-OI JNT showed the best compromise in terms of threshold voltage, SS and DIBL compared to the other III–V JNTs architectures reported to date.[18]

- In the following years, S. Sahay and M. J. Kumar proposed a double gate junctionless FET (DGJLFET) with an extended back gate (EBG) architecture for significantly improved performance in the sub-10-nm regime also demonstrated the quantum confinement-induced bandgap widening diminishes the parasitic bipolar junction transistor (BJT) action and, therefore, facilitates the scaling of the conventional DGJLFETs to the sub-5-nm channel regime where the quantization effects are significant.[19]

- In the year of 2017, Thirunavukkarasu et al. experimentally demonstrated silicon junctionless (JL) trench gate-all-around (GAA) nanowire field-effecttransistor with an atomically thin channel thickness of 0.65 nm and a very thin oxidewith a thickness of 12.3 nm. Experimental results indicated that this device with achannel thickness of 0.65 nm achieves a sub-threshold slope (SS) of 43

mV/decade, which is the best yet achieved by any reported JLFET. Owing to the atomically thinchannel, this device has an extremely high  $I_{ON}/I_{OFF}$  current ratio of >108.Furthermore, the atomically thin channel GAA JLFET exhibits a low thresholdvoltage (V<sub>TH</sub>) variation and negligible drain-induced barrier lowering(DIBL < 0.4 mV/V). [20]

- In the same year, DehdashtiAkhavan et al studied the influence of random dopantfluctuations (RDF) on the statistical variability of the electrical characteristics ofn-channel silicon junctionless nanowire transistor (JNT) using three dimensional quantum simulations based on the non-equilibrium Green's function (NEGF) formalism.[21]

- In the following years,S. Berrada et al. used the Non-Equilibrium Green's Functionformalism to study the dependence of the threshold voltage variability on the cross-section shape and the gate length in Junction Less Field Effect Transistors.[22]

- M.K.A Titu et al., In their work, by employing self-consistent solver studiedCapacitance-Voltage (C-V) characteristics and the threshold voltage variation ofp-type Rectangular Gate Junctionless Field Effect Transistor (RG-JLFET) andDouble Gate Junctionless Field Effect Transistor (DG-JLFET). The self consistentsolver solves Schrodinger-Poisson equations with appropriate boundary conditionsand takes wave function penetration and other quantum mechanical effects intoaccount.[61]

- Recent years include work of Bora ,N. et al. presented an analytical model for ultrascaled symmetric double gate (SDG) nanowire junctionless field effect transistor(JLFET), which includes charge quantization in all the regions of operation. Thismodel was based on a first-order correction for the confined energies obtained bysolving the Schrodinger's equation. The model predicted the quantum mechanical effects (QME) on the surface potential, drain current and transconductance for a highly doped and extremely thin silicon layer of thickness down to 4nm.[68]

- Bora ,N. et al. presents the effects of quantum confinements on the surfacepotential, threshold voltage, drain current, transconductance, and drain conductance a Dual Material Double Gate Junctionless Field Effect Nanowire Transistor(DMDG-JLFENT). The carrier energy quantization on the threshold

voltage of aDMDG-JLFENT is modeled, and subsequently, other parameters like drain currentwere analytically presented. The QME considered here is obtained under thequantum confinement condition for an ultra-thin channel, i.e., below 10 nm of Sithickness.[23]

• In our current year, Bolokian, M. et al. suggested a junctionless field effect transistorwith an embedded p-type layer (EPL-JLT) near the drain channel side, employing calibrated structure simulations to obtain a complete depletion region in a 6 nmchannel length. The incorporation of a p-type layer improves leakage current (I<sub>OFF</sub>) and subthreshold swing (SS) for a 6 nm regime structure at 5.9 eV work function(WF) while the ON current (I<sub>ON</sub>) diminishes a little. This considerable achievement in the leakage current enables obtaining multiple threshold voltages (V<sub>TH</sub>) byadjusting the gate WF. The proposed device has a leakage current of 1 nA μm<sup>-1</sup> evenat a 5.1 eV WF. The scaling of the EPL-JLT for different channel lengths is investigated. [24]

#### 2.10. Work Ahead

From the chronological literature survey on Junctionless transistors(JLFET) since its birth on 2009, numerous investigations and simulations were performed to explore the physical properties and characteristics of the new born novel device, JLFET. After vast researches on JLFET, we precisely modeled I-V Characteristics of JLFET and also diminished Subthreshold Slope well below 60mV/dec at deep sub-micron level. In addition to that, short channel effects on JLFET were also extensively studied and alleviated problems of SCE to a large extent with significant reduction in DIBL.

But most of the proposed models lacked inclusion of Quantum Confinement Effects which is a quite significant factor in such deep submicron levels, Charge confinement due to Quantum Confinement effects strongly influence physical parameters of JLFET. Variation of Threshold Voltage, Subthreshold Slope and other parameters due to Quantum effects should be considered for evolving a more precise analytical model of JLFET.

Doping Fluctuation (RDF) has detrimental effects on the performance of JLFET at deep submicron levels. A few papers regarding effects of RDF on JLFET were studied without inclusion of quantum confinement effects. Thus work remains to be done regarding impact of RDF on variation of physical parameters of JLFET along with inclusion of Quantum Effects due to dimensions scaling.

# Chapter 3

# **Device Simulation of JLFET**

We have simulated short channel DG SMG JLFET using Silvaco TCAD Atlas and observed physical properties of JLFET under different modes of operation.

Following specifications of DG SMG JLFET are used in our simulation:

| Device Parameters                               | Value                                                                         |

|-------------------------------------------------|-------------------------------------------------------------------------------|

| $t_{ox}(Gate\ Oxide\ Thickness)$                | 1nm                                                                           |

| $\epsilon_0(Permittivity\ of\ Free\ Space)$     | $8.854 \text{x} 10^{-12} \text{m}^{-3} \text{ kg}^{-1} \text{s}^4 \text{A}^2$ |

| $\epsilon_{Si}(Permittivity\ of\ Si)$           | $11.8\epsilon_0$                                                              |

| $\epsilon_{ox}(Permittivity\ of\ Oxide)$        | $3.97\epsilon_0$                                                              |

| $\chi_m$ (Electron Affinity)                    | 4.17 eV                                                                       |

| $t_{Si}(Si\ Substrate\ Thickness)$              | 2nm                                                                           |

| $L_G(Gate\ Length\ of\ JLFET)$                  | 20nm                                                                          |

| $N_D(Donor\ Concentration\ in\ Si)$             | $5x10^{19}cm^{-3}$                                                            |

| $L_S(Source\ Length\ of\ JLFET)$                | 2.5nm                                                                         |

| $L_D(Drain\ Length\ of\ JLFET)$                 | 2.5nm                                                                         |

| $W_{Si}(Width\ of\ Silicon\ Bulk)$              | 2nm                                                                           |

| $L_{Si}(Length\ of\ Silicon\ Substrate)$        | 25nm                                                                          |

| $\phi_m$ (Work Function of n $^+$ Poly Si Gate) | 4.7eV                                                                         |

| $V_{DS}$ (Drain to Source Voltage)              | 0.05V                                                                         |

| a (Lattice Constant of Si)                      | 5.429Å                                                                        |

| $m_0$ (Rest mass of $e^-$ )                     | 9.11x10 <sup>-31</sup> kg                                                     |

| $m_l$ (Longitudinal Effective mass of $e^-$ )   | $0.92m_0$                                                                     |

| $m_t$ (Transverse Effective mass of $e^-$ )     | $0.19m_0$                                                                     |

Table 3.1. Device Parameters for simulation of JLFET.

## 3.1 Results and Discussion

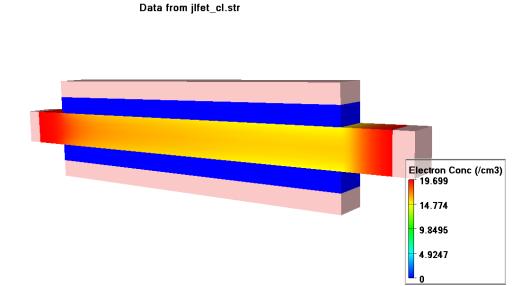

We have simulated a short channel Double Gate (DG) Single Material Gate(SMG) Junctionless Transistor presented in Figs. 3.1 and 3.2 using Silicon as bulk material with channel length  $L_G$  as 20nm, bulk thickness  $t_{Si}$  as 2nm, bulk width  $W_{Si}$  as 2nm, oxide thickness  $t_{ox}$  as 1nm and Donor Dopant Density  $N_D$  of  $5 \times 10^{19}$  cm<sup>-3</sup>.

ATLAS

Data from ilfet.str

Fig. 3.1: 3D Device Structure of DG SMG JLFET.

Fig.3.2: Cross Sectional View of DG SMG JLFET.

We would be using bulk conduction regime of JLFET for threshold voltage and sub threshold drain current calculations, so it is a good approximation to use bulk mobility of electrons  $(\mu_n = 1350 \ cm^2 V^{-1} Sec^{-1})$  instead of surface mobility.

We would now analyze behavior of JLFET in different operation modes.

#### **Depletion Mode:**

We provided a negative bias Gate Voltage  $(V_{GS} = -0.6V, V_{DS} = 0.5V)$  and observed changes in Physical Parameters of JLFET under Depletion Mode.

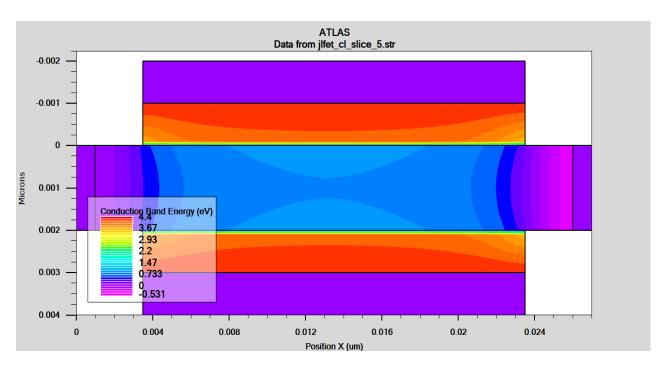

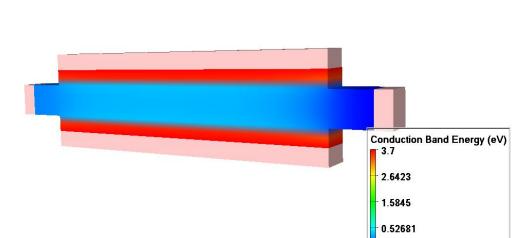

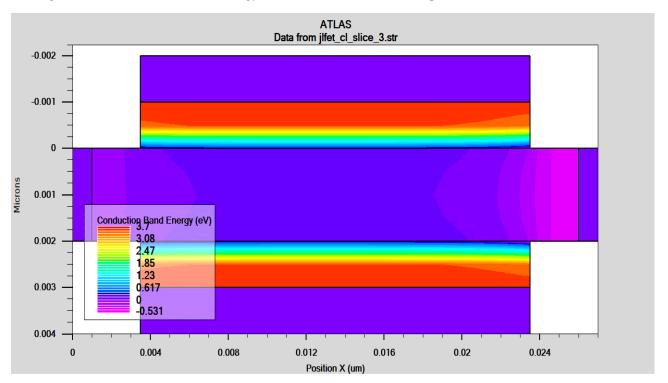

InFig.3.3 and Fig.3.4,we could observe symmetry in conduction band energy due to symmetric DG JLFET structure.

ATLAS

Data from jlfet\_cl.str

Fig. 3.3: Conduction Band Energy in JLFET under Depletion Mode(3D View).

Fig. 3.4: Conduction Band Energy in JLFET (Cross Sectional view) under Depletion Mode.

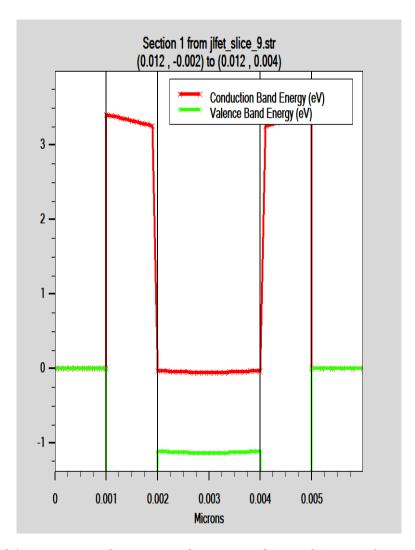

Figs.3.4. and 3.5. depict symmetric upward band bending of Conduction Band Energy near surface region throughout the channel length.

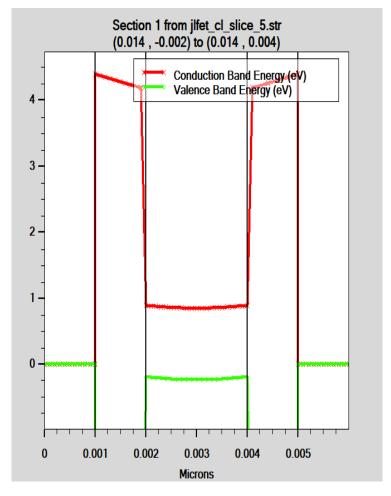

Fig. 3.5: Energy Band Diagram of JLFET under Depletion Mode.

We could see from Fig 3.4. and 3.6, a considerable conduction band energy barrier around the bulk region would prevent drift flow of electrons from source to drain despite of having a considerable drain voltage.

Fig.3.6. shows Conduction Band Energy barrier is quite significant in the central line channel region that would prevent bulk conduction of current through drift mechanism. Diffusion mechanism is insignificant in JLFET because electrons are the majority charge carriers responsible for current conduction.

Fig.3.6: Variation of Conduction Band Energyacross the central line channel of JLFET under Depletion Mode.

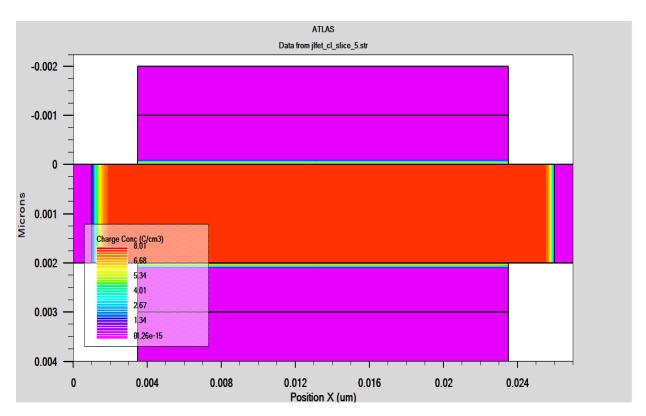

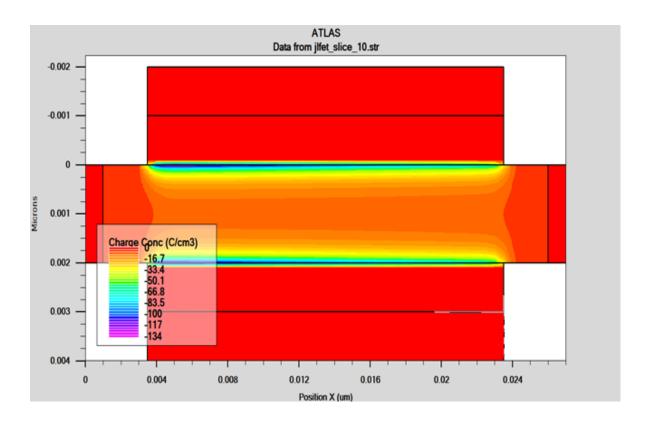

If we observe conduction band energy distribution across oxide layers in Fig.3.4, a gradient in conduction band energy instead of a constant value is found. It is also shown by a gradual rise of conduction band energy in Fig.3.5 appearing for the space charge apprising from ionization of dopant atoms in Silicon bulk.On the contrary, the fixed oxide trap charges and interface charges depicted in the oxide regions of Fig.3.7 are responsible for the abrupt rise in conduction band energy in oxide regions.

Fig. 3.7: Charge Concentration in JLFET under Depletion Mode.

Fig. 3.8: Hole Concentration in JLFET under Depletion Mode

Fig. 3.9: Hole Concentration in JLFET across the central line channel region of JLFET under Depletion Mode.

Under depletion mode, bulk region of JLFET is depleted of electrons as shown in Figs.3.10 and 3.11 rather accumulated by holes. There is a gradual increase in hole concentration as we move towards the channel region from either side due to symmetry in source and drain regions (symmetric for  $V_{DS} = 0$ ). Hole concentration is minimum in source and drain regions and gradually rises to maximum value in the bulk region across the channel, as evident from Figs.3.8. and 3.9.

ATLAS

Data from jlfet\_cl.str

Fig. 3.10: Electron Concentration in JLFET under Depletion Mode.

Fig.3.11:Electron Concentration across central line channel region of JLFET under Depletion Mode.

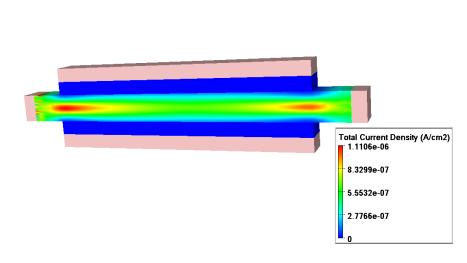

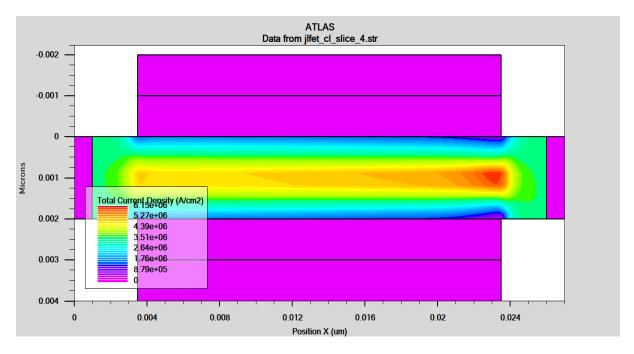

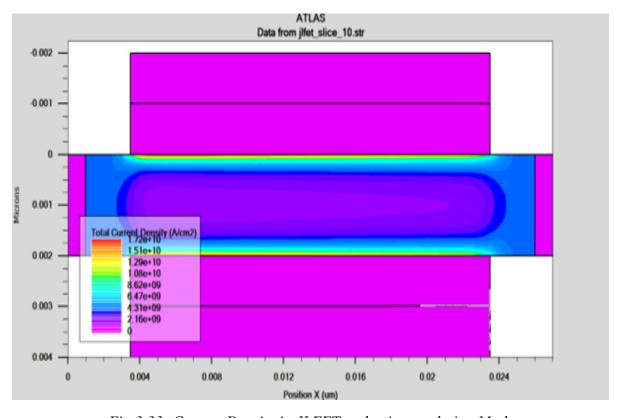

Under depletion mode, central line channel is vanished due to depletion of electrons in the bulk channel region resulting in discontinuity of flow from source to drain, as seen in Fig.3.12. Unlike MOSFETs, channel region tends to form around bulk instead of oxide-semiconductor interface surfaces. Current Density around oxide-semiconductor interface regions is negligible due to accumulation of holes near the surface regions as can be seen in Fig.3.8. Hotspots in the current density are found to appear in the vicinity of drain and source regions and gradually spread into the bulk region.

ATLAS Data from jlfet.str

Fig.3.12: Current Density in JLFET under depletion mode.

#### **Weak Depletion Mode:**

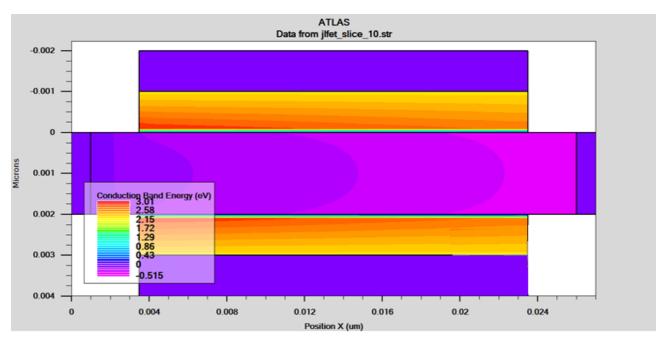

We provided a positive Gate Bias Voltage ( $V_{GS} = 0.1V$ ,  $V_{DS} = 0.5V$ ) and observed changes in Physical Parameters of JLFET under Weak Depletion Mode. The conduction band energies in JLFET under this mode are presented in Figs.3.13 (3D view) and 3.14 (cross-sectional view).

ATLAS

Data from jlfet\_cl.str

Fig. 3.13: Conduction Band Energy in JLFET under Weak Depletion Mode.(3D View).

Fig. 3.14: Conduction Band Energy in JLFET under Weak Depletion Mode(cross sectional view).

<u>0.5309</u>2

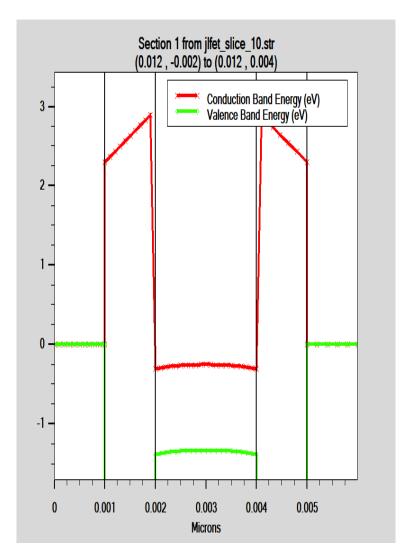

In Fig.3.13 and Fig.3.14,the upward band bending of Conduction Band Energy near surface region throughout the channel length is quite weaker compared to Fig.3.3 and Fig.3.4 in Weak Depletion Mode.We could see onset of Flat Band in the bulk region since Conduction Band Energy gradient is very less throughout the channel region in JLFET as depicted in Fig.3.15.

Fig.3.15: Energy Band Diagram of JLFET under Weak Depletion Mode

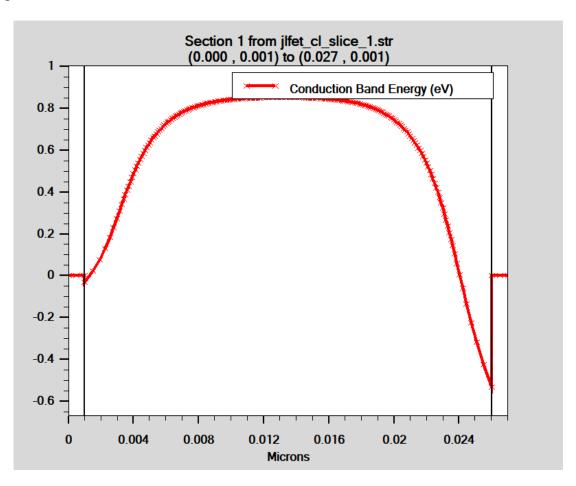

From Fig.3.16,we could infer conduction band energy barrier against electron flow from source to drain is significantly lowered in Weak Depletion Regionthat may lead to subthreshold current conduction through the central line channel region, provided significant electron concentration has been achieved in the bulk region.

Fig. 3.16: Variation of Conduction Band Energyacross the central line channel of JLFET under Weak Depletion Mode

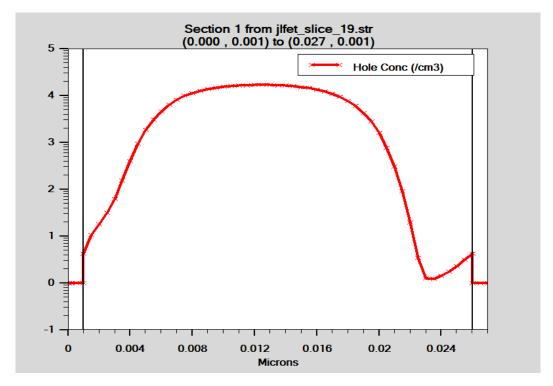

From Fig.3.17 and Fig.3.18, it is apparent that the hole concentration has been significantly lowered throughout the effective gate channel length. The central line channel region experiences minimum hole concentration as in Fig.3.19.

Fig.3.18:Hole Concentration across the central line channel region of JLFETunder Weak Depletion Mode (Horizontal Section)

Fig. 3.19: Hole Concentration in the central line channel region of JLFET under Weak Depletion Mode (Vertical Section).

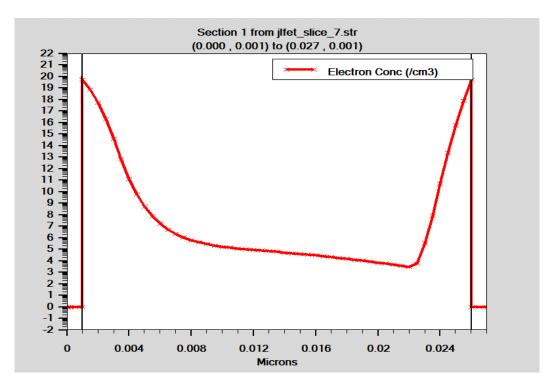

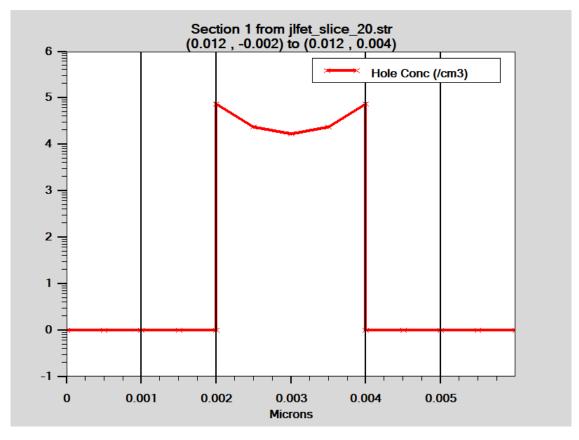

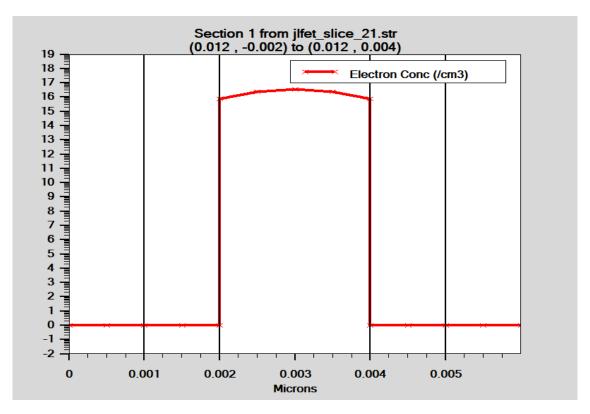

On the contrary, electron concentration has been drastically increased throughout the bulk region and maximum electron concentration (due to complete ionization of Dopant atoms in Source and Drain) gradually spreading across the channel region from source to drain as shown in Fig. 3.20, with a maximum peak around the central line region in Fig. 3.21.

**ATLAS**

Fig. 3.20: Electron Concentration in JLFET under Weak Depletion Mode.

Fig.3.21: Electron Concentration across central line channel region of JLFET under Weak Depletion Mode.

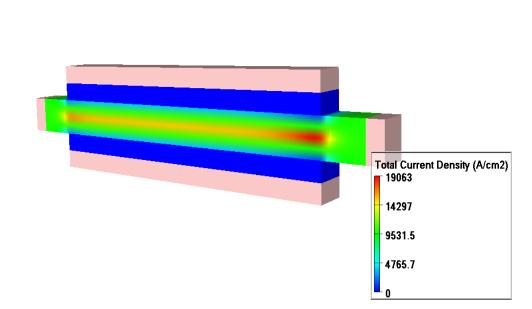

As electron concentration is significant in bulk channel region with greatly lowered conduction band energy barrier across the central line channel region, quite a prominent central line channel region has been formed resulting in bulk current conduction, shown in Fig. 3.22.

ATLAS

Data from ilfet\_cl.str

Fig. 3.22: Current Density in JLFET under Weak Depletion Mode.

#### **Weak Accumulation Mode:**

We provided a positive Gate Bias Voltage ( $V_{GS} = V_{TH} = 0.38V$ ,  $V_{DS} = 0.5V$ ) and observed changes in Physical Parameters of JLFET under Weak Accumulation Mode.

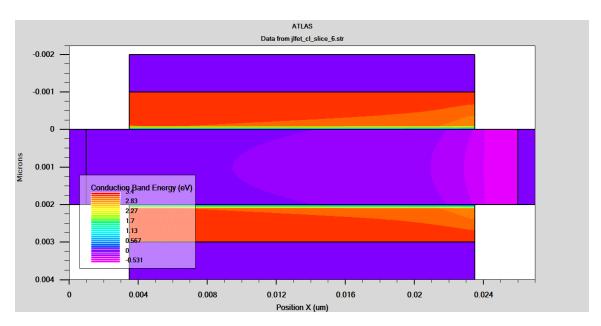

From Fig.3.23,we could see there is a visble downward band bending of Conduction Band Energy near surface region throughout the channel length that implies onset of accumulation of electrons at the surfaces in Weak Accumulation Mode. We could see Flat Band Condition in the bulk region in Fig.3.24 under this condition.

Fig.3.23: Conduction Band Energy in JLFET under Weak Accumulation Mode (Cross Sectional view)

Fig. 3.24: Energy Band Diagram of JLFET under Weak Accumulation Mode.

For Gate Voltage equal to Threshold Voltage ,there is no conduction band energy barrier opposing electron flow from source to drain rather download slope of conduction band energy assists in drift current conduction through the central line channel region. Fig. 3.25 supports this fact.

Fig. 3.25: Variation of Conduction Band Energyacross the central line channel of JLFET under Weak Accumulation Mode.

With onset of accumulation region, hole concentration starts to diminish throughout the effective gate channel length gradually from drain to source, as shown in Fig.3.26.

ATLAS

Data from jlfet\_cl.str

Fig. 3.26: Hole Concentration in JLFET under Weak Accumulation Mode.

From Fig.3.27,we could see maximum electron concentration (due to complete ionization of dopant atoms in Source and Drain) throughout the bulk region in JLFET.

Fig. 3.27: Electron Concentration in JLFET under Weak Accumulation Mode.

A Significant bulk channel as well as surface channel have been formed due to accumulation of electrons at the surfaces (seen in Fig.3.28),resulting in significant current flow both through bulk conduction regime as well as accumulation layer regime(inFig.3.29).

**ATLAS**

Fig. 3.28: Current Density in JLFET under weak accumulation mode (3D View).