#### DESIGN OF A LOW-POWER ASYNCHRONOUS 10-BIT SAR ADC IN 65 nm TECHNOLOGY

## THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENT FOR THE DEGREE OF MASTER OF TECHNOLOGY

IN

#### VLSI DESIGN & MICROELECTRONICS TECHNOLOGY

## THESIS SUBMITTED BY SHIBMALYA SEN

University Registration No.: 154114 of 2020-2021

Exam Roll No.: M6VLS23009

Class Roll No.: 002010703012

UNDER THE SUPERVISION OF **DR. SAYAN CHATTERJEE**

### DEPARTMENT OF ELECTRONICS AND TELE-COMMUNICATION ENGINEERING

JADAVPUR UNIVERSITY

**JUNE 2023**

#### **CERTIFICATE OF RECOMMENDATION**

This is to certify that the thesis entitled "DESIGN OF A LOW-POWER ASYNCHRONOUS 10-BIT SAR ADC IN 65 nm TECHNOLOGY" has been carried out by SHIBMALYA SEN (University Registration No: 154114 of 2020-2021) under my guidance and supervision and be accepted in partial fulfilment of the requirement for awarding the degree of "MASTERS OF TECHNOLOGY IN VLSI AND MICROELECTRONICS". The research results presented in this thesis have not been included in any other paper submitted for the award of any degree to any other Institute or University.

#### DR. SAYAN CHATTERJEE

#### EXTERNAL THESIS SUPERVISOR

DEPT. OF ELECTRONICS AND TELECOMMUNICATION ENGINEERING JADAVPUR UNIVERSITY **KOLKATA 700032**

PROF. ARDHENDU GHOSHAL **Prof. MANOTOSH BISWAS**

HEAD OF THE DEPARTMENT **DEAN**

DEPT. OF ELECTRONICS AND FACULTY OF ENGINEERING

ELECOMMUNICATION ENGINEERING AND TECHNOLOGY

JADAVPUR UNIVERSITY JADAVPUR UNIVERSITY

**KOLKATA 700032 KOLKATA-700032**

# CERTIFICATE OF RECOMMENDATION

This is to certify that the thesis entitled "DESIGN OF A LOW-POWER ASYNCHRONOUS 10-BIT SAR ADC IN 65 nm TECHNOLOGY" has been carried out by SHIBMALYA SEN (University Registration No: 154114 of 2020-2021) under my guidance and supervision and be accepted in partial fulfilment of the requirement for awarding the degree of "MASTERS OF TECHNOLOGY IN VLSI AND MICROELECTRONICS". The research results presented in this thesis have not been included in any other paper submitted for the award of any degree to any other Institute or University.

DR. SAYAN CHATTERJEE

Dr. Sayan Chatterjee

Professor

Electronics & Telecomm. Engg. Dept.,

Jadavpur University, Kolkata - 700032.

EXTERNAL THESIS SUPERVISOR

Jadavpul Ullica TION ENGINEERING

DEPT. OF ELECTRONICS AND TELECOMMUNICATION ENGINEERING

JADAVPUR UNIVERSITY

**KOLKATA** 700032

Prof. MANOTOSH BISWAS

HEAD OF THE DEPARTMENT

DEPT. OF ELECTRONICS AND

ELECOMMUNICATION ENGINEERING

JADAVPUR UNIVERSITY

**KOLKATA 700032**

MANOTOSH BISWAS

Professor and Head

Professor and Head

Electronics and Telecommunication Engineering

Jadavpur University, Kolkata - 32

Ardhendu Glioshel 12/06/23

PROF. ARDHENDU GHOSHAL

DEAN

FACULTY OF ENGINEERING

AND TECHNOLOGY

JADAVPUR UNIVERSITY

KOLKATA-700032

DEAN

Faculty of Engineering & Technology

JADAVPUR UNIVERSITY

KOLKATA-700 032

#### **CERTIFICATE OF APPROVAL**#

The foregoing THESIS is hereby approved as a creditable study of an Engineering Subject carried out and presented in a manner of satisfactory to warrant its acceptance as a pre-requisite to the DEGREE for which it has been submitted. It is to be understood that by this approval, the undersigned do not necessarily endorse or approve any statement made, opinion expressed or conclusion drawn therein but approve the THESIS only for the purpose for which it has been submitted

| submitted.                                             |                               |

|--------------------------------------------------------|-------------------------------|

| Committee on final examination for the evaluation of t | the Thesis                    |

|                                                        |                               |

|                                                        |                               |

|                                                        | (Signature of the Supervisor) |

|                                                        |                               |

|                                                        |                               |

|                                                        | (Signature of the Examiner1)  |

|                                                        |                               |

|                                                        |                               |

|                                                        | (Signature of the Examiner2)  |

|                                                        |                               |

# only in case the thesis is approved.

#### DECLARATION OF ORIGINALITY AND COMPLIANCE OF ACADEMIC ETHICS

I hereby declare that this thesis contains literature survey and original research work done by the undersigned candidate, as a part of his degree of "MASTER OF TECHNOLOGY IN VLSI AND MICROELECTRONICS". All information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that as required by these rules and conduct, I have fully cited and referenced all materials and results that are not original to this work.

#### Thesis Title

## DESIGN OF A LOW-POWER ASYNCHRONOUS 10-BIT SAR ADC IN 65 nm TECHNOLOGY

#### SHIBMALYA SEN

University Registration No.: 154114 of 2020-2021

Exam Roll No.: M6VLS23009

Class Roll No.: 002010703012

DEPT. OF ELECTRONICS AND TELE-COMMUNICATION ENGINEERING FACULTU OF ENGINEERING AND TECHNOLOGY

JADAVPUR UNIVERSITY

KOLKATA - 700032

|       | INDIA |                 |

|-------|-------|-----------------|

| Date: |       |                 |

|       |       | (SHIBMALYA SEN) |

|       |       | IV   Page       |

#### **ACKNOWLEDGEMENT**

I would like to begin by expressing my heartfelt gratitude to my esteemed Master's supervisor, Dr. Sayan Chatterjee, whose guidance and mentorship have profoundly shaped my interest and curiosity in the fascinating realm of Electromagnetism, including the captivating field of Microwave Engineering. Dr. Chatterjee's patience, extensive knowledge, and remarkable rapport with his students have undeniably brought out the very best in me. I am immensely fortunate to have had the opportunity to undertake my Master's thesis under the tutelage of such an accomplished and esteemed professor.

Furthermore, I would like to extend my sincere appreciation to the Head of the Department, Prof. Manotosh Biswas, whose unwavering support and willingness to lend a helping hand have been invaluable throughout my academic journey. His encouragement and guidance have played a pivotal role in my growth and development.

Lastly, but certainly not least, I am profoundly grateful to my beloved parents. Their unwavering belief in my abilities and unwavering encouragement to pursue my passion have been the cornerstone of my achievements. Without their unwavering support, I would not have reached the position I am in today. I am truly blessed to have such exceptional parents who have always been my pillars of strength.

I am deeply indebted to each of these individuals for their profound impact on my academic and personal growth. Their contributions have been immeasurable, and I will forever be grateful for the opportunities they have provided and the faith they have placed in me.

| Doto  |  |  |          |         |

|-------|--|--|----------|---------|

| Date: |  |  | (SHIBMAL | YA SEN) |

|       |  |  |          |         |

#### **ABSTRACT**

Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) is one of the most popular and widely used ADC architectures due to its high speed, low power, and reasonable resolution capabilities. SAR ADC has gained a lot of interest in recent years because of its suitability for portable and low-power devices. The SAR ADC works by comparing the input voltage to a series of reference voltages generated by a digital-to-analog converter (DAC), and then using a binary search algorithm to determine the closest match. The resolution of the SAR ADC depends on the number of bits in the digital output, and higher resolutions can be achieved by increasing the number of bits. However, increasing the number of bits results in longer conversion times and higher power consumption. Therefore, there is a tradeoff between resolution, speed, and power consumption in SAR ADC design. This thesis focuses on the design and optimization of SAR ADCs, including various circuit topologies, techniques, and architectures to achieve high performance, low power, and high resolution. The research also explores the impact of various process, voltage, and temperature (PVT) variations on the performance of SAR ADCs and proposes techniques to mitigate these effects. Finally, the proposed SAR ADCs are compared with existing state-of-the-art ADCs, and their performances are evaluated in terms of power consumption, speed, and resolution.

In recent years, there has been a growing need for Successive Approximation Register (SAR) Analog-to-Digital Converter in medical application such as pacemaker or neuromorphic applications. Accordingly, the demand for long battery life-time poses the requirement for designing ultra-low power SAR ADCs.

Presents work investigates an asynchronous 1.1V 10-bit successive approximation register (SAR) analog-to-digital converter (ADC) implemented in 65nm CMOS technology. The asynchronous SAR ADC system consists of an internal clock generator, sample and hold switches, capacitive digital-to-analogue converter (DAC), dynamic comparator, and SAR logic. Running a 64-point FFT on the output of the SAR ADC with a 1.2 V differential input signal results in a maximum ENOB of 9.38 bits at 20 MHz sample rate, an SNR of 56.56 dB and aof total power consumption of 676 uW. This SAR ADC system can be used in systems where low power consumption, moderate resolution and moderate speed are mainly required, such as computer memory cores for artificial intelligence applications and sensors for applications, Biomedical and neuromorphic chips.

#### **ABBREVIATIONS**

ADC Analog to Digital Converter

BWC Binary-Weighted Capacitor

DAC Digital to Analog Converter

DNL Differential Non-Linearity

DFF Delay type Flip Flop

DL Delay Line

DR Dynamic Range

ENOB Effective Number of Bits

FOM Figure of Merit

FFT Fast Fourier Transform

HD Harmonic Distortion

INL Integral Non Linearity

LSB Least Significant Bit

MSB Most Significant Bit

SAR Successive Approximation Register

SINAD Signal to Noise and Distortion Ratio

SFDR Spurious-Free Dynamic Range

SNR Signal to Noise Ratio

SHC Sample and Hold Circuit

TWC Two-Stage Weighted Capacitor

#### **List of Figures**

| Figure 1: ADC architectures, applications, resolution, and sampling rates     | 6  |

|-------------------------------------------------------------------------------|----|

| Figure 2: Block diagram of the SAR ADC                                        | 7  |

| Figure 3: Clock and timing profile of the SAR ADC                             | 7  |

| Figure 4: The conventional bootstrapped sample and hold circuit               | 10 |

| Figure 5: The basic structure of the single-stage dynamic latch comparator    | 12 |

| Figure 6: The two-stage preamplifier and dynamic latch                        | 13 |

| Figure 7: The R-2R structure                                                  | 16 |

| Figure 8: The conventional capacitive DAC                                     | 17 |

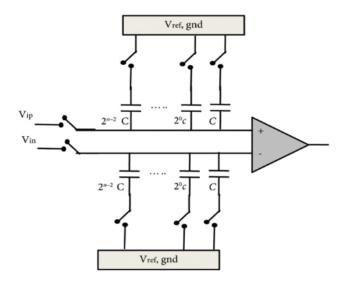

| Figure 9: Fully differential structure of CDAC                                | 18 |

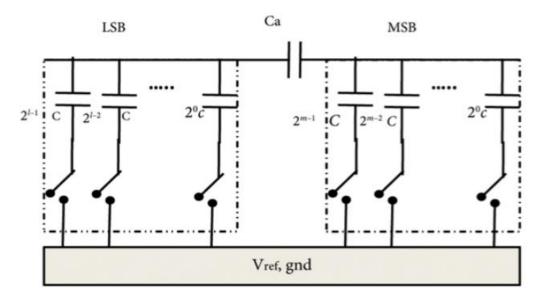

| Figure 10: The two-stage subarray capacitor technique                         | 18 |

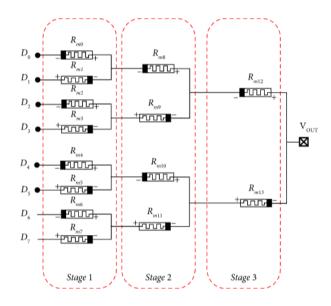

| Figure 11: The dual split three-stage subarray CDAC                           | 19 |

| Figure 12: The merge-split CDAC technique                                     | 19 |

| Figure 13: MSB split CDAC                                                     | 19 |

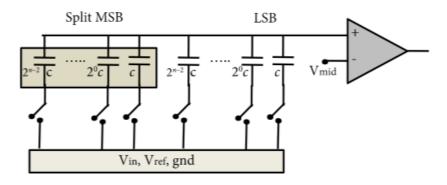

| Figure 14: LSB split CDAC                                                     | 20 |

| Figure 15: The C-2C dummy capacitor                                           | 20 |

| Figure 16: The charge-sharing switching technique                             | 21 |

| Figure 17: The asymmetric CDAC                                                | 21 |

| Figure 18: The capacitance multiplexing technique                             | 22 |

| Figure 19: The asymmetric switching with the segment CDAC                     | 23 |

| Figure 20: Extra reference voltage by using goblet architecture               | 23 |

| Figure 21: The dual sampling technique                                        | 24 |

| Figure 22: Hybrid and junction splitting                                      | 24 |

| Figure 23: The schematic of the SC integrator                                 | 25 |

| Figure 24: The pseudo-two-stage SAR with active charge-transferring technique | 25 |

| Figure 25: The block diagram of SAR ADC in                                    | 26 |

| Figure 26: The DAC of two memristor connected in opposite direction           | 26 |

| Figure 27: The monotonic voltage switching scheme                             | 27 |

| Figure 28: The charge redistribution scheme                                   | 27 |

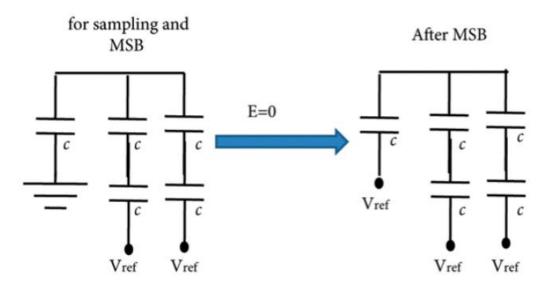

| Figure 29: Zero energy drained form Vcm                                       | 28 |

| Figure 30: The two-step switching method.                                     | 28 |

|                                                                               |    |

| Figure 31: The charge-sharing voltage scheme                                                                                                                | 29  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 32: The trilevel and Vcm-based capacitor switch                                                                                                      | 30  |

| Figure 33: The hybrid switching scheme                                                                                                                      | 30  |

| Figure 34: Two energy saving methods                                                                                                                        | 31  |

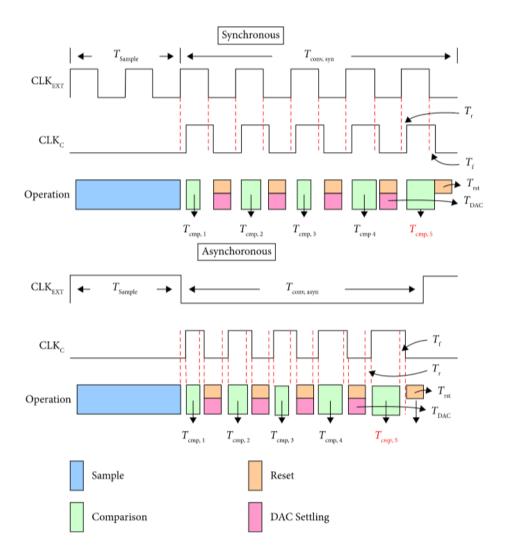

| Figure 35: Timing diagram of (a) synchronous and (b) asynchronous control logic                                                                             | 33  |

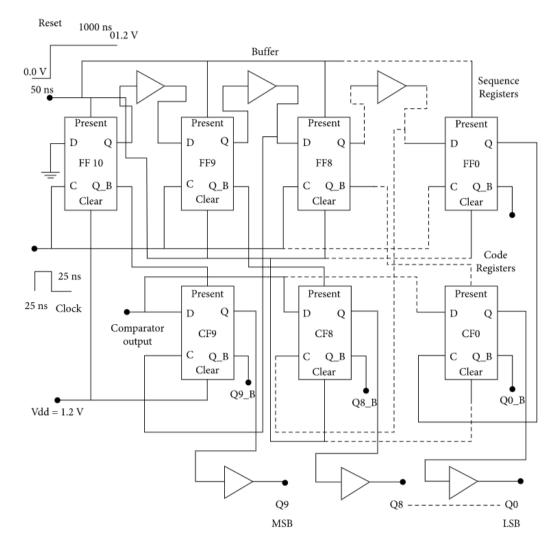

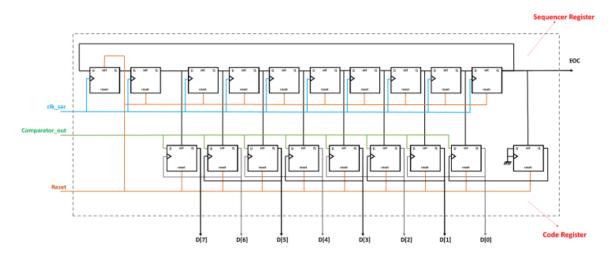

| Figure 36: Schematic of the sequence/code register SAR logic                                                                                                | 34  |

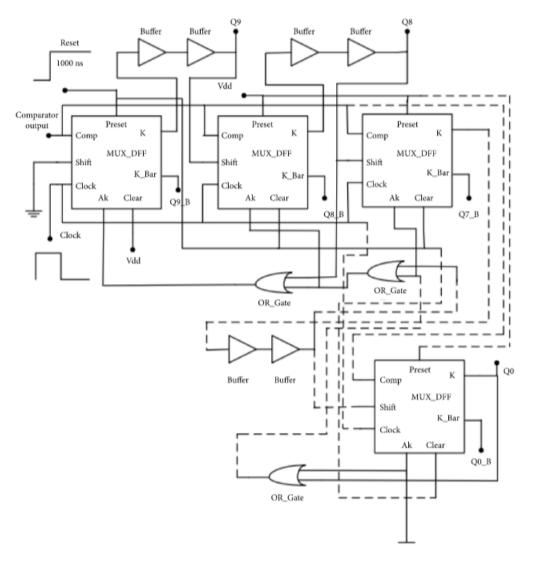

| Figure 37: Schematic of the nonredundant register SAR logic                                                                                                 | 35  |

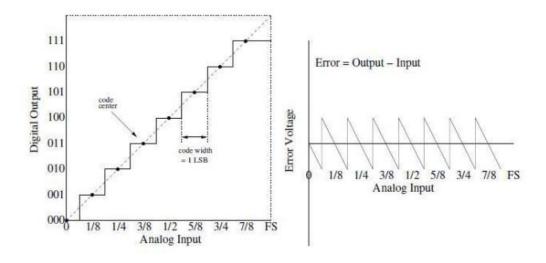

| Figure 38: Quantization error of an ideal ADC, borrowed from                                                                                                | 43  |

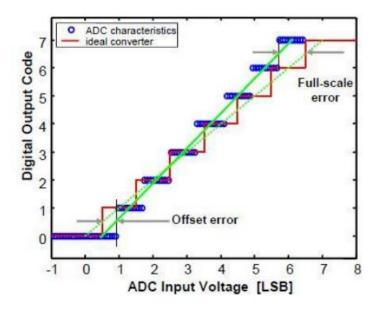

| Figure 39: Offset and full scale error                                                                                                                      | 44  |

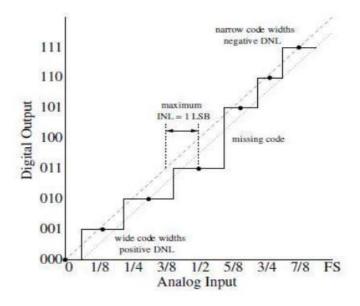

| Figure 40: DNL and maximum INL, borrowed from                                                                                                               | 44  |

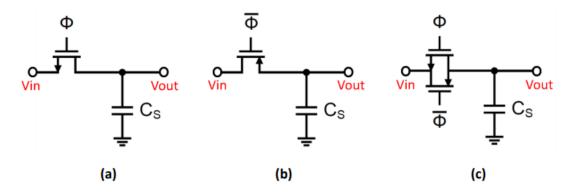

| Figure 41: Basic sampling circuits (a) NMOS switch, (b) PMOS switch, (c) CM Transmission gate                                                               |     |

| Figure 42. Non-idealities in MOSFET switches (a) input-dependent R <sub>ON</sub> , (b) Charge inject (c) Clock feedthrough.                                 |     |

| Figure 43: Basic bootstraped switch                                                                                                                         | 47  |

| Figure 44: The double bootstrap circuit                                                                                                                     | 48  |

| Figure 44: Capacitive DAC for a 3-bit SAR ADC                                                                                                               | 49  |

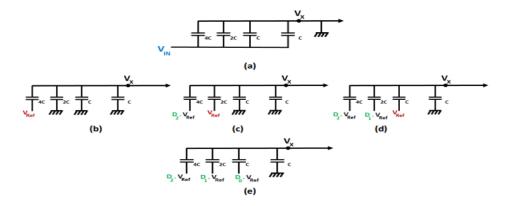

| Figure 45: Node voltages of the DAC capacitors for each stage (a) Sampling phase, Comparison 1, (c) Comparison 2, (d) Comparison 3, (e) Final binary output | , , |

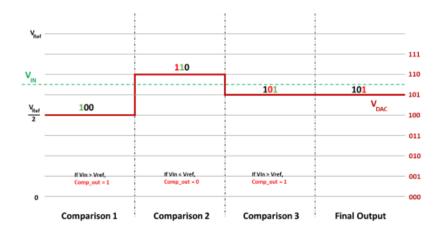

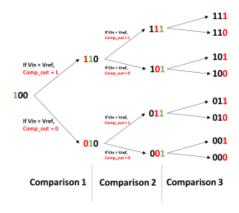

| Figure 46: Binary search process in the 3-bit SAR system                                                                                                    | 51  |

| Figure 47: Binary tree showing all the possible outputs of a 3-bit SAR ADC                                                                                  | 51  |

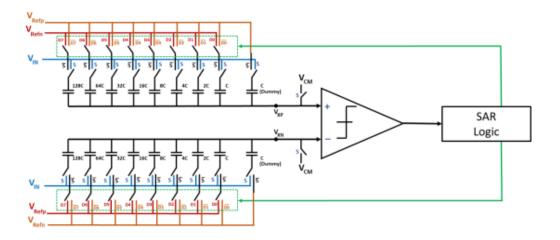

| Figure 48: Differential capacitive DAC of an 8-bit SAR ADC                                                                                                  | 52  |

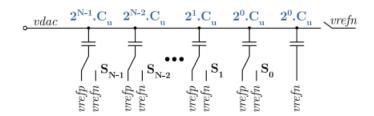

| Figure 49: Binary-weighted capacitive array                                                                                                                 | 53  |

| Figure 50: Split-capacitor array                                                                                                                            | 53  |

| Figure 51: Practical implementation of split capacitor Array                                                                                                | 53  |

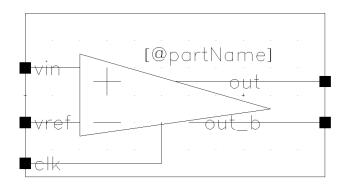

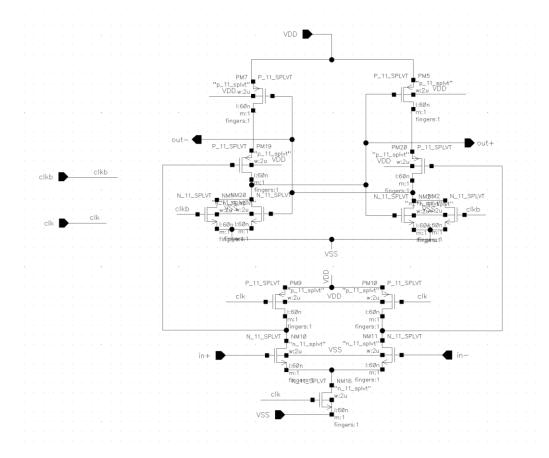

| Figure 52: Comparator Schematic                                                                                                                             | 55  |

| Figure 53: Block diagram of the SAR Logic                                                                                                                   | 58  |

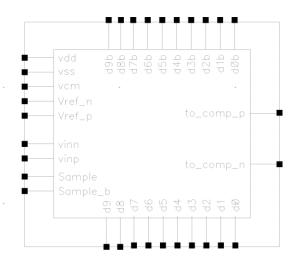

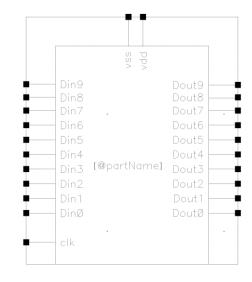

| Figure 54: Sample and hold symbol                                                                                                                           | 62  |

| Figure 55: Comparator symbol                                                                                                                                | 63  |

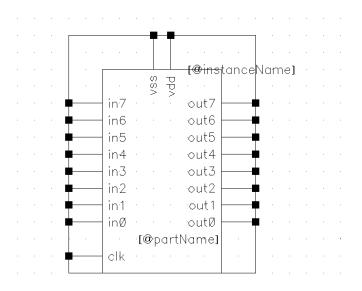

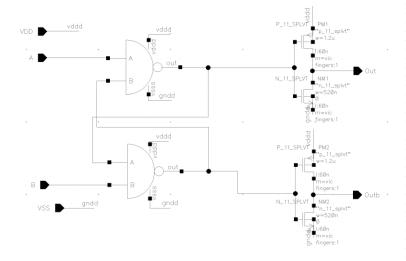

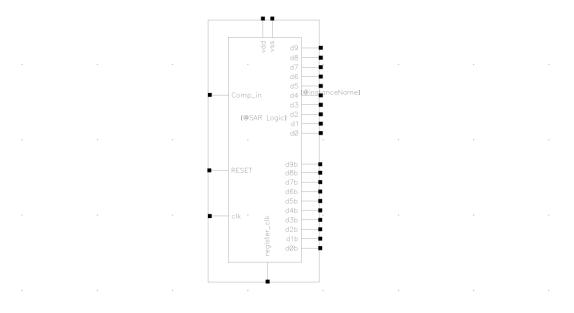

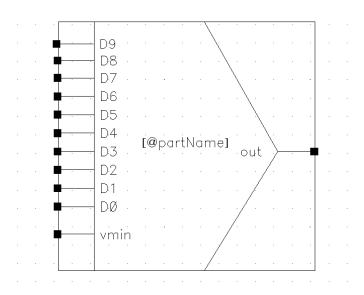

| Figure 56: SAR Output Register                                                                                                                              | 65  |

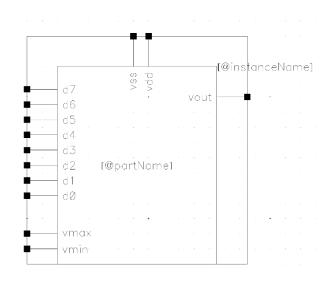

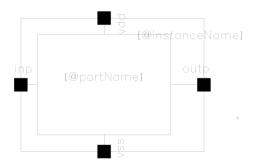

| Figure 57: DAC Symbol                                                                                                                                       | 66  |

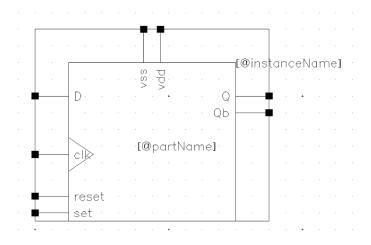

| Figure 58: D-FF symbol.                                                                                                                                     | 68  |

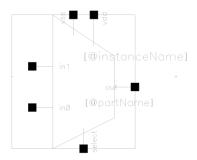

| Figure 59: Not Gate Symbol                                                                                                                                  | 69  |

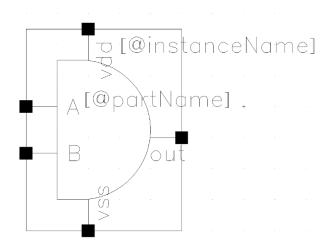

| Figure 60: XOR Gate symbol.                                                                                    | 70 |

|----------------------------------------------------------------------------------------------------------------|----|

| Figure 61: AND Gate Symbol                                                                                     | 71 |

| Figure 62: MUX Symbol                                                                                          | 72 |

| Figure 63: Delay call symbol                                                                                   | 73 |

| Figure 64: Clock generator circuit.                                                                            | 74 |

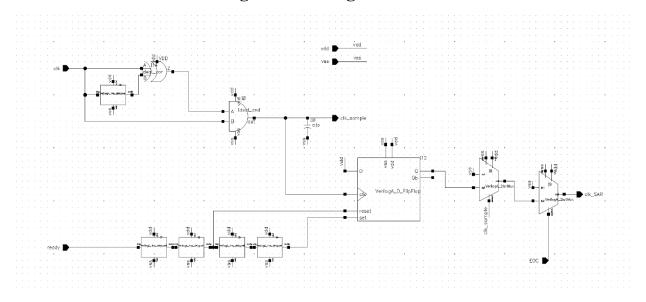

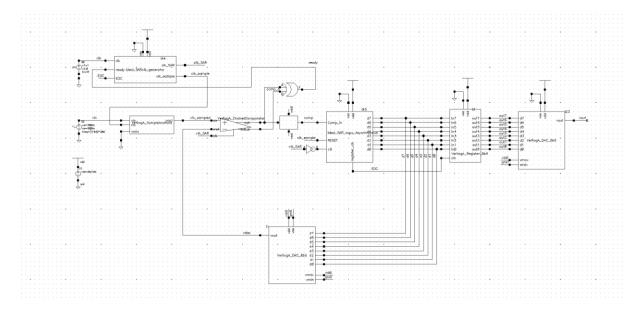

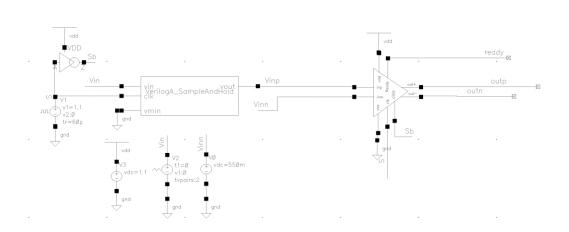

| Figure 66: Asynchronous SAR ADC circuit using VerilogA                                                         | 74 |

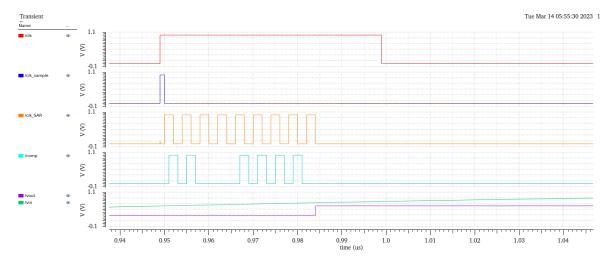

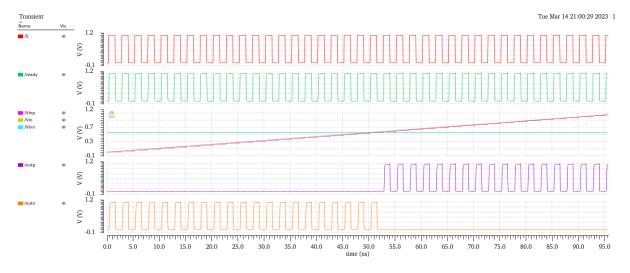

| Figure 67: Transient Waveforms of the ideal asynchronous SAR ADC testbench                                     | 74 |

| Figure 68: 1 conversion cycle for the asynchronous SAR ADC                                                     | 74 |

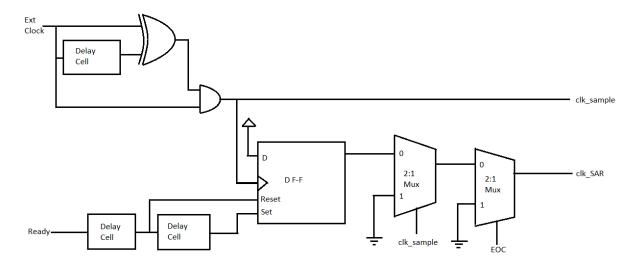

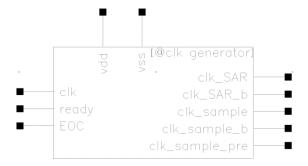

| Figure 69: Block diagram of clock generator circuit.                                                           | 75 |

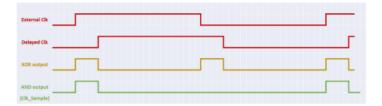

| Figure 70: Timing diagram for "clk_sample" generation circuit                                                  | 75 |

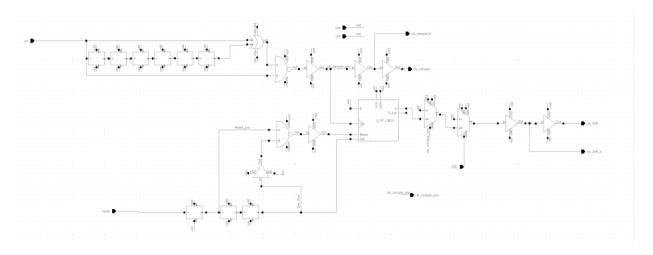

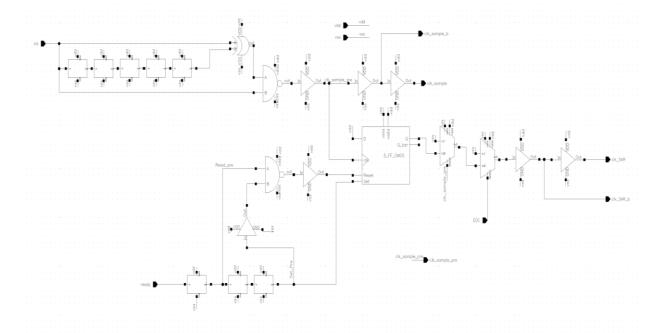

| Figure 71: Schematics of the circuit implementation of the internal clock generator                            | 76 |

| Figure 72: Digital gates used in the internal clock generator block (a) NAND, (b) Inverted 2-to-1 Mux, (d) XOR |    |

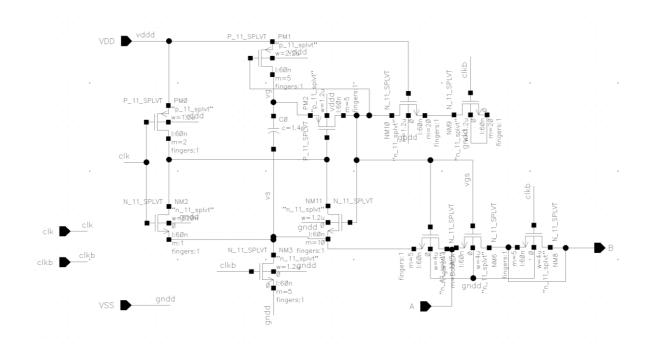

| Figure 73: Delay Cell circuit implementation                                                                   | 77 |

| Figure 74: The bootstrapped circuit                                                                            | 78 |

| Figure 75: Bootstrapped switch testbench                                                                       | 79 |

| Figure 76: Bootstrapped Switch Design Variables                                                                | 79 |

| Figure 77: Transient Waveforms of the bootstrapped switch testbench                                            | 79 |

| Figure 78: 1 cycle of the input to the bootstrapped switch                                                     | 80 |

| Figure 79: Block Diagram of the Dynamic Comparator                                                             | 80 |

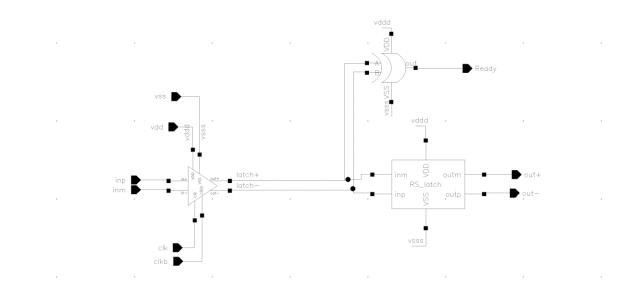

| Figure 80: Two Stage Dynamic Comparator                                                                        | 81 |

| Figure 81: R-S Latch circuit.                                                                                  | 81 |

| Figure 82: Sample and hold circuit testbench                                                                   | 82 |

| Figure 83: Design variables for Comparator                                                                     | 82 |

| Figure 84: Comparator Test-bench Wave                                                                          | 82 |

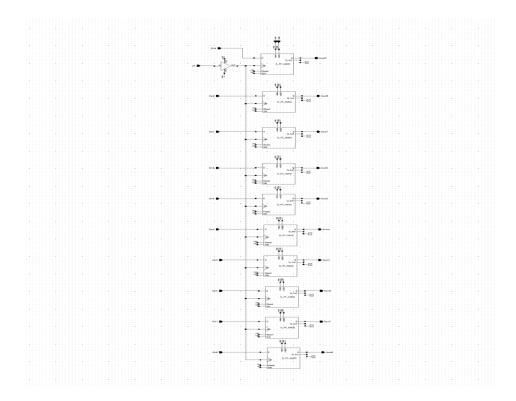

| Figure 85: Binary weighted capacitive DAC                                                                      | 83 |

| Figure 86: Testbench for the capacitive DAC                                                                    | 83 |

| Figure 87: Transient waveforms of the capacitive DAC testbench                                                 | 84 |

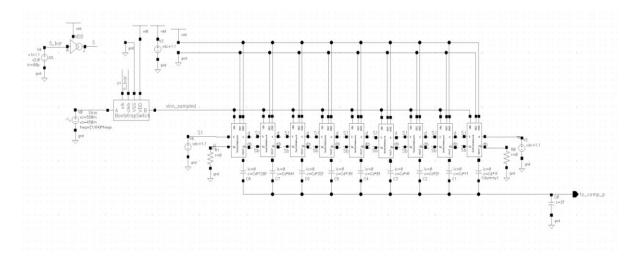

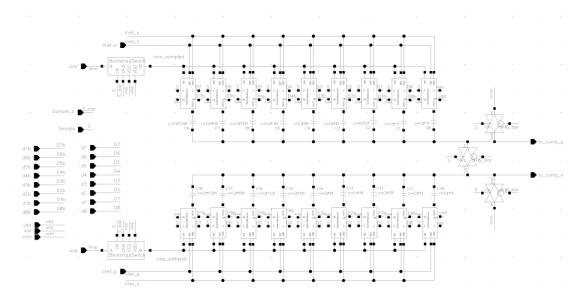

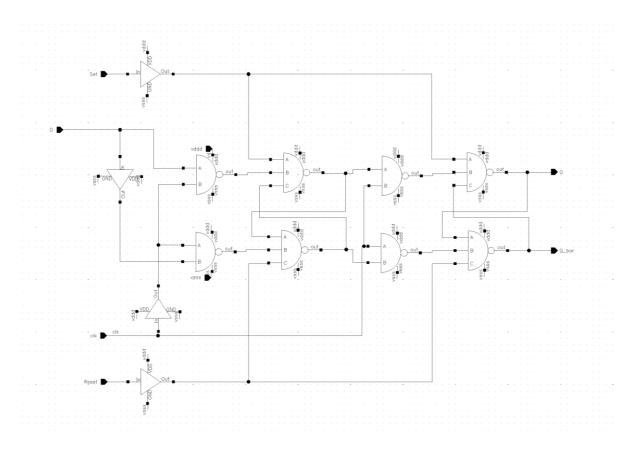

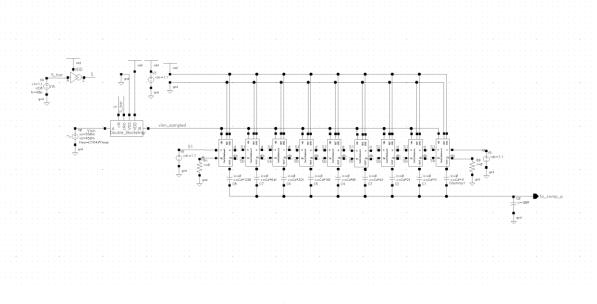

| Figure 88: 8-bit SAR Logic schematic                                                                           | 84 |

| Figure 89: SAR Logic Testbench setup                                                                           | 85 |

| Figure 90(a): Transient waveforms of the capacitive DAC testbench (Cin = 0V)                                   | 85 |

| Figure 90(b): Transient waveforms of the capacitive DAC testbench (Cin = 1.1V)                                 | 85 |

| Figure 91: Schematics of the output register                                      | 86   |

|-----------------------------------------------------------------------------------|------|

| Figure 92: CMOS D-Flip Flop.                                                      | 87   |

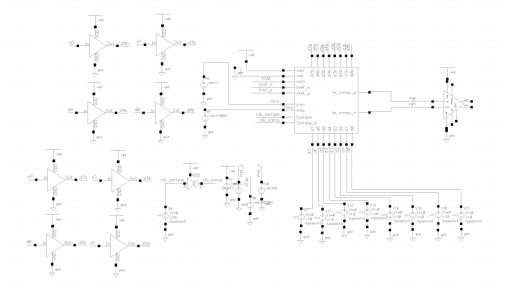

| Figure 93: Testbench of the whole asynchronous SAR ADC                            | 87   |

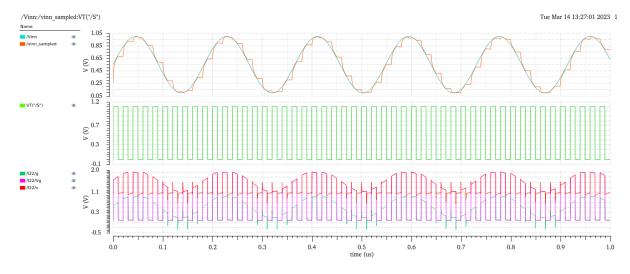

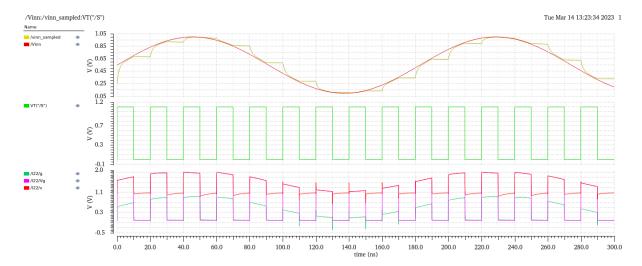

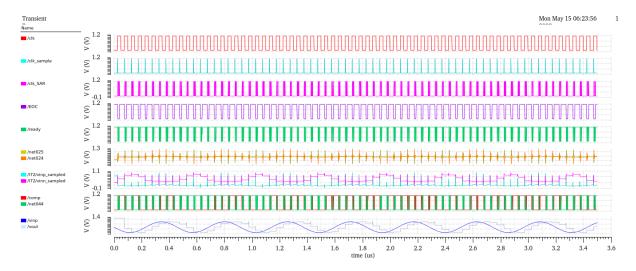

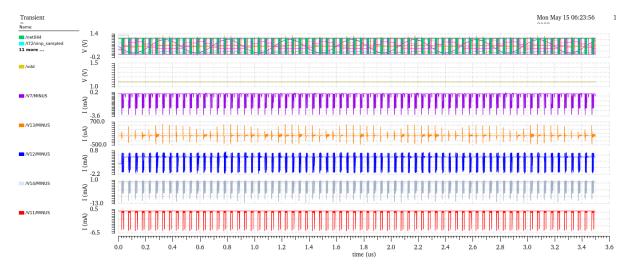

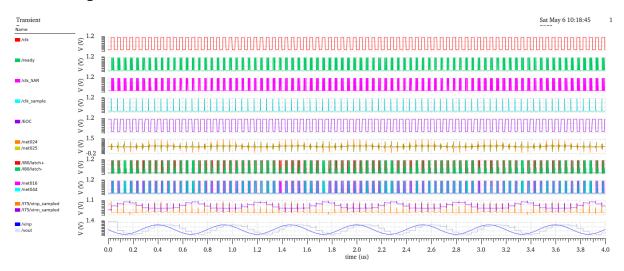

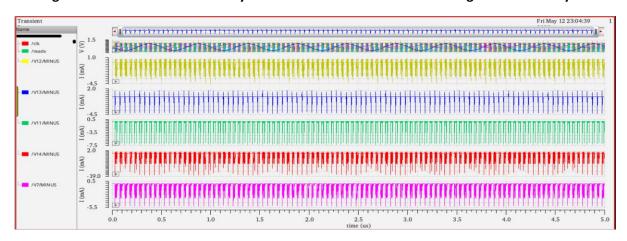

| Figure 94: Transient waveforms of the asynchronous SAR ADC testbench              | 88   |

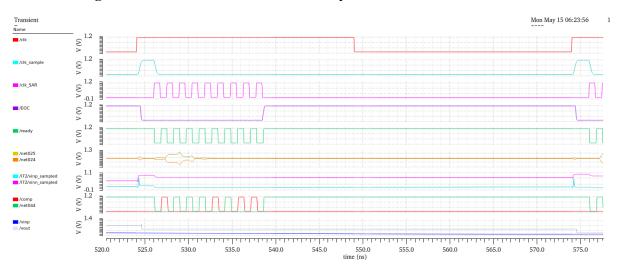

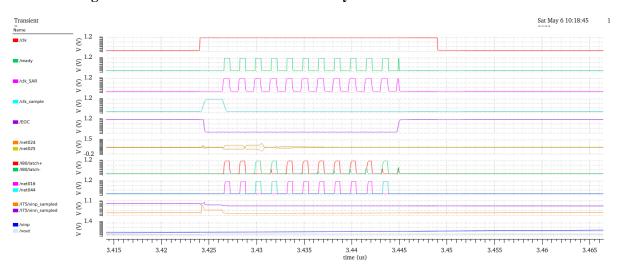

| Figure 95: Waveforms of the asynchronous SAR ADC testbench during 1 cecycle       |      |

| Figure 96: Waveform of the current drawn by each circuit of the SAR ADC           | 88   |

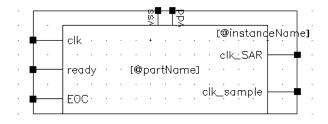

| Figure 97: Block Diagram of Clock Generator                                       | 91   |

| Figure 98: Clock Generator Symbol                                                 | 91   |

| Figure 99: Circuit Diagram of Double bootstrapped switch                          | 92   |

| Figure 100: Block Diagram of Bootstrapped Switch                                  | 92   |

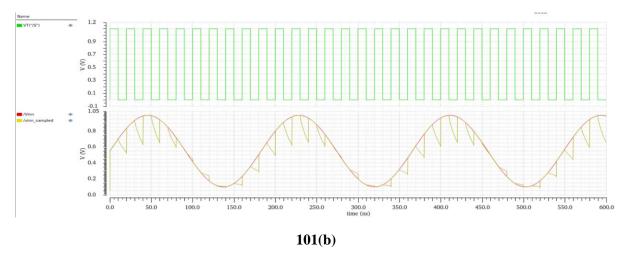

| Figure 101: Bootstrapped Switch testbench setup. (a) Circuit (b) Waveform         | 93   |

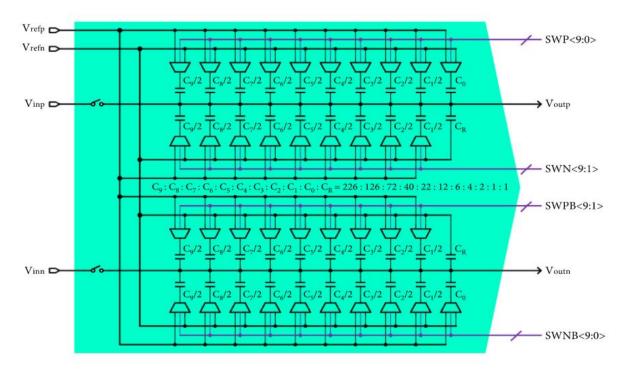

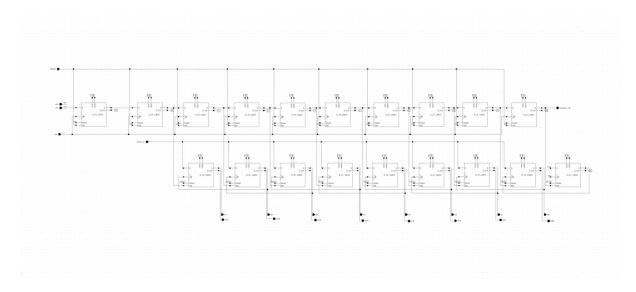

| Figure 102: Circuit Diagram of Split-Capacitor DAC                                | 93   |

| Figure 103: Block Diagram of DAC                                                  | 94   |

| Figure 104: Testbench Setup for DAC                                               | 94   |

| Figure 105: Transient waveforms of the capacitive DAC testbench                   | 94   |

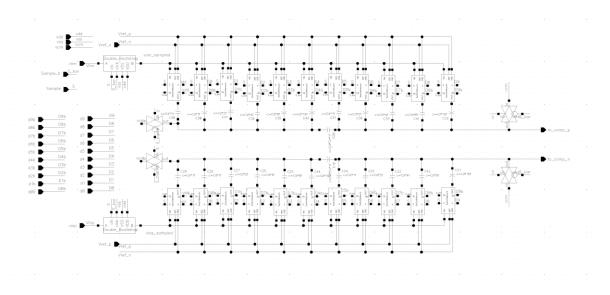

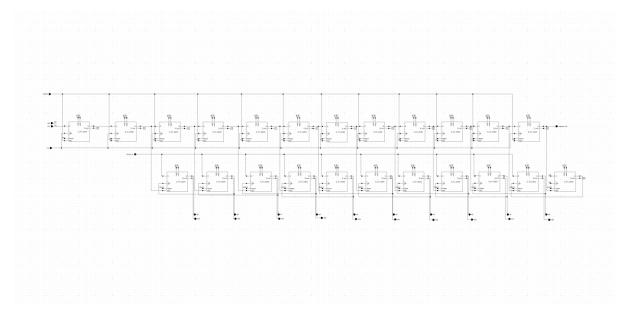

| Figure 106: 10-bit SAR Logic schematic                                            | 95   |

| Figure 107: SAR Logic Symbol.                                                     | 95   |

| Figure 108: SAR Output Register                                                   | 96   |

| Figure 109: SAR Register Symbol.                                                  | 96   |

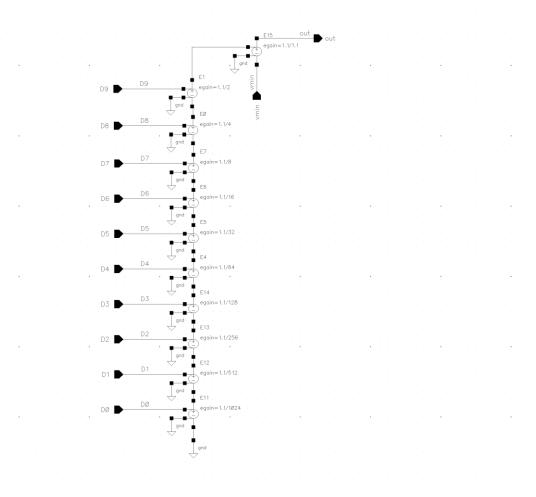

| Figure 110: 10-bit Ideal output DAC                                               | 97   |

| Figure 111: Ideal DAC Symbol                                                      | 97   |

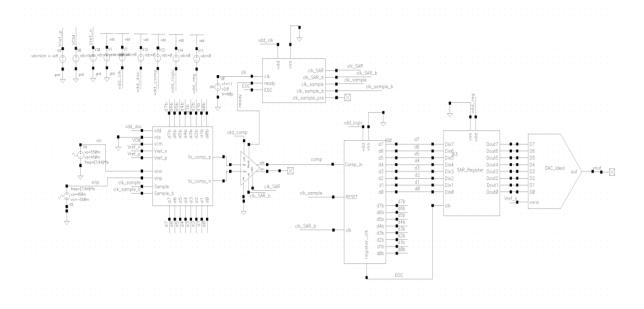

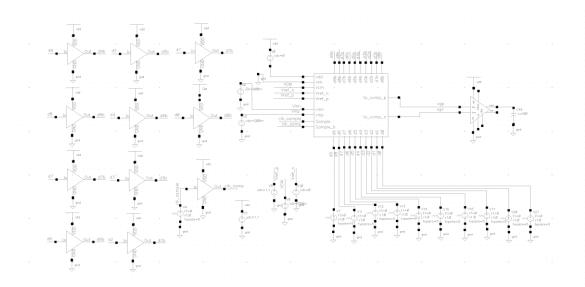

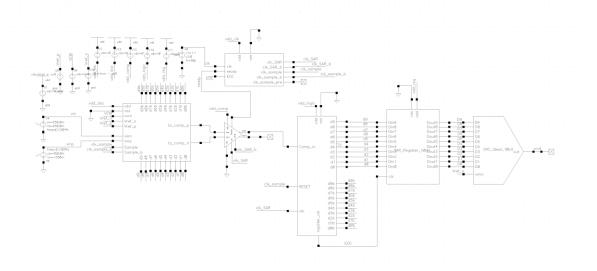

| Figure 112 (a): Testbench of the whole asynchronous SAR ADC, (b): Design Variable | es98 |

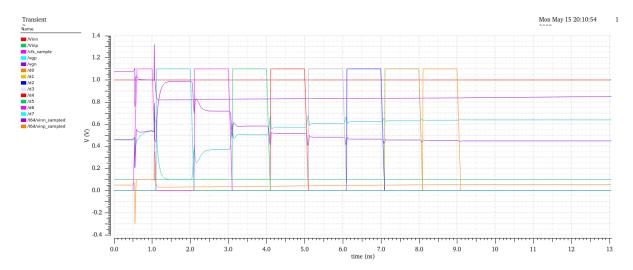

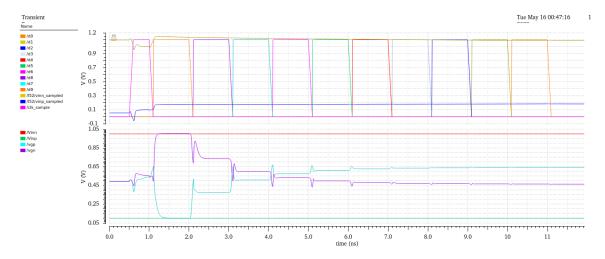

| Figure 113: Transient waveforms of the asynchronous SAR ADC testbench             | 99   |

| Figure 114: Waveforms of the asynchronous SAR ADC testbench during 1 cocycle      |      |

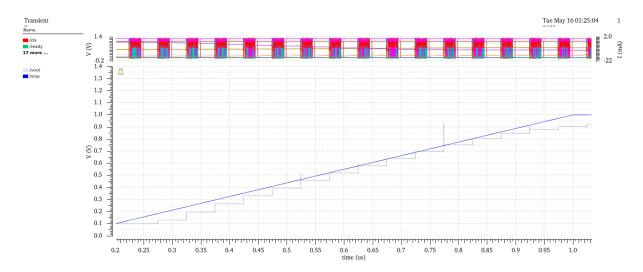

| Figure 115: Current consumption for each block                                    | 99   |

| Figure 116: Transient response of the ADC for a Ramp Signal                       | 100  |

#### **CONTENTS**

| Acknowledgn    | nent                                                    | V    |

|----------------|---------------------------------------------------------|------|

| Abstract       |                                                         | VI   |

| List of Figure | s                                                       | VIII |

| CHAPTER 1      | . Introduction                                          |      |

| Section 1.1    | Overview                                                | 1    |

| Section 1.2    | Types of ADCs                                           | 1    |

| Section 1.3    | Comparison between SAR ADC and other ADC architectures  | 2    |

| Section 1.4.   | Application of SAR ADC in Neuromorphic Chips            | 3    |

| Section 1.5    | Event Based SAR ADC                                     | 3    |

| CHAPTER 2      | 2. Literature Review                                    |      |

| Section 2.1    | Chapter Overview                                        | 5    |

| Section 2.2    | Overview of ADC Architectures                           | 6    |

| Section 2.3    | SAR Sample and Hold Circuit                             | 9    |

| Section 2.4    | Different Configuration of Dynamic Comparator           | 11   |

| Section 2.4.1  | Single-Stage Dynamic Latch Comparator                   | 11   |

| Section 2.4.2  | Two-Stage Dynamic Latch Comparator                      | 13   |

| Section 2.4.3  | Three-Stage Dynamic Latch Comparator                    | 14   |

| Section 2.4.4  | Multistage Preamplifier Dynamic Latch Comparator        | 14   |

| Section 2.5    | SAR CDAC Architecture                                   | 15   |

| Section 2.5.1  | Capacitive DAC Array (CDAC)                             | 16   |

| Section 2.5.2  | CDAC Voltage Switching Schemes                          | 27   |

| Section 2.6    | SAR Register and its Control Logic                      | 32   |

| Section 2.7    | Summary of the Published SAR ADC Performance Parameters | 36   |

| Section 2.8    | Conclusion                                              | 42   |

| CHAPTER 3      | 3. SAR ADC Principles                                   |      |

| Section 3.1 A  | nalog to Digital Conversion fundamentals                | 43   |

| Section 3.1.1 Resolution                                | 43 |

|---------------------------------------------------------|----|

| Section 3.1.2 Quantization Error                        | 43 |

| Section 3.2 Static Performance                          | 43 |

| Section 3.2.1 Offset and Full-Scale Error               | 43 |

| Section 3.2.2 Differential Nonlinearity                 | 44 |

| Section 3.2.3 Integral Nonlinearity                     | 44 |

| Section 3.2.4 Missing Code                              | 45 |

| Section 3.3 Dynamic Performance                         | 45 |

| Section 3.3.1 Signal-to-Noise Ratio                     | 45 |

| Section 3.3.2 Spurious-Free Dynamic Range               | 45 |

| Section 3.3.3 Signal-to-Noise-and-Distortion Ratio      | 45 |

| Section 3.3.4 Effective Number of Bits                  | 45 |

| Section 3.4.1 Bootstrapped Sample-And-Hold Circuit      | 46 |

| Section 3.4.2 Double Bootstrap circuit                  | 48 |

| Section 3.5 Capacitive DAC                              | 49 |

| Section 3.5.1 Single-ended capacitive DAC               | 49 |

| Section 3.5.2 Differential SAR Architecture             | 51 |

| Section 3.5.3 Split binary-weighted capacitive array    | 52 |

| Section 3.6 Comparator                                  | 55 |

| Section 3.6.1 Two Stage Dynamic Comparator              | 55 |

| Section 3.6.2 Equivalent Input Noise of the First Stage | 55 |

| Section 3.7 SAR logic                                   | 57 |

| Section 3.8 Output DAC                                  | 58 |

| Section 3.9 Specifications for the Design               | 59 |

| CHAPTER 4.                                              |    |

| Section 4.1 Implementation of SAR ADC                   | 61 |

| Section 4.2 Design of an 8-Bit SAR ADC in VerilogA      | 61 |

| Section 4.2.1 Sample-And-Hold Code:                     | 61 |

| Section 4.2.2 Clocked Comparator:                       | 62 |

| Section 4.2.3 Output Register 8- bit                         | 63  |

|--------------------------------------------------------------|-----|

| Section 4.2.4 DAC (8 bit )                                   | 65  |

| Section 4.2.5 D-Flipflop.                                    | 66  |

| Section 4.2.6 Inverter Gate                                  | 68  |

| Section 4.2.7 XOR Gate                                       | 69  |

| Section 4.2.8 AND Gate                                       | 70  |

| Section 4.2.9 Multiplexer (2-to-1).                          | 71  |

| Section 4.2.10 Delay Cell (1ns)                              | 72  |

| Section 4.2.11 Clock Generator using ideal VerilogA blocks   | 73  |

| Section 4.2.12 Complete SAR ADC Block using VerilogA         | 74  |

| Section 4.3 Design of an 8-bit SAR ADC                       | 75  |

| Section 4.3.1 Internal Clock Generator                       | 75  |

| Section 4.3.2 The bootstrapped Circuit                       | 78  |

| Section 4.3.3 The Comparator Circuit                         | 80  |

| Section 4.3.4 Capacitive DAC                                 | 82  |

| Section 4.3.5 SAR Logic                                      | 84  |

| Section 4.3.6 Output Register                                | 86  |

| Section 4.3.7 Whole Asynchronous SAR ADC system              | 87  |

| Section 4.4 Design of 10-bit SAR ADC                         | 91  |

| Section 4.4.1 Clock Generator Circuit                        | 91  |

| Section 4.4.2 Double Bootstrapped Switch                     | 93  |

| Section 4.4.3 Split Capacitive DAC                           | 93  |

| Section 4.4.4 SAR Logic                                      | 95  |

| Section 4.4.5 Output Register                                | 95  |

| Section 4.4.6 Ideal Output DAC                               | 97  |

| Section 4.4.7 Complete Asynchronous 10-bit SAR ADC Testbench | 98  |

| Section 4.4.8 Output of the 10-bit SAR                       | 99  |

| Conclusion and Future Works.                                 | 103 |

| Bibliography                                                 | 105 |

#### Chapter 1

#### Introduction

#### 1.1 Overview

The increasing demand for solutions in disease diagnosis and treatment has led to a growing need for advancements in medical and healthcare systems. Biomedical applications, such as medical implants and wireless sensors, have emerged as critical tools for long-term patient monitoring without imposing significant limitations [1–4]. Figure 1 illustrates the architecture of a wireless body sensor network (WBSN) [5]. This network comprises wireless sensors strategically placed inside, or around the human body to monitor vital body parameters and movements. The collected biomedical data from these nodes needs to be wirelessly transmitted to a base station. Hence, the analog-to-digital converter (ADC) plays a crucial role in converting analog biomedical signals into a digital format suitable for storage and processing. Given that these nodes operate on portable battery-powered devices, there is a need for energy-efficient integrated circuit designs. It is evident that minimizing power consumption is a critical challenge in wireless biomedical applications due to limited battery life [6]. The ADC serves as a fundamental component by acting as an interface between the analog domain and digital processing domain.

#### 1.2 Types of ADCs

There are several ADC architectures available in the market that serve different purposes and have their own advantages and disadvantages. Some of the commonly used ADC architectures are Delta-Sigma, Flash, Pipeline, and Dual-Slope ADCs. Here's a comparison of SAR ADC with other ADC architectures:

- Delta-Sigma ADC: Delta-Sigma ADCs are known for their high resolution capabilities

and low noise, making them ideal for high-precision applications. However, they have

a slow conversion rate and require more power than SAR ADCs. In contrast, SAR

ADCs have a higher conversion rate, consume less power, and have a simpler

architecture, but may not provide the same level of resolution and noise performance

as Delta-Sigma ADCs.

- 2. Flash ADCs have a fast conversion rate, but they require a large number of comparators, which can increase the power consumption and cost of the system. Flash ADCs also have limited resolution capabilities and can only achieve resolutions up to 8 bits, while SAR ADCs can achieve resolutions up to 16 bits.

- 3. Pipeline ADC: Pipeline ADCs are known for their high speed and high-resolution capabilities, but they require more power than SAR ADCs. Pipeline ADCs also have a more complex architecture, making them harder to design and implement.

- 4. Dual-Slope ADC: Dual-Slope ADCs are known for their high accuracy and low cost, but they have a slow conversion rate and are sensitive to noise and temperature

variations. SAR ADCs have a higher conversion rate, consume less power, and have a simpler architecture, but may not provide the same level of accuracy as Dual-Slope ADCs.

Overall, each ADC architecture has its own set of advantages and disadvantages, and the choice of ADC architecture depends on the specific requirements of the application. SAR ADCs are a popular choice due to their high speed, low power consumption, reasonable resolution capabilities, and simple architecture, making them ideal for portable and low-power devices where power consumption is a critical concern.

#### 1.3 Comparison between SAR ADC and other ADC architectures

SAR ADC is often considered the best choice for many applications:

- 1. Delta-Sigma ADC: Delta-Sigma ADCs offer high resolution and low noise, making them ideal for high-precision applications. However, they require a complex architecture, have a slower conversion rate, and consume more power than SAR ADCs. Delta-Sigma ADCs are often used in applications where high accuracy is required, such as medical equipment and instrumentation. In contrast, SAR ADCs offer a faster conversion rate, consume less power, and have a simpler architecture, making them a better choice for applications that require lower resolution and faster sampling rates.

- 2. Flash ADC: Flash ADCs offer fast conversion rates but require a large number of comparators, which can increase power consumption and cost. Flash ADCs are often used in applications that require low resolution and fast sampling rates, such as video and audio processing. In contrast, SAR ADCs offer a higher resolution, consume less power, and have a simpler architecture, making them a better choice for applications that require higher resolution and lower power consumption.

- 3. Pipeline ADC: Pipeline ADCs offer high resolution and high speed, but require more power and have a more complex architecture than SAR ADCs. Pipeline ADCs are often used in applications that require high resolution and high-speed sampling rates, such as imaging and wireless communication. In contrast, SAR ADCs offer a simpler architecture, consume less power, and provide reasonable resolution capabilities, making them a better choice for applications that require a balance between resolution and power consumption.

- 4. Dual-Slope ADC: Dual-Slope ADCs offer high accuracy and low cost but have a slow conversion rate and are sensitive to noise and temperature variations. Dual-Slope ADCs are often used in applications that require high accuracy but can tolerate slower sampling rates, such as temperature sensing and industrial process control. In contrast, SAR ADCs offer a faster conversion rate, consume less power, and have a simpler architecture, making them a better choice for applications that require a balance between speed, resolution, and power consumption.

#### 1.4 Application of SAR ADC in Neuromorphic Chips

SAR (Successive Approximation Register) ADCs (Analog-to-Digital Converters) are widely used in neuromorphic vision chips due to their high precision and low power consumption. Neuromorphic vision chips are designed to mimic the structure and function of the human visual system, and require high-speed and high-resolution ADCs to convert analog signals from photoreceptors into digital signals for processing.

One of the main challenges in designing neuromorphic vision chips is achieving high resolution while maintaining low power consumption. SAR ADCs are well-suited for this task, as they are able to achieve resolutions of up to 24 bits while consuming very little power.

SAR ADCs are also able to operate at high speeds, which is important in neuromorphic vision chips where real-time processing is required. The fast conversion time of SAR ADCs enables them to capture and process visual information at a high rate, allowing the chip to respond quickly to changes in the environment.

Another advantage of SAR ADCs is their ability to perform accurate and precise conversions even in the presence of noise. Neuromorphic vision chips often operate in noisy environments, and SAR ADCs are able to filter out unwanted noise and provide accurate digital representations of the visual signal.

SAR ADCs are commonly used in neuromorphic vision chips to convert the output of photoreceptors into digital signals that can be processed by the neural network. The high precision and low power consumption of SAR ADCs make them an ideal choice for this application.

In addition to photoreceptor conversion, SAR ADCs are also used in neuromorphic vision chips to convert the output of the neural network back into analog signals for control of actuators such as motors and servos.

In summary, SAR ADCs are an important component of neuromorphic vision chips due to their ability to achieve high resolution and operate at high speeds while consuming very little power. Their ability to filter out noise and provide accurate digital representations of the visual signal make them an ideal choice for use in these types of systems.

#### 1.5 Event Based SAR ADC

Event-based SAR (Successive Approximation Register) ADCs (Analog-to-Digital Converters) are a type of ADC that have been developed specifically for use in event-based neuromorphic systems. Event-based neuromorphic systems are designed to mimic the function of the brain, which processes information in an asynchronous, event-driven manner.

Traditional ADCs sample the input signal at a fixed rate and convert the signal into a series of digital values. However, in event-based systems, this approach is not practical, as the input signal may contain long periods of inactivity, which wastes power and reduces the efficiency of the system.

Event-based SAR ADCs overcome this issue by only sampling the input signal when a significant change in the signal is detected. This is achieved using an event-based architecture, where the ADC only operates when an event occurs, and the output of the ADC is generated in response to that event.

Event-based SAR ADCs operate by monitoring the input signal for changes and generating a digital output only when a significant change is detected. The ADC only consumes power when a change occurs, which reduces the overall power consumption of the system.

The output of the ADC is generated using a successive approximation register, which performs a binary search to determine the digital value that best represents the input signal. The SAR ADC can achieve high precision even with a low sampling rate, which further reduces the power consumption of the system.

Event-based SAR ADCs are commonly used in neuromorphic vision and audio systems, where the input signal is highly dynamic and asynchronous. In these systems, the ADC can sample the input signal only when a significant change occurs, which reduces the power consumption of the system and allows it to operate more efficiently.

In summary, event-based SAR ADCs are a type of ADC that have been developed specifically for use in event-based neuromorphic systems. Their event-driven architecture and low power consumption make them well-suited for use in vision and audio systems, where the input signal is highly dynamic and asynchronous.

#### Chapter 2

#### **Literature Review**

#### 2.1 Chapter Overview

In recent years, there has been a growing interest in the successive approximation register (SAR) ADC, particularly for its application in biomedical fields [13]. This chapter aims to review and analyze various techniques proposed for low-power SAR ADCs in the past five years, focusing on their suitability for biomedical applications. The goal is to provide researchers in the field of energy-efficient SAR ADC design with a comprehensive understanding of the key components and different implementation schemes.

This survey offers the following contributions:

- i. A comprehensive examination of different single SAR ADC implementations, highlighting their respective advantages, disadvantages, and challenges associated with each component.

- ii. Investigation of various optimization techniques employed to reduce power consumption in SAR ADCs, based on a thorough analysis of numerous publications from 2017 to 2022.

- iii. Clear comparisons of different single SAR ADC techniques across various CMOS technologies, enabling researchers to make informed design choices.

- iv. Detailed analysis and discussion of results based on key performance metrics such as power consumption, resolution, speed, and linearity. This information is presented through tables and figures for easy reference and comparison.

The subsequent sections are structured as follows: Section 2.2 provides an overview of the SAR ADC architecture, outlining its fundamental operation. Section 2.3 explores the various approaches to sample and hold switching, discussing their characteristics and trade-offs. Section 2.4 presents different configurations of the dynamic comparator, highlighting their strengths and limitations. The architectures of the capacitor digital-to-analog converter (CDAC) are discussed in Section 2.5, with a focus on their design considerations. Section 2.6 delves into the SAR register and its control logic, explaining their role in the conversion process. A summary of recent performance parameters for SAR ADCs is presented in Section 2.7, offering a comprehensive overview of the state-of-the-art in the field. Finally, concluding remarks are provided in Section 2.8, summarizing the key findings and potential future research directions.

#### 2.2 Overview of SAR ADC Architecture

#### **SAR ADC Architecture**

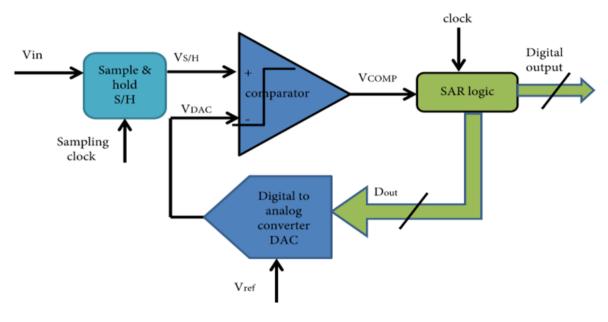

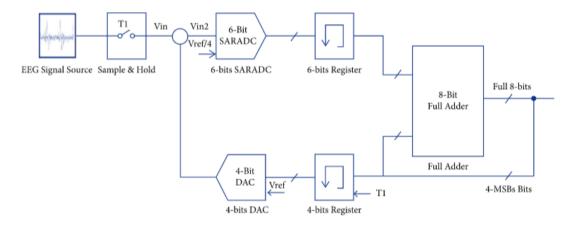

In this section, we will provide a comprehensive overview of the architecture of a Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) and highlight its advantages compared to other types of ADCs. The basic implementation of a SAR ADC is illustrated in Figure 2, which depicts the key components involved in the conversion process.

These components include a Sample-and-Hold (S/H) switch, an internal Digital-to-Analog Converter (DAC), a comparator, and successive approximation logic.

The operation of a Successive Approximation Register Analog-to-Digital Converter (SAR ADC) commences by sampling the input signal through the Sample-and-Hold (S/H) switch. Subsequently, the digital code stored in a register is converted into an analog value by an internal Digital-to-Analog Converter (DAC). This analog value is then compared to the sampled signal voltage using a comparator, generating a digital output. The digital output guides the successive approximation logic to update the code stored in the register. Initially, the most significant bit (MSB) is presented in digital form and converted into an analog value for comparison with the input signal.

Throughout the conversion process, the comparator output determines the next bit to be determined. If the comparator output is high (1), indicating that the input signal voltage (Vin) is greater than half of the reference voltage (Vref/2), the MSB remains stored in the SAR register, and a high bit is loaded into the next bit position. Conversely, if Vref/2 < Vin, the comparator output will be low (0). This prompts the control circuit to write a low bit to the current bit position and a high bit to the next bit position. This iterative process continues, determining each bit from the MSB to the least significant bit (LSB), until all N required bits are determined.

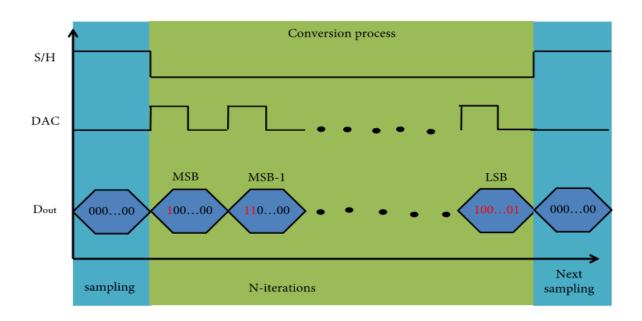

The Figure 3 shows clock and timing of the SAR ADC, illustrating the two main phases of operation: the sampling process and the conversion process. During the conversion process, each bit is determined sequentially following the described procedure, resulting in the final digital representation of the input signal.

By understanding the architecture and operation of a SAR ADC, we gain insight into its advantages and suitability for various applications. The SAR ADC offers high resolution, excellent linearity, and low power consumption, making it a popular choice in many signal processing systems.

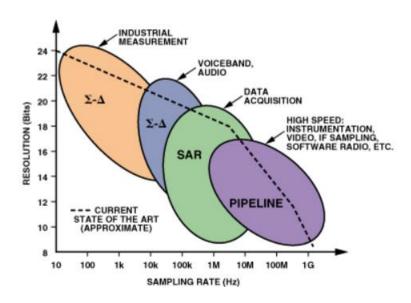

Figure 1: ADC architectures, applications, resolution, and sampling rates.

Figure 2: The SAR ADC Block diagram (Source: Hindawai.com)

Figure 3: The SAR ADC Clock and timing profile(Source: Hindawai.com)

Primary advantage of a SAR ADC in comparison to other types of ADCs, is its ability to achieve low power consumption. This characteristic makes SAR ADCs highly desirable for various applications. In this thesis, we will explore and demonstrate various methods employed to further reduce power consumption in SAR ADCs.

The working principle of SAR (Successive Approximation Register) ADC involves a series of comparisons to determine the digital output of the analog input signal. Here are the basic steps involved in the working of a SAR ADC:

- 1. Sample and Hold: The input analog voltage is sampled and held by a Sample and Hold (S/H) circuit. The S/H circuit holds the input voltage constant during the conversion process.

- 2. Binary Search: The SAR ADC uses a binary search technique to determine the digital output of the analog input signal. The SAR ADC starts with the MSB (Most Significant Bit) and compares the input voltage with the midpoint of the DAC (Digital to Analog Converter) output voltage range. Depending on the result of the comparison, the SAR ADC sets the MSB to 1 or 0 and proceeds to the next bit.

- 3. Successive Approximation: The SAR ADC repeats the binary search process for each bit, moving from the MSB to the LSB (Least Significant Bit). Each bit is set to 1 or 0 depending on the comparison result with the DAC output voltage.

- 4. Output: Once all the bits have been determined, the digital output is available at the output of the SAR ADC.

Various configurations have been proposed for the comparator in SAR ADCs to address power consumption, time delay, and noise effects [14–24]. Additionally, modified binary-weighted capacitor digital-to-analog converter (CDAC) structures have been developed to save both area and energy [25–68]. Switching schemes for the CDAC reference voltage have also been explored to reduce power supply voltage and increase conversion speed [69–89]. Algorithmic techniques have been explored to decrease the count of iterations required for the process of conversion [90–100]. Furthermore, the SAR ADC architecture is particularly well-suited for CMOS processes [101].

However, when applied in biomedical applications, low-power SAR ADCs face several challenges. Designing a low-power, high-resolution SAR ADC becomes particularly challenging as the binary-weighted CDAC array's area increases exponentially with resolution, leading to higher power consumption and larger chip area [10]. The leakage current of the sampling switch becomes a critical consideration at low sampling frequencies, as it can introduce nonlinearity due to the extended conversion period [11]. Bit decision errors can also arise from noise sources such as the comparator, power supply, or settling time of the CDAC [12]. In the subsequent sections, we will provide a detailed explanation of the ADC components.

In wireless biomedical applications, the power consumption of Analog-to-Digital Converters (ADCs) plays a vital role in preserving battery life. These applications also have specific requirements, such as compact chip area, medium resolution, and variable sampling speeds that can range from kilo samples per second (KS/s) to mega samples per second (MS/s) [7, 8]. ADCs in these applications are expected to meet key performance parameters, including sampling frequency (FS), resolution, effective number of bits (ENOB), signal-to-noise-and-distortion ratio (SNDR), power consumption, and figure of merit (FOM). It is particularly critical to achieve higher resolution and speed simultaneously, making the ADC a crucial component in the overall design [2].

The ADC architecture plays a significant role in determining the system's performance [9]. Despite previous efforts in ADC design and implementation, developing high-speed ADCs with high resolution and low power consumption remains a challenge for biomedical applications. Therefore, adopting an energy-efficient architecture like the successive approximation register (SAR) ADC is a suitable choice for converting analog signals to digital data while meeting the low power requirements [10–12].

#### 2.3 The Sample and Hold Circuit

At the forefront of the Successive Approximation Register Analog-to-Digital Converter (SAR ADC) lies the sample and hold (S/H) circuit. The sample switch, a crucial component of the S/H circuit, faces various challenges, such as maintaining dynamic linearity, minimizing power consumption, and enhancing noise immunity. The core function of the S/H operation is to transform a continuous-time signal into a sampled or time-discrete signal, ensuring a uniform sampling period. To prevent aliasing effects, it is imperative to adhere to the Nyquist theorem when selecting the appropriate sampling frequency.

One common approach is to employ a simple sample switch utilizing an NMOS transistor [102], which offers low power consumption at a lower cost. However, this type of switch is susceptible to sub-par switching effects, nonlinearity, harmonic distortion, and noise.

The crucial problem in S/H switching is the variation of conductivity between the gate and source terminals ( $\mathbf{g}_{gs}$ ) of the sample transistor in the linear region. As the input signal changes ( $\mathbf{V}_{in}$ ), the conductivity ( $\mathbf{g}_{gs}$ ) changes (1).

$$g_{gs} = \mu C_{ox}(W/L) (V_{dd} - V_{in} - V_{Tn}),$$

(1)

where  $\mu$  is the surface mobility,

$\mathbf{c}_{ox}$  is the capacitance per unit gate area,

and  $V_{Tn}$  the threshold voltage of MOSFET.

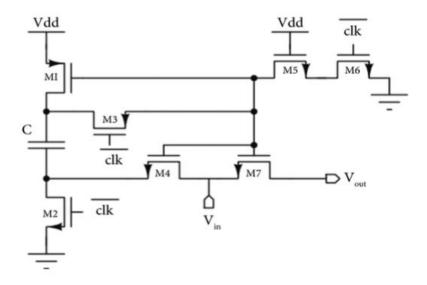

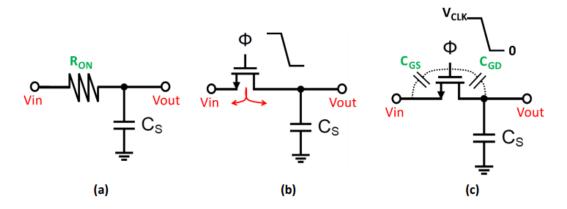

Sampled signal is subject to two common distortions: charge injection and clock feedthrough. Charge injection refers to the presence of charge between the source and drain terminals when the sample switch is turned off. Clock feedthrough, on the other hand, occurs due to the overlapping coupling capacitor between the gate and drain terminals, resulting in injected charge. To mitigate these distortions, it is best to implement the sample switch using CMOS transmission gates [8, 64, 103] or according to Figure 4 in bootstrap switch configuration [2, 5, 6, 11, 17, 22, 24, 31, 34, 45, 53, 58, 63, 65–67, 86, 90, 94, 104]. These alternative implementations help reduce the impact of charge injection and clock feedthrough, enhancing the overall performance of the sample and hold circuit.

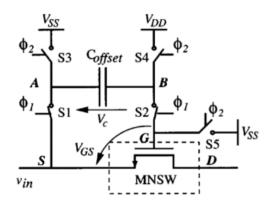

Figure 4: Conventional bootstrapped sample and hold circuit [63].

The utilization of CMOS transmission gates helps reduce conductivity variations, but it does not fully address the issue of input dependence. Furthermore, the presence of a large parasitic capacitor limits the resolution of the successive approximation register (SAR) ADC. To overcome these challenges and improve linearity while reducing power consumption, the implementation of a bootstrap switch has proven to be an effective solution [12, 23]. Figure 4 illustrates the operation of the bootstrap switch. When the complementary clock signal "(clk) is high, transistors M1 and M2 are turned on, allowing the capacitor C to charge to the supply voltage. Transistors M3, M5, and M6 are employed to isolate the capacitor C from the gate of transistor M7. Contrarily, when "(clk) not high, transistor M3 and M4 are switched on, enabling the capacitor C to discharge through the gate of M7. This configuration ensures that the conductivity remains constant and solely dependent on the supply voltage, thereby reducing nonlinearity error and voltage error caused by charge injection.

For enhanced linearity and improved common mode noise immunity, a double bootstrap switch is employed in some SAR ADC designs [12, 23]. This double bootstrap switch supports a fully differential architecture for the SAR comparator. By raising the gate-source voltage to twice the supply voltage, the double bootstrap switch achieves its objectives. Additionally, the use of a bootstrap switch followed by a dummy switch is employed to compensate for clock feedthrough [3, 4]. In this scheme, the charge injected during the conversion process is compared to the charge induced by the dummy switch.

In the context of SAR ADCs for biomedical applications, achieving power consumption of less than microwatts is a target design goal. Therefore, the bootstrap circuit is commonly adopted as the regular structure for the SAR sample and hold switch [63]. Table 1 provides a summary of different circuit schemes, highlighting the trade-off between power consumption, linearity, and noise. It can be seen that ultralow power consumption can be attained using CMOS TG [64], but at the expense of noise performance and dynamic linearity. On the other hand, the bootstrap switch offers improved linearity and noise characteristics. To further enhance

linearity, researchers have explored techniques such as the dual-path linearization technique [104], albeit with an associated increase in power consumption.

Table 1: Comparing different S/H structures.

| Structure                                                       | CMOS<br>TG  | Bootstrap<br>switch | Double<br>bootstrap<br>switch | Bootstrap switch<br>with a dummy<br>switch |

|-----------------------------------------------------------------|-------------|---------------------|-------------------------------|--------------------------------------------|

|                                                                 |             |                     |                               |                                            |

| Dynamic linearity                                               | Poor        | Good                | Very high                     | High                                       |

| Power                                                           | Very<br>low | Low                 | High                          | Mediocre                                   |

| Common-mode noise immunity                                      | Low         | Average             | High                          | High                                       |

| Distortion due to Charge<br>injection and clock feed<br>through | High        | Average             | Low                           | Very low                                   |

#### 2.4 Different Configuration of Dynamic Comparator

The role of the comparator in Successive Approximation Register Analog-to-Digital Converters (SAR ADCs) is paramount, as it facilitates the comparison between the sampled input and the voltage stored on the capacitor arrays of the Digital-to-Analog Converter (DAC). The output of the SAR comparator serves as the basis for determining the equivalent digital representation, which is subsequently fed into the SAR logic for further processing. In this section, we delve into the exploration of different SAR comparator designs, with a particular focus on strategies aimed at minimizing power consumption to meet the specific requirements of biomedical applications.

In addition to power consumption, several performance factors are considered, encompassing accuracy, speed, resolution, propagation time delay, input-referred offset voltage, supply sensitivity, and meta-stability [14].

Among the different designs, the dynamic latch comparator has been widely employed in previous works [15]. The state-of-the-art Successive Approximation Register Analog-to-Digital Converters (SAR ADCs) employ four implementation techniques: the single-stage dynamic latch with a simple structure, the two-stage dynamic latch, the three-stage dynamic latch, and the multistage preamplifier dynamic latch. These techniques represent advancements in SAR ADC design, each offering unique characteristics and performance benefits.

#### 2.4.1 Single-Stage Dynamic Latch Comparator

The primary approach for comparator design involves the utilization of single-stage dynamic latch comparators. These comparators offer advantages in terms of power and area efficiency

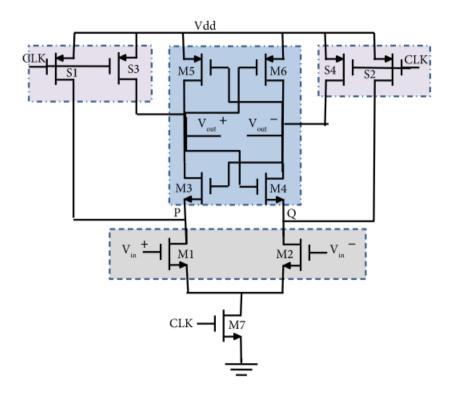

due to their minimal transistor count. Figure 5 illustrates the fundamental structure of a single-stage dynamic latch comparator [3, 4, 6, 16, 63, 86, 94], which comprises three sections: the differential amplification section (M1 and M2), the cross-coupled inverter section (M3:M6), and the reswitched section (S1:S4).

Figure 5: The basic structure of the single-stage dynamic latch comparator.[6]

The single-stage dynamic comparator operates in two distinct phases: the reset phase and the generation phase. During the reset phase, when the "clk" signal is low, the previous analog input is cleared, the switches are activated, and the output is charged to the supply voltage Vdd using the MOSFET loading capacitor. No static power is consumed during this phase. In the generation phase, when the "clk" signal is high, the amplification output is generated through a positive feedback loop established by the cross-coupled inverter section. The resulting output is determined by the differential input, and even a slight difference in the input is converted into digital levels at the full scale.

It can be observed from Figure 5, that if V+ in exceeds V- in, the node P discharges faster than the node Q, resulting in M3 and M4 to turn off until the Vgs (gate-source voltage) of M3, M4 reaches Vdd - Vthn. Once this threshold is reached, M3 and M4 are turned on. As a result, the V+ out and V- out nodes begin to discharge. The V+ out node discharges faster than the V-out node until the Vgs of M5 and M6 reach Vdd - Vthn, at which point M5 and M6 are turned on. Consequently, V+ out is grounded, and V-out is connected to Vdd, or vice versa. When V-in exceeds V+ in, the output is inverted, with V+ out connected to Vdd and V- out grounded.

A fully differential comparator offers the advantage of converting changes in input voltage signals to full-scale signals quickly and provides common mode noise rejection [6]. However,

designing the comparator involves challenges such as noise and nonlinear distortion, particularly at high Vdd. To address these challenges, adaptive supply techniques have been employed, such as using Vdd during sampling and MSB conversion, while using Vdd/2 in subsequent conversions a reduction in power consumption is observed. [16].

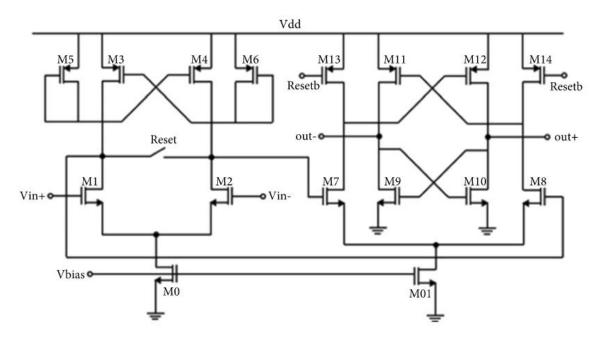

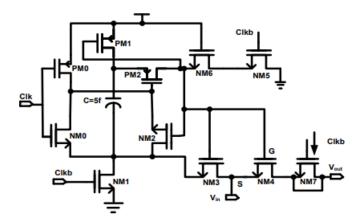

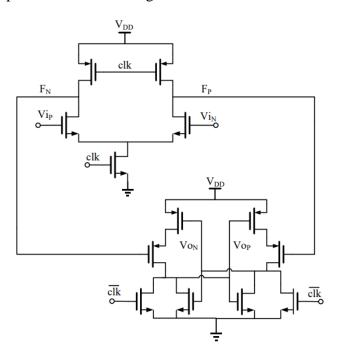

#### 2.4.2 Two Stage Dynamic Latch

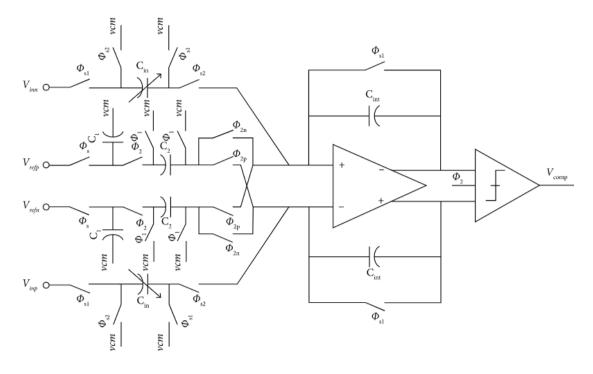

Two-stage comparator design as illustrated in Figure 6 involves the cascaded connection of a preamplifier stage and a single-stage dynamic latch [2, 5, 7, 11, 12, 15, 18–20, 27, 33, 35, 44, 53, 65, 90, 102].

Figure 6: Two stage preamplifier and dynamic latch [27].

Two-stage dynamic latch SAR comparator offers various improvements in performance for SAR ADC. It addresses issues such as kick-back noise, input-referred offset voltage, and comparison speed [14]. Different implementations have been employed to further enhance the performance of the comparator [15]. In [17], an inverter-based amplifier is utilized to enhance common mode regulation. [18] explores the application of forward body bias with lower threshold voltages, resulting in reduced delay, improved noise sensitivity, decreased RMS input-referred noise, and enhanced offset voltage. The folded cascade preamplifier comparator introduced in [19] achieves reduced delay and power consumption, while also improving the standard deviation of the offset voltage. Furthermore, [20] focuses on transistor sizing optimization to enhance input-referred offset and minimize kick-back noise. Lastly, the dynamic latch design incorporates a complement differential pair, leading to a decrease in the input-referred offset voltage [7]. These research works demonstrate various techniques and approaches aimed at improving different performance aspects of SAR ADCs.

#### 2.4.3 Three-Stage Dynamic Latch Comparator

To address issues related to delay, power consumption, kick-back noise, and input-referred offset voltage, the SAR comparator incorporates the preamplifier stage, single-stage dynamic latch, and buffer stage [1, 31, 103]. This integration aims to optimize the performance of the comparator. Moreover, certain designs incorporate the use of two inverter stages in conjunction with the single-stage dynamic latch [29, 52, 58]. This configuration offers multiple advantages such as eliminating static current consumption during the reset phase, improving the driving capability, and enabling a rail-to-rail digital output. In a specific approach described in Section 5, a four-input dynamic comparator is utilized [58], leveraging the dual sampling technique.

#### 2.4.4 Multistage Preamplifier Dynamic Latch Comparator

To address the trade-off between sensitivity, offset voltage, and speed, a comparator scheme utilizes multiple stages of the preamplifier stage and a single-stage dynamic latch, combining their advantages while achieving rejection of common mode voltage and external noise [21]. This configuration takes into consideration process and temperature (PT) variations by employing a single preamplifier stage and a bistable multivibrator latch stage, resulting in PT variation of less than 0.58 LSB [22].

Conversely, alternative designs utilize a time-domain comparator to achieve power reduction, enhance the signal-to-noise and distortion ratio (SNDR), and accelerate the conversion process [23, 24]. This type of comparator operates by converting the input voltage into pulses with varying durations and employs logic circuits such as D-flip flops for signal processing.

Table 2 provides a comprehensive overview of different comparator circuit schemes, offering a comparison based on several factors including power consumption, speed, kick-back noise, input-referred offset voltage, and resolution. Among these architectures, the single-stage dynamic latch comparator stands out with its minimal transistor count, resulting in the lowest power consumption. However, it operates at relatively slower speeds and exhibits larger offset voltage and least significant bit (LSB) values, which can impact the overall resolution of the ADC. Nevertheless, for biomedical applications where lower-to-medium sampling rates and resolution requirements are acceptable, the use of single-stage dynamic latch comparators remains a viable option. An alternative approach involves incorporating an amplifier stage into the dynamic comparator to improve the offset performance. Examples of such approaches include the utilization of two-stage dynamic latch comparators, tail transistor latch comparators, and PMOS latch comparators, which provide enhanced offset voltage at the expense of higher power consumption.

Table 2: A comparison between various configurations of the comparators is presented.

| Configurations     | Single-stage<br>dynamic latch<br>comparator | Two-stage<br>dynamic latch<br>comparator | Three-stage<br>dynamic latch<br>comparator | Multistage<br>dynamic latch<br>comparator |

|--------------------|---------------------------------------------|------------------------------------------|--------------------------------------------|-------------------------------------------|

|                    |                                             |                                          |                                            |                                           |

| No. of transistor  | Least                                       | Moderate                                 | High                                       | Highest                                   |

| Area               | Small                                       | Moderate                                 | Large                                      | Largest                                   |

| Power consumption  | Very low                                    | Moderate                                 | High                                       | Highest                                   |

| Speed              | Very low                                    | Low                                      | High                                       | Moderate                                  |

| Kick-back<br>noise | High                                        | Low                                      | Moderate                                   | Very low                                  |

| Offset voltage     | Highest                                     | Moderate                                 | Low                                        | Very low                                  |

The provided comparison in Table 2 serves as a valuable resource for designers to select the most suitable comparator circuit configuration based on their specific power and throughput requirements. In the context of biomedical applications, where the focus is on reducing power consumption while maintaining a low sample rate and moderate accuracy, the single-stage dynamic latch comparator, with appropriate modifications [16], can be a favorable option. Alternatively, the two-stage dynamic latch comparator offers a familiar solution that strikes a balance between power, speed, and noise considerations [27]. Some researchers have explored the use of tail transistors [2, 4, 7] or PMOS latch comparators [2, 4, 12, 102] to achieve decreased power consumption in their designs.

#### 2.5 CDAC Architecture

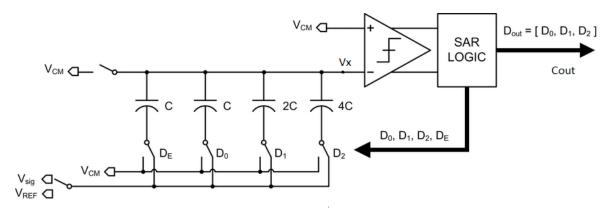

With the increasing demand for power consumption reduction in various biomedical applications, the role of the digital-to-analog converter (DAC) has become crucial [31]. The purpose of the DAC is to convert digital input bits into an analog output voltage using a reference voltage and an array of capacitors controlled by switches, as depicted in Figure 2. The resulting voltage is determined by the weight of the input bits relative to the reference voltage. Hence, the performance of the Digital-to-Analog Converter (DAC) is greatly influenced by the design of the capacitor array and the allocation of the reference voltage.

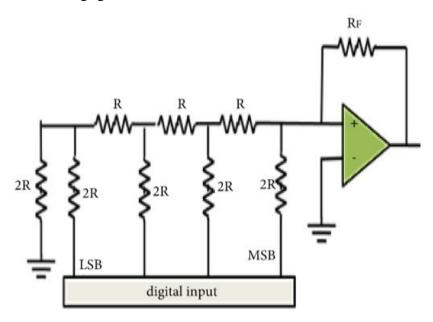

In previous works, a resistor-based DAC has been commonly employed [103]. An example of this is the R-2R ladder DAC shown in Figure 7. This implementation offers simplicity and high-speed conversion. However, it suffers from drawbacks such as high power consumption, large area occupation, lower stability, nonlinearity, and stringent matching requirements. Some studies have explored this DAC technique [25–89]. An alternative approach is to replace the resistor string with a capacitor array, which results in significant power and area savings. The

capacitor-based DAC (CDAC) exhibits lower energy dissipation, improved linearity, and reasonably shorter processing time. Nevertheless, the accuracy of the CDAC can be affected by leakage. Since the conversion time is typically within a few microseconds, the impact of leakage can be considered negligible [101].

Figure 7: The R-2R DAC structure.[101]

As depicted in Figure 3, the conversion process from digital input to analog output involves two main phases: sampling and conversion. In the sampling phase, the input voltage is stored on the capacitor array of the CDAC. Subsequently, in the conversion phase, the switches are manipulated until the equivalent digital code is achieved. It is worth noting that the switching operations of the DAC represent a significant source of power consumption in SAR ADCs. In the following subsection, various techniques for implementing the CDAC will be discussed.

#### 2.5.1 Capacitive DAC Array (CDAC)

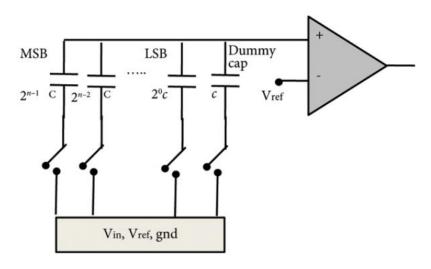

Undoubtedly, the arrangement of the capacitor array plays a crucial role in the energy consumption of the CDAC. This section provides a detailed introduction to different techniques for implementing the capacitor array in the CDAC. Several capacitor techniques have been proposed in previous works to improve power efficiency and reduce the area occupied by the CDAC arrays [25-68]. These approaches aim to achieve power reduction and area optimization through effective management of the capacitor arrays.

The conventional structure of the capacitor array consists of binary-weighted capacitors along with a dummy capacitor for full-scale operation. In an N-bit DAC, N capacitors are utilized. However, for high-resolution DACs, a large-sized capacitor is required, as illustrated in Figure 8. In the traditional voltage switching approach, the initial configuration involves connecting the most significant bit (MSB) capacitor to the reference voltage (Vref), while the remaining capacitors are connected to ground (gnd). The voltage present on the MSB capacitor corresponds to half of the Vref. When the input voltage is below Vref/2, the MSB capacitor is switched to ground, and the subsequent capacitor is connected to Vref. Conversely, if the input

voltage exceeds or equals Vref/2, the MSB capacitor remains connected to Vref, while the next capacitor is switched to Vref. Previous studies have employed this conventional structure and voltage switching scheme [1, 25]. In order to further enhance the power efficiency of the capacitor arrays in the Digital-to-Analog Converter (DAC), various capacitive-based DAC techniques have been proposed [25-68].

Figure 8: The scheme of conventional capacitive DAC.[27]

Various implementation techniques have been proposed to enhance the efficiency of the capacitor digital-to-analog converter (CDAC) and achieve energy and area savings [25-68]. These techniques mainly involve modifications to the CDAC array structure. Four main techniques have been introduced: the CDAC array structure technique, one capacitor splitting technique, hybrid redistribution technique, and special capacitor array arrangement technique. These approaches aim to reduce the size of the CDAC and improve its performance. Furthermore, the use of multiple reference voltages has been explored as a means to achieve power savings. These techniques collectively contribute to the optimization and efficiency of CDAC implementations.

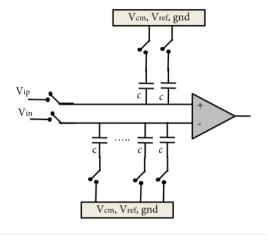

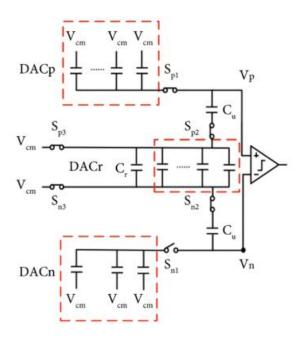

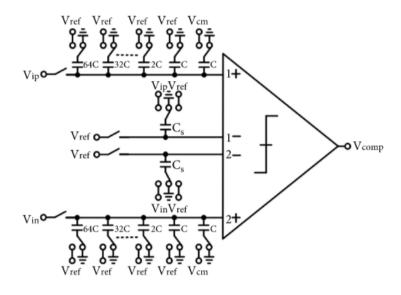

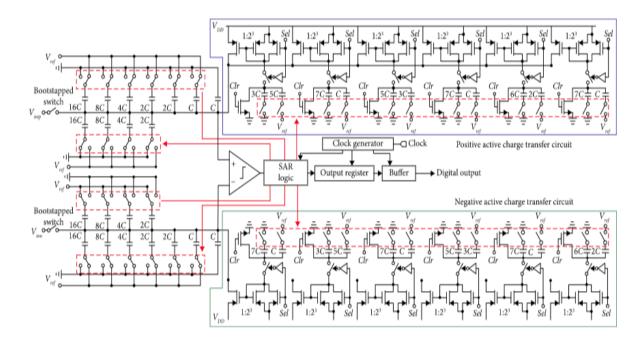

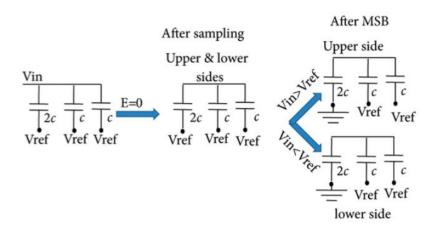

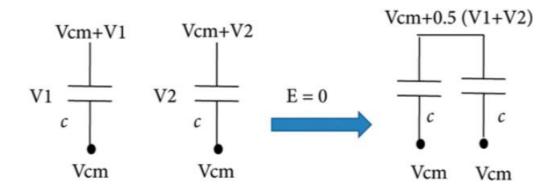

In the CDAC array structure technique, modifications are made to all capacitors in the conventional CDAC array. The fully differential CDAC architecture, as shown in Figure 9, has been proposed to address static power consumption, improve the dynamic range, and enhance common-mode noise rejection [12, 87]. This technique involves the use of two symmetric CDAC arrays on the upper and lower sides, along with a differential input comparator. One of the key advantages of this architecture is the reduction in size of the most significant bit (MSB) capacitor, which is achieved by employing a capacitor size of 2 n-2 instead of the original 2 n-1 size. However, it is important to note that this technique may introduce a varying common-level problem, which needs to be carefully addressed and mitigated in the design process. Overall, the fully differential CDAC architecture offers several benefits in terms of power consumption, dynamic range, and common-mode noise rejection, but it requires careful consideration of common-level variations.

Figure 9: Structure of a Fully differential CDAC.[27]

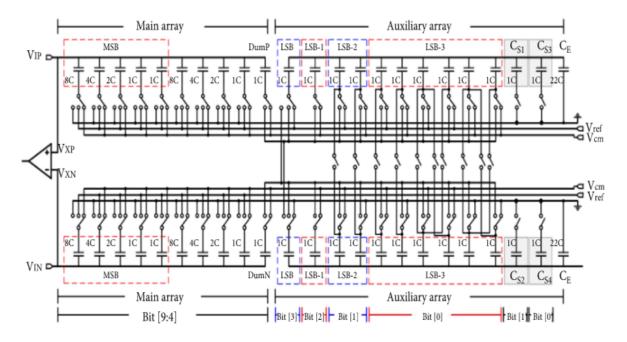

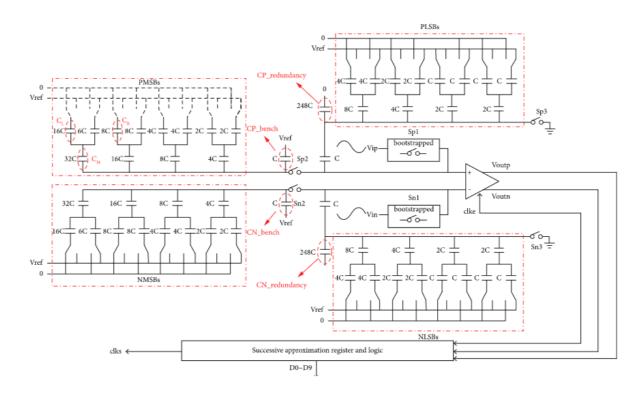

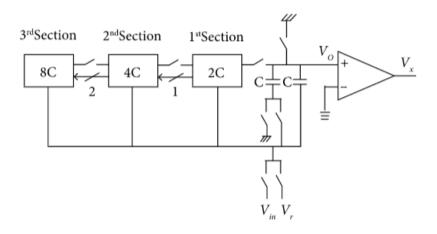

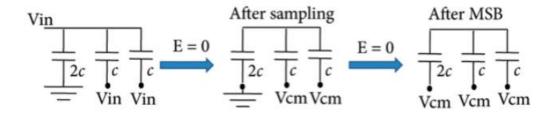

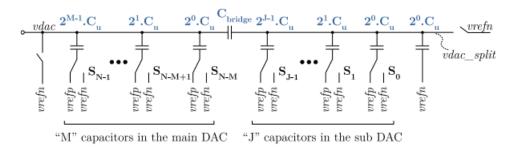

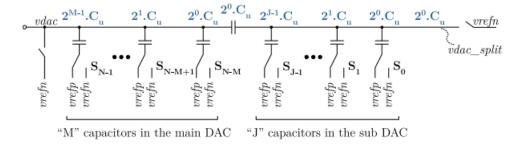

The two-stage subarray capacitor technique has been widely explored in various studies [2–6, 19, 27–30, 90, 95]. This technique involves dividing the capacitor digital-to-analog converter (CDAC) into two subarrays: the most significant bit (MSB) subarray with m bits and the least significant bit (LSB) subarray with L bits, as depicted in Figure 10. The utilization of this technique offers several advantages, including improved energy efficiency and reduced area compared to conventional techniques. Additionally, it contributes to enhanced linearity and eliminates the influence of parasitic capacitors [27–30]. Overall, the two-stage subarray capacitor technique is a valuable approach for achieving efficient and accurate digital-to-analog conversion.

Figure 10: Two-stage subarray capacitor technique.[27]

In order to reduce die size, cost, and threshold voltage, the MOS capacitor has been adopted as a replacement for the MIM (metal-isolated-metal) capacitor DAC array [29]. Furthermore, a modified two-stage dual split CDAC array technique has been utilized to mitigate mismatch

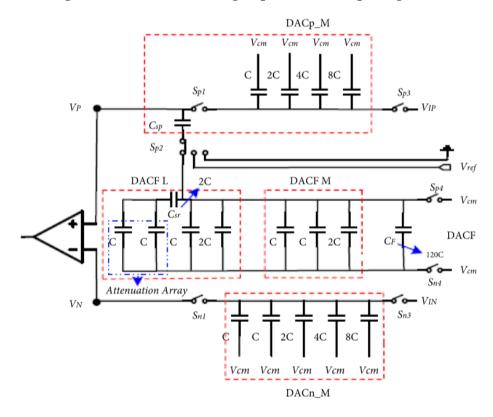

offset and decrease the size of the capacitor array [31–34]. This structure consists of three stages: subarray capacitor, most significant bit (MSB), and middle and least significant bits (MLSB and LSB), as depicted in Figure 11. By employing the hybrid capacitor technique, it is possible to achieve high resolution and optimize the area of the capacitor digital-to-analog converter (CDAC). However, it should be noted that this technique may introduce a higher level of mismatch compared to the two-stage subarray capacitor technique. As a result, the linearity of the three-stage subarray capacitor technique may be slightly lower than that of the two-stage subarray capacitor technique. Nonetheless, the hybrid capacitor technique still offers advantages in terms of resolution and CDAC area optimization.

Figure 11: Dual split three-stage subarray CDAC.[31]

Unlike in the merge-split technique as indicated in Figure 12, capacitors on each side are split into two similar capacitors except the dummy capacitor and unit capacitors [35–37].

Figure 12: Merge-split CDAC technique [35].

Rather than managing the entire CDAC array, it may be sufficient to employ a single capacitor splitting technique. The MSB splitting technique, which divides the MSB capacitor into binary-weighted capacitors (Figure 13), is a widely adopted approach [11, 12, 22, 25, 38–46]. Significant power savings of up to 37% have been reported in [25]. Another technique that enhances linearity with minimal additional hardware is the reswitching technique [45]. This technique enables the reuse of previously switched capacitors between neighboring codes.

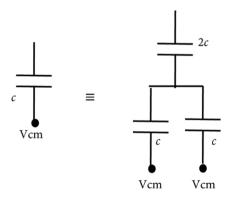

On the other hand, the LSB capacitor technique involves splitting the LSB capacitor into two serial capacitors (Figure 14) [47, 48]. This technique effectively reduces the overall capacitance by one-eighth. Similarly, the splitting of the dummy capacitor into two capacitors, known as C-2C, has been utilized in [28, 49–51] (Figure 15). This technique achieves a remarkable reduction in average energy consumption of up to 99.6% and decreases the capacitor area by up to 87.21% [51].

Figure 13: MSB split Capacitive DAC.[25]

Figure 14: LSB split-Cap-DAC.[47]

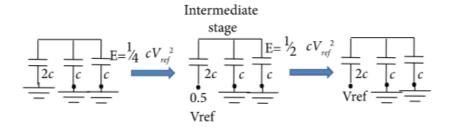

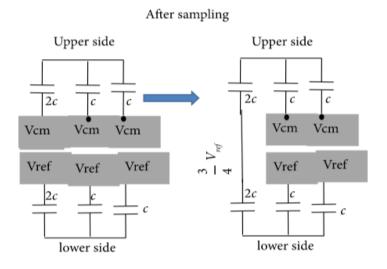

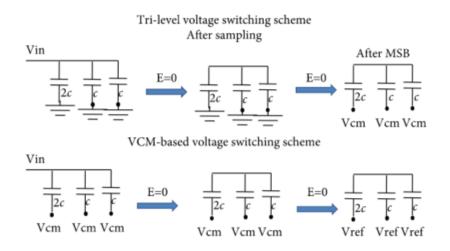

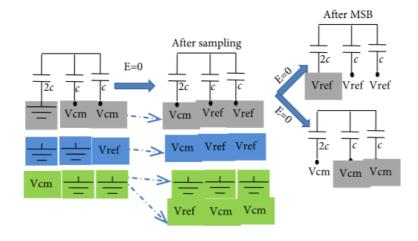

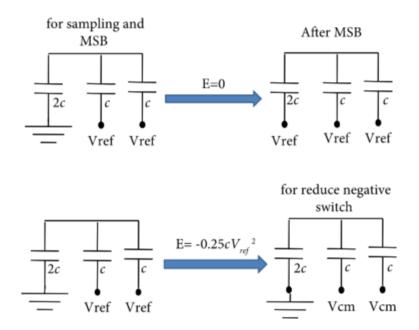

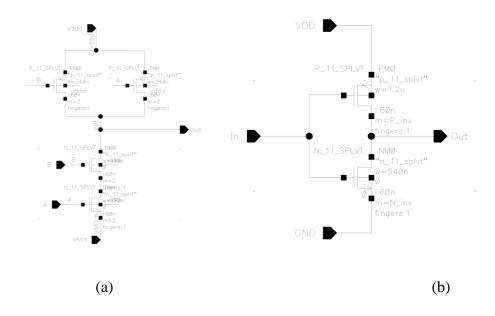

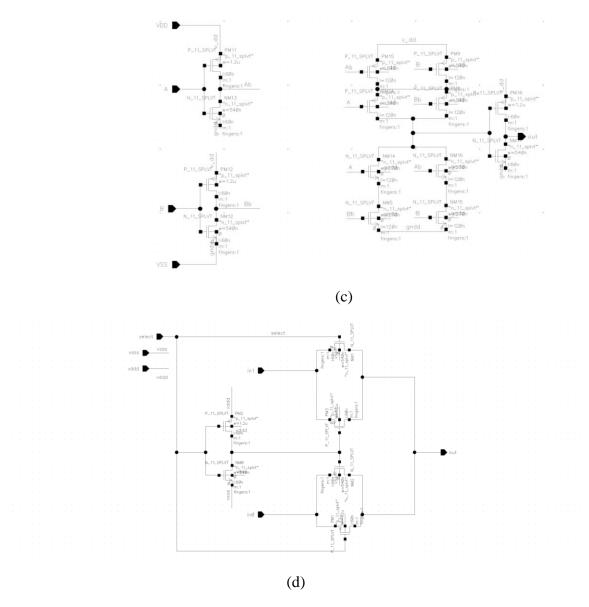

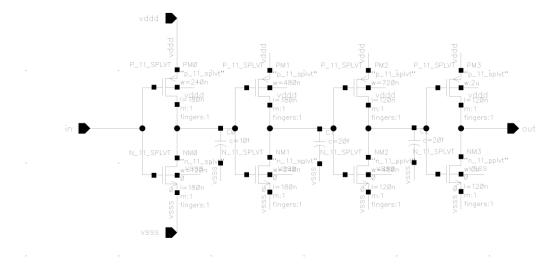

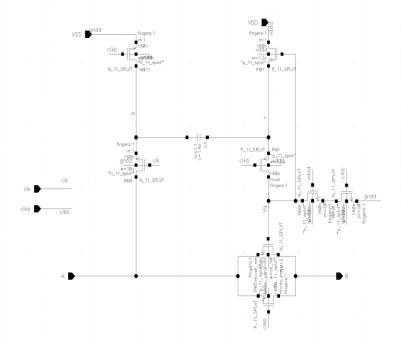

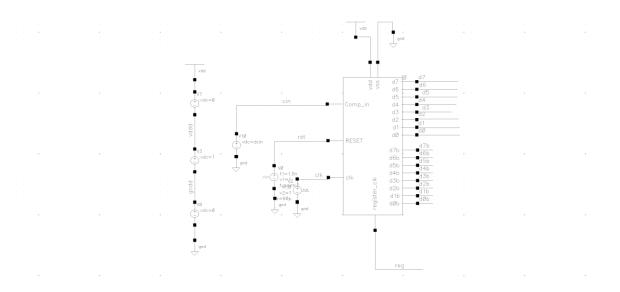

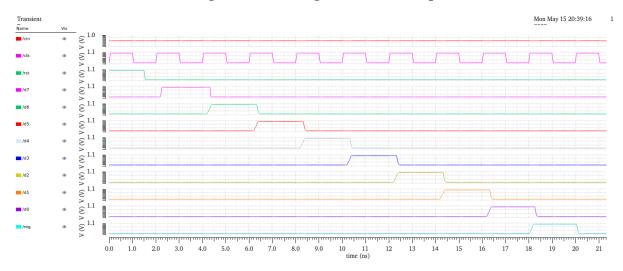

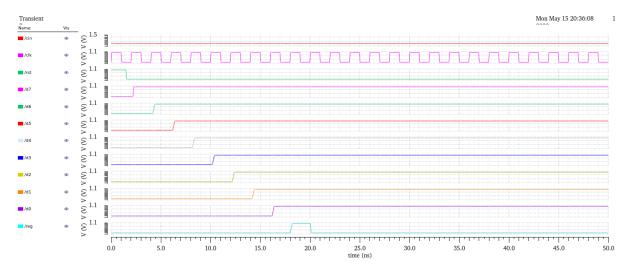

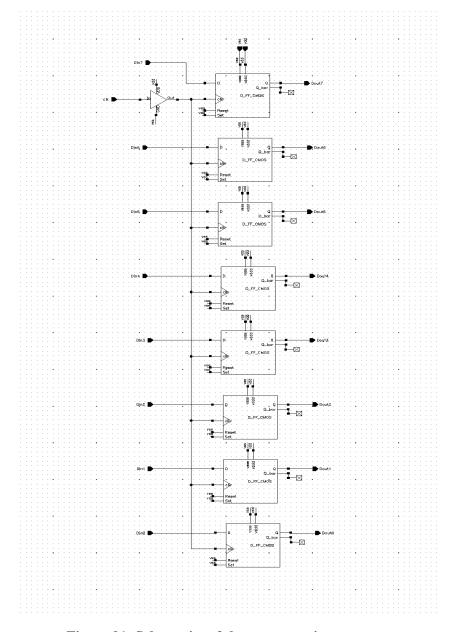

Figure 15: C-2C dummy capacitor.[47]