# ACCELERATING DEEP NETWORK-BASED IMAGE ANALYSIS USING RE-CONFIGURABLE ARCHITECTURE

A thesis submitted in partial fulfilment of the requirement for the award of the degree of Master of Technologies in VLSI Design & Micro Electronics Technology

# By RANITA PAL

Class Roll Number: 002010703004 Examination Number: M6VLS23008 Registration Number: 154106 of 2020-2021

Under the Guidance of

### Dr. Sayan Chatterjee

(Professor, Jadavpur University, Kolkata)

&

### Prof. Amlan Chakrabarti

(Professor and Director, A.K. Choudhury School of IT, University of Calcutta)

Jadavpur University

June 2023

#### FACULTY OF ENGINEERING & TECHNOLOGY JADAVPUR UNIVERSITY

#### CERTIFICATE OF RECOMMENDATION

This is to certify that the thesis entitled — "ACCELERATING DEEP NET WORK-BASED IMAGE ANALYSIS USING RE-CONFIGURABLE ARCHITECTURE" has been carried out by Ranita Pal bearing Class Roll No: 002010703004, Examination Roll No.: and Registration No: 154092 of 2020-21, under my guidance and supervision and be accepted in fulfilment of the requirement for the degree of " Master of Technology in VLSI Design & MicroElectronics Technology" in the Department of Electronics and Telecommunication Engineering". No prior submission of the research results in this thesis for any degree at any other institution or university.

PROF. SAYAN **CHATTERJEE**

(Internal Thesis Supervisor,

Dept. of Electronics &

Telecommunication

Engineering, Jadavpurayan Chatterjee

University)

Froressor Electronics & Telecomm. Engg. Dept., Telecomm. Engg. 700032. Jadavpur University, Kolkata - 700032.

DR. MANOTOSH BISWAS

(Head of Department,

Dept. of Electronics &

Telecommunication

Engineering, Jadavpur

University)

MANOTOSH BISWAS

Professor and Head

: Electronics and Telecommunication Engineering Jadavpur University, Kolkata - 32

PROF.

AMLAN K. Choudhury

**CHAKRABARTI**

School of IT

12/06/2023

(External Thesis Supervisor,

Professor and Director, A.K. Choudhury School of IT, University of Calcutta)

Ardhenda Gloshel 12/06/23

PROF.

**ARDHENU**

GHOSAL

(Dean,

Faculty of Engineering & Technology, Jadavpur University)

# FACULTY OF ENGINEERING & TECHNOLOGY JADAVPUR UNIVERSITY

#### CERTIFICATE OF APPROVAL

The forgoing thesis titled "ACCELERATING DEEP NETWORK-BASED IMAGE ANALYSIS USING RE-CONFIGURABLE ARCHITECTURE"

is here approved as a creditworthy study of an engineering subject conducted and presented satisfactorily to warrant its acceptance as a pre-requisite to the degree for which it was submitted. It is understood that the undersigned does not automatically support or accept any argument made, opinion expressed, or inference is drawn in it by this approval, but only approve the thesis for the reason for which it was submitted.

| Evaluation of the Thesis         |

|----------------------------------|

| Signature of Internal Supervisor |

| Signature of External Supervisor |

| Signature of External Examiner1  |

| Signature of External Examiner2  |

Author's declaration of originality

I, RANITA PAL, hereby declare that the work presented in the thesis is entirely

my original work. I have appropriately acknowledged and referenced any sources

utilized in the creation of this work. No part of this work has been previously

submitted for academic assessment or publication, except where specifically refer-

enced. I affirm that I have not engaged in any form of plagiarism, and I accept

full responsibility for the content and integrity of this work.

By signing this declaration, I affirm that the above statements are true and that

I have complied with the ethical standards and requirements set forth by the

academic institution and the relevant guidelines for originality and integrity in

research.

Name: Ranita Pal

University Registration No.: 154106 of 2020-2021

Exam Roll No: M6VLS23008

Class Roll No.: 002010703004

Thesis Title: ACCELERATING DEEP NETWORK-BASED IMAGE

ANALYSIS USING RE-CONFIGURABLE ARCHITECTURE

Signature of Candidate: .....

Date: .....

iii

### Acknowledgements

I would like to begin by expressing my heartfelt gratitude to my supervisors, **Prof. Amlan Chakraborti** and **Dr. Sayan Chatterjee** for their guidance, expertise, and unwavering support in shaping this thesis. I have been very fortunate to have a guide like them. Their positivity, confidence, and ideas help me to complete my thesis, and they guide me as a guardian.

I extend my sincere thanks to **Dr. Manotosh Biswas**, the Head of the Department for consistently extending a helping hand whenever needed. I also thank my fellow project mates, friends, and technical and non-technical staff of Jadavpur University who have helped me directly or indirectly during the tenure of my thesis work.

I want to express my gratitude to my parents and family also, for their invaluable love and encouragement.

Ranita Pal

Jadavpur University Kolkata-32, West Bengal

### **Abstract**

This thesis investigates the utilization of reconfigurable architectures, specifically field-programmable gate arrays (FPGAs), for accelerating deep neural network-based image classification tasks. Four different DNN classification model architectures are analyzed using a custom medical image dataset. The trained model weights are compiled into an hardware-specific model weights and executed on an FPGA board, taking advantage of the parallel processing capabilities and hardware acceleration offered by the DPU architecture. The evaluation of performance and efficiency gains encompasses factors such as inference time, accuracy, and resource utilization. The experimental results demonstrate that the integration of software and hardware components leads to significant improvements in speed and energy efficiency. However, certain limitations and areas for improvement are identified, highlighting future research opportunities for optimizing reconfigurable architectures for image analysis tasks. In summary, this thesis presents a comprehensive exploration of the advantages and challenges associated with reconfigurable architectures for accelerating deep neural network-based image analysis. The findings provide valuable insights into the potential of FPGAs and DPUs in enhancing the performance of image analysis tasks based on deep neural networks and establish a foundation for future advancements in this field.

### List of Acronyms

**FPGA** Field Programmable Gate Array

DPU Xilinx® Deep Learning Processing Unit

CPU Central Processing Unit

SoC System on Chip

**ANN** Artificial Neural Network

**CNN** Convolutional Neural Network

IP semiconductor Intellectual Property

AI Artificial Intelligence

**DL** Deep Learning

**AXI** Advanced eXtensible Interface

TCL Transaction Control Language

XSA Xilinx Support Archive

API Application Programmable Interface

**DDR** Double Data Rate

**HDL** Hardware Description Language

**DTG** Device Tree Generator

mAp Mean Average Precision

V.P. Viral Pneumonia

### Contents

| 1 | Inti | roduction                                | 1  |

|---|------|------------------------------------------|----|

|   | 1.1  | Motivation                               | 2  |

|   | 1.2  | Objective                                | 3  |

|   | 1.3  | Contribution of Hypothesis               | 3  |

|   | 1.4  | Thesis organization                      | 4  |

| 2 | The  | esis Background                          | 6  |

| 3 | Init | ial Experiments and Findings             | 9  |

|   | 3.1  | Vitis                                    | 9  |

|   | 3.2  | Vitis AI                                 | 10 |

|   | 3.3  | Hardware Core                            | 11 |

|   |      | 3.3.1 DPU architecture                   | 11 |

|   |      | 3.3.2 DPU Naming                         | 13 |

|   |      | 3.3.3 DPU Configuration                  | 13 |

|   |      | 3.3.4 DPU Integration                    | 16 |

| 4 | Too  | ols and Prototyping Environment Utilized | 19 |

|   | 4.1  | Xilinx                                   | 19 |

|   |      | 4.1.1 Vitis AI                           | 19 |

|   |      | 4.1.2 Vitis AI DPU                       | 20 |

|   |      | 4.1.3 Vitis AI Quantiser                 | 21 |

|   |      | 4.1.4 Vitis AI Compiler                  | 23 |

|   |      | 4.1.5 ZCU104                             | 25 |

|   | 4 2  | User Hardware                            | 26 |

|   | 4.3 | User S  | Software                               | 6 |

|---|-----|---------|----------------------------------------|---|

|   |     | 4.3.1   | Docker                                 | 6 |

|   |     | 4.3.2   | Jupyter Notebook                       | 7 |

| 5 | Mo  | del Co  | emparison 28                           | 2 |

|   | 5.1 | RESN    | ET-50                                  | C |

|   |     | 5.1.1   | Description                            | C |

|   |     | 5.1.2   | Reason for choosing the model          | C |

|   |     | 5.1.3   | Training/Fine-tuning the model         | 1 |

|   |     | 5.1.4   | Quantization                           | 2 |

|   |     | 5.1.5   | Compiling quantised model to xmodel 3  | 4 |

|   | 5.2 | DENS    | SENET-169                              | 5 |

|   |     | 5.2.1   | Description                            | 5 |

|   |     | 5.2.2   | Reason for choosing the model          | 5 |

|   |     | 5.2.3   | Training/Fine-tuning the model         | 6 |

|   |     | 5.2.4   | Quantization                           | 7 |

|   |     | 5.2.5   | Compiling quantised model to xmodel 38 | 8 |

|   | 5.3 | VGG-    | 16                                     | 9 |

|   |     | 5.3.1   | Description                            | 9 |

|   |     | 5.3.2   | Reason for choosing the model          | 9 |

|   |     | 5.3.3   | Training/Fine-tuning the model 40      | C |

|   |     | 5.3.4   | Quantization                           | 1 |

|   |     | 5.3.5   | Compiling quantised model to xmodel 45 | 2 |

|   | 5.4 | Mobile  | eNet                                   | 3 |

|   |     | 5.4.1   | Description                            | 3 |

|   |     | 5.4.2   | Reason for choosing the model 43       | 3 |

|   |     | 5.4.3   | Training/Fine-tuning the model 4       | 4 |

|   |     | 5.4.4   | Quantization                           |   |

| 6 | Des | criptic | on of Workflow 4                       | 7 |

|   | 6.1 | Tools   | Execution Process 4                    | 7 |

|   |     | 611     | Vivado 2020 2 HLx edition 4            | 7 |

|    |       | 6.1.2          | Vitis AI                                  | 48 |

|----|-------|----------------|-------------------------------------------|----|

|    |       | 6.1.3          | Petalinux                                 | 48 |

|    |       | 6.1.4          | Edge AI environment on the ZCU104 board . | 48 |

|    | 6.2   | Integra        | ation of fine-tuned models with ZCU104    | 49 |

|    |       | 6.2.1          | Hardware                                  | 49 |

|    |       | 6.2.2          | Software                                  | 54 |

|    |       | 6.2.3          | Prepare Files for Platform Packaging      | 58 |

|    | 6.3   | Applie         | eation on DPU                             | 64 |

|    |       | 6.3.1          | Docker Setup on the Host                  | 65 |

|    |       | 6.3.2          | Model Deployment                          | 65 |

|    |       | 6.3.3          | Deployment on Edge boards                 | 66 |

| 7  | Resi  | ult <b>A</b> n | alysis                                    | 70 |

|    | 7.1   | Datase         | et                                        | 71 |

|    | 7.2   | Proof          | of Concept and Accuracy Analysis          | 74 |

|    | 7.3   | Model          | Size and Resource Utilization             | 77 |

|    | 7.4   | Hardw          | vare Acceleration:                        |    |

|    |       | Perfor         | mance & Evaluation                        | 78 |

| 8  | Con   | clusio         | ns                                        | 82 |

| 9  | Futu  | ıre Wo         | ork                                       | 83 |

| 10 | Sum   | ımary          |                                           | 84 |

| Bi | bliog | raphy          |                                           | 85 |

# List of Figures

| 3.1 | DPU architecture                                                 | 12 |

|-----|------------------------------------------------------------------|----|

| 3.2 | DPU Naming                                                       | 13 |

| 3.3 | DPUCZDX8G architecture                                           | 14 |

| 3.4 | DPU IP with all its interfaces                                   | 18 |

| 4.1 | Vitis AI Quantizer Framework                                     | 21 |

| 4.2 | Vitis AI Quantizer Workflow                                      | 22 |

| 4.3 | Vitis AI Compiler Framework                                      | 23 |

| 4.4 | Vitis AI Compiler Workflow                                       | 24 |

| 4.5 | Xilinx ZCU104 Evaluation Board and Peripheral Con-               |    |

|     | nections                                                         | 25 |

| 5.1 | Confusion Matrix for ResNet-50 model                             | 31 |

| 5.2 | Confusion Matrix for DenseNet-169 model                          | 36 |

| 5.3 | Confusion Matrix for VGG-16 model                                | 40 |

| 5.4 | Confusion Matrix for MobileNet model                             | 44 |

| 6.1 | Simplified view of development flow in proposed solution         | 50 |

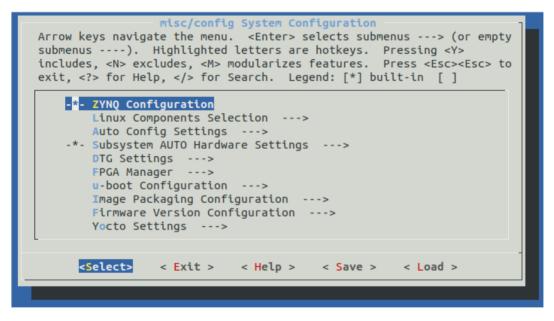

| 6.2 | $Screenshot\ of\ DPU\ configuration\ used\ in\ this\ project\ .$ | 52 |

| 6.3 | Screenshot of a block diagram of hardware configura-             |    |

|     | tion used in this project                                        | 53 |

| 6.4 | Additional User Packages in PetaLinux                            | 55 |

| 6.5 | Petalinux Root filesystem configuration window                   | 56 |

| 6.6 | Device Tree for ZCU104                                           | 57 |

| 6.7 | Petalinux configuration window                                   | 57 |

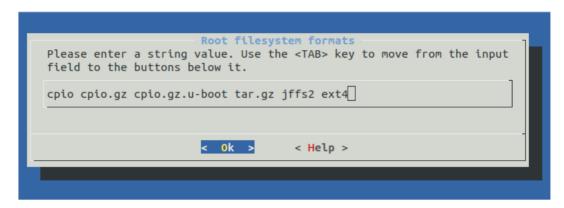

| 6.8 | Petalinux Root filesystem configuration formats window           | 58 |

| 6.9  | Contents of linux.bif                                        | 59 |

|------|--------------------------------------------------------------|----|

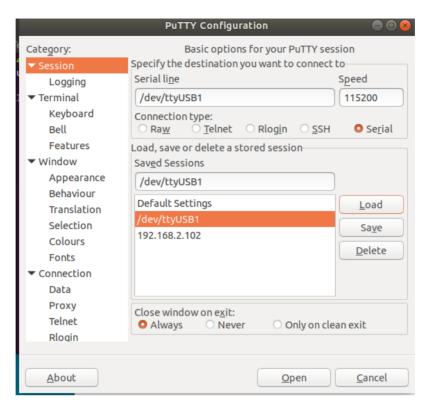

| 6.10 | Screenshot of Putty Configuration Window                     | 63 |

| 6.11 | Screenshot of terminal shortly after Petalinux has suc-      |    |

|      | cessfully booted greeting with a login screen                | 63 |

| 6.12 | $creen shot\ of\ DPU\ Signature\ Viewed\ ZCU104\ with\ DEx-$ |    |

|      | plorer                                                       | 64 |

| 6.13 | Screenshot of Quantized model file                           | 66 |

| 6.14 | Screenshot of Compiled xmodel file                           | 67 |

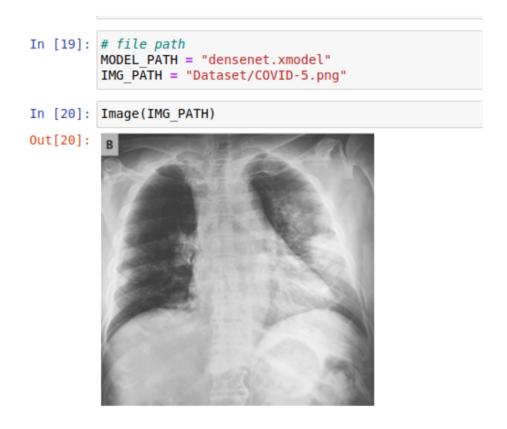

| 7.1  | Screenshot of COVID dataset image                            | 71 |

| 7.2  | Screenshot of COVID class prediction                         | 72 |

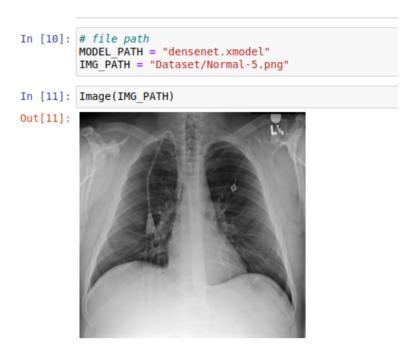

| 7.3  | Screenshot of Normal class dataset image                     | 72 |

| 7.4  | Screenshot of Normal class prediction                        | 73 |

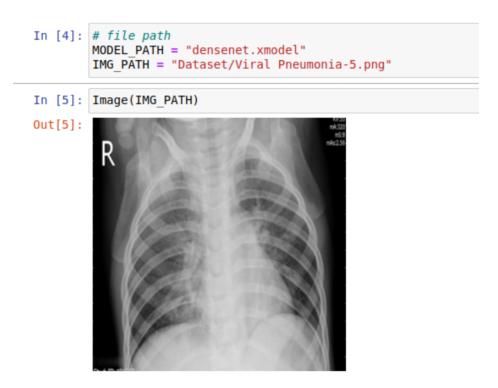

| 7.5  | $Screenshot\ of\ Viral\ Pneumonia\ class\ dataset\ image.$   | 73 |

| 7.6  | Screenshot of Viral Pneumonia class prediction               | 74 |

### List of Tables

| 3.1  | DPU parameters in Vivado                                            | 16 |

|------|---------------------------------------------------------------------|----|

| 5.1  | Classification Report of ResNet-50 model                            | 32 |

| 5.2  | $Confusion\ Matrix\ for\ Quantized\ ResNet50\ model\ \ .\ \ .$      | 33 |

| 5.3  | $Classification \ Report \ of \ Quantized \ ResNet50 \ model \ \ .$ | 33 |

| 5.4  | Confusion Matrix for Compiled ResNet-50 model                       | 34 |

| 5.5  | Classification Report of Compiled Resnet-50 model                   | 34 |

| 5.6  | Classification Report of DenseNet-169 Model                         | 37 |

| 5.7  | Confusion Matrix for Quantized DenseNet model                       | 37 |

| 5.8  | Classification Report of DenseNet-169 Quantized Model               | 38 |

| 5.9  | Confusion Matrix for Compiled DenseNet-169 model                    | 38 |

| 5.10 | Classification Report of Compiled DenseNet-169 model                | 39 |

| 5.11 | Classification Report of Vgg-16 model                               | 41 |

| 5.12 | Confusion Matrix for Quantized Vgg-16 model                         | 41 |

| 5.13 | Classification Report of Quantized Vgg-16 Model                     | 42 |

| 5.14 | Confusion Matrix for Compiled Vgg-16 model                          | 42 |

| 5.15 | Classification Report of Compiled Vgg-16 model                      | 43 |

| 5.16 | Classification Report of MobileNet                                  | 45 |

| 7.1  | Comparison of average accuracy values per class for                 |    |

|      | ResNet-50 model                                                     | 75 |

| 7.2  | Comparison of average accuracy values per class for                 |    |

|      | DenseNet model                                                      | 75 |

| 7.3  | Comparison of average accuracy values per class for                 |    |

|      | Van 16 model                                                        | 76 |

| 7.4 | Comparison of average accuracy values per class for  |    |

|-----|------------------------------------------------------|----|

|     | $MobileNet \dots \dots \dots \dots \dots \dots$      | 76 |

| 7.5 | Comparison of Model Sizes and Resource Utilization . | 77 |

| 7.6 | Inference Time Comparison between CPU and DPU.       | 79 |

### Chapter 1

### Introduction

In recent years, deep neural networks (DNNs) have revolutionized the field of image analysis, enabling remarkable advancements in tasks such as image classification [1], object detection [2], and semantic segmentation. However, as DNNs continue to grow in complexity and demand higher computational resources, the need for efficient and high-performance hardware accelerators becomes crucial [3]. Re-configurable architectures, such as field-programmable gate arrays (FPGAs), offer a promising solution for accelerating DNN computations due to their flexibility, parallel processing capabilities, and energy efficiency [4].

This thesis explores the acceleration of a few different deep neural network-based image classification architectures through the integration of software and re-configurable hardware architecture. Specifically, the focus lies on leveraging the capabilities of the ZCU104 FPGA board and the development and optimization of a deep learning processing unit (DPU) architecture to enhance the performance and efficiency of image analysis tasks.

#### 1.1 Motivation

Running artificial neural networks on different types of hardware-based accelerators is a topic extensively discussed for many years. Many educational institutions across the world use various development boards as teaching aids and for quick prototyping. The motivation behind this work lies in the demand for real-time image classification and the potential of FPGA-based implementations to achieve high-performance inference in resource-constrained environments [5]. Furthermore, hardware acceleration enables scalability and flexibility. With the ability to scale up the number of accelerator units or integrate multiple accelerators, deep learning models can be trained and deployed on large-scale systems or distributed environments [6]. This scalability is particularly crucial for handling massive datasets and complex network architectures.

FPGA DNN accelerators [7] have become relatively new, offering low-latency, energy-efficient, and customizable solutions for accelerating deep neural network computations in various applications. The current research on implementing DPUs on FPGAs is relatively limited compared to other areas focusing on the given algorithms. However, there is vast untapped potential for further research, particularly in implementing image classification applications on student-friendly platforms. By utilizing different deep learning models on the ZCU104 evaluation kit, educational purposes can be served effectively. This proposed solution holds the promise of enhancing students' understanding of how artificial neural networks can be accelerated on FPGAs, facilitating the acceleration of various applications on hardware platforms.

### 1.2 Objective

This thesis aims to design architectures for important deep neural networks used in image analysis, primarily focusing on the software domain. The designed architectures will be optimized and fine-tuned for specific image analysis tasks. Subsequently, the implementation phase will involve leveraging accelerated DPU IP on hardware platforms. This entails configuring the DPU architecture using tools like Vitis IDE and integrating it with the FPGA board. The ultimate goal is to achieve high-performance and energy-efficient image classification by executing the optimized deep neural networks on the hardware platform, harnessing the capabilities of the DPU for accelerated inference.

### 1.3 Contribution of Hypothesis

The main idea for the proposed solution was that Vitis AI could be used to quickly deploy neural network applications that were accelerated by DPU without modifying hardware architectures. Four alternative deep neural network models will be tested on the ZCU104 hardware platform in order to demonstrate its usability and simplicity. If Vitis AI performs as expected, it will make accelerating deep neural network inference easier than ever before and enable quick prototyping of new embedded solutions requiring real-time medical image processing. This approach holds the potential to simplify and expedite the development of advanced embedded systems in the medical domain.

### 1.4 Thesis organization

This thesis is formulated in the following chapters:

- The **Thesis Background** chapter provides a concise overview of previously proposed solutions that are relevant to the current problem. It includes a list of similar solutions along with a brief analysis from the author regarding the feasibility of utilizing these solutions to address the problem at hand. This section offers a valuable glimpse into the existing work that has been done in the field, providing context and highlighting the advancements made prior to the current study.

- The Initial Experimental and Findings chapter presents the workflow and initial experimental phase undertaken in the thesis before arriving at the final solution. It outlines the various tools that were initially intended for use in finding the solution but were ultimately disregarded, accompanied by the reasons for their exclusion. This chapter sheds light on the early stages of the research process, providing insight into the methodologies explored and the reasons behind the choices made in the pursuit of the ultimate solution.

- The **Used Tools** chapter comprehensively documents and explains the key tools employed in the development of the solution. It provides a detailed inventory of the essential software, hardware, and technologies utilized throughout the project, accompanied by thorough explanations of their functionalities and contributions. This chapter serves as a comprehensive reference, offering readers a comprehensive understanding of the tools harnessed to implement the solution effectively.

- The Model Comparison chapter conducts a comprehensive evaluation of four distinct models, considering various factors

such as time, performance, and model size, for image analysis in both software and hardware contexts. Through a meticulous analysis, this chapter provides a comparative assessment of the models, shedding light on their respective strengths and weaknesses. By examining their performance metrics and considering their computational efficiency, this chapter enables a thorough understanding of the trade-offs involved in selecting a suitable model for image analysis tasks.

- The **Description of Workflow** chapter serves as a comprehensive resource for individuals seeking to replicate the provided solution and implement various deep neural networks on the FPGA platform, specifically the ZCU104 Evaluation board. It offers detailed instructions and necessary tools to enable users to successfully replicate and implement the solution.

- The **Result Analysis** section digs into the methodology used to analyze the proposed solution and presents the experimental findings obtained.

- The **Conclusion** section summarizes the key findings and offers a concise overview of the main analysis results.

- The **Future work** section highlights potential areas for improvement and suggests possible enhancements to the proposed solution.

### Chapter 2

### Thesis Background

This chapter provides an overview of earlier attempts to run deep neural networks on similar platforms. The objective was to identify existing solutions that address similar problem descriptions. Among these attempts, a particularly close match was found, where a Convolutional Neural Network (CNN) was implemented on the ZCU104 board using DPU IP [8]. This implementation aimed to leverage custom hardware platforms to accelerate the inference process and reduce overall energy consumption. In this chapter, we dig into the details of the closest solution and examine its relevance to the current problem.

Numerous studies have been conducted utilizing the DPU on FPGA platforms, particularly on Zynq devices. These works explore the potential of leveraging the DPU's capabilities to accelerate various computational tasks. The utilization of DPU on FPGA has emerged as a popular research area, showcasing its effectiveness and versatility in accelerating neural network computations and enabling efficient hardware acceleration. For example, in the conference paper [9], the work focuses on achieving time-predictable execution of Deep Neural Networks (DNNs) accelerated on FPGA System-on-Chips (SoCs). The study utilizes the modern DPU accelerator by Xilinx and conducts extensive profiling on the Zynq Ultrascale+ platform.

Based on the profiling data, an execution model is proposed to derive response-time analysis. To enhance predictability, a custom FPGA module named DICTAT is introduced. Experimental results, including analytical bounds and measurements, demonstrate the effectiveness and performance of the approach for Advanced Driver Assistance Systems (ADAS) applications.

In the research paper "FPGA-Based Adaptive Hardware Acceleration for Multiple Deep Learning Tasks" [10] by the authors Yufan Lu; Xiaojun Zhai; Sangeet Saha; Shoaib Ehsan; and Klaus D. McDonald-Maier from School of Computer Science and Electronic Engineering, University of Essex, Colchester, UK addresses the challenges of deploying deep learning algorithms on resourceconstrained mobile and embedded systems. The authors propose an adaptive hardware resource management system implemented on FPGAs, which dynamically manages on-chip hardware resources to accommodate various tasks. By utilizing dynamic function exchange (DFX) technology, the system allocates hardware resources for deploying deep learning units (DPUs), optimizing performance and power consumption. The prototype is implemented on Xilinx Zyng UltraScale+ series chips, and experimental results demonstrate significant improvements in computing efficiency for resourceconstrained systems across different scenarios. The proposed scheme achieves power savings of 38% and 82% in low and high working load cases, respectively, resulting in an energy reduction of approximately 75.8% compared to the baseline approach.

In the article "An Effective Design to Improve the Efficiency of DPUs on FPGA" [11] by Yutian Lei, Qingyong Deng, Saiqin Long and Shaohui Liu; Sangyoon Oh, there was a similar attempt to accelerate multitasking applications involving multiple CNN mod-

els, resulting in low utilization and scheduling efficiency. This paper proposes an effective solution called Multi-Core with Different Size (MCDS) and DPU Plus, aiming to improve DPU utilization in terms of time and space. By increasing the number of DPU cores and optimizing their utilization, MCDS enhances overall throughput while efficiently managing on-chip resources. Additionally, the DPU Plus design enhances scheduling efficiency by concurrently implementing the DPU with other crucial auxiliary modules on the same FPGA. Experimental results demonstrate the effectiveness of the proposed approach, with a 16.2x acceleration compared to CPU execution and a 3.0x increase in system throughput.

The majority of articles in the field focus on Convolutional Neural Network (CNN) implementations on FPGA platforms utilizing the DPU as a hardware accelerator. In this thesis, however, a novel approach is taken by experimenting with various Artificial Neural Network (ANN) models for hardware implementation using the DPU IP. The results of these experiments reveal a remarkable inference speedup of 90x, showcasing the effectiveness and potential of this approach in accelerating neural network computations on FPGA-based systems.

### Chapter 3

### Initial Experiments and Findings

The current chapter focuses on the early experimental stages of this thesis, highlighting the evolution of the initial task description and the discovery of the proposed solution. It provides insights into the influence of Vitis and Vitis AI in guiding the development of the solution. The chapter explores the reasons behind the changes in the task description and examines the role played by Vitis and Vitis AI in shaping the direction of the research.

#### 3.1 Vitis

Vitis, known as the Vitis Unified Software Platform, is a software platform developed by Xilinx that facilitates the development of embedded software and accelerated applications on various Xilinx platforms, including FPGAs, SoCs, and ACAPs. It offers a unified programming model for accelerating Edge, Cloud, and Hybrid computing applications. With its embedded programming versatility, Vitis has the potential to significantly enhance the development workflow and speed of embedded and accelerated applications [12].

One of the key advantages of Vitis is its integration of high-level frameworks, allowing developers to utilize programming languages such as C, C++, or Python to create hardware-accelerated applications. Additionally, it provides low-level APIs that offer greater control over the implementation process when necessary. This combination of high-level frameworks and low-level APIs empowers developers to leverage the full potential of the underlying hardware and optimize the performance of their applications.

#### 3.2 Vitis AI

Vitis AI serves as a dedicated development platform for AI inference on Xilinx hardware platforms. It encompasses a range of optimized IP (DPU), tools, libraries, models, and example designs. With a strong emphasis on high efficiency and user-friendliness, Vitis AI aims to streamline the process of developing and deploying AI models on Xilinx platforms [13].

Vitis AI adopts a Docker-based approach to deliver its suite of tools to developers, offering a more convenient installation experience compared to its predecessor, DNNDK. By leveraging Docker containers, Vitis AI simplifies the process of setting up the required software environment, ensuring consistency and ease of deployment across different systems.

The Vitis AI guide [14] offers comprehensive instructions and examples for developers to leverage the platform's capabilities in performing different applications. It covers installation, model conversion, and optimization techniques, and provides practical examples, enabling effective deployment of AI models on Xilinx hardware platforms.

#### 3.3 Hardware Core

The hardware core at the heart of the development environment is known as the Deep Learning Processing Unit (DPU). This programmable engine is specifically designed to optimize the performance of ANNs and CNNs. CNNs are particularly well-suited for tasks such as object detection and recognition, as they enable efficient interconnection between perceptrons. The DPU can be implemented within the programmable logic (PL) of various Xilinx boards, offering user-configurable options. This flexibility allows the DPU to meet the performance requirements of diverse applications while minimizing FPGA space and cost. More detailed information about the hardware architecture of the DPU, including the DPUCZDX8G optimized for Zynq Ultrascale+ MPSoCs, can be obtained from this document [15].

#### 3.3.1 DPU architecture

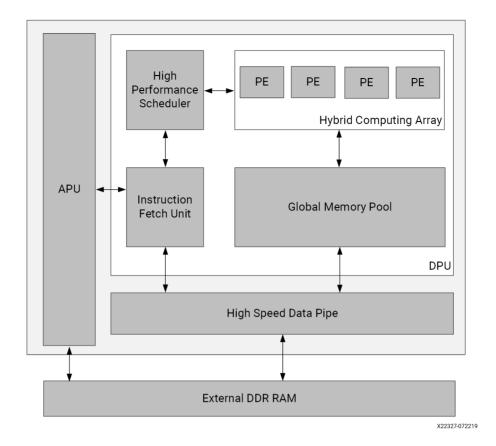

The hardware architecture of the DPU, specifically the DPUCZDX8G optimized for Zynq Ultrascale+ MPSoCs, is depicted in Figure 3.1. It comprises four key components:

- Instruction scheduler: The instruction scheduler is responsible for managing the execution of instructions, which belong to a specialized set optimized for common operations in CNNs. These instructions are read from on-chip memory and scheduled for execution by the processing engines in the computing engine.

- On-Chip buffer controller: It handles operations on the onchip memory, which stores input data, intermediate results, and

Figure 3.1: DPU architecture

outputs. This improves overall DPU performance by avoiding delays associated with off-chip memory communication.

- Computing engine: The computing engine serves as the execution core of the DPU, consisting of an array of processing engines (PEs) designed with a deep pipelined architecture to maximize throughput.

- **AXI Interfaces**: AXI interfaces are used for data communication with the off-chip memory and the processor, which controls the DPU's execution.

To further enhance performance, a DSP Double Data Rate (DDR) technique is employed, which increases resource utilization and requires an additional clock. These architectural components and techniques contribute to the DPU's efficiency and performance in accelerating neural network computations.

#### 3.3.2 DPU Naming

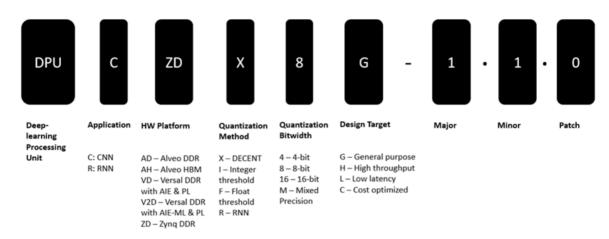

Different fields of DPU name are used to indicate different features or purposes, and the naming scheme is shown in the figure 3.2.

Figure 3.2: DPU Naming

The DPUCZDX8G IP is specifically optimized for integration with the Zynq UltraScale+ MPSoC. It can be seamlessly incorporated as a block in the programmable logic (PL) of the chosen Zynq Ultra-Scale+ MPSoCs, establishing direct connections with the processing system (PS). Users have the flexibility to configure the DPU and adjust various parameters to optimize the utilization of PL resources or enable specific features. For detailed instructions on integrating the DPU into custom AI projects or products, please refer to the corresponding documentation - https://github.com/Xilinx/Vitis-AI/tree/master/dsa/DPU-TRD

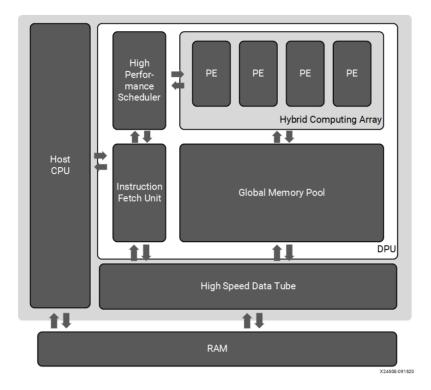

### 3.3.3 DPU Configuration

The DPU is a configurable core that provides various options for managing resource utilization, such as DSP slices, LUT, block RAM, and UltraRAM. Key configuration parameters include:

Figure 3.3: DPUCZDX8G architecture

- Number of cores: A single DPU instance can have up to 4 cores, balancing implementation efficiency with resource usage.

- Architecture: The DPU IP provides architectural choices with different levels of parallelism, such as B512, B800, B1024, B1152, B1600, B2304, B3136, and B4096. The numeric value in the names represents the number of operations per clock cycle, impacting parallelism. Higher parallelism enhances performance but demands more resources for DPU implementation.

- RAM usage: The on-chip memory utilized to enhance performance is a RAM memory responsible for storing weights, biases, and intermediate results. When instantiating the DPU module, you have the flexibility to choose the amount of RAM to reserve. This can be done by selecting either the *High RAM usage* or the *Low RAM usage* option, allowing the users to optimize the memory footprint based on their specific requirements and constraints.

- Channel augmentation: This technique enhances performance by utilizing excess parallelism when the number of input channels is lower than the channel input parallelism of the architecture.

- Depth-wise Convolution: In standard convolution, each input channel is processed individually with a specific kernel, and the results are With depth-wise convolution, it splits into two parts: depth-wise and point-wise. Depth-wise processes channels concurrently, while point-wise combines results with a 1x1 kernel. This boosts performance by utilizing parallelism to evaluate multiple activation maps to be evaluated per clock cycle.

- Average Pool: Average Pooling is a computation that shrinks a matrix by averaging its elements. The matrix is divided into smaller squares, like 2x2 to 8x8. Each square's elements are summed and divided by the square's element count to get the average. This reduces input size, enhancing performance in neural network inference.

- ReLU type: ReLU (Rectified Linear Unit) is an activation function commonly used in neural networks. It transforms negative values to zero while keeping positive values unchanged. There are different variations of ReLU that can be chosen: ReLU, ReLU6, and LeakyReLU.

- **Softmax**: A logistic regression function called the softmax allows for the conversion of any obtained value to probabilities between 0 and 1. Hardware dedicated to this operation is utilized, eliminating the need for the processor to perform it separately.

By customizing these features, users can optimize the DPU implementation for their specific application, finding the right balance between resource utilization and performance. After configuration, the enabled options are saved in an *arch.json* file, which is later used by the Vitis AI tools.

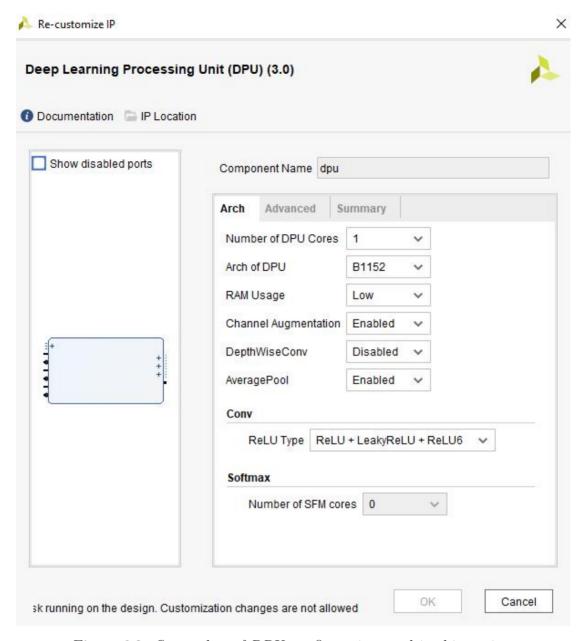

The following are the parameters of the DPU configuration utilized in this project:

| Parameter                 | Value                      |

|---------------------------|----------------------------|

| DPU cores                 | 1                          |

| Arch of DPU               | B1152                      |

| Usage                     | low                        |

| Channel aug-<br>mentation | enabled                    |

| Average Pool              | enabled                    |

| Conv                      | ReLu, Relu6,<br>Leaky Relu |

| Softmax cores             | 0                          |

Table 3.1: DPU parameters in Vivado

Once the configuration process of the DPU is finished, it's crucial to save the enabled options. This ensures the compiler can make accurate selections for instructions during synthesis. The chosen settings are automatically stored in a file named *arch.json*, which contains the configuration data. The *arch.json* file is later utilized within the Vitis AI environment for further processing and utilization.

### 3.3.4 DPU Integration

Once the structure and functionalities of the DPU core have been explained, it is essential to understand the integration process within a project. Vitis AI offers two possible solutions [16].

- → The first approach involves creating a project with VIVADO, the Xilinx software used to design, synthesize, and load hardware systems onto the FPGA.

- $\rightarrow$  The second option is to utilize the Vitis IDE, a comprehensive tool that enables the creation of applications combining software and hardware components.

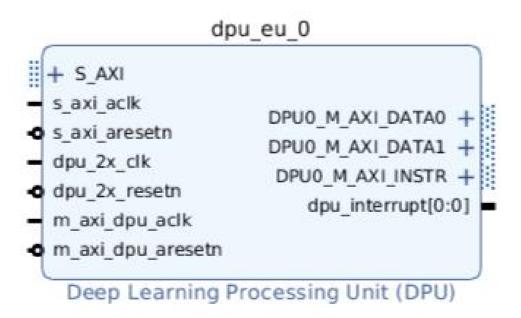

In both cases, it is crucial to consider that the DPU requires communication with the processing system (PS), which is the software environment running on the processor. This communication involves control signals, instructions, and data exchange. To facilitate this task, communication interfaces need to be added, and a communication protocol must be selected. The DPU employs the AXI (Advanced eXtensible Interface) protocol, a burst-based protocol that divides communication into five independent channels: read address, read data, write address, write data, and write response. The architecture includes the following interfaces:

- An **AXI4-lite slave interface** is utilized to receive control data and base addresses where instructions are stored in memory. The received data is stored in internal registers for runtime availability.

- An **AXI4** master interface is used to access the instruction memory based on the received base addresses. It reads the instructions that need to be executed.

- An optional **AXI4** master interface is automatically inserted if the softmax option has been enabled during the configuration process. This interface is responsible for handling the softmax data, ensuring efficient processing of the softmax operation.

• Two **AXI4** master interfaces are utilized to read the data that needs to be processed during execution. The presence of two separate interfaces enables the reading of larger data, maximizing the utilization of DPU parallelism.

In addition to the communication interfaces, integrating the DPU requires considering other signals such as interrupt signals, clocks, and resets. The number of interrupt signals corresponds to the number of cores in the DPU, with each core having its own interrupt signal. Two clocks are needed, one for managing the communication protocol and the other for the internal logic. The frequency of the internal logic clock should be twice that of the communication clock. Similarly, two resets are used, one for communication handling and the other for internal logic. The figure 3.4 shows a diagram of DPU IP with its interfaces.

Figure 3.4: DPU IP with all its interfaces

### Chapter 4

## Tools and Prototyping Environment Utilized

This chapter explains the tools that were used to put the suggested solution into practice. There is a brief description of the history of each tool and how it was applied to the proposed solution under each one.

### 4.1 Xilinx

Xilinx is a renowned technology company that specializes in delivering a diverse range of computer hardware and software solutions [17]. Established in 1984 in Silicon Valley, Xilinx has gained global recognition for its programmable logic devices. Throughout this solution, Xilinx plays a crucial role by providing the majority of the tools utilized in the development process. With a global presence, Xilinx continues to supply its innovative products to customers worldwide.

#### 4.1.1 Vitis AI

An Integrated Development Environment called Xilinx® Vitis AI can be used to speed up AI inference on Xilinx platforms. Throughout the development process, Vitis AI offers resources including ex-

ample designs and tutorials in addition to optimised IP, tools, libraries, and models. Its great efficiency and simplicity of usage enable it to fully realise the AI acceleration potential of Xilinx SoCs and Alveo Data Centre accelerator cards. For more information, refer to section 3.2

#### 4.1.2 Vitis AI DPU

Vitis AI DPU (Deep Learning Processing Unit) is a hardware accelerator specifically designed by Xilinx for deep learning tasks. It is an essential component of the Vitis AI development platform, enabling efficient and high-performance execution of CNNs on Xilinx FPGA platforms. The DPU provides optimized hardware implementations for key CNN operations such as convolution, pooling, and activation functions, resulting in accelerated inference and improved energy efficiency. With its flexible architecture and integration with the Vitis AI toolchain, the Vitis AI DPU empowers developers to deploy and optimize their deep learning models for a wide range of applications, from edge devices to data centers.

The provided article [13], serves as a comprehensive guide for integrating the DPU into a custom platform. It offers step-by-step instructions and explanations on how to successfully integrate the DPU IP into your own hardware design. The guide covers various aspects, including the required software and hardware components, configuration options, and implementation considerations. By following the instructions outlined in the article, developers can effectively integrate the DPU into their custom platforms and leverage its capabilities for efficient and accelerated deep learning inference.

#### 4.1.3 Vitis AI Quantiser

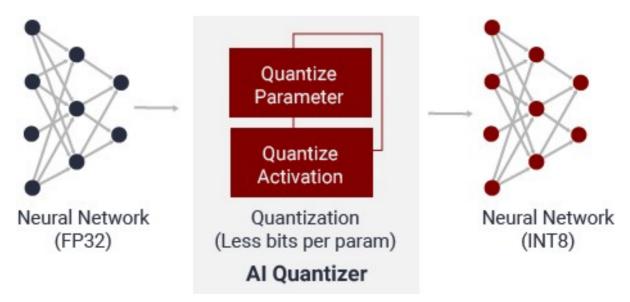

Integer quantization is a technique employed in the deployment of neural networks on Xilinx DPUs to enhance efficiency. By quantizing neural network weights and activations to integer values, various benefits are achieved, including reduced energy consumption, decreased memory usage, and optimized data path bandwidth during inference. This approach optimizes the deployment of neural networks on Xilinx DPUs, resulting in improved overall performance and resource utilization.

Vitis AI Quantizer is a tool provided by Xilinx as part of the Vitis AI development platform [13]. It is designed to facilitate the quantization process of deep neural networks, which is a technique used to reduce the precision of network parameters and activations. By quantizing a network, the precision of numerical values can be reduced from floating-point to fixed-point or integer representations. This results in smaller model sizes and improved inference performance on target hardware. The figure 4.1 shows the Vitis AI Quantiser Framework.

Figure 4.1: Vitis AI Quantizer Framework

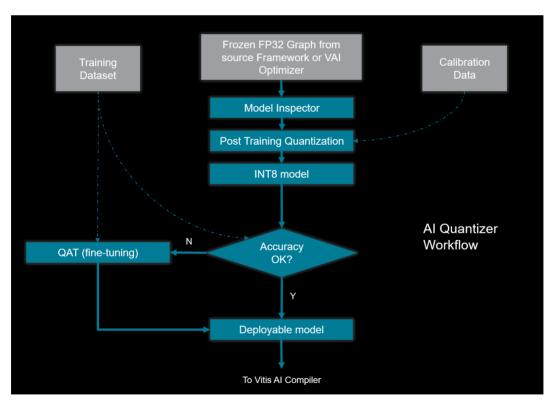

In scenarios where specific network topologies lead to significant accuracy degradation, developers can utilize a technique called Quantization Aware Training (QAT). By leveraging the original training data, QAT enables multiple backpropagation passes to fine-tune quantized weights, minimizing accuracy loss. This approach optimizes the quantization process by considering accuracy impact during training, resulting in improved performance and preserving desired accuracy levels for neural networks. With Vitis AI Quantizer, developers can effectively optimize deep neural network models for Xilinx hardware platforms. The tool reduces precision of network parameters and activations, achieving a balance between model size, inference performance, and resource utilization. This enables efficient and high-performance deep learning inference on Xilinx devices [18]. The overall model quantization flow is detailed in the following figure 4.2.

Figure 4.2: Vitis AI Quantizer Workflow

## 4.1.4 Vitis AI Compiler

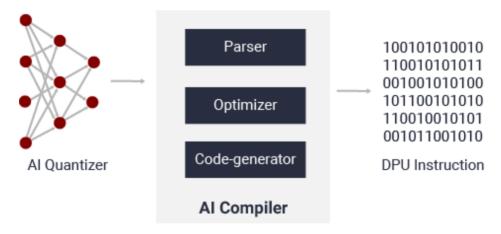

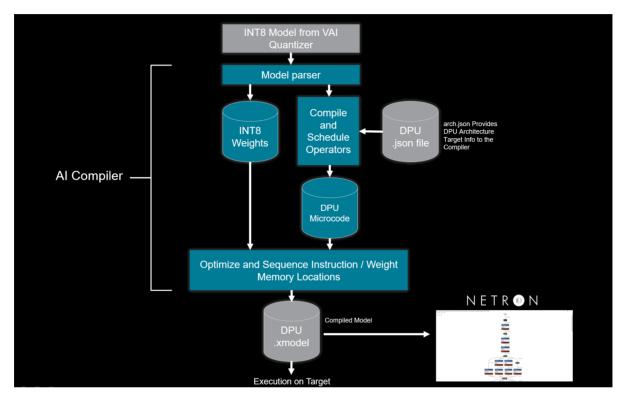

After quantization, the Vitis AI Compiler plays a crucial role in constructing an intermediate representation (IR) of the model, known as Xilinx Intermediate Representation (XIR). This IR consists of separate control and data flow representations, allowing for various optimizations. For example, batch normalization operations can be fused with convolutions to enhance efficiency. The compiler optimizes the graph and partitions it into subgraphs, ensuring that DPU-executable subgraphs are identified and processed accordingly. Architecture-aware optimizations are then applied, and an instruction stream is generated for the DPU subgraph. The optimized graph is serialized into a compiled .xmodel file. [18]. The following figure 4.3 shows the Vitis AI Compiler Framework.

Figure 4.3: Vitis AI Compiler Framework

During the compilation process, a DPU arch.json file is provided to the compiler, which communicates the target DPU architecture. It ensures that the compiled model is compatible with the specific DPU's capabilities. Failure to use the correct arch.json file can result in runtime errors. Therefore, models must be recompiled if they are intended for deployment on a different DPU architecture.

After compiling the model into the .xmodel file, Netron can be used to review the final graph structure and gain insights into the optimized model representation. The following diagram 4.4 illustrates a high-level overview of the Vitis AI Compiler workflow:

Figure 4.4: Vitis AI Compiler Workflow

**NOTE!** The Vitis AI Compiler is an integral part of the Vitis AI toolchain and is included within the VAI Docker environment. However, the source code for the compiler itself is not made available to users. Users can access and utilize the compiler functionality through the provided Vitis AI toolchain, which includes the necessary binaries and libraries for the compilation and optimization of models.

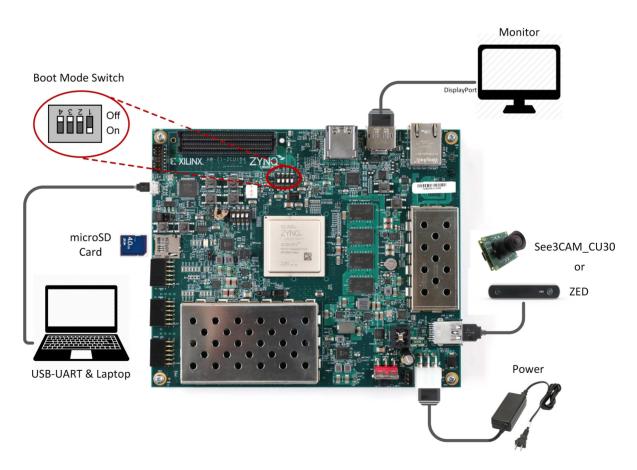

## 4.1.5 ZCU104

The ZCU104 board, developed by Xilinx, is an evaluation platform that utilizes the Zynq UltraScale+ ZU7 device. It offers a comprehensive set of features and interfaces for prototyping and testing various applications, including machine learning. The ZCU104 board provides high-performance processing capabilities, FPGA fabric, integrated peripherals, and connectivity options, making it suitable for a wide range of development projects. This Xilinx user guide [19] describes in detail the features of the ZCU104 evaluation board. This guide can be used for developing and evaluating designs targeting the Zynq UltraScale MPSOC devices, specifically ZCU104 board. The Vitis AI pre-built board images support the ZCU104 interfaces shown in the figure 4.5.

Figure 4.5: Xilinx ZCU104 Evaluation Board and Peripheral Connections

The Xilinx ZCU104 evaluation board incorporates the ZU7 Zynq UltraScale+ device, providing an ideal platform for accelerating machine learning applications. With its mid-range capabilities, the ZCU104 enables developers to kickstart their machine-learning projects efficiently. More detailed information about the ZCU104 board can be found on the Xilinx website. https://www.xilinx.com/products/boards-and-kits/zcu104.html.

## 4.2 User Hardware

The host PC utilized in this process was a desktop computer with the following key specifications:

• Processor: Intel Core I7 Processor

• RAM: 24GB DDR4-2666

• Storage device: M.2 SSD NVMe PCLe Gen3

• Operating system: Ubuntu 18.4.3 LTS

## 4.3 User Software

#### 4.3.1 Docker

Docker is an open-source platform that enables developers to automate the deployment, scaling, and management of applications within isolated containers. Containers are lightweight, standalone environments that encapsulate an application and all its dependencies, including libraries, binaries, and configuration files.

The key components of Docker include:

- **Docker Engine**: The runtime engine that allows you to build, run, and manage containers. It provides the necessary tools and services for container orchestration.

- **Docker Image**: A read-only template that contains the application code, runtime, libraries, and dependencies required to run an application. Images serve as the building blocks for containers.

- **Docker Container**: Containers are isolated environments running applications with their dependencies, ensuring consistency and portability across different systems.

- **Dockerfile**: A text file that contains instructions for building a Docker image. It defines the base image, dependencies, configuration, and other components required to create a reproducible image.

#### Docker for Vitis AI

Docker for Vitis AI is a containerization platform that enables users to create and deploy portable and isolated environments for running Vitis AI applications. By utilizing Docker, users can package their Vitis AI application and its dependencies into a containernthat can be easily distributed and run on any system that supports Docker.

## 4.3.2 Jupyter Notebook

Jupyter Notebook is a browser-based interactive programming environment that enables the execution of programs, including languages like Python, in an interactive manner. It provides a user-friendly interface where code, text, and visualizations can be combined in a single document, making it convenient for data exploration, analysis, and collaboration.

# Chapter 5

# **Model Comparison**

The effectiveness and inference time of four different model architectures was explored in this study for the purpose of classifying chest X-ray images. The chosen architectures were initially pre-trained on large datasets and subsequently fine-tuned using our distinct chest X-ray image dataset.

In this project, RESNET-50, DenseNet-169, VGG-16, and MobileNet were the selected model architectures. These architectures were specifically chosen due to their robustness and track record in successfully addressing classification tasks.

The application of pre-trained weights, learned from training on extensive datasets like ImageNet, was initiated for each model. Subsequently, a fine-tuning process was undertaken using our chest X-ray image dataset. During this process, the basic model layers were frozen, except for the final dense layers, to enable the models to acquire domain-specific features and patterns.

After fine-tuning, the performance of each model is evaluated on both CPU and DPU platforms to assess their effectiveness, accuracy and inference time across different setups. This evaluation provides valuable insights into the potential advantages of leveraging specialized hardware, specifically DPUs, for deep learning tasks. By comparing the performance metrics of the models on CPU and DPU platforms, we can determine the impact of hardware acceleration on their effectiveness. These metrics, such as accuracy, precision, recall, and F1 score, offer insights into the comparative performance of the models under different hardware setups.

Each of the model architectures will be analyzed in five segments, where the details of each respective segment are broken down:-

- 1. Description of the model: It contains a brief description of the model architecture along with its specializations.

- 2. Reason for choosing the model: It contains a logical reason for which the model architecture was chosen for the task.

- 3. Training/Fine-tuning the model: It contains steps and details regarding the training of the model.

- 4. Quantization: The Vitis AI Quantizer tool helps with the quantization process of DNN models, reducing their precision from floating-point to fixed-point representation for improved performance, computational efficiency and resource utilization on Xilinx devices.

- 5. Compiling quantised model to xmodel: Vitis AI platform includes a compiler infrastructure that optimizes and compiles the quantized AI models for deployment on Xilinx FPGAs or SoCs. The compilation process involves transforming the model and generating efficient hardware-specific instructions for accelerated inference.

#### 5.1 RESNET-50

#### 5.1.1 Description

ResNet-50, as part of the ResNet (Residual Network) family, is a CNN architecture. This study employs the '50-layered' version of ResNet, indicating a moderately deep network structure.

It introduces residual connections, allowing information to flow directly across layers. The model consists of several residual blocks, each containing stacked convolutional layers and shortcut connections. These connections enable the learning of residual mappings, alleviating the vanishing gradient problem.

The architecture of ResNet-50 typically includes initial convolutional layers, followed by four stages of residual blocks with different numbers of filters. The spatial resolution of the feature maps decreases as the network deepens, while the number of filters usually doubles at each stage. The final stage involves global average pooling to reduce the spatial dimensions, followed by a fully connected layer for classification. Hence, it is able to extract deep meaningful spatial features from the data.

## 5.1.2 Reason for choosing the model

RESNET-50 is a suitable model for chest X-ray classification due to its deep architecture, pre-trained weights, and transfer learning capabilities. Its depth allows it to capture intricate patterns in X-ray images, while pretraining on large datasets provides general visual representations. The model's residual connections address training challenges, and its success in image classification tasks makes it a promising choice for chest X-ray classification.

## 5.1.3 Training/Fine-tuning the model

After undergoing the fine-tuning process, the pre-trained ResNet-50 model yields the following results:-

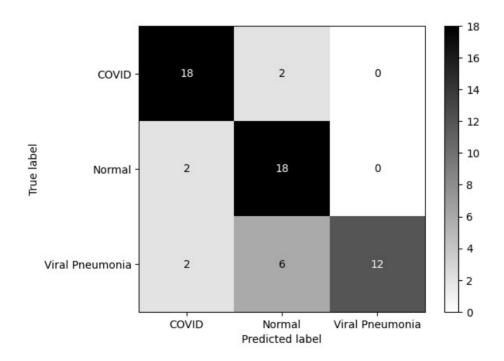

• Model size: 286.8 MB

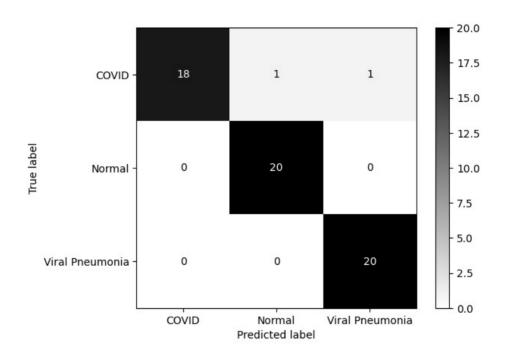

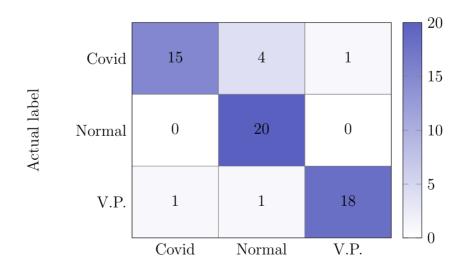

• Evaluation of the fine-tuned model: The confusion matrix 5.1 represents the performance evaluation of a classification model with three classes. The diagonal elements of the matrix indicate the true positive values for each class. Specifically, for Class 1, there are 18 instances correctly classified as positive. For Class 2, there are 18 instances correctly classified as positive. And for Class 3, there are 12 instances correctly classified as positive. The confusion matrix provides a detailed breakdown of the model's accuracy and misclassifications for each class.

Figure 5.1: Confusion Matrix for ResNet-50 model

Table 5.1 presents the classification report for the RESNET-50 model. The classification report provides performance metrics such as precision, recall, F1-score, and support for each class in the classification task. The classification report table shown shows that the average accuracy obtained for each class is 0.80. This means that, on average, the classification model correctly predicts the class labels with an accuracy of 80%.

|                 | Precision | Recall | F1-<br>score | Support |

|-----------------|-----------|--------|--------------|---------|

| COVID           | 0.82      | 0.90   | 0.86         | 20      |

| Normal          | 0.69      | 0.90   | 0.78         | 20      |

| Viral Pneumonia | 1.00      | 0.60   | 0.75         | 20      |

| accuracy        | -         | -      | 0.80         | 60      |

| macro avg       | 0.84      | 0.80   | 0.80         | 60      |

| weighted avg    | 0.84      | 0.80   | 0.80         | 60      |

Table 5.1: Classification Report of ResNet-50 model

## 5.1.4 Quantization

Quantization of the trained model weights using the Vitis-AI quantizer yields the following results:-

• Time taken: 491.09 seconds

• Model size: 95.8 MB

• Evaluation of the Quantized model:

After the quantization process, there have been slight changes in the true positive values of the model as depicted from the table 5.4.Specifically, for Class 1, the true positive count has changed from

Predicted label

Table 5.2: Confusion Matrix for Quantized ResNet-50 model

18 to 17. For Class 2, the true positive count remains the same at 18. However, for Class 3, the true positive count has changed from 12 to 20. Higher true positive values after quantization indicate improved accuracy, as the quantized model correctly identifies more instances from each class.

|                 | Precision | Recall | F1-<br>score | Support |

|-----------------|-----------|--------|--------------|---------|

| COVID           | 0.89      | 0.85   | 0.87         | 20      |

| Normal          | 0.90      | 0.90   | 0.90         | 20      |

| Viral Pneumonia | 0.95      | 1.00   | 0.98         | 20      |

| accuracy        | -         | -      | 0.92         | 60      |

| macro avg       | 0.92      | 0.92   | 0.92         | 60      |

| weighted avg    | 0.92      | 0.92   | 0.92         | 60      |

Table 5.3: Classification Report of Quantized ResNet-50 model

# 5.1.5 Compiling quantised model to xmodel

Compiling the quantized model to xmodel yields the following results: -

• xModel size: 25.1MB

# • Evaluation of the Compiled model:

Predicted label

Table 5.4: Confusion Matrix for Compiled ResNet-50 model

|                 | Accuracy | Precision | Recall | F1-<br>score |

|-----------------|----------|-----------|--------|--------------|

| COVID           | 0.93     | 0.85      | 0.94   | 0.9          |

| Normal          | 0.93     | 0.95      | 0.86   | 0.90         |

| Viral Pneumonia | 0.97     | 0.95      | 0.95   | 0.95         |

Table 5.5: Classification Report of Compiled Resnet-50 model

#### 5.2 DENSENET-169

#### 5.2.1 Description

DenseNet-169 is a convolutional neural network architecture known for its dense connectivity pattern. It consists of 169 layers, making it a deep model. The key characteristic of DenseNet-169 is its dense blocks, where each layer is directly connected to every other layer within the block. This dense connectivity promotes feature reuse and gradient flow, enabling better information propagation throughout the network. By densely connecting layers, DenseNet-169 achieves efficient parameter usage and reduces redundancy. This architecture has shown impressive performance in various computer vision tasks, including image classification, due to its ability to effectively capture fine-grained details and exploit feature correlations.

## 5.2.2 Reason for choosing the model

DenseNet-169 is well-suited for chest X-ray classification due to its dense connectivity, efficient parameter usage, and ability to capture fine-grained details. Chest X-ray images often contain intricate patterns and subtle abnormalities, which can be effectively learned and represented by DenseNet-169's dense blocks. The dense connections promote feature reuse, enabling better gradient flow and information propagation. With its deep architecture and efficient parameter usage, DenseNet-169 can capture the nuances and correlations of chest X-ray abnormalities, leading to accurate classification results. Its success in various computer vision tasks makes it a promising model for chest X-ray classification, particularly in capturing the intricacies of chest pathologies.

## 5.2.3 Training/Fine-tuning the model

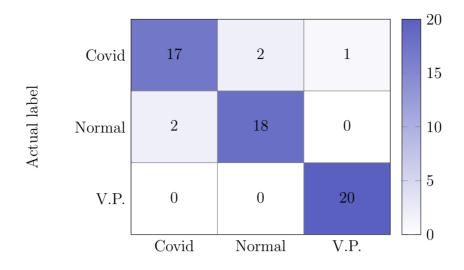

After undergoing the fine-tuning process, the pre-trained DenseNet-169 model yields the following results:-

• Model size: 155.9 MB

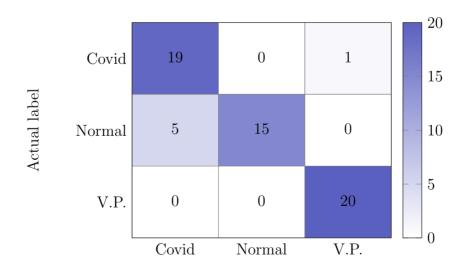

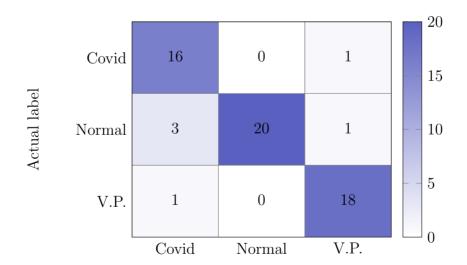

• Evaluation of the fine-tuned model: The confusion matrix represents the performance evaluation of a classification model with three classes. The diagonal elements of the matrix indicate the true positive values for each class. The confusion matrix for a 3-class problem shown in table 5.2 shows true positive values of 18, 20, and 20 for each class.

Figure 5.2: Confusion Matrix for DenseNet-169 model

The classification table 5.6 shows that the average accuracy obtained for each class is 0.97. This means that, on average, the classification model correctly predicts the class labels with an accuracy of 97%.

|                 | Precision | Recall | F1-<br>score | Support |

|-----------------|-----------|--------|--------------|---------|

| COVID           | 1.00      | 0.90   | 0.95         | 20      |

| Normal          | 0.95      | 1.00   | 0.98         | 20      |

| Viral Pneumonia | 0.95      | 1.00   | 0.98         | 20      |

| accuracy        | -         | -      | 0.97         | 60      |

| macro avg       | 0.97      | 0.97   | 0.97         | 60      |

| weighted avg    | 0.97      | 0.97   | 0.97         | 60      |

Table 5.6: Classification Report of DenseNet-169 Model

## 5.2.4 Quantization

Quantization of the trained model weights using the Vitis-AI Quantizer yields the following results:-

• Time taken: 1025.25 seconds

• Model size: 53.9 MB

• Evaluation of the Quantized model:

Predicted label

Table 5.7: Confusion Matrix for Quantized DenseNet model

|                 | Precision | Recall | F1-<br>score | Support |

|-----------------|-----------|--------|--------------|---------|

| COVID           | 0.79      | 0.95   | 0.86         | 20      |

| Normal          | 1.00      | 0.75   | 0.86         | 20      |

| Viral Pneumonia | 0.95      | 1.00   | 0.98         | 20      |

| accuracy        | -         | -      | 0.90         | 60      |

| macro avg       | 0.91      | 0.90   | 0.90         | 60      |

| weighted avg    | 0.91      | 0.90   | 0.90         | 60      |

Table 5.8: Classification Report of DenseNet-169 Quantized Model

## 5.2.5 Compiling quantised model to xmodel

Compiling the quantized model to xmodel yeilds the following results: -

• xModel size: 14.2 MB

• Evaluation of the Compiled model:

Predicted label

Table 5.9: Confusion Matrix for Compiled DenseNet-169 model

|    |      | Recall  | F1-<br>score |

|----|------|---------|--------------|

| 88 | 0.90 | 0.78    | 0.83         |

| 91 | 0.75 | 1.00    | 0.85         |

| 96 | 1.00 | 0.9     | 0.94         |

| (  | 91   | 91 0.75 | 91 0.75 1.00 |

Table 5.10: Classification Report of Compiled DenseNet-169 model

#### 5.3 VGG-16

## 5.3.1 Description

VGG-16 is a convolutional neural network architecture known for its deep and straightforward structure. It consists of 16 layers, including 13 convolutional layers and 3 fully connected layers. VGG-16 follows a simple and uniform design philosophy, where convolutional layers use small 3x3 filters with stride 1 and max pooling layers with 2x2 filters and stride 2. This architecture enables VGG-16 to capture both low-level and high-level visual features effectively. With its deep layers, VGG-16 can learn intricate patterns in images, making it suitable for various computer vision tasks, including image classification, object detection, and segmentation.

## 5.3.2 Reason for choosing the model

VGG-16 can be a suitable model for chest X-ray classification due to its deep architecture and strong feature representation capabilities. Chest X-ray images often contain complex patterns and subtle abnormalities that require capturing fine-grained details. VGG-16's deep structure, with multiple stacked convolutional layers, allows it to learn intricate features and hierarchies of visual information. The use of small filter sizes and max-pooling layers helps capture local and global features effectively. Moreover, VGG-16 has been exten-

sively evaluated and proven successful in various computer vision tasks, including image classification, making it a reliable choice for accurate chest X-ray classification.

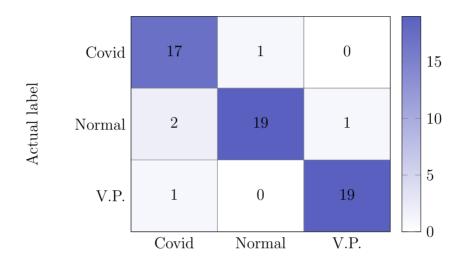

## 5.3.3 Training/Fine-tuning the model

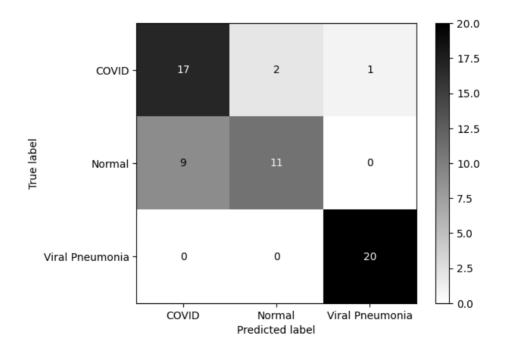

After undergoing the fine-tuning process, the pre-trained ResNet-50 model yields the following results:-

• Model size: 177.6 MB

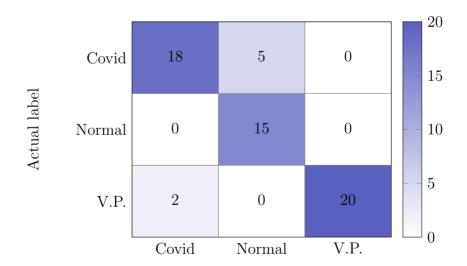

• Evaluation of the fine-tuned model: The confusion matrix for a 3-class problem in figure 5.3 shows true positive values of 14, 20, and 18 for each class.

Figure 5.3: Confusion Matrix for VGG-16 model

The classification table 5.11 shows that the average accuracy obtained for each class is 0.87. This means that, on average, the classification model correctly predicts the class labels with an accuracy of 87%.

|                 | Precision | Recall | F1-<br>score | Support |

|-----------------|-----------|--------|--------------|---------|

| COVID           | 1.00      | 0.70   | 0.82         | 20      |

| Normal          | 0.74      | 1.00   | 0.85         | 20      |

| Viral Pneumonia | 0.95      | 0.90   | 0.98         | 20      |

| accuracy        | -         | -      | 0.87         | 60      |

| macro avg       | 0.90      | 0.87   | 0.87         | 60      |

| weighted avg    | 0.90      | 0.87   | 0.87         | 60      |

Table 5.11: Classification Report of Vgg-16 model

## 5.3.4 Quantization

Quantization of the trained model weights using the Vitis-AI quantizer yields the following results:-

• Time taken: 437 seconds

• Model size: 59.4 MB

• Evaluation of the Quantized model:

Predicted label

Table 5.12: Confusion Matrix for Quantized Vgg-16 model

|                 | Precision | Recall | F1-<br>score | Support |

|-----------------|-----------|--------|--------------|---------|

| COVID           | 0.94      | 0.75   | 0.83         | 20      |

| Normal          | 0.80      | 1.00   | 0.89         | 20      |

| Viral Pneumonia | 0.95      | 0.88   | 0.88         | 20      |

| accuracy        | -         | -      | 0.88         | 60      |

| macro avg       | 0.89      | 0.88   | 0.88         | 60      |

| weighted avg    | 0.89      | 0.88   | 0.88         | 60      |

Table 5.13: Classification Report of Quantized Vgg-16 Model

## 5.3.5 Compiling quantised model to xmodel

Compiling the quantized model to xmodel yeilds the following results: -

• xModel size: 15.2 MB

• Evaluation of the Compiled model:

Predicted label

Table 5.14: Confusion Matrix for Compiled  $Vgg-16 \mod l$

|                 | Accuracy | Precision | Recall | F1-<br>score |

|-----------------|----------|-----------|--------|--------------|

| COVID           | 0.91     | 0.80      | 0.94   | 0.86         |

| Normal          | 0.93     | 1.00      | 0.83   | 0.90         |

| Viral Pneumonia | 0.95     | 0.9       | 0.94   | 0.92         |

Table 5.15: Classification Report of Compiled Vgg-16 model

#### 5.4 MobileNet

#### 5.4.1 Description

MobileNet is a lightweight convolutional neural network architecture designed for efficient and resource-constrained environments, such as mobile devices and embedded systems. It aims to strike a balance between model size and accuracy. It employs depth-wise separable convolutions, which separate the standard convolution operation into depth-wise and point-wise convolutions. This factorization significantly reduces the computational cost and number of parameters while preserving the model's ability to learn meaningful representations. The architecture allows MobileNet to achieve high efficiency and fast inference times, making it suitable for real-time applications and scenarios where computational resources are limited.

## 5.4.2 Reason for choosing the model

MobileNet can be a suitable model for chest X-ray classification due to its lightweight architecture and efficient inference. Chest X-ray classification tasks often require real-time performance and are frequently deployed on resource-constrained devices. MobileNet's design, with depth-wise separable convolutions, significantly reduces the computational complexity and model size while maintaining reasonable accuracy. This efficiency allows for faster inference times and

lower memory requirements, making it well-suited for real-time chest X-ray classification on mobile devices or embedded systems. Despite its compact size, MobileNet can still capture relevant features and patterns in X-ray images, enabling accurate classification of abnormalities with reduced computational overhead.

## 5.4.3 Training/Fine-tuning the model

After undergoing the fine-tuning process, the pre-trained MobileNet model yields the following results:-

• Model size: 40.7 MB

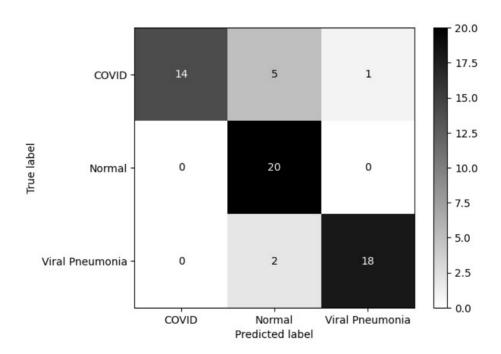

• Evaluation of the fine-tuned model: The confusion matrix for a 3-class problem in figure 5.4 shows true positive values of 17, 11, and 20 for each class.

Figure 5.4: Confusion Matrix for MobileNet model

The table 5.16 below presents the classification report for the RESNET-50 model. The classification report provides performance metrics

such as precision, recall, F1-score, and support for each class in the classification task.

|                 | Precision | Recall | F1-<br>score | Support |

|-----------------|-----------|--------|--------------|---------|

| COVID           | 0.69      | 0.90   | 0.78         | 20      |

| Normal          | 1.00      | 0.60   | 0.75         | 20      |

| Viral Pneumonia | 0.91      | 1.00   | 0.95         | 20      |

| accuracy        | -         | -      | 0.83         | 60      |

| macro avg       | 0.87      | 0.83   | 0.83         | 60      |

| weighted avg    | 0.87      | 0.83   | 0.83         | 60      |

Table 5.16: Classification Report of MobileNet

The classification table shown above shows that the average accuracy obtained for each class is 0.83. This means that, on average, the classification model correctly predicts the class labels with an accuracy of 83%.

#### 5.4.4 Quantization

Quantization of the trained model weights using the Vitis-AI quantizer yields the following results:-

• Model size: 95.8 MB

## • Evaluation of the quantized model:

During the evaluation of the quantized MobileNet model, it was observed that all the testing images were predicted for the label Covid [0], which is deemed inaccurate because of the usage of separable convolution in order to reduce parameters. Information can be lost due to the channel-wise convolution involved in separable convolution. In the case of TensorFlow quantization, it has been noted that this operation resembles the addition of noise to an already trained

network, with the expectation that the model has generalized well. While this approach tends to work effectively and maintain high accuracy for heavier models such as Inception and ResNet, it results in accuracy loss for lightweight models like MobileNet, given their simplicity and lightweight nature.

# Chapter 6

# Description of Workflow

This chapter provides comprehensive step-by-step instructions on utilizing Xilinx Vitis AI to execute multiple DNN models on the ZCU104 Ultrascale MPSoC board. The purpose of integrating various existing tutorials into a single guide is to create a comprehensive resource that covers everything from setting up the environment to running applications on the ZCU104 board. This ensures that users have a consolidated reference for all aspects of working with Vitis AI on the ZCU104 platform.

# 6.1 Tools Execution Process

While providers usually provide documentation for installing development tools, this section serves as a concise guide. Although it is possible to set up and use the tools without this guide, the author shares some observations from their own experience in setting up the tools. To determine the specific hardware platform used for the solution and the testing process, please refer to 4.2.

#### 6.1.1 Vivado 2020.2 HLx edition

Installation instructions for Vivado HLx edition 2020.2 are widely documented and can be found at [20]. When choosing which software to install in this sample, just Vivado is necessary.

#### 6.1.2 Vitis AI

Vitis AI can be installed using a quick start guide [13]. The majority of requirements for successfully installing Vitis AI on the host PC are covered in this article, however, there are a few factors the author highlights for the reader that may facilitate the installation process. The next section of this guide will cover how to set up ZCU104. For information about ZCU104, refer to section 4.1.5.

#### 6.1.3 Petalinux

The "Petalinux Tools Documentation Reference Guide" [21] contains instructions for installing Petalinux. For installation, please refer to this manual. It is nicely written and offers advice on how to resolve common problems that may arise when installing Petalinux tools.

Launching a settings.sh or settings.csh script that additionally checks for the installation of Petalinux tools is recommended as the primary step in setting up the Petalinux working environment. The author notes that this script does not operate in a different terminal window and only applies Petalinux tools path variables to the current terminal session. These paths must be present in the Linux environment's \$PATH variable in order to permanently add Petalinux Tools.

## 6.1.4 Edge AI environment on the ZCU104 board

This subsection is composed of many software packages that are required in order to successfully accelerate the image classification process on the hardware platform and use shell scripts written to ease this process for developers.

It is of utmost importance to note that the installation process may not precisely adhere to the provided instructions. Due to the absence of official guidelines from Xilinx, the hardware configuration employed in this project encountered several errors [22]. Consequently, it is recommended to install any extra dependencies that may not be covered in the current edition of the official Installation guide. It is possible that this situation may improve with subsequent official versions, leading to more comprehensive guidance.

# 6.2 Integration of fine-tuned models with ZCU104

The setup of the ZCU104 board and how to get fine-tuned models to run on ZCU104 are covered in this section and its subsections. The present guide is an updated version of Xilinx's manual UG1414, with a few additional procedures highlighted [13]. As indicated in the introduction of this chapter, the Xilinx guide UG1414 is also replicated here. Each section of this guide includes prerequisites that specify what the user must do or have in order to follow it.

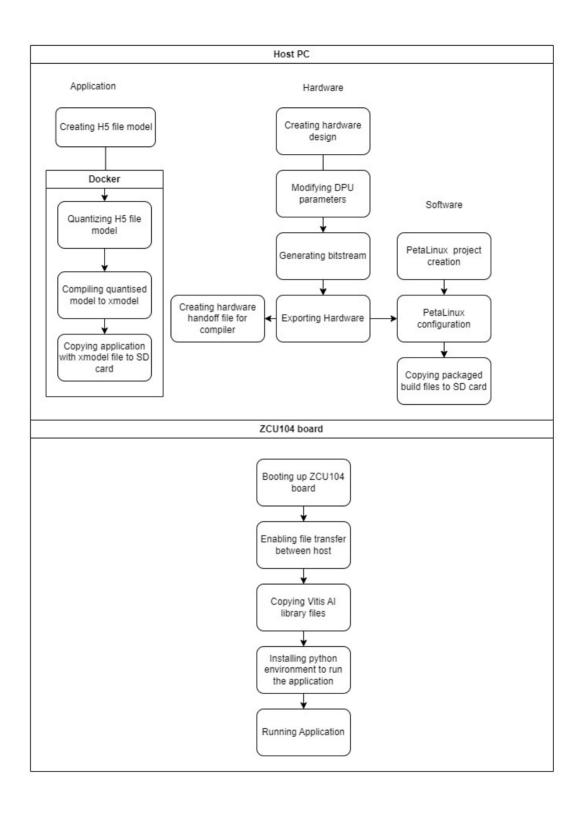

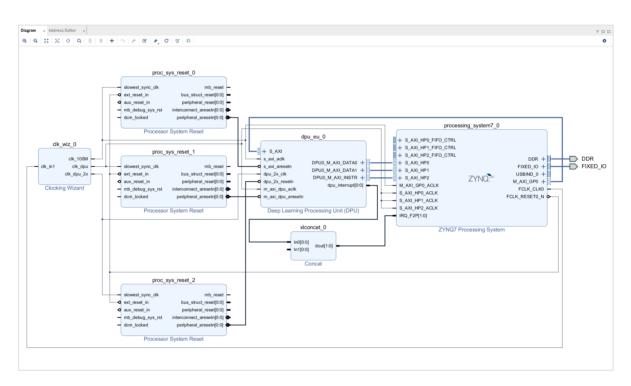

A simplified diagram illustrates the development process for executing fine-tuned models on the ZCU104 board, outlining the key steps and components involved, which can be found in the figure 6.1.

#### 6.2.1 Hardware

The hardware design part employs a guide from Xilinx Vitis Tutorials [23]. Prerequisites for this subsection:

• Vivado Design suite 2020.2 HLx Edition (any edition works)

To create a DPU hardware platform using Vivado 2020.1, follow these steps:

• Set the Vivado environment: In the linux terminal, type:

Figure 6.1: Simplified view of development flow in proposed solution

source <Vivado install path>/Vivado/2020.2/settings64.sh

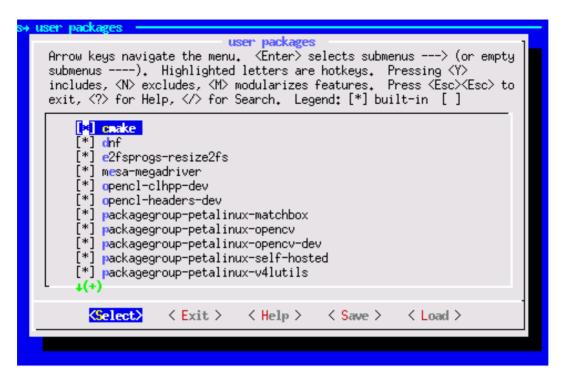

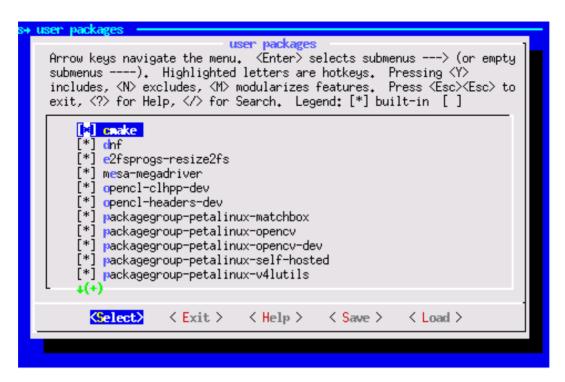

vivado