# REALISATION OF RECIEVER(RX) EQUALIZATION TECHNIQUES TO ENHANCE THE EYE-DIAGRAM FOR USB 3.2 AT 10 Gb/s SPEED

# THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENT FOR THE DEGREE OF MASTER OF TECHNOLOGY

IN

#### VLSI DESIGN & MICROELECTRONICS TECHNOLOGY

THESIS SUBMITTED BY

#### **DEBADITTYA DAS**

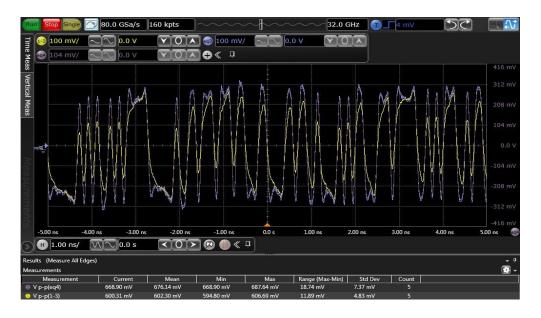

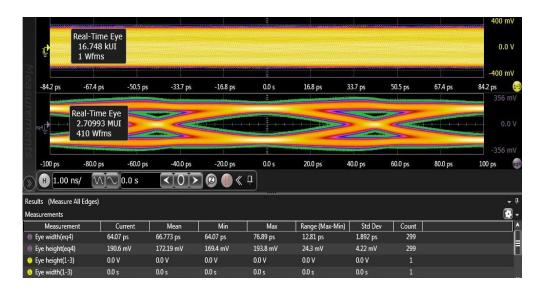

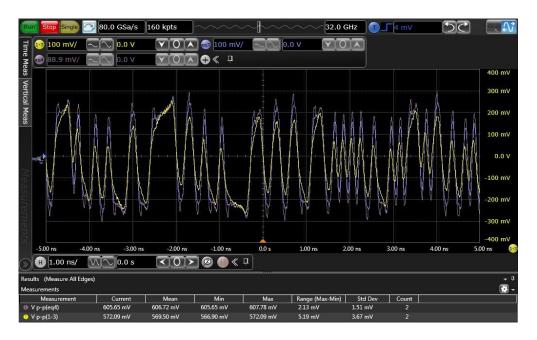

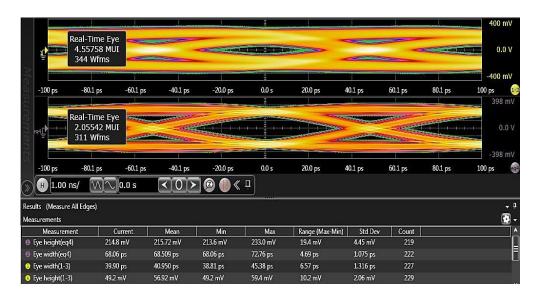

University Registration No.: 154104 of 2020-2021

Exam Roll No.: M6VLS23005

Class Roll No.: 002010703002

UNDER THE SUPERVISION OF

DR. SAYAN CHATTERJEE

# DEPARTMENT OF ELECTRONICS AND TELECOMMUNICATION ENGINEERING

JADAVPUR UNIVERSITY

**JUNE 2023**

#### FACULTY OF ENGINEERING AND TECHNOLOGY

# ELECTRONICS AND TELECOMMUNICATION ENGINEERING JADAVPUR UNIVERSITY

### **CERTIFICATE OF RECOMMENDATION**

This is to certify that the thesis entitled "REALISATION OF RECIEVER(RX) EQUALIZATION TECHNIQUES TO ENHANCE THE EYE-DIAGRAM FOR USB 3.2 AT 10 Gb/s SPEED" has been carried out by DEBADITTYA DAS (University Registration No: 154104 of 2020-2021) under my guidance and supervision and be accepted in partial fulfillment of the requirement for awarding the degree of "MASTER OF TECHNOLOGY IN VLSI DESIGN AND MICROELECTRONICS TECHNOLOGY". The research results presented in this thesis have not been included in any other paper submitted for the award of any degree to any other Institute or University.

Balaji G.K.

DR. SAYAN CHATTERJEE BALAJI GK

INTERNAL THESIS SUPERVISOR EXTERNAL THESIS SUPERVISOR

DEPT. OF ELECTRONICS AND STAFF ENGINEER, HARDWARE

TELECOMMUNICATION ENGINEERING ENGINEERING

JADAVPUR UNIVERSITY WESTERN DIGITAL CORP.

KOLKATA-700032 BANGALORE- 560103

-----

DR. MANOTOSH BISWAS PROF. ARDHENDU GHOSAL

HEAD OF THE DEPARTMENT DEAN

DEPT. OF ELECTRONICS AND FACULTY OF ENGINEERING

TELECOMMUNICATION ENGINEERING AND TECHNOLOGY

JADAVPUR UNIVERSITY JADAVPUR UNIVERSITY

KOLKATA-700032 KOLKATA-70003

# FACULTY OF ENGINEERING AND TECHNOLOGY ELECTRONICS AND TELECOMMUNICATION ENGINEERING JADAVPUR UNIVERSITY

## **CERTIFICATE OF APPROVAL**#

The foregoing THESIS is hereby approved as a creditable study of an Engineering Subject carried out and presented in a manner of satisfactory to warrant its acceptance as a pre-requisite to the DEGREE for which it has been submitted. It is to be understood that by this approval, the undersigned do not necessarily endorse or approve any statement made, opinion expressed, or conclusion drawn therein but approve the THESIS only for the purpose for which it has been submitted.

Committee on final examination for the evaluation of the Thesis

| (Signature of the Internal Supervisor) |

|----------------------------------------|

| Balaji G.K.                            |

| (Signature of the External Supervisor) |

|                                        |

| (Signature of the Examiner 1)          |

| (Signature of the Examiner 2)          |

# FACULTY OF ENGINEERING AND TECHNOLOGY

# **ELECTRONICS AND TELECOMMUNICATION ENGINEERING** JADAVPUR UNIVERSITY

# CERTIFICATE OF RECOMMENDATION

This is to certify that the thesis entitled "REALISATION OF RECIEVER(RX) EQUALIZATION TECHNIQUES TO ENHANCE THE EYE-DIAGRAM FOR USB 3.2 AT 10 Gb/s SPEED" has been carried out by DEBADITTYA DAS (University Registration No: 154104 of 2020-2021) under my guidance and supervision and be accepted in partial fulfillment of the requirement for awarding the degree of "MASTER OF TECHNOLOGY IN VLSI DESIGN AND MICROELECTRONICS TECHNOLOGY". The research results presented in this thesis have not been included in any other paper submitted for the award of any degree to any other Institute or University.

Soyan Chatteju 12/6/23

DR. SAYAN CHATTERJEE

INTERNAL THESIS SUPERVISOR

DEPT. OF ELECTRONICS AND

TELECOMMUNICATION ENGINEERING

KOLKATA-700032 Dr. Sayan Chatterjee

Electronics & Telecomm. Engg. Dept. Adaypur University, Kolkata - 700032

DR. MANOTOSH BISWAS

HEAD OF THE DEPARTMENT

DEPT. OF ELECTRONICS AND

TELECOMMUNICATION ENGINEERING

JADAVPUR UNIVERSITY

KOLKATA-700032

Balaji GK.

BALAJI GK

EXTERNAL THESIS SUPERVISOR

STAFF ENGINEER, HARDWARE

**ENGINEERING**

WESTERN DIGITAL CORP.

BANGALORE-560103

PROF. ARDHENDU GHOSAL

DEAN

**FACULTY OF ENGINEERING**

AND TECHNOLOGY

JADAVPUR UNIVERSITY

KOLKATA-700032

MANOTOSH BISWAS

Professor and Head Electronics and Telecommunication Engineering Jadavpur University, Kolkata - 32

# FACULTY OF ENGINEERING AND TECHNOLOGY ELECTRONICS AND TELECOMMUNICATION ENGINEERING JADAVPUR UNIVERSITY

# DECLARATION OF ORIGINALITY AND COMPLIANCE OF ACADEMIC ETHICS

I hereby declare that this thesis contains literature survey and original research work done by the undersigned candidate, as a part of his degree of "MASTER OF TECHNOLOGY IN VLSI AND MICROELECTRONICS TECHNOLOGY". All information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that as required by these rules and conduct, I have fully cited and referenced all materials and results that are not original to this work.

#### Thesis Title

# REALISATION OF RECIEVER (RX) EQUALIZATION TECHNIQUES TO ENHANCE THE EYE-DIAGRAM FOR USB 3.2 AT 10 Gb/s SPEED

#### **DEBADITTYA DAS**

University Registration No.: 154104 of 2020-2021

Exam Roll No.: M6VLS23005

Class Roll No.: 002010703002

# DEPT. OF ELECTRONICS AND TELE-COMMUNICATION ENGINEERING FACULTY OF ENGINEERING AND TECHNOLOGY JADAVPUR UNIVERSITY

KOLKATA - 700032

**INDIA**

| Date: |  |  |

|-------|--|--|

|       |  |  |

### **ACKNOWLEDGEMENT**

I would like to begin by expressing my heartfelt gratitude to Dr. Sayan Chatterjee, my M.Tech supervisor. I want to acknowledge the profound influence he has had on nurturing my passion and inquisitiveness for the theory and practicality of high-speed serial communications, including the realm of USB communication. His unwavering patience, extensive knowledge, and exceptional rapport with his students consistently bring out their utmost potential. I am truly grateful for the opportunity to conduct my master's thesis under the guidance of such a competent and esteemed professor.

Furthermore, I extend my heartfelt gratitude to the members of the Hardware Engineering team (FPG) at SanDisk for generously sharing their knowledge relevant to my thesis's topics throughout my internship. I would like to offer special thanks to Balaji GK, my internship and external guide, for engaging in enthusiastic discussions, imparting industry-level insights pertaining to my subject, and providing invaluable assistance during experimental endeavors. Working alongside these exceptional professionals significantly contributed to my personal and professional growth.

I also wish to express my gratitude to Dr. Manotosh Biswas, the Head of the Department, for consistently extending a helping hand whenever needed, demonstrating unwavering support throughout my academic journey.

Most importantly, I am profoundly grateful to my parents for their unwavering encouragement in pursuing my passion and for their constant belief in my abilities. With their enduring love and support, I have been able to reach the heights I stand at today.

| Date: |                  |

|-------|------------------|

|       | (DEBADITTYA DAS) |

#### **ABSTRACT**

In recent years, technology scaling and the demand for higher data rates have driven innovation at high-speed interfaces. To meet the requirements of ultra-low power and high-speed data rate signaling, integrated systems-on-chip have become essential components in modern computing systems. While traditional parallel links have been used for a long time, controlling the skew between clocks and data lanes in the link becomes increasingly challenging with faster data rates. To address this issue, faster serial links with reduced pin count and area have emerged as an alternative. High-speed serial IO standards like PCI-e, SATA, USB, TBT, DP, HDMI, and M-PHY have replaced traditional parallel links like PCI, serving multiple applications such as processor-to-processor or processor-to-peripheral communication.

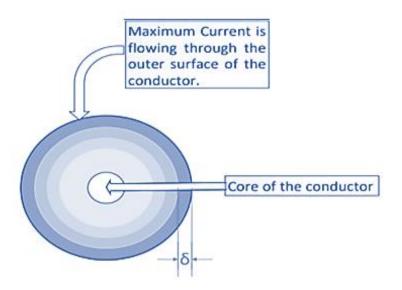

A typical highspeed serial communication consists of two blocks namely the transmitter (TX) block and the receiver (RX) block and a medium through which the communication happens known as channel. However, as the data rates increase, these channels behave as lossy transmission lines due to different factors like skin effect, crosstalk, internal resistance of the transmission line, Inter-Symbol Interference and dielectric absorption of signals which severely degrades the transmitted data symbols.

To mitigate these losses, various techniques can be employed, such as using low-loss dielectric materials, optimizing the conductor size and spacing, employing shielding to reduce interference and crosstalk, and using equalization. Out of these, equalization being the most widely used technique in the industry postproduction. Equalization techniques are used at both the transmitter (TX) and the receiver (RX) end of the communication to compensate for signal distortion due to losses in the channel.

This thesis concentrates mainly on the realization and comparison of various techniques of equalization applied at the receiver (RX) end of communication for widely used serial highspeed communication protocol named USB (specifically USB 3.2). Presently, various industry standard equalization techniques and even the combination of two or more equalization techniques at the receiver (RX) end is studied, discussed, and performed in a lab environment to conclude as of which of these equalization techniques produces the best eye-diagram by compensating for the losses that occur in the channel at the industry level. All these studies are performed at a data rate of 10 Gb/s.

#### **ABBREVIATIONS**

PCI-e Peripheral Component Interconnect express

SATA Serial Advanced Technology Attachment

**USB** Universal Serial Bus

**TBT** Thunderbolt

**DP** Decentralized Periphery

**HDMI** High-Definition Multimedia Interface

**M-PHY** MIPI Physical layer

**PCI** Peripheral Component Interconnect

IO Input/Output

**SerDes** Serializer/Deserialize

**OEM** Original Equipment Manufacturer

**SSP** Super Speed Plus

**PAM** Pulse Amplitude Modulation

NRZ Non-Return-to-Zero

CTLE Continuous Time EqualizationDFE Decision Feedback EqualizationFFE Feed Forward Equalization

IC Integrated Circuits

PCB Printed Circuit Boards

SCSI Small Computer Systems Interface ISA Industry-Standard Architecture

**PCMCIA** Personal Computer Memory Card Industry Association

HSTL High-Speed Transistor Logic

SSO Simultaneous Switching Outputs

DMT Discrete Multitone Transmission

DAC Digital to Analog Converter

ADC Analog-to-Digital Converter

FEC Forward Error Correction

**BER** Bit Error Rate

**CP PLL** Charged Pump Phase Locked Loop

LC-VCO Inductance Capacitance Voltage Controlled Oscillator

ISI Inter Symbol Interference

HPC High-Performance Computing

**AI** Artificial Intelligence

**TSMC** Taiwan Semiconductor Manufacturing Company Ltd.

**AVIPSA** Automated Validation of Internet Security Protocol and Applications

HDL Hardware Description LanguageRFI Radio Frequency Interference

**CMOS** Complementary Metal-Oxide Semiconductor

**ESD** Electrostatic Discharge **DDR** Double Data Rate

**ADS** Advance Design Systems

LE Linear Equalizer

CDR Clock Data Recovery

PFD Phase-Frequency Detector

**LF** Loop Filter

PWM Pulse-Width Modulation VNA Vector-Network-Analyzer

**HFSS** High-Frequency Structure Simulator

PLL Phase- Locked Loop

**USB-IF** Universal Serial Bus Implementers Forum

**USB-PD** USB Power Delivery

PHY Physical Layer

**LFPS** Low-Frequency Periodic Signaling

SSC Spread Spectrum Clocking

EMI Electromagnetic Interference

SNR Signal-to-Noise Ratio

VNA Vector Network Analyzer

NEXT Near End Cross Talk

FEXT Far End Cross Talk

DJ Deterministic Jitter

DCD Duty Cycle Distortion

HPJ High Probability Jitter

**RJ** Random Jitter

**DDJ** -Data Dependent Jitter

SJ Sinusoidal Jitter

PJ Periodic Jitter

UUGJ Uncorrelated Unbounded Gaussian JitterCBGJ Correlated Bounded Gaussian Jitter

UI Unit Interval FB Feedback Filter

**PFAG** Pulse Function Arbitrary Generator

**DUT** Device Under Test

CLB Compliance Load Board

SMA Subminiature Version A

CP Compliance Patterns

**PRBS** Pseudo Random Binary Sequence

EW Eye Width EH Eye Height

# **CONTENTS**

| Acknowledgement                                        | v              |

|--------------------------------------------------------|----------------|

| Abstract                                               | vi             |

| Abbreviations                                          | vii-viii       |

| Chapter 1. Introduction                                | 1-3            |

| Section 1.1 Overview                                   | 1              |

| Section 1.2 Motivation                                 | 1-2            |

| Section 1.3 Objectives                                 | 2              |

| Section 1.4 Structure of the Work                      | 3              |

| Chapter 2. Literature Review                           | 4-16           |

| Section 2.1 Overview                                   | 4              |

| Section 2.2 High Speed Serial Link                     | 4-9            |

| Section 2.2.1 Brief History of High-Speed Serial Links | 4-5            |

| Section 2.2.2 Serial Vs parallel Communication         | 5-6            |

| Section 2.2.3 SerDes Architecture and Applications     | 6-7            |

| Section 2.2.4 Channel Noises                           | 8              |

| Section 2.2.5 Latency                                  | 8-9            |

| Section 2.2.6 Differential Signaling                   | 9-10           |

| Section 2.3 Universal Serial Bus (USB)                 | 10-12          |

| Section 2.4 Equalization Techniques                    | 12-16          |

| Chapter 3. Architecture of High Speed SerDes           | 17-33          |

| Section 3.1 Data Transmission                          | 17-18          |

| Section 3.2 Types of Data Transmission                 | 18-21          |

| Section 3.2.1 Parallel Transmission                    | 18-20          |

| Section 3.2.2 Serial Transmission                      | 20-21          |

| Section 3.3 Modes of Data Transmission                 | 21-22          |

| Section 3.4 Significance of Serial Communication       | 23             |

| Section 3.5 Introduction to High Speed SerDes          | 23-25          |

| Section 3.6 Transmitter (TX)                           | 25-29          |

| Section 3.6.1 Phase Locked Loop (PLL) Clock Generator  | 25-26          |

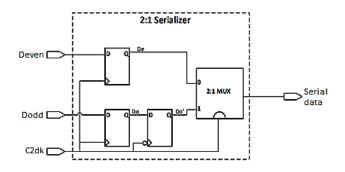

| Section 3.6.2 Serializer                               | 26-27          |

| Section 3.6.3 Transmitter (TX) Equalization            | 27-28.         |

| Section 3.6.4 Driver<br>Section 3.7 The Channel        | 28-29<br>29-30 |

|                                                        | 30-33          |

| Section 3.8 Receiver (RX)                              |                |

| Section 3.8.1 Receiver (RX) equalization               | 30-31          |

| Section 3.8.2 Clock and Data Recovery (CDR)            | 31-32          |

| Section 3.8.3 Descrializer                             | 32-33          |

| Section 3.8 Summary                                    | 33             |

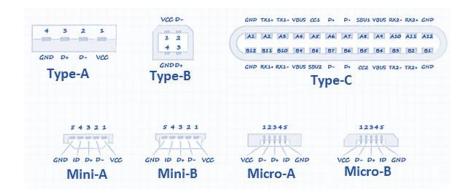

| Chapter 4. Universal Serial Bus (USB)-3.2                                                             | 34-53          |

|-------------------------------------------------------------------------------------------------------|----------------|

| Section 4.1 Introduction                                                                              | 34             |

| Section 4.2 Data Transfer in USB                                                                      | 34-35          |

| Section 4.3 Advantages of USB                                                                         | 35-36          |

| Section 4.4 USB Standards                                                                             | 36-39          |

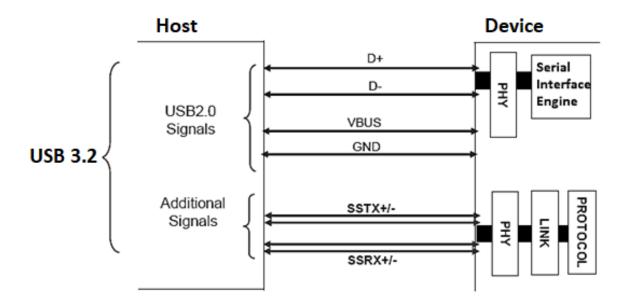

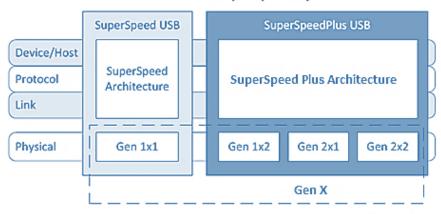

| Section 4.5 Architectural Overview of USB 3.2                                                         | 40             |

| Section 4.6 Architectural Differences Between USB 3.2 and USB 2.0                                     | 41-42          |

| Section 4.7 USB 3.2 System Description                                                                | 43-53          |

| Section 4.7.1 Introduction                                                                            | 43-44          |

| Section 4.7.2 Mechanical                                                                              | 44-45          |

| Section 4.7.3 Power Standards and Management                                                          | 45-47          |

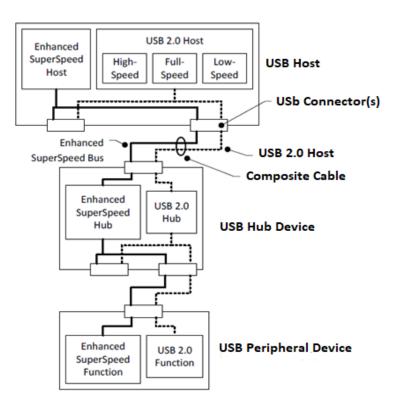

| Section 4.7.4 Enhanced SuperSpeed Bus Architecture                                                    | 47-49          |

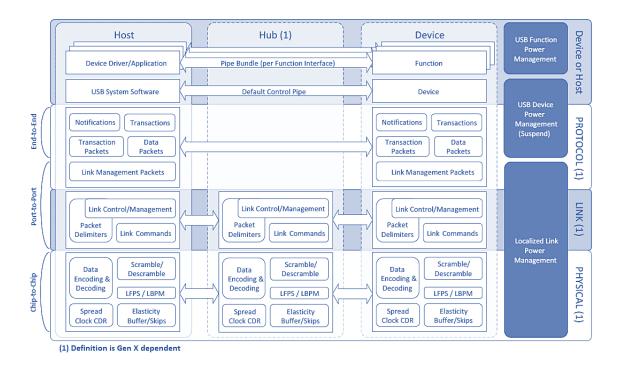

| Section 4.7.5 Physical Layer                                                                          | 49-50          |

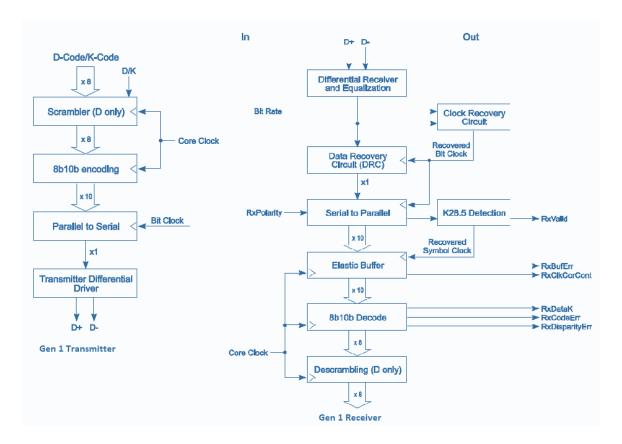

| Section 4.7.6 Gen 1 Physical Layer                                                                    | 50-51          |

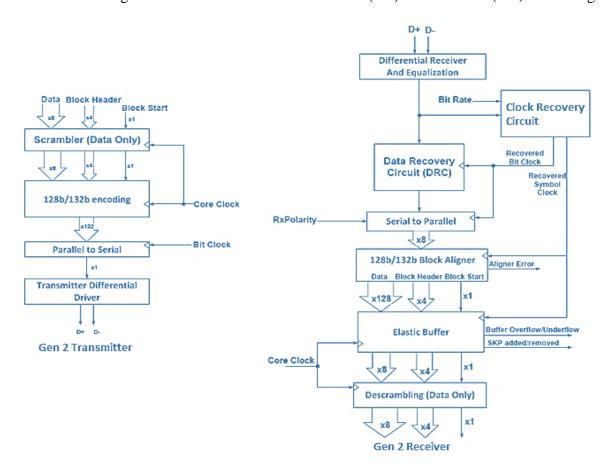

| Section 4.7.7 Gen 2 Physical Layer<br>Section 4.8 Conclusion                                          | 51-52<br>53    |

| Section 4.8 Conclusion                                                                                | 33             |

| Chapter 5. Equalization Techniques for USB 3.2                                                        | 54-70          |

| Section 5.1 Channel Impairments                                                                       | 54-62          |

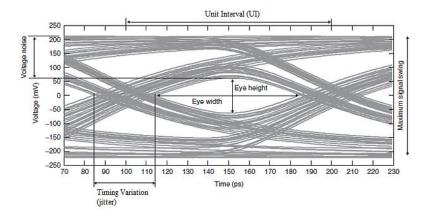

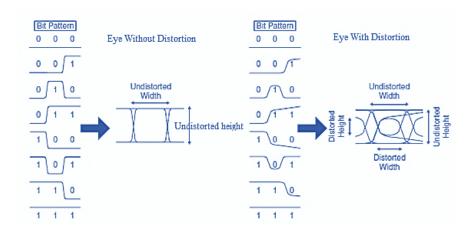

| Section 5.2 Eye-diagram                                                                               | 63-64          |

| Section 5.3 Need of Receiver (RX) Equalization                                                        | 65             |

| Section 5.4 Receiver (RX) Equalization Techniques                                                     | 65-70          |

| Section 5.5 Conclusion                                                                                | 70             |

| Chapter 6. Measurement And Results                                                                    | 71-95          |

| Section 6.1 Introduction                                                                              | 71             |

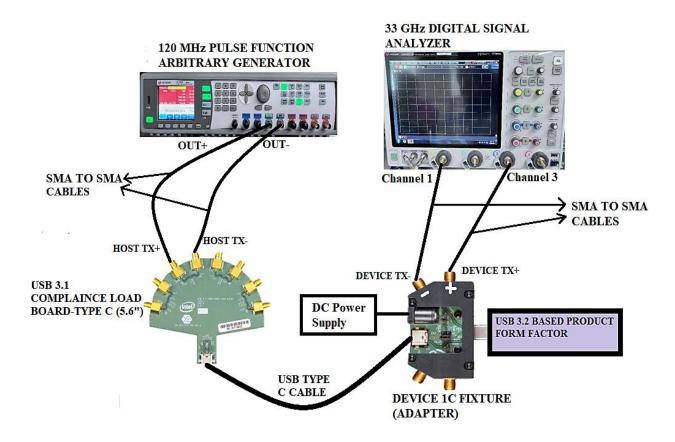

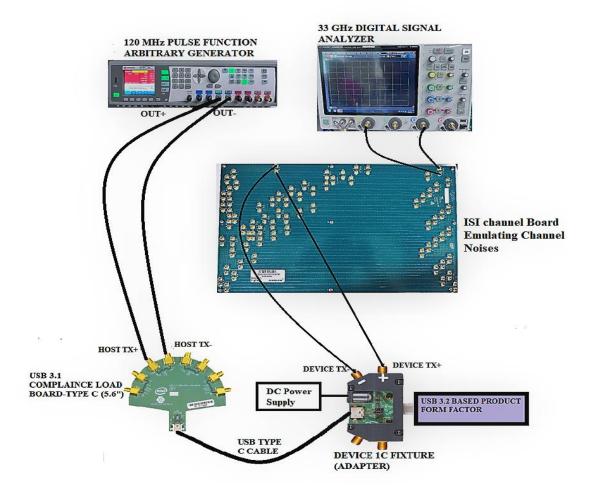

| Section 6.2 Measurement Setup                                                                         | 72-74          |

| Section 6.3 Working of the measurement setup                                                          | 74-75          |

| Section 6.4 Measurement procedure                                                                     | 75-76          |

| Section 6.5 Observations and Results                                                                  | 76-92          |

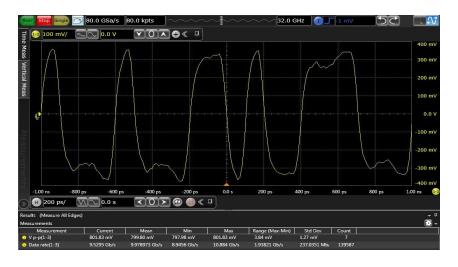

| Section 6.5.1 Behaviour of Channel with No loss                                                       | 77             |

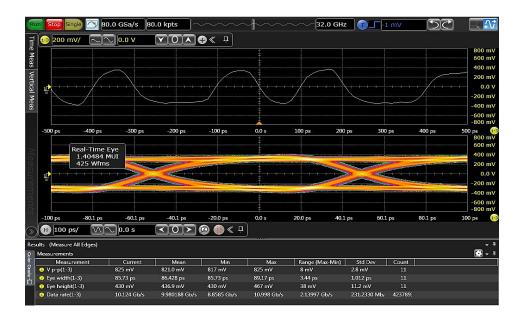

| Section 6.5.2 CTLE equalization at receiver (RX) end                                                  | 77-80          |

| Section 6.5.3 FFE equalization at receiver (RX) end                                                   | 80-82          |

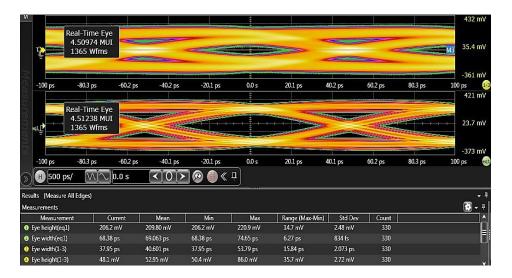

| Section 6.5.4 DFE equalization at receiver (RX) end                                                   | 82-84          |

| Section 6.5.5 CTLE & FFE equalizations at receiver (RX) end                                           | 85-87          |

| Section 6.5.6 DFE & FFE equalizations at receiver (RX) end                                            | 87-89          |

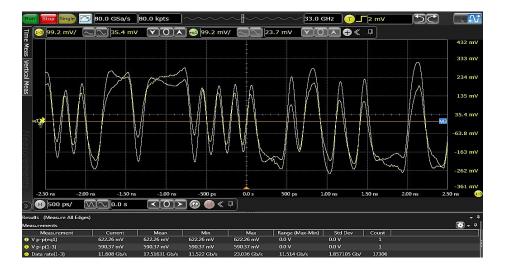

| Section 6.5.7 CTLE, FFE & DFE equalizations at receiver (RX) end<br>Section 6.6 Tabulation of Results | 90-92<br>93-95 |

| Section 6.6 Tabulation of Results                                                                     | 93-93          |

| <b>Chapter 7. Conclusion and Future works</b>                                                         | 96-97          |

| Section 7.1 Conclusion                                                                                | 96-97          |

| Section 7.2 Future Works                                                                              | 97             |

| Bibliography                                                                                          | 98-102         |

# Chapter 1

## Introduction

# 1.1 Chapter Overview

The transmitter (TX) and receiver (RX) circuits in high-speed serial links use physical medium for communication between the device I/O interface and the host I/O interface and vice-versa. These channels are specifically designed for high-speed operation and are utilized to send and receive data. The channel through which the data is transmitted is referred to as the medium, and in an optimal scenario, it would be represented by a wire behaving as a short circuit. However, as data rates escalate, the wires begin to operate as lossy transmission lines, which can lead to severe degradation of the transmitted data symbols. To counteract these non-idealities caused by the channel, equalization is a widely used technique. [1]

This chapter focuses on the motivation behind the use of different equalization techniques used in USB based serial communication to compensate for the losses to the data signal during transmission. Also, the objectives of using these equalization techniques during validation process of USB based products post-production to ensure the proper transfer of data between the device and host is discussed briefly. Lastly, the structure of the thesis work that is carried out is discussed to give reader an idea of the flow of this thesis paper.

#### 1.2 Motivation

The progress in semiconductor processing technology has enabled processors to handle vast amounts of data. To take full advantage of this development, I/O links must also increase their bandwidth while minimizing the impact on pin count, area, and power consumption. Traditional parallel links have been in use in circuits for a long time, but with faster data rates, controlling the skew between clocks and data lanes in the link becomes difficult. A viable alternative is to use faster serial links, which require fewer pins and less area [2]. High-speed serial I/O standards such as PCI-e [3], HDMI [4], and USB [5], have replaced traditional parallel links and are utilized in multiple applications, such as processor-to-processor or processor-to-peripheral communication. Serial I/O communication poses some challenges, including channel loss, Inter-Symbol Interference (ISI), crosstalk, and increased complexity in the receiver (RX) to facilitate clock recovery from the data stream [2].

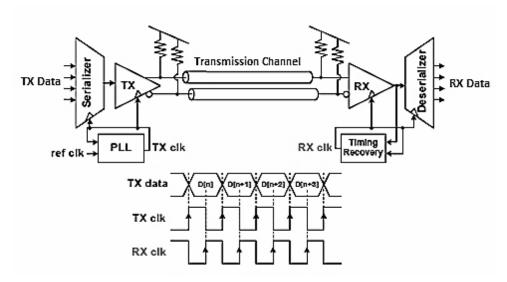

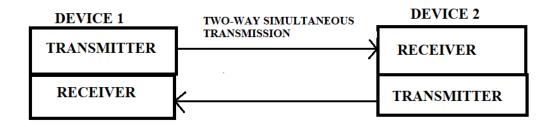

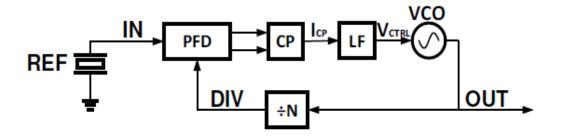

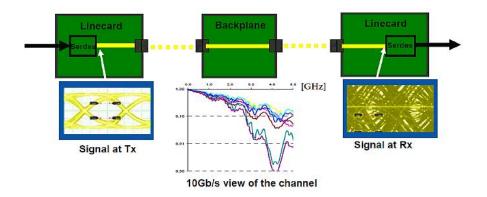

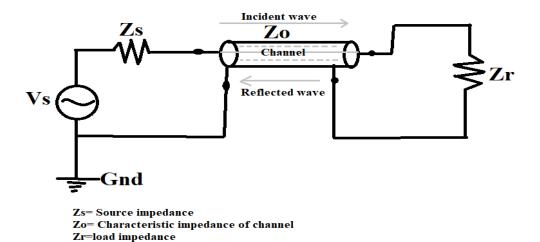

Fig.1.1: High speed serial IO link [2].

The diagram in Figure 1.1 displays the primary constituents of a standard high-speed serial link (SerDes). As there is a constraint on the number of I/O pins in chip packages and printed circuit boards, a transmitter (TX) converts incoming parallel data into a serial format, while a receiver (RX) converts high-speed serial data into parallel data [2]. The data signals that are transmitted via these channels are affected by the channel loss, ISI, cross-talks etc. that causes the signals to lose the amplitude. This is the reason behind the application of equalization in both transmitter (TX) and receiver (RX) end. Equalization boosts the amplitude of the high frequency component of the signal to compensate for the loss during transmission.

# 1.3 Objectives

There are different industry accepted equalization techniques which are used to validate the highspeed serial link communication between the host and device and vice versa.

- This thesis concentrates on comparison of different receiver (RX) equalization techniques and different combinations of those techniques. The comparison is based on eye-diagrams and signal amplitude obtained from the data signals passing through the channel.

- The objective of this thesis is to have a better understanding of equalization and more specifically receiver (RX) equalization for USB standard-based product validation at a high speed of 10 Gb/s and conclude finally as to which equalization technique works the best to mitigate the channel losses and helps to study the communication link in a better way.

- The objective of this thesis is also to give the reader an overall perspective of the factors taken into consideration while validating an USB standard-based product in any industry which deals with high-speed serial link communication.

#### 1.4 Structure of Work

In this section, the outline of the thesis work is mapped with brief introduction about each of them.

#### • Chapter 2. Literature Review:

This chapter contains brief reviews of various thesis papers, journals, book chapters, books and publications related to High-speed serial links, Equalization techniques and USB. These papers have inspired and supported the thoughts required to complete this thesis paper.

#### • Chapter 3: Architecture of High Speed SerDes:

This chapter describes the fundamental concept and architecture of High- speed SerDes. Different blocks and their constituents and their operations are covered in detail.

#### • Chapter 4: USB-3.2:

This chapter concentrates mainly on the USB-3.2 and everything about its architecture and other necessary topics that will help the reader to understand the focus of this work. This chapter also compares the USB 3.2 with its predecessors.

#### • Chapter 5: Equalization Techniques:

This chapter discusses different equalization techniques on both the transmitter (TX) and the receiver (RX) end. But the focus will be on the equalization techniques on the receiver (RX) end.

#### • Chapter 6: Measurement and Results

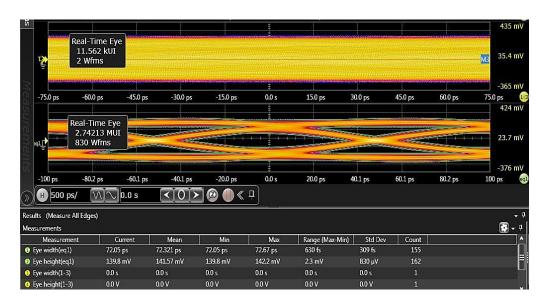

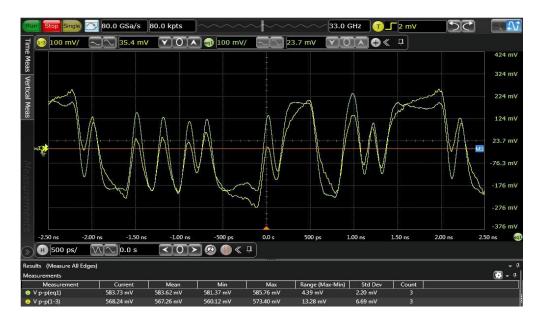

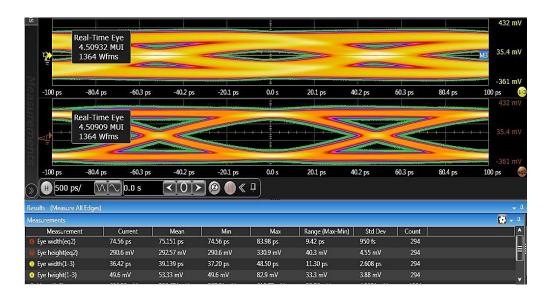

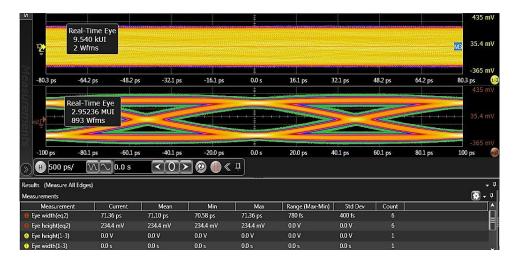

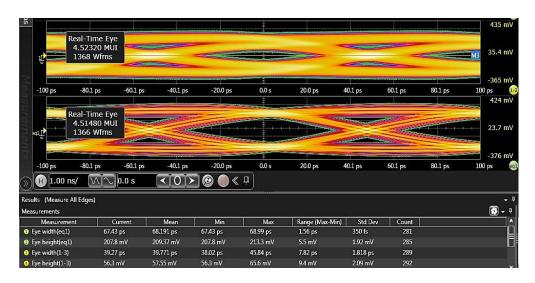

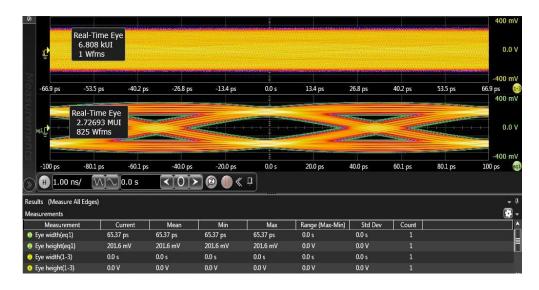

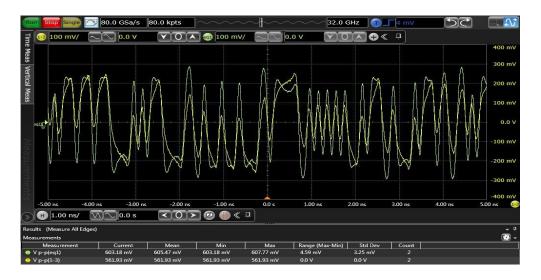

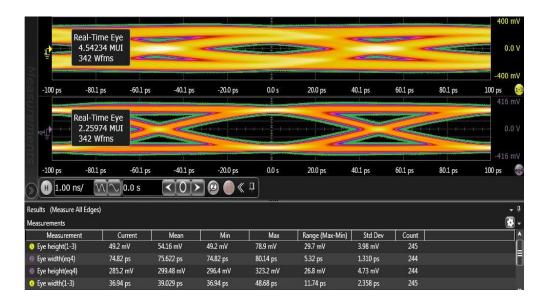

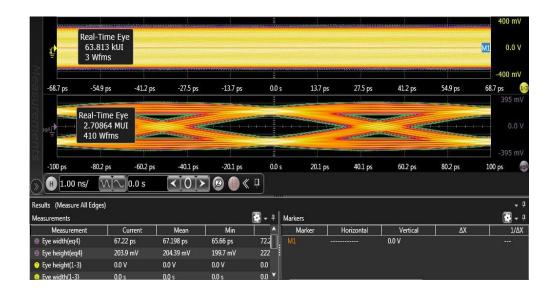

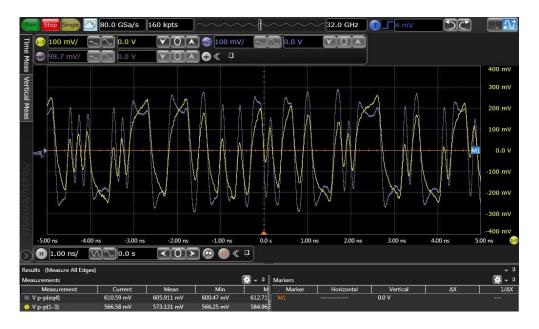

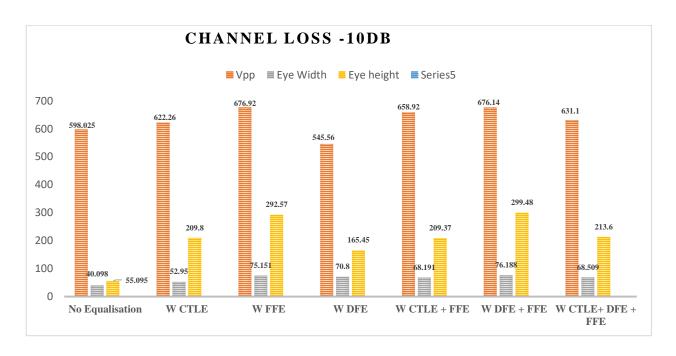

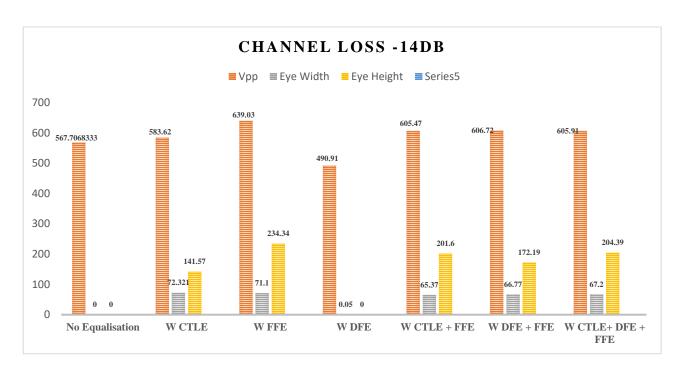

This chapter contains information about the measurement set-up and the different eye-diagrams obtained when various equalization techniques are implemented, and data signals are sent via channel.

#### • Chapter 7: Conclusion and Future Works

This chapter concludes all the findings of the work carried out and the future works that can possibly be accepted and applied by the industry.

# Chapter 2

### **Literature Review**

# 2.1 Chapter Overview

This chapter contains detailed review of different book chapters, papers, journals related to topics like data transmission, high speed serial link, SerDes architecture, different versions of USB and equalization. These documents fueled the knowledge required to complete this thesis. Section 2.2 presents a brief history of high-speed serial links, its comparison with its parallel counterpart, challenges related to channel losses in high-speed communication, differential signaling and SerDes Architectures and Applications. Section 2.3 contains review of different papers related to analysis of USB 3.2 architecture, analysis of predecessor versions and their physical layers and architectures. Section 2.4 finally, contains brief review of different research works having information about different equalization techniques, their significance, why and where they are used in both transmitter (TX) and receiver (RX) block and proposed ideas to increase the equalizer's efficiency by putting additional circuitry or by enhancing the existing circuit.

#### 2.2 High Speed Serial Link

## 2.2.1 Brief History of High-Speed Serial Links

In paper [6] it is mentioned that in the past, circuit design primarily relied on Transistor-Transistor Logic (TTL). More complex integrated circuits (ICs), such as multi-bit registers and counters, were created by discrete gate ICs communicating with each other using parallel communication on printed circuit board (PCB) assemblies. However, the alignment of these circuits for external communication was challenging. As a result, serial ports became the standard for communication between boxes in early computers. Over time, alignment issues were resolved, and high-speed parallel printer ports became more common. Parallel technologies, such as Industry-Standard Architecture (ISA) [7], Small Computer Systems Interface (SCSI) [8], Peripheral Component Interconnect (PCI) [9], and Personal Computer Memory Card Industry Association (PCMCIA) [10], evolved. Despite these advancements, serial technology remained prevalent. Ethernet and Token Ring became popular in many applications, with the latter adapted to work on category 5 (Cat 5) wire. Parallel technologies faced challenges in accommodating new interface demands, and standards like PCI 33 evolved into PCI 66 to support more exotic signaling. However, attempts to support parallel technology, such as using low-swing standards like High-Speed Transistor

Logic (HSTL), were not very successful. Meanwhile, Ethernet speeds increased from 10 Mb to 100 Mb/s, making it highly desirable for desktop use.

[6] also mentioned that around the same time, the fractional phase detector was introduced, which boosted serial interface speeds to the multi-gigabit range. This made serial technology a strong contender, especially as a backplane technology. As serial pin count and simultaneous switching outputs (SSO) improved, multi-gigabit serial became the preferred option on PCB assemblies, ultimately replacing parallel technology.

### 2.2.2 Serial Vs parallel Communication

In [11], the author discussed an elaborated comparison between serial and parallel communication based on few parameters as follows:

| Parame<br>ters    | Serial<br>Communication                                                                                                                                                                        | Parallel<br>Communicati<br>on                                                                                                                              |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit transmission  | Serial transmission involves the transfer of a single bit of data per clock pulse.                                                                                                             | Parallel transmission involves the transfer of 8 bits of data per clock pulse.                                                                             |

| Performance       | Due to the transfer of only one bit per clock pulse in serial transmission, its performance is typically slower than that of parallel transmission, which can transfer 8 bits per clock pulse. | Parallel transmission is generally considered to be more efficient in performance than serial transmission because it can transfer 8 bits per clock pulse. |

| Complexity        | Serial transmission is typically less complex than parallel transmission.                                                                                                                      | Parallel transmission is generally considered to be more complex than serial transmission.                                                                 |

| Wiring Complexity | Serial communication typically requires less channel and less wiring resulting in less wiring complexity.                                                                                      | Parallel communication has more wiring and channels and is more complex than serial communication.                                                         |

|                  |                                                                                                                                                                | Parallel communication on     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

|                  | Serial communication is less susceptible to noise and signal degradation as compared to parallel communication since the data are transmitted via same channel | the other hand is more        |

|                  |                                                                                                                                                                | susceptible to noise and      |

| Signal Integrity |                                                                                                                                                                | signal degradation because    |

| Signal integrity |                                                                                                                                                                | each bit is transferred on    |

|                  |                                                                                                                                                                | separate wires which causes   |

|                  |                                                                                                                                                                | crosstalk between the data    |

|                  |                                                                                                                                                                | signals                       |

| Data Rates       | Can achieve higher data rates                                                                                                                                  | Parallel communication links  |

|                  | compared to parallel                                                                                                                                           | cannot achieve higher data    |

|                  | communication, particularly over                                                                                                                               | rates for long distance       |

|                  | long distances because the signals                                                                                                                             | communication because of      |

|                  | are less degraded by noise.                                                                                                                                    | lossy channels.               |

|                  | Serial Transmission is preferred for                                                                                                                           | Parallel Transmission is      |

| Preference       | long distance transmission                                                                                                                                     | preferred only for short      |

|                  | long distance transmission                                                                                                                                     | distance.                     |

| Cost Efficiency  | Serial transmission requires only a                                                                                                                            | Parallel transmission         |

|                  | single link, making it relatively easy                                                                                                                         | typically requires multiple   |

|                  | to implement without incurring                                                                                                                                 | links, resulting in higher    |

|                  | significant costs. As a result, it is                                                                                                                          | implementation costs and      |

|                  | often considered to be a cost-                                                                                                                                 | making it less cost-efficient |

|                  | efficient option                                                                                                                                               | than serial transmission.     |

# 2.2.3 SerDes Architecture and Applications

According to [12], when evaluating SerDes devices, many system designers focus solely on speed and power consumption without considering the internal architecture of the SerDes and how it processes data. However, the internal architecture of the SerDes can greatly impact system parameters such as topology, protocol overhead, data formatting and flow, latency, clocking and timing requirements, and the need for additional buffering and logic, which can ultimately affect system cost, performance, and efficiency.

Also [12], said that there are four distinct SerDes architectures that have evolved over the years to address specific system design issues: parallel clock SerDes, 8b/10b SerDes, embedded clock

bits (also known as start-stop bit) SerDes, and bit interleaving SerDes. The inner workings of these architectures, their differences were explored and demonstrated how each is suited to specific applications in today's industry.

In paper [13] it is presented a high-speed wireline communication system implementation utilizing Discrete Multitone (DMT) transmission. The study included a theoretical analysis of channels typically employed for SERDES chip-to-chip communication, highlighting the benefits of DMT technology, such as improved spectral efficiency and simplified transceiver design due to DMT's pseudo-narrowband characteristics. Simulation results demonstrated that DMT can achieve higher data rates than traditionally used non-return-to-zero (NRZ) and pulse-amplitude modulation (PAM) techniques, even with typical channel correction circuitry such as continuous-time linear equalizers (fs) and decision-feedback equalizers (DFEs). Additionally, a combined bit-loading/power allocation and transmit side equalization algorithm is presented to improve the system's data rate and reduce its bit error rate. The measurement results in [13] included a demonstration of a digital-to-analog converter (DAC) and analog-to-digital converter (ADC) test bed operating under realistic conditions for chip-to-chip communication with a data rate exceeding 250 GB/s, including sufficient overhead for forward-error-correction (FEC) coding needed to reduce the bit-error rate (BER).

As IoT and Cloud Computing continue to evolve, the data center is experiencing an increase in bandwidth demands, resulting in the development of new 112 Gb/s electrical interface standards for wireline communication. To maintain compatibility with existing 56 Gb/s standards, PAM4 is the chosen signaling method. Paper [14] presented the design and implementation of a 112 Gb/s PAM4 wireline receiver (RX) test-chip, which was implemented in FinFET technology. The receiver (RX) 's architecture included a four-stage continuous-time linear equalizer (CTLE), a peaking capacitance buffer, a 56 GSa/s time-interleaved 7-bit SAR ADC, DSP, and adaptation loops.

The study in [15], reported the design of a high-performance 3 GHz charge pump phase-locked loop (CP PLL) in TSMC 28nm CMOS technology, featuring a low phase noise LC voltage-controlled oscillator (LC-VCO) and high accuracy charge pump (CP). The paper [15] also addressed nonideal effects and provides corresponding solutions for CP and LC-VCO. Post-layout simulation results indicated that the PLL can achieve 0.86 ps rms jitter and a power consumption of 13 mW at 3 GHz.

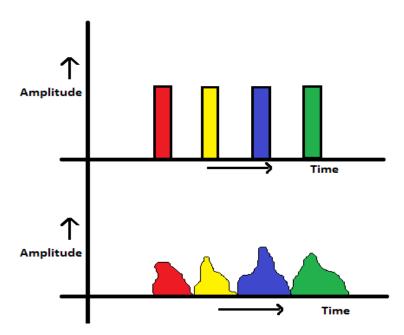

#### 2.2.4 Channel Noises

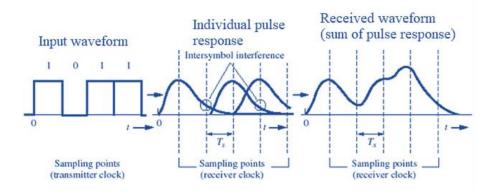

Paper [16] mentioned that the communication industry is continually evolving towards higher speeds, lower power consumption, and bigger data rates. While Ethernet has reached its peak, optical interconnects have been integrated into electronic devices and chips to support multigigabit rates, and wireless telecommunications are transitioning towards the 5G era. However, these advancements have resulted in new challenges such as crosstalk, refraction, and Inter-Symbol Interference (ISI) that can affect Signal Integrity. Maintaining Signal Integrity is crucial for researchers involved in designing high-speed and big data systems. [16] also mentioned that ISI is an unavoidable problem in both wireless and wired systems, where reflections of signals and multipath propagation cause ISI. One of the most effective ways to combat ISI is equalization. As a signal travels from the transmitter (TX) to the receiver (RX), it is distorted by the channel and other noises. The equalizer's job on the receiver (RX) end is to use filters to recover the original signal from the distorted signal. Equalization is widely used to mitigate ISI distortion in optical, PCB backplanes, and cable channels, among other applications. Fig.2.1 gives an oversight of ISI effect

Fig. 2.1: Effect of Inter symbol Interference on data bits [16].

## **2.2.5** Latency

Paper [17] considered throughput and latency to be two critical factors in context of High-Performance Computing (HPC), Artificial Intelligence (AI), and high-frequency trading applications, particularly for larger capacitive loads. The latency part, which must be low for such applications to perform effectively was under the limelight. To reduce overall latency without

affecting the Serializer/Deserializer (SerDes) throughput, the function of each transceiver component and implemented circuits that address latency was examined. Some conventional transceiver blocks had been replaced with a proposed architecture that significantly reduced associated latency. Paper [17] also offered a detailed account of the implementation, including circuit simulation up to the extracted netlist level. A 20Gb/s transceiver using Taiwan Semiconductor Manufacturing Company Ltd. (TSMC) 28nm HPC+ technology was developed, focusing solely on the transmitter (TX) portion and as a result, Significant latency reduction was observed as compared to another conventional transmitter (TX)s.

#### 2.2.6 Differential Signaling

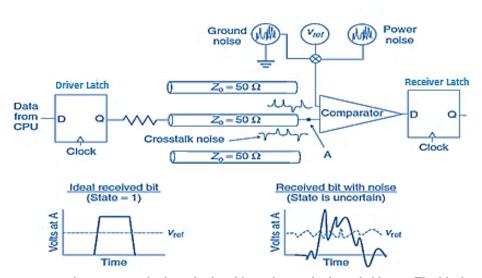

In paper [18] it is mentioned that a technique called single-ended signaling is utilized where a dedicated transmission line is used for each bit on the bus. Signal integrity maintenance, however, becomes challenging due to the noise generated by digital systems, crosstalk, and nonideal current return paths with higher data rates. In single-ended signaling, the bus clock receives each data bit transmitted on a single transmission line. The received waveform is compared to a reference voltage  $V_{ref}$ , and a logic 1 is latched in if the voltage is greater than  $V_{ref}$ , otherwise, it is latched in as a logic 0. If the magnitude of the noise coupled onto the driver, receiver (RX), transmission lines, reference planes, or clock circuits is significant, the relationship between the transmitted waveform and  $V_{ref}$  can be distorted, resulting in bit errors. How noise can cause uncertainty in determining a logic 0 or 1 is depicted in Figure 2.1.

Fig. 2.2: How system noise can severely degrade signal integrity on single-ended buses. The ideal versus noisy receiver (RX) voltages compared to the reference voltage [18].

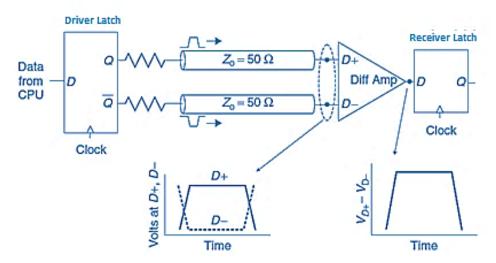

Also [18] mentioned a method that significantly mitigates the impact of system noise is to use a pair of transmission lines for each bit on the bus. The two transmission lines are driven in opposite directions (180 degrees out of phase) in the odd mode, and the voltage difference between them is utilized to restore the signal at the receiver (RX) with the aid of a differential amplifier. This method is commonly known as differential signaling and is shown in Figure 2.2.

Fig. 2.3: Differential signaling where each bit is transmitted from the driver to a receiver (RX) using a pair of transmission lines driven in the odd mode. The signal is recovered at the receiver (RX) with a differential amplifier [18].

## 2.3 Universal Serial Bus (USB)

In paper [19] it is mentioned that the use of USB 2.0 device controllers in electronic devices such as mobile devices, external hard drives and gaming controllers has become very common, which calls for the need to develop an efficient USB 2.0 device controller architecture to address the battery life concerns in current devices. Explanation on the functionality of a USB 2.0 device controller and the main reason behind its power inefficiency was given. Thereafter, an architecture that employed clock gating techniques and a fine-grained power gating approach based on data traffic to enhance power efficiency was presented. The design was based on the open-source USB 2.0 device controller soft-core from the Open Cores Organization.

In paper [20], an analysis of why USB 3.0 is a perfect upgrade from its predecessor was made. The USB 3.0 technology offers faster transmission speeds of up to 5 Gb/s, which is ten times faster than USB 2.0 (480 Mb/s). This increased speed translates to reduced transmission times for data. Other features of USB 3.0 include reduced power consumption and backward compatibility with USB 2.0. In November 2008, the USB 3.0 Promoter Group completed the specification of version 3.0 and transitioned it to the USB Implementers Forum (USBIF), which is the managing body of

USB specifications. This move made the specification available to hardware developers for implementation in future products. One of the new features of USB 3.0 is the "SuperSpeed" bus that provided a fourth transfer mode at 5.0 Gb/s. Although the raw throughput is 4 Gb/s, the specification deemed it reasonable to achieve 3.2 Gb/s (0.4 Gb/s or 400 Mb/s).

Paper [21] mentioned USB as a widely used interface for connecting external computer peripherals. For high-speed data transfer, dedicated hardware implements all the functions of the USB interface. It is a standard for wired connection between two electronic devices, with a maximum speed of 5Gb/s. The cable has a connector at either end, with one end being the same across all USB cables, while the other end is specific to the mobile device. The USB standard has evolved over time, with different versions including USB 1.0, 1.1, USB 2.0, and USB 3.0. The USB Host Controller manages the transmission, reception, and flow control of packets on the bus. Investigation on the architecture of USB 3.0, including its different layers and power management is finally done.

In [22], a secure USB mechanism that prevented leakages of authentication data and eliminated the need to compare authentication data for smart human care services, which has been a significant issue with existing flash drives was proposed. The proposed mechanism ensured confidentiality, integrity, authentication, and access control and protects data from impersonation, man-in-the-middle, replay, and eavesdropping attacks by malicious attackers. Formal verification using the AVISPA tool confirmed the security of the proposed mechanism. Therefore, it was expected that a safer and more secure USB flash drive can be produced using the mechanism proposed.

Paper [5] focused on the design of the physical layer of USB3.0 with Super Speed capability, which included the PCI express and PIPE interface. The design in this paper [5], enabled data to be transferred serially from transmitter (TX) to receiver (RX) at 2.5 Gb/s and generated a clock that ran at a frequency of 125MHz to transfer data in parallel interfaces. The authors also proposed an architecture for the USB3.0 physical layer, which was implemented using Verilog HDL in Xilinx Vivado 2017.4.

In [23], the radio frequency interference (RFI) caused by the universal serial bus 3.0 connector to a nearby antenna was investigated. A model of the connector radiation as an equivalent stripline-fed slot antenna, which is based on analyzing the common mode current path on the connector structure was also proposed. This model allowed replacing the original connector radiation source with an equivalent magnetic dipole source that is directly correlated with the physical quantity on

the connector. Reciprocity theorem to use the equivalent dipole source for predicting the coupled noise power to the antenna was applied in [23]. The proposed model and mechanism are validated using full-wave simulation and measurement. Application of the magnetic dipole source for estimating RFI in a real laptop system was demonstrated.

In paper [24], the impact of mechanical tolerances on skew in USB 2.0 cables was examined in. A full-wave simulation of the cable cross section was used to determine the contribution of tolerances to skew. Using a fractional factorial experimental design, the contributing factors and interaction terms were identified, and Monte Carlo simulations were conducted to investigate each factor's sensitivity to skew. By employing the design of experiments approach, the relationship between mechanical tolerances and skew was recognized. Furthermore, a systematic approach was used to determine the relationship between skew and emission. The results indicated that a net skew of approximately 20-30 ps resulted in a 4-5 dB increase in emission above 350 MHz.

According to [25], The USB 3.2 specification defined the latest iteration of the USB industry standard. It outlined the protocol definition, bus management, and programming interface required to develop systems and peripherals that adhere to this standard. USB 3.2 was designed to improve the performance of USB 3.1 by adding dual-lane support to the USB Type-C cable and connector, thereby providing more bandwidth for devices like Solid State Drives and High-Definition displays. The specification referred to Enhanced SuperSpeed as a set of features or requirements that apply to USB 3.x bus operation. Differences from USB 3.0's SuperSpeed features or requirements were identified as Superspeed Plus (or SSP) features or requirements. The primary goal of USB 3.2 was to enable devices from different vendors to interoperate in an open architecture while leveraging the existing USB infrastructure, such as device drivers and software interfaces. The specification was meant to enhance the PC architecture, from portable and business desktop environments to simple device-to-device communications. It was intended to give OEMs and peripheral developers enough flexibility for product versatility and market differentiation without losing compatibility or carrying obsolete interfaces.

# 2.4 Equalization Techniques

The study in [26], focused on the operation of a 4Gb/s serial channel over copper wires. To cancel out the frequency-dependent attenuation caused by skin-effect resistance in copper wires, a 4GHz FIR equalizing filter was incorporated into a differential transmitter (TX). The equalizer achieved a flat frequency response to within 5% over the 200MHz to 2GHz bandwidth, even over wires with high-frequency attenuation of 6dB. Most of the transmitter (TX) operates at 400MHz, except

for the final stage. The transmitter (TX) output stage uses a stable 10-phase 400MHz clock to sequence an array of drivers that implement the FIR filter. The concept of digital-signal equalization was presented in [26], the system design and circuit design of the equalizing transmitter (TX) was described too, and finally, simulation results from a 0.5mm CMOS transmitter (TX) operating at 4Gb/s were presented.

To address limitations in data transmission caused by modal dispersion in fiber-optic links, [27] proposed two different equalizer implementation approaches to improve transmission capacities. The equalizer's building blocks, including a multiplier cell, a delay line, and an output buffer stage, are fully integrated on a 0.18-µm CMOS process. In [27] comparison between performance of a passive LC delay line and an active inductance peaking delay line for continuous-time tap-delay implementation against process variation and power consumption were made. Additionally, a delay-locked loop was proposed to counter delay variations caused by changes in the process corner. After transmission through a 500-m multimode-fiber channel, a 10-Gb/s nonreturn-to-zero signal is received, and signal impairment due to differential modal delay was successfully compensated using both feed-forward equalizers.

A 7-tap 40 Gb/s feed forward equalizer (FFE) is presented in the [28], which has been fabricated using a 65 nm standard CMOS process. Broad banding and calibration techniques were implemented to ensure high-speed operation while keeping power consumption low. The chip consumed 80 mW from a 1 V supply, and featured ESD protection for 40 Gb/s I/Os, as well as an inexpensive plastic package to bring it closer to commercial viability. The tap delay frequency response variation was measured to be less than 1 dB up to 20 GHz, and the tap-to-tap delay variation was less than 0.3 ps. The chip exhibited more than 50% vertical and 70% horizontal eye opening from a closed input eye. The use of a CMOS process allowed for further integration of this core into a decision feedback equalizer or a clock and data recovery/demux based receiver (RX).

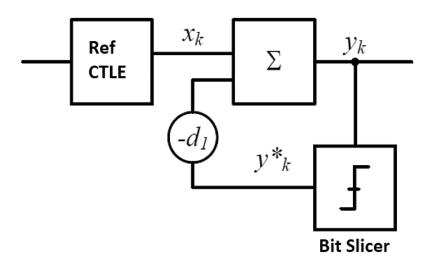

In [1], equalization techniques for mitigating Inter-Symbol Interference (ISI) in high-speed communication links were discussed. The paper covered both transmit and receive equalizers and included the presentation of high-speed circuits for implementing them. Also, in [1], it was demonstrated that a digital transmit equalizer was the easiest to design, while a continuous-time receiver (RX) equalizer usually delivered better performance. Decision feedback equalizer (DFE) was described, and the loop latency issue was addressed. Additionally, techniques for adaptively setting the equalizer parameters were also presented.

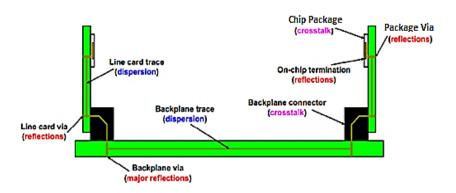

In [29], considerations and decisions involved in designing equalization circuits for USB 3.0 SuperSpeed transceivers were outlined. Different interconnect channels and their electrical characteristics, the USB 3.0 specification requirements that impacted equalizer optimization, the parameters that defined equalizer behaviour and their recommended operating ranges, and the challenges and solutions for equalizer training implementation were also covered. While the USB 3.0 specification provides guidelines for SuperSpeed transceiver design, [29] offered additional insights and recommendations for transceiver designers dealing with equalization.

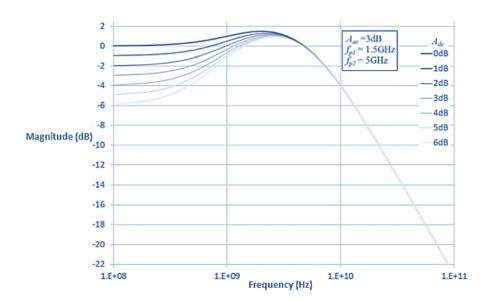

In paper [30], the author said that the difference in speed between on-chip and off-chip communication has widened as the IC process technology has shrunk to improve chip performance. On-chip circuit speed has surpassed off-chip communication speed, limiting the performance threshold of systems with multiple ICs. To address this gap, I/O interfaces like PCI-Express, USB 3.0, and DDR3 use high-speed transceiver systems that operate in the Giga-Hertz range. However, the copper interconnect on a motherboard backplane cannot support data rates, leading to signal integrity issues with nonideal effects introduced by the channel. To compensate for high-frequency losses introduced by the channel, a Continuous-Time Linear Equalizer (CTLE) was used at the receiver (RX) front-end. The implementation of CTLE was typically limited to first-order, but second-order CTLE offered incremental peaking gain when dealing with channels of high losses. Paper [30], therefore presented the characteristics and theoretical circuit analysis of first-order and second-order CTLEs, both designed to address a 5Gb/s data rate transmission. An arbitrary 20-inch channel was used as a test bench to compare the performance of the two equalizers. Simulation results demonstrated an improvement in receive eye voltage opening and insertion loss for second-order CTLE but with degradation in terms of receive eye time opening, jitter, and amplitude noise.

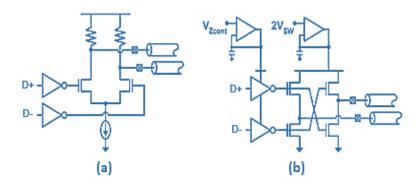

In paper [31], a USB 3.0 compatible transmitter (TX) and a corresponding receiver (RX) linear equalizer are presented, with an exploration of the architecture and circuit design techniques utilized to satisfy strict overall link design requirements. The output voltage amplitude and deemphasis levels of the transmitter (TX) are programmable, and the output impedance is calibrated to  $50~\Omega$ . A programmable receiver (RX) equalizer was also presented, designed to compensate for channel losses, and employed alongside a DC offset compensation scheme. The equalizer operated at 6.25 GHz and provides 10 dB overall gain equalization, with 5.5 dB peaking at the maximum gain setting. The layout area of the transmitter (TX) core was 400  $\mu$ m x 210  $\mu$ m, and the equalizer core was 140  $\mu$ m x 70  $\mu$ m, designed using a well-established 65 nm complementary metal oxide semiconductor process. At a data rate of 5 Gb/s, the power consumption of the transmitter (TX)

and the equalizer were 55 mW and 4 mW, respectively, from a 1.2 V supply. The target application for these high-speed blocks was the implementation of the critical part of the physical layer, which defined the signaling technology of SuperSpeed USB3 PHY.

In Paper [32], the author focused on optimizing equalization architecture for high-speed serial communication, specifically for 25Gb/s or above backplane communication. The Advance Design Systems (ADS) Channel Simulator was used to analyze the high-speed backplane channel by examining its frequency and impulse responses. Various equalization architectures, including the high frequency boost values of linear equalizer (LE) and tap coefficients of decision feedback equalizer (DFE), were analyzed in detail. The results demonstrated that using a combined LE/DFE yields much better performance compared to using LE or DFE separately, with only a slightly increased complexity cost.

In paper [33] it is mentioned that low-power equalization was still in high demand for wireline receiver (RX) s that operate at high speeds on copper media. Also, in [33], a design was presented that included a continuous-time linear equalizer and a two-tap half-rate/quarter-rate decision-feedback equalizer that utilized charge steering techniques to reduce power consumption. The prototype was implemented in 45 nm technology and consumed only 5.8 mW from a 1 V supply, while compensating for a 24 dB loss with BER  $< 10^{-12}$ .

Equalization is used to combat Inter-Symbol Interference (ISI) caused by multipath in time-dispersive channels. ISI occurs when the modulation bandwidth is greater than the coherence bandwidth of the radio channel and modulation pulses are spread in time. A receiver (RX) with an equalizer can combat an average range of delay and channel amplitude that is expected. Equalizers must be adaptive because the channel is generally time-varying. Various adaptive equalizers can be used in radio channels to cancel interference while providing diversity. They track the time-varying characteristics of the mobile channel because the mobile fading channel is time-varying, and the equalizer must be adaptive in nature to combat this. In [34], different equalization techniques in digital communication were analyzed and a conclusion as to how much each of them is effective was derived.

With the communication industry rapidly moving towards a multi-gigabit era, inter symbol Interference (ISI) has become a significant issue that needs serious attention. As the world moves towards 5G and beyond, and with the introduction of electronic devices designed for multi-Gigabit data transfer, there is a greater need for exploration of Equalization Techniques compared to the past with low data rates. The main purpose of Equalization techniques is to ensure that the receiver

(RX) detects the same pattern as the transmitter (TX) and correct any errors caused by the transmission path. Paper [16], presented a comparative analysis of different equalization techniques using MATLAB simulation. Furthermore, Advance Design System (ADS) and Optic Wave simulations were conducted for high-speed serial link design and Optical link, and the receiver (RX) output was compared using Q-factor and Eye pattern, both with and without the implementation of Equalization.

In [35], a neural equalizer as a potential solution for better performance compared to traditional conversational equalizers was proposed. The neural equalizer was designed to minimize mean square error and distortion due to ISI. The results of the analysis indicated that the operational behaviour of the neural equalizer was superior to that of all existing conversational system of equalizers. The proposed equalizer was tested for every channel with its own bit-error rate and noisy data, and simulation results showed that the properly designed equalizer had a lower bit error rate (BER) and better overall performance.

In the field of wireline communication, a recent study [36], showcased a PAM4 receiver (RX) design. This design incorporated continuous time linear equalizers (CTLEs) and a 2-tap direct decision feedback equalizer (DFE). The receiver employed a CMOS track-and-regenerate slicer and was fabricated using 28-nm CMOS technology. Remarkably, the design achieved impressive performance results, with a bit-error-rate (BER) surpassing 10-12 and an energy efficiency of 1.1 pJ/b at a data rate of 60 Gb/s. These measurements were taken over a channel with an 8.2-dB loss at the Nyquist rate.

# Chapter 3

# **Architecture of High Speed SerDes**

#### 3.1 Data Transmission

Data transmission refers to the transfer of digital data from one device to another through point-to-point data streams or channels. These channels can be wired or wireless. The transmission can occur over a wired or wireless network, using various communication technologies and protocols. Data transmission can include both analog and digital data.

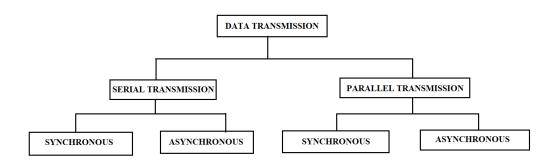

Figure 3.1 gives an insight of the most common methods of data transmission include serial transmission and parallel transmission. In serial transmission, data is sent one bit at a time over a single communication channel. This method is slower than parallel transmission, which sends multiple bits simultaneously over multiple channels.

Fig. 3.1 Types of data transmission

Data transmission is an essential aspect of modern communication and plays a crucial role in enabling communication between different devices. It is used in various applications, including voice and video communication, internet browsing, and file sharing. However, it is important to ensure that the data transmitted is secure and free from unauthorized access.

The effectiveness of data transmission is heavily dependent on the amplitude and transmission speed of the carrier channel. The data transfer rate, which refers to the amount of data transferred within a given time period, determines whether a network can support data-intensive tasks. Network congestion, latency, server health, and insufficient infrastructure can cause data transmission rates to decline, which can negatively impact business performance. High-speed data transfer rates are essential for processing complex tasks like online streaming and large file transfers.

In conclusion, data transmission is the backbone of modern communication and enables the transfer of digital data between devices. To ensure efficient data transmission, it's important to have a reliable communication network and infrastructure. This will help guarantee high-speed data transfer rates, which are necessary for handling data-intensive applications.

#### 3.2 Types of Data Transmission

#### 3.2.1 Parallel Transmission

Parallel transmission is a data transmission method in which multiple bits of data are transmitted simultaneously over multiple data lines. In parallel transmission, each bit is transmitted through a separate data line, which allows for faster data transfer compared to serial transmission.

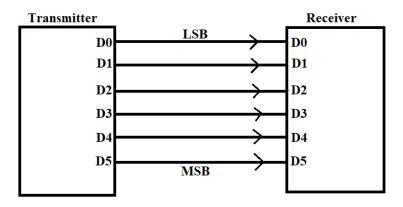

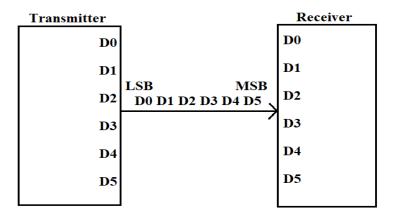

Parallel communication comprises multiple data lines that can carry multiple data bits simultaneously. The data from the transmitting port will be sent to the corresponding receiving port. Therefore, for n-bit parallel communication, 2n ports and n wires are needed as shown in Fig.3.2

Fig. 3.2 Parallel transmission interface

Parallel transmission is commonly used in computer systems for data transfer between components such as memory, processors, and input/output devices. This is because computer systems require high-speed data transfer for quick processing and response times.

One of the advantages of parallel transmission is its ability to transmit multiple bits of data simultaneously, which results in faster data transfer rates. Parallel transmission is also less susceptible to errors than serial transmission, as errors can be easily detected and corrected.

However, one of the main limitations of parallel transmission is the requirement for multiple data lines, which can be expensive, takes more area and is complex to implement in some applications.

Additionally, parallel transmission is susceptible to skew, which occurs when the signals on different data lines arrive at different times, causing errors in data transmission.

There are two main types of parallel transmission: synchronous and asynchronous.

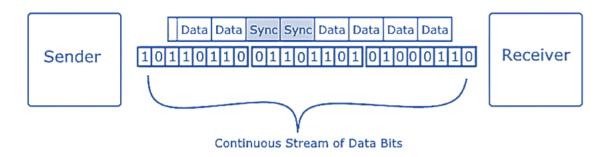

Synchronous parallel transmission involves sending data in parallel at fixed intervals, with a clock signal used to synchronize the transmission. This type of transmission is commonly used in computer memory systems and other high-speed applications, where the timing of data transfer is critical. Figure 3.3 gives an insight of the data flow in a synchronous transmission.

Fig. 3.3. Alignment of data bits in a synchronous data transmission [37].

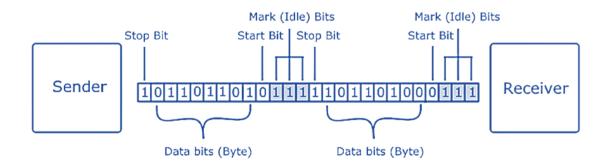

Asynchronous parallel transmission, on the other hand, involves sending data in parallel without a fixed clock signal. Instead, each data bit is accompanied by a start and stop bit to indicate the beginning and end of the data transmission. This type of transmission is commonly used in low-speed applications, such as keyboard input, where timing is less critical. Figure 3.4 gives an insight of the data flow in an asynchronous transmission.

Fig. 3.4. Alignment of data bits in an asynchronous data transmission [37].

In conclusion, parallel transmission is a data transmission method that offers faster data transfer rates compared to serial transmission. It is commonly used in computer systems for high-speed data transfer, but it can be limited by its requirement for multiple data lines and susceptibility to skew. Despite these limitations, parallel transmission remains an essential component of modern computing.

#### 3.2.2 Serial Transmission

Serial transmission is a method of transmitting data where the bits of data are transmitted sequentially, one after the other, over a single communication line as shown in Fig.3.3. In serial transmission, each bit is transmitted separately, resulting in slower data transfer rates than parallel transmission. Serial communication most commonly use in chip-to-chip data transfer because it requires only one communication line and is less susceptible to noise interference.

Fig. 3.3 Serial transmission interface

In serial transmission, data is sent in a specific format that includes start and stop bits to indicate the beginning and end of each data packet. This format allows for error detection and correction, making serial transmission a reliable method of data transfer.

Two main types of serial transmission exist, namely synchronous and asynchronous transmission.

Synchronous serial transmission employs a clock signal to synchronize the transmitter (TX) and receiver (RX), with data sent at fixed intervals. The transmitter (TX) generates the clock signal, which is transmitted alongside the data. Synchronous transmission is commonly used in applications where high data transfer rates are essential, such as in computer networking and telecommunications. Figure 3.3 shows how the data bits are aligned in a synchronous data transmission.

Asynchronous serial transmission, on the other hand, doesn't require a clock signal. Instead, each data byte is sent with start and stop bits that indicate the beginning and end of the transmission.

Asynchronous transmission is commonly used in low-speed applications such as keyboard input and serial printer communication. Figure 3.4 shows how the data bits are aligned in an asynchronous data transmission.

One of the main advantages of serial transmission is its simplicity and cost-effectiveness compared to parallel transmission. It is also ideal for long-distance communication because the data can be transmitted over long distances without significant signal degradation.

However, one of the limitations of serial transmission is its slower data transfer rates, which may not be suitable for applications that require high-speed data transfer, such as large file transfers or video streaming. However, with the advancements in data transfer protocols, improved circuitry and fast I/Os, serial communication has been upgraded in terms of speed and it is a preferred mode of data transmission in high-speed data transmission.

In conclusion, serial transmission is a reliable and cost-effective method of data transfer that is commonly used in communication systems. It is suitable for long-distance communication and offers error detection and correction. However, its slower data transfer rates may limit its use in applications that require high-speed data transfer.

#### 3.3 Modes of Transmission

Data transmission is a crucial process involved in transmitting digital or analog data from one device to another. In general, two modes of data transmission are simplex and duplex.

Simplex transmission is a unidirectional mode of data transmission, where data only flows in one direction - from the sender to the receiver (RX). It is commonly used in scenarios where data is transmitted in one direction only, for instance, in broadcast systems or fire alarms. Figure 3.5 shows, the communication between sender and receiver (RX) in simplex transmission.

Fig 3.5. Simplex Transmission.

Duplex transmission, on the other hand, is a bidirectional mode of data transmission, where data flows in both directions simultaneously. It is commonly used in situations that require simultaneous data transmission and reception, for example, in telephony, video conferencing, and computer networking.

Duplex transmission can further be categorized into two types:

Half-duplex transmission- It allows for the transmission and reception of data, but not simultaneously, Figure 3.6, shows the communication between sender and receiver (RX) in half-duplex transmission. The devices take turns to transmit and receive data, and this mode is commonly used in Ethernet networks and two-way radio communication.

Fig. 3.6. Half-duplex transmission.

Full-duplex transmission- It enables simultaneous transmission and reception of data, which is required in scenarios that involve real-time, high-speed data transfer such as fiber optic communication, satellite communication, and internet data transfer. Figure 3.7 shows the communication between sender and receiver (RX) in full-duplex transmission

Fig. 3.7. Full-duplex transmission.

In conclusion, simplex and duplex are the two primary modes of data transmission, and duplex transmission can be divided into half-duplex and full-duplex. The choice of mode depends on the specific application requirements such as the rate of data transfer, direction of data flow, and the need for simultaneous data transmission and reception.

#### 3.4 Significance of Serial Data Transmission

Serial data transmission is often considered a better option compared to parallel data transmission, due to several reasons:

Firstly, serial transmission requires fewer wires or channels than parallel transmission, thus making it more cost-effective and easier to implement.

Secondly, the single-stream nature of serial transmission makes it less vulnerable to signal interference and noise, as compared to parallel transmission. As a result, it is easier to detect and correct errors in data transmission. Moreover, a high-speed serial link will usually exhibit less radiated emissions a parallel transmission. This is because functioning gigabit links require excellent signal integrity.

Thirdly, serial transmission has the ability to cover longer distances between the transmitter (TX) and receiver (RX) as the signal can be amplified or regenerated at different points along the transmission path. In contrast, parallel transmission may suffer from signal degradation over longer distances, as each data line can be affected by interference and noise.

Fourthly, modern serial transmission technologies such as USB, Ethernet, and Thunderbolt, can achieve high data transfer rates that match those of parallel transmission, thus making it suitable for a wide range of applications.

Overall, while parallel transmission may have certain advantages in certain applications, serial transmission has become the preferred method for many data communication systems due to its simplicity, reliability, and flexibility.

# 3.5 Introduction to High-Speed SerDes

I/O design has incorporated serial-to-parallel and parallel-to-serial conversions as well as clock synchronization with incoming data since the early days. However, with the advancement of integrated circuit (IC) technology and the increase in maximum toggle rate (Fmax), the demand for I/O bandwidth has significantly grown. In fact, some advancements have enabled I/O frequency beyond Fmax, which has made SERDES an increasingly important technology.

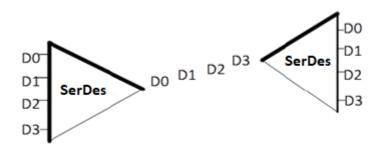

The Serializer/Deserializer (SerDes) device is critical for high-speed applications because it can transfer data serially and convert parallel data to serial and vice versa. Figure 3.8 [38], shows a simplified model of the SerDes device [38].

Fig. 3.8. Simplified model of SerDes link [38].

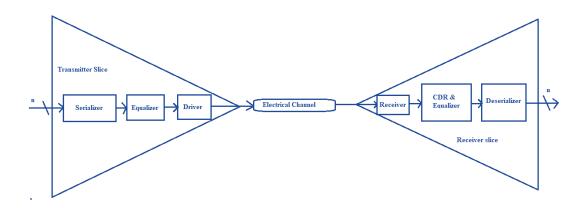

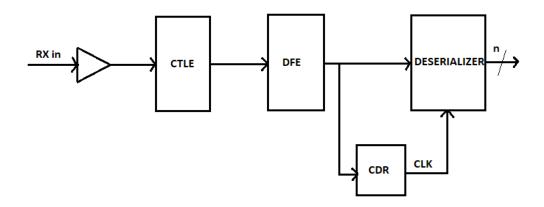

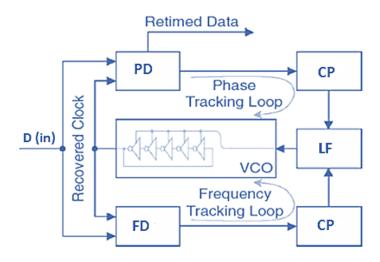

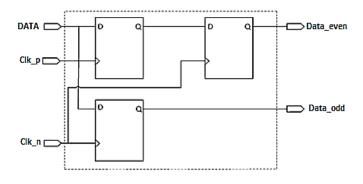

Figure 3.9, illustrates, a basic block diagram of a high-speed SerDes device. The process starts with n-bit parallel data, which is converted to serial data using a Serializer. An equalizer is utilized to ensure good signal integrity of the serialized data, which is then transmitted through a differential channel. On the receiver (RX) side, the serial data is received by a receiver (RX), and then fed into a Clock Data Recovery (CDR) circuit, which generates the clock. After passing through the equalization and recovery circuitries, the data is finally processed by a Deserializer, which converts the serial data back to parallel data.

Fig. 3.9. Basic block diagram of a high-speed SerDes link

The generalized model of a High-Speed SerDes, depicted in Figure 3.9, is composed of a serializer and transmitter (TX) driven by a Phase-Locked Loop (PLL) clock synthesizer, a channel, a receiver (RX), and a Deserializer driven by a Clock-Data Recovery (CDR) unit. The serializer accepts the incoming parallel data-stream and converts it into a serial data-stream, which is then transmitted to the TX. The TX generates a pulse train depending on the data symbols to be transmitted across the channel and the pulse-width, which is determined by the transmit clock timing at the beginning, end, and edges. The receiver (RX) consists of a sampler and a decision circuit, which are responsible for sampling the received data-bit stream from the channel and recovering both the transmitted data and the clock. Once the receiver (RX) recovers the transmitted serial bit-stream,

it is sent to the Deserializer block, which converts the received serial data back to its original parallel form for future interfaces [39].

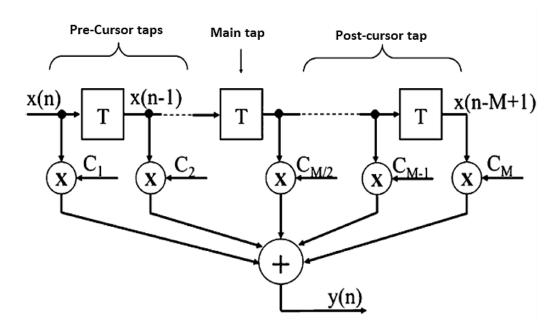

#### 3.6 Transmitter (TX)

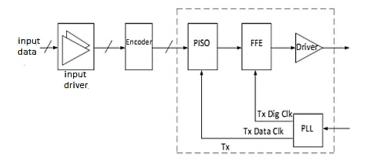

The primary function of the transmitter (TX) is to transmit a high-speed data stream to a receiver (RX) by providing a high-speed voltage swing at the transmitter (TX)'s pins. Figure 3.10 depicts a typical block diagram of the transmitter (TX), which encompasses four key operations: parallel to serial conversion, clock generation, feedforward equalization, and line driving. The transmitter (TX) receives an n-bit parallel data stream as input, which is then converted into a high-speed serial data stream by the serializer block. The PLL generates a multi-phase clock based on an external reference clock. The transmitter (TX) utilizes FeedForward Equalization (FFE) to mitigate the impact of Inter-Symbol Interference (ISI). Lastly, the driver is employed to match the output impedance of the transmitter (TX) with the impedance of the channel (transmission line) [38].

Fig. 3.10. Block Diagram of transmitter (TX) [38].

## 3.6.1 Phase-Locked Loop (PLL) Clock Generator