### Server SoC Density Efficient on RAS Validation Activity

Thesis submitted in partial fulfilment of the requirements for the award of the degree of

#### Master of Technology in VLSI Design & Microelectronics Technology

by

#### JUI GHOSH

Examination Roll No: M6VLS22009

Class Roll No: 001910703009

Registration No.: 150137 of 2019-2020

Under the Esteemed Guidance of

Prof. Sayan Chatterjee

(Internal Supervisor)

Mrs. Manjula Kumar and Mr. Ashok Kumar Dabbugunta

(External Supervisor)

DEPARTMENT OF ELECTRONICS AND TELE-COMMUNICATION ENGINEERING

JADAVPUR UNIVERSITY, KOLKATA - 700032, WEST BENGAL, INDIA

June 2022

## DECLARATION OF ORIGINALITY AND COMPLIANCE OF ACADEMIC ETHICS

I hereby declare that the thesis entitled "Server SoC- Density Efficient on RAS Validation activity" submitted by me, to be awarded a Master of Technology degree from VLSI Design and Microelectronics Technology at the University of Jadavpur is a record of honest work done by me under the guidance of an Internal Professor. Sayan Chatterjee, external director Ms. Manjula Kumar and manager Mr. Ashok Kumar Dabbugunta.

I further declare that the work reported in this thesis has not been submitted and will not be submitted, in part or in full, for any other degree or diploma from this institution or any other institution or university.

Place: Kolkata

Jui Ghosh

Date: 28/6/2022 Signature of the candidate

# Faculty of Engineering and Technology, Jadavpur University <u>CERTIFICATE</u>

This is to certify that the work contained in this thesis entitled "Server SoC Density Efficient on RAS Validation Activity " is a bonafide work of Jui Ghosh (Exam Roll No.: M6VLS22009; Class Roll No.: 001910703009; Registration No.: 150137 of 2019-2020), carried out in the Department of Electronics and Telecommunication Engineering, Jadavpur University, Kolkata under my supervision and that it has not been submitted elsewhere for a degree.

INTERNAL GUIDE Prof. Sayan Chatterjee

Jadavpur University, Kol-700032

EXTERNALGUIDE(MANAGER)

Ashok Kumar Dabbugunta

INTEL INDIA PRIVATE LTD.

D AshoKkumos

Prof. Ananda Shankar Chowdhury

Head of the Department

Department of ETCE, Jadavpur University, Kol-700032 Prof. Chandan Majumdar

Dean

Faculty Council of Engg. & Tech. (FET), Jadavpur University, Kol-700032

## Faculty of Engineering and Technology, Jadavpur University

### **CERTIFICATE OF APPROVAL\***

This is to ensure that the Master Thesis entitled "Server SoC Density Efficient on RAS Validation activity" is recognized as a credible engineering study conducted and presented satisfactorily to validate its acceptance as pre-academic requirements. brought to us. It is understood that with the consent you sign below it does not confirm or accept all the statements made, the opinion expressed, or the conclusions reached but only authorizes the thesis for the purpose for which it was sent.

| Co | ommittee on Final Examination |

|----|-------------------------------|

|    | for Evaluation of the Thesis  |

|    |                               |

|    |                               |

|    |                               |

|    |                               |

|    |                               |

Examiners

<sup>\*</sup>Only in case the thesis is approved

#### **ABSTRACT**

With the expansion and complexity of System on Chip, it is necessary to do verification and validation to meet the industry standards, this is very important and even harder to achieve. Coverage is very much important in domain of verification to verify all the specifications of the protocol and fabric are covered. By getting good coverage number it can be determined if the code is perfect for covering specification and the code is exercised properly or not. Although verification is a vast domain, not only for coverage, but this test environment can also be created for any protocol. Now a day for SOC's Pre-Silicon Verification and Post Silicon Validation both are very much important. In this paper the work will be discussed based on coverage for Intel Specific Protocol especially functional coverage and code coverage. Here for writing configuration System Verilog is used and for simulation and testing scripting language Perl is used.

#### **ACKNOWLEDGEMENT**

It is my pleasure to express with deep sense of gratitude to my guide Prof. Sayan Chatterjee, of Jadavpur University, for his constant guidance, continual encouragement, understanding, more than all, he taught me patience in my endeavour. My association with him is not confined to academics only, but it is a great opportunity on my part of work with an intellectual and expert in the field of verification. I would like to express my gratitude to Pro Vice Chancellor Prof. Samantak Das, Prof. Chiranjib Bhattacharjee, Dean of Faculty Council of Engg. & Tech. (FET) Dr. Rajat Ray A, project coordinators of Jadavpur University for providing with an environment to work in and for his inspiration during the tenure of the course. I would also like to thank my external guide, Mrs. Manjula Kumar, my manager Mr. Ashok Kumar Dabbugunta and the experts of our team from INTEL who were involved in the validation survey for this research project. Without their passionate participation and input, the validation survey could not have been successfully conducted. In jubilant mood I express ingeniously my whole-hearted thanks to the panel members and all teaching staff & members working as limbs of our university for their not-self-centred enthusiasm coupled with timely encouragements showered on me with zeal, which prompted the acquirement of the requisite knowledge to finalize my course study successfully. It is indeed a pleasure to thank my parents and friends who persuaded and encouraged me to take up and complete this task. At last, but not least, I express my gratitude and appreciation to all those who have helped me directly or indirectly toward the successful completion of this project.

I would also like to thank seniors and all the faculty members of the department and all the team members of intel, who directly or indirectly helped me with this work.

I want to thank my family with my whole heart especially my father, my mother and my younger brother for helping me complete this work. Their support was invaluable to me.

| Place: Kolkata |  |

|----------------|--|

|                |  |

Date: 28/6/2022 Signature of the candidate

## **CONTENT**

| Chapter-1                                                                  | 1          |

|----------------------------------------------------------------------------|------------|

| Introduction                                                               | 2-8        |

| 1.1 Introduction                                                           |            |

| 1.2 Background                                                             |            |

| 1.2.1 GNRD                                                                 |            |

| 1.2.2 RAS                                                                  |            |

| 1.3 Brief Methodology of the Project                                       |            |

| 1.4 Assumption made/constrains of Project                                  |            |

| 1.5 Objective                                                              |            |

| 1.6 Motivation                                                             |            |

| 1.7 Problem Statement                                                      |            |

| 1.8 Organization of Thesis                                                 |            |

| Chapter-2                                                                  | 9          |

| Literature Review                                                          | 10-34      |

| 2.1 Literature Review                                                      |            |

| 2.1.1 Design and Integration Methods of Multi-Thre Core 65nm SoC Processor | eaded Dual |

| 2.1.2 Dual-Core Intel SoC Processor 65-nm 16-MB Die L3 Cache               | Shared On- |

| 2.2 Power Reduction Techniques for an 8-core SoC Proce                     | ssor       |

| 2.3 Parallel Mutual Information Based Construction of Genome-Scale Networks on SoC Processor                    |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| 2.4 Optimizing Purdue-Lin Microphysics Scheme for SoC Phi<br>Coprocessor                                        |  |  |  |

| 2.5 Optimization of EULAG Kernel on Intel SoC Phi Through Load Imbalancing                                      |  |  |  |

| 2.6 Multi-Core and Many-Core Memory Systems                                                                     |  |  |  |

| 2.7 Package Design Optimization for Intel SoC                                                                   |  |  |  |

| 2.8 Exploiting Parallelism and Vectorisation in Breadth-First Search for the Intel SoC Phi                      |  |  |  |

| 2.9 Integration of Performance Improvement and Stencil Power Application Intel to Intel SoC Scalable Processors |  |  |  |

| Chapter-3                                                                                                       |  |  |  |

| PHYSICAL ARCHITECTURE 36-52                                                                                     |  |  |  |

| 3.1 IMPLEMENTATION OF SOC INTEGRATION                                                                           |  |  |  |

| 3.2 RAS                                                                                                         |  |  |  |

| 3.2.1 RAS Security                                                                                              |  |  |  |

| 3.2.1.a Security Assurance                                                                                      |  |  |  |

| 3.2.1.b Security Feature                                                                                        |  |  |  |

| 3.3 PUnit IERR and MONFAIL                                                                                      |  |  |  |

| 3.3.1 IERR Network                                                                                              |  |  |  |

| 3.3.2 MONFAIL Network                                                                                           |  |  |  |

| 3.4 MDFCI                                                                                                       |  |  |  |

| 3.5.1 PUnit Overview                                                                                            |  |  |  |

| 3.5.2 PUnit Services                                                                                                                                                                                                                                                     |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.6 GPIO                                                                                                                                                                                                                                                                 |      |

| 3.7 RAS Features in PUnit                                                                                                                                                                                                                                                |      |

| 3.8 Design Verification                                                                                                                                                                                                                                                  |      |

| 3.9 System Verilog for Verification                                                                                                                                                                                                                                      |      |

| 3.10 Universal Verification Methodology                                                                                                                                                                                                                                  |      |

| 3.11 Security in Mobile device based SoCs                                                                                                                                                                                                                                |      |

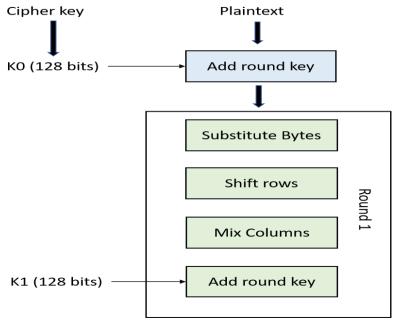

| 3.11.1 Cryptography and Encryption                                                                                                                                                                                                                                       |      |

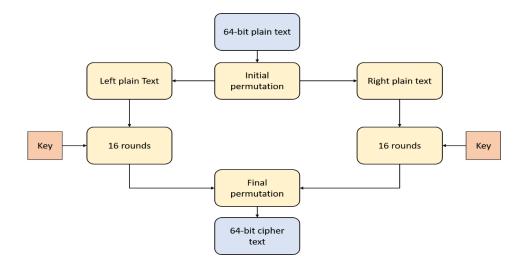

| 3.11.2 Data Encryption Standard                                                                                                                                                                                                                                          |      |

| 3.11.3 Triple DES                                                                                                                                                                                                                                                        |      |

|                                                                                                                                                                                                                                                                          |      |

|                                                                                                                                                                                                                                                                          |      |

| Chapter-4 53                                                                                                                                                                                                                                                             |      |

| Chapter-4 53  Design and Implementation of UVM be                                                                                                                                                                                                                        |      |

| Design and Implementation of UVM be                                                                                                                                                                                                                                      |      |

| Design and Implementation of UVM be                                                                                                                                                                                                                                      | ased |

| Design and Implementation of UVM by Testbenches in RAS 54                                                                                                                                                                                                                | ased |

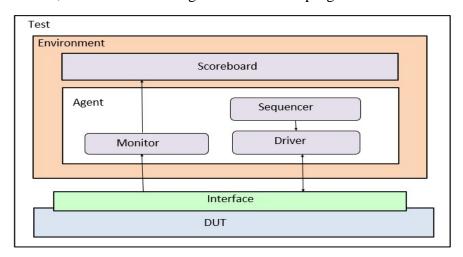

| Design and Implementation of UVM by Testbenches in RAS  4.1 UVM Testbench Specification                                                                                                                                                                                  | ased |

| Design and Implementation of UVM by Testbenches in RAS  4.1 UVM Testbench Specification  4.2 Design methodology of SoC Design Verification                                                                                                                               | ased |

| Design and Implementation of UVM by Testbenches in RAS  4.1 UVM Testbench Specification  4.2 Design methodology of SoC Design Verification  4.3 Implementation using UVM Class Library                                                                                   | ased |

| Design and Implementation of UVM barestbenches in RAS  4.1 UVM Testbench Specification  4.2 Design methodology of SoC Design Verification  4.3 Implementation using UVM Class Library  4.3.1 Modelling a sequence item                                                   | ased |

| Design and Implementation of UVM by Testbenches in RAS  4.1 UVM Testbench Specification  4.2 Design methodology of SoC Design Verification  4.3 Implementation using UVM Class Library  4.3.1 Modelling a sequence item  4.3.2 Building UVM Driver                       | ased |

| Design and Implementation of UVM by Testbenches in RAS  4.1 UVM Testbench Specification  4.2 Design methodology of SoC Design Verification  4.3 Implementation using UVM Class Library  4.3.1 Modelling a sequence item  4.3.2 Building UVM Driver  4.3.3 Building Agent | ased |

| 4.4.3 Test Debug                               |       |

|------------------------------------------------|-------|

| CHAPTER – 5                                    | 65    |

| <b>Results and Discursion</b>                  |       |

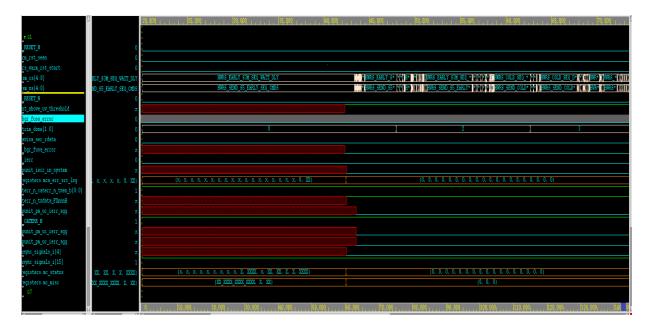

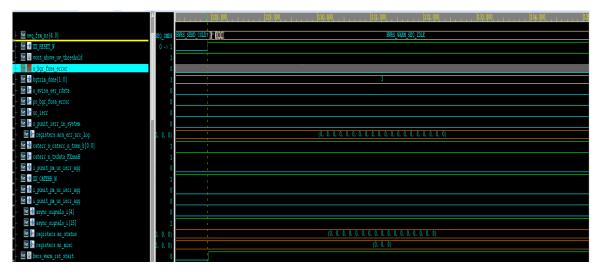

| 5.1 Simulation Results                         |       |

| 5.1.1 Simulation of Various infacing protocols |       |

| 5.1.2 Simulation logs of the connectivity tool |       |

| 5.1.3 Simulation logs of UVM test benches      |       |

| 5.14Simulation results off memory access test  |       |

| 5.2 Details of Test for sequences              |       |

|                                                |       |

| CHAPTER-6                                      | 74    |

| <b>Conclusion and Future Scope</b>             | 75-76 |

| 6.1 Conclusion                                 |       |

| 6.2 Future Scope                               |       |

| 6.3 Learning Outcomes of the Project           |       |

|                                                |       |

4.4.1 Test Plan

4.4.2 Test Development

### **List of Figure**

| Figure No. |        | Title                                      | Pa | ge |

|------------|--------|--------------------------------------------|----|----|

| No.        |        |                                            |    |    |

| 1.1        | 1      | New Generation SoC Processor               |    | 2  |

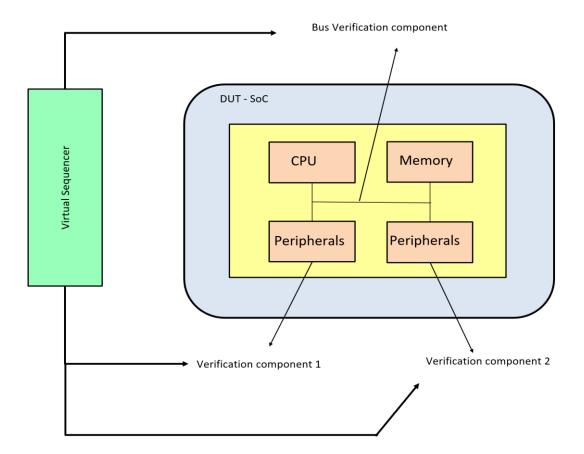

| 4.1        |        | UVM Testbenches Architecture               |    | 54 |

| 4.2        |        | UVM Testbenches design for SoC             |    | 56 |

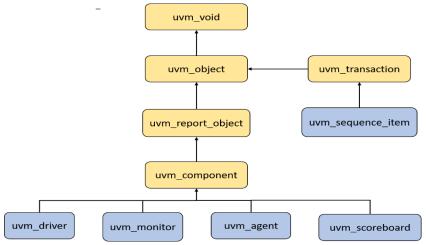

| 4.3        |        | UVM class Hierarchy                        |    | 57 |

| 4.4        |        | Definition of sequence-item                |    | 58 |

| 4.5        | Constr | aints on sequence item data in destination | IP | 59 |

| 4.6        |        | Driver definition                          |    | 60 |

| 4.7        |        | Monitor definition                         |    | 60 |

| 4.8        |        | Agent definition                           |    | 61 |

| 4.9        |        | Building the component of the agent        |    | 61 |

| 4.10       | C      | Connecting the subcomponent of agent       |    | 62 |

| 4.11       |        | Definition of the environment class        |    | 62 |

| 5.1        |        | Simulation of BGR protocol                 |    | 66 |

| 5.2        | Sim    | ulation of BGR protocol in PUNIT_IERR      | _  | 67 |

| 5.3        |        | Simulation of BGR protocol                 |    | 67 |

| 5.4        |        | Simulation of PLL protocol                 |    | 67 |

| 5.5        | Sim    | ulation of PLL protocol in PUNIT_IERR      |    | 68 |

| 5.6  | Simulation of PLL protocol in PUNIT_IERR | 68 |

|------|------------------------------------------|----|

| 5.7  | Screenshot of the log file               | 68 |

| 5.8  | Resource usage for PLL sequence          | 69 |

| 5.9  | Resource usage for BGR sequence          | 69 |

| 5.10 | Simulation result of memory              | 70 |

|      | access test for ierr_pll sequence        |    |

| 5.11 | Simulation result of memory              | 71 |

|      | access test for ierr_bgr sequence        |    |

|      |                                          |    |

| 5.12 | Check the input and output of PLL        | 71 |

|      | Sequence                                 |    |

| 5.13 | Check the input and output of BGR        | 72 |

|      | Sequence                                 |    |

#### **Abbreviations**

**Term Definition**

**ACPI** Advanced Configuration and Power Interface

ADR Asynchronous Data Refresh

**AER** Advanced Error Reporting

ART Always Running Timer

**AWFCS** Assured Write Frame Checksum Sequence

BIOS Basic Input/Output System

BSP Boot Service Processor

CATERR Catastrophic Error

**CCP** Converged Core Perimeter

CIA Configurable Ip Adapter

CLKI Clock Interface standard

**CPU** Central Processing Unit

CXL Intel Compute Express Link

DIMM Dual Inline Memory Module

DSO DTF Source Observer

DSP DFX secure plugin

DTF Debug Trace Fabric

DTS Digital Thermal Sensor

**DVFS** Digital Voltage Frequency Scaling

DVP Debug Visibility Packetizer

**ECC** Error Correction Code

FCS Frame Checksum Sequence

FIVR Fully Integrated Voltage Regulator

FPC Fuse Protocol Converter

FQN IPX Fully Qualified Name

FRB Fault Resilient Boot

**GPF** Global Persistant Flush (ADR for CXL)

GPIO General Purpose Input/Output

HPM Hierarchical Power Management

**HWP** HardWare Performance (states)

HWRS Hardware Reset Sequencer

ICL Instrument Connectivity Language

IERR Processor Internal Error

IPX IP eXchange

ISA Ip Specific Adapter

ISS Intel Speed Step

ITD Inverse Temperature Dependence

IVT Ivv Town server

LTA Line Tracker Algorithm

LTR Latency Tolerance Reporting

MBVR Mother Board Voltage Regulator

MBVR Mother Board Voltage Regulator

MBVRM Mother Board Voltage Regulator

Module

MCA Machine Check Abort

MCERR Machine Check Error

MCTP Management Component Transport

**Protocol**

MSR Model Specific Register

N/A Not Applicable

NMI Non-Maskable Interrupt

OOB Out-of-band

OS Operating System

OS Operating System

PA Protocol Aware

PCH Platform Controller Hub

PCH Intel Platform Controller Hub

PCIe PCI Epress

PDL Procedural Description Language

PECI Platform Environmental Control

**Interface**

PGCB Power Gate Control Block

PMC Power management controller

PMT Platform Monitoring Technology

PState Performace State

PUnit Power control Unit

PWM Pulse Width Modulation

PWM Pulse Width Modulation

RAC Read access control

RAS Reliability, Availability, Servicibility

RC Resource Controller

RA Resource Adapter

SAI Security Attributes of the

**Initiator**

SCU Soc Control Unit, synonym for

**PUnit**

SGX Software Guard Extensions

SDL Security Design Lifecycle

SMI System, Management Interrupt

SMM System management mode

**SRAR** Software Recoverable Action Required

sVID Serial Voltage IDentification

TDX Trust Domain Extensions

TRM Technical Reference Manual

TSC Time Stamp Counter

TSOD Temperature Sensor on DIMM

UCNA UnCorrectable No Action

UFS Uncore Frequency Scaling, generally mesh

**DVFS**

URT synonym for ART

VISA Visualization of Signals Architecture

VR Voltage Regulator

VRM Voltage Regulator Module

VRCI Voltage Regulator Common Interface

standard

VSEC Vender Specific Extended Capabilitites

WAC Write access control

## CHAPTER 1 INTRODUCTION

#### Introduction

#### 1.1 Introduction

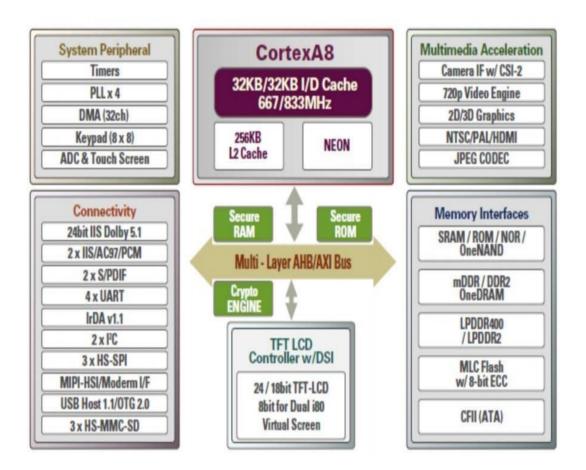

According to Moore's law, as transistor sizes get smaller, the density of integrated circuits will almost double annually. A shift from computation-centric designs to communication-centric architectures with several IP cores has occurred as a result of these developments in Very Large Scale Integration (VLSI) integration density. An integrated circuit known as a "system-on-chip" (SoC) combines all of the parts of a computer system onto a single silicon chip. These include memory, general-purpose input and output ports, a central processing unit (CPU), and auxiliary components like modems and a graphics processing unit (GPU). An SoC's fundamental block diagram is displayed in Figure 1.1. Any SoC will have a memory subsystem, CPU subsystem, multimedia subsystem, and peripheral subsystem. Communication between these subsystems is possible.by means of various interfacing protocols through a Network-on-chip.

Figure 1.1: General SoC design

a lot of power and space limitations. As a result, a lot of fundamental architectures need a reliable communication infrastructure. These problems are now being solved using Network on Chip (NoC).

NoC is a network-based communications subsystem and router-based packet switching network that lies between SoC components. For SoC integration, it is necessary to comprehend functionality, system requirement requirements, numerous protocols, architecture, and interface details. It takes a lot of time.

Design Verification is a crucial stage of SoC Design. By identifying potential mistakes in both the design and the system's architecture, the design verification stage assesses the design's quality and ensures its accuracy in operation. Both the block/IP level and the SoC level can undertake design verification. The top-level SoC operations are the focus of SoC level verification, together with the accuracy of the intercommunication between the sub-blocks.

The security blocks, which are in charge of ensuring the security and legitimacy of sensitive data used in the SoC, are the sub-block that is being focused on for SoC verification in this case. These security blocks are essential in current chips where data security is of highest importance since they can authenticate and encrypt data as needed.

#### 1.2 Background:

It is no secret that Intel's Enterprise processor has been expanded in recent generations Compared to the competition, Intel is chasing its mass death strategy while relying on a manufacturing facility that has not provided the best in the market. Today's businesses are increasingly relying on Intel Soc servers to run applications that require data and are important for policy. Server reliability, availability, and efficiency (RAS) are key issues in today's business enterprise IT systems that deliver critical applications and services, as failure to deliver applications can cost every hour of system malfunction. In addition, the chances of such failures increase statistically with server size, data, and memory required for this post. The Intel SoC family provides a complete and robust set of RAS features in silicon to provide error detection, correction, content, and detection across all processors, memory, and I/O data methods. This set feature is a powerful platform where software and software vendors can create modern RAS layers to provide complete server reliability across the hardware-software stack from silicon to delivery of applications and services. The Intel SoC family brings all of these features to a competitive and energy-intensive price compared to traditional RISC-based solutions in the market.

Intel's new generation SoC building strategy will have a dual track of product-based (Performance-core (P-core) and Efficient-core (E-core) products, from two advanced platforms to one common site, defining the industry. This new approach will increase per watt performance, component features and Intel's overall competitiveness in the industry. While introducing this new approach, Intel has strengthened its compliance with SoC largest ecosystem platform today and the benefits that customers will receive from a single investment.

#### 1.2.1. Server SoC:

This is a Intel next generation processor with low power at SoC Product Swim Lane. It replaces the ICL-D product and is targeted at a wide range of markets, including comm, storage, and IOTG.

Server SoC can be divided into 2 main components, the reusable previously used SoC Compute die (s) and the Server SoC unique IO die, which includes the 2xNAC 200G Ethernet Subsystem, and various Networking Accelerator. Compute die and IO die are MCP within the BGA package at the Kelseyville platform. Server SoC supports two product line flavours Advance and Ultra. Advance SOC has compute die computer (s), HCC 42 cores and MCC 18 cores, as well as a single IO. During the Ultra SoC, XCC has up to 48 cores and 2 examples of IO deaths.

Server SoC provides a way to prevent the processor from operating above the maximum safe operating temperature. It is useful for a variety of reasons such as thermal throttling to reduce heat to avoid processor damage, and electrical compensation due to Inverse Temperature Dependency (ITD). This is achieved by using a network of various temperature sensors to measure temperatures in a wide range of tropical and subtropical regions. PCcode analyses the temperature to initiate thermal movements and to report data to the platform through various MSRs. If you are not in this throttling-based firmware function, there is a hardware protection called THERMTRIP that is fully hosted by compatible hardware.

Digital Thermal Sensors (DTS) sensors are precise hybrid signal circuits that generate internal electrical energy equal to the total temperature and then convert analog to digital. DTS supports CRI Slave virtual interface that will be connected to the Service Adapter (RA). The App Manager controls the DTS temperature sensor values with the help of the App adapter over the PMSB bus. RA reads DTS temperature values over the CRI interface and provides data back to RC via PMSB bus. The RC reads the amount of DTS periodically almost every 500µs and sends them to Punit as part of the telemetry service.

Server SoC is targeted at the Micro server market in the Kaseyville area. The GNR-D SOC contains Compute die (from previously used SoC) and the IO die and Integrated ETX Server SoC will have a PCH less with integrated boot supported by S3M.Bacon profile. It does not have support for multiple sockets. It has an integrated clock solution for clock production. S3M is used as BACON (Boot Access Control). S3M is in the S5 domain and ETX components.

#### 1.2.2. RAS (Reliability, Availability, Serviceability) Feature:

For the most crucial applications, such as websites, enterprise resource planning (ERP), customer relationship management (CRM), and business intelligence (BI) applications, new technologies in more advantageous price conditions are necessary. Many of these applications must also be accessible locally or worldwide twenty-four hours a day. The largest website, BI, and advanced apps cannot be solved by integrating and leveraging real resources alone, even though they can help fulfil availability needs. The hourly cost of a single business plan failing can easily go from tens of thousands to millions of dollars. All of this evidence necessitates the use of extremely sophisticated and durable servers that are well-suited to large-scale integration and vital business applications. Only those failures that can be handled at the hardware level are allowed by standard RAS server usage. Normally,

RAS is an important component of system design. The reliability of the system depends on how well it can detect errors, correct them or reuse them to maximize Availability and provide sufficient error information to service errors.

Larger designs are less flawed that can make parts less reliable, especially in storage structures. Although solid errors are similar to production errors that are corrected by replacement, severe errors due to aging are not. Also, soft errors due to cosmic rays can temporarily affect values. Reliability: The ability to recognize all errors increases the reliability of the correct answer. Acquisitions are therefore increased.

Reliability: Data integrity is related to data protection through the detection and repair of errors, or if it cannot be corrected, the retention of these errors. Error detection confirms that errors are detected in the data and command level. Debugging deals with an error found by returning an error piece of data or fragments with their correct algorithm. Content error ensures that corrupted data is thus marked across all major components and data pathways so that sub-systems other than those that fail can take appropriate action if they encounter such errors.

Availability: Modern methods improve system availability by providing methods that allow for seamless operation even in the face of irreparable errors. These methods include multiple depletion levels (spare processors, DIMM memory, and I / O resources), automatic failover to silicon and Hardware levels, and software-assisted error detection in various layers of the software stack, from OS and virtual. The memory manager (VMM) at the bottom of the website, commercial, or application layers at the top end. All of this provides server stability in the face of irreparable hardware failures. Using methods such as ECC data allows for one-bit errors (per set) and increases the availability of a useful component.

Service: Modern methods improve usability using predictable failure analysis to identify problematic components before creating irreparable errors or real downtime, thus facilitating the replacement of components in the event of severe failure. System partitioning is used to further separate workloads that are affected by irreparable errors from other functional loads that operate on the same server infrastructure and facilitate repair. Errors may be corrected, irreparable, or even fatal. The last two PVC clubs. Reporting these errors in detail, allows you to identify when and where errors occur. This allows for servicing (changing, excluding, etc.) part of the full system.

#### 1.3 Brief Methodology of the project

The project is broadly divided into two phases namely

- 1. RAS Integration Different types of IP cores are grouped according to interfacing details, port names, port width and given SoC specifications. The process for compiling is as follows:

- For a list of ports, port width, hole direction, hole and block functions and related details from the design team.

- Look at the information obtained from key design owners and understand what and how the communication should be made.

- Creating connections between different IP Cores according to the specifications provided by updating the files received by the design team. These files contain a list of hole names, directions and a wide range of holes. A compatible port that should be connected to every hole should be added to the files.

- Keep files updated and open an Intel ID connection tool.

- Examine the output list of output files to detect offline inputs, errors, unloaded output and multi-drive holes and correct them.

- 2. RAS Verification Verification is done with the help of System Verilog test benches.

The verification process is as follows:

- Adherence to the Universal Validation Methodology (UVM) standard, which allows for the rapid development and reuse of verification facilities and IP verification (VIP).

- The construction phase is performed at the beginning of the UVM testbench simulation, in which parts of the test bench are built, repaired and connected.

- The operating phase consists of the start of the simulation and the running phase. The running phase is time consuming, as this is the stage where the case is examined.

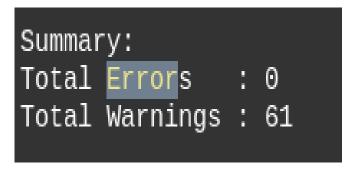

- The final phase of cleaning, which includes extraction, inspection, report and final clauses. Here, the results of the test case are collected and the number of errors, if any, is reported.

#### 1.4. Assumptions made / Constraints of the project

The communication and verification of the various IP Cores is done using Qualcomm proprietary tools. Screenshots of results, captions, internal configurations of various IP cables cannot be disclosed. Caption code, results are adjusted so that company information is not compromised and true to actual results obtained.

#### 1.5. Objective:

- The main purpose of this project is to study the various techniques of Physical Design and Physical Verification of the structure generated.

- The structure generated in the netlist list with various processes, power, and temperature using industry tools, which are useful for verification and compliance details. Intricate designs such as Test-chips.

- The work also aims to create the most common challenges one faces over time by making changes, time, and power over complex chip chips and providing possible solutions.

- The role of physical validation in some of the most useful design processes like ECO is also explained in this work.

- This activity is also a discussion of possible improvements and improvements to existing systems using a specific writing strategy to prepare the verification process for future challenges.

#### 1.6. Motivation

RAS integration is a challenge and a complete process. It requires a good understanding and grasp of the various protocols that come together to make connections between the two modules. You need to first understand the functionality of each block, the function of the anchors in it and the type of visible interface between all the IP cores present in the RAS before merging.

RAS authentication differs from IP / block level verification as it not only ensures the performance of individual IPs / blocks, but rather ensures their performance when integrated as part of the entire system. This is very important in ensuring the production of flawless and flawless chips. Additionally, security blocks are an integral part of the SoC, and their flawless operation is an important step in ensuring secure data transactions.

#### 1.7. Problem statement

One SoC chip has about 90000 to 1 lakh connections to be made between the different IP cores present in it. Every IP core has its own debug, clock, Design for Test (DFT) signals with the exception of the integrated signals that must be present.

connected to other cores. Connecting IP cores requires a good understanding of their performance, integration details, RAS structure, and should be done according to the provided SoC / ASIC data.

The complexity and development of SoC design and architecture has made design validation one of the most important stages in the design cycle. It is a large and complex domain that is constantly evolving. Therefore, it requires a systematic approach to properly verify and correct errors for advanced SoC designs

#### 1.8. Organisation of Thesis:

Chapter 2 discusses a brief discussion of the earlier function of the SoC processor

- Chapter 3 discusses various collaborative agreements such as PUnit, IERR, MONFAIL used in RAS. Apart from this, the principles of design validation and its emergence from System Verilog to UVM are discussed. Additionally, an overview of the various defines protocols is presented.

- Chapter 4 discusses the specification of the UVM test bench design and its customization to ensure SoC quality. Implementation of a test bench designed using UVM classes and methods is described in detail.

- Chapter 5 discusses the results obtained after integrating and validating the various IP Cores. Displays a variety of simulation logs and results generated during design validation, as well as a brief summary of the pass / fail status for advanced testing.

- Chapter 6 discusses the different learning outcomes, the scope of the future of the work done, and the conclusion of the work done.

## CHAPTER 2 Literature Review

#### **Literature Review**

#### 2.Literature Review

There is a growing need for the successful processing of big data in the education community and industry in order to obtain valuable information. Most of the frameworks are built on commercial machines with multi-core or multi-core processors such as the Intel SoC E-series and Intel SoC Phiseries. These processors always have complex mesh connections, caches, and memory hierarchies. There are many differences in structural features between central memory systems and much more. This chapter will review some of the work done on Intel SoC Processors: Multi-Core, Memory Systems and the Integrated Genome-Scale Networks Information for SoC Processor.

## 2.1.1 Design and Integration Methods for a Multi-Threaded Dual Core 65nm Processor

The successful construction of a complex multi-billion transistor processor relies heavily on solid, certified silicon and composite methods. Process weight of 65nm, the pursuit of the best performance of the segment, and the aggressive schedule to go to market are strongly emphasized in the new construction and the composite method that allows silicon performance. Here, researchers Raj Varada, Mysore Sriram, Kris Chou, James Guzzo did an excellent job of explaining the design and integration techniques used successfully in the multi-threaded dual processor 65nm SoC.

The Moore Performance Measurement Process The process allows multiple processors to be integrated into the same chip in a 65nm process area. Combined with multi-thread technology [1], the dual-core processor looks like four sensible processors and can run four wires simultaneously on the same processor chip. Designing and assembling a processor with more than 1 billion transistors is an important challenge given its market-time objectives and complexity of the original 65nm processors. Designs are based on solid design principles and methods.

The SoC MP [2] processor described in this white paper contains two 64-bit cores and a 16MB Unified Level 3 (L3) cache. Each theme supports two strands and has a combined 2 MB (L2), which is widely used in the construction of standard buildings. This processor was limited to creating a highly efficient high-performance virtual interface (SDI) that uses core processor cores, integrated L3 repository, and processor front side bus (FSB). Main preparation is required. CBC). This structure reduces the reservoir and delays in external bus access. This, in turn, reflects the visual SDI connector at the conceptual level. CBC archive handles basic solutions, L3 repository access, and external bus applications.

This is a brand-new design for using low latency, high-density chip connectivity fabric, which includes RAS capabilities for robust server performance. CBC logic and chip level integration are performed using the techniques described in this document. The main components of the portable CBC component were control blocks and data exchange blocks.

Apart from these blocks, there was another sensible part of washing, DFx, and crossing the domain. Part of the chip cache was designed using the same method as it is treated as a black composite box. Therefore, the definition of temporary storage strategies is beyond the scope of this document. This reflects the high-level structure of the processor. The processor chip is a 435mm2 chip, and has a transistor of 1.33B. It operates above 3.0GHz from 1.25V core supply

The CBC is designed to limit strength. The CBC block is divided into two categories based on the average function factor (AF) and sensitivity of power or value of time. The most important time block with the highest AF rate was originally designed using transistor-based cells. When the required time interaction level is reached, the cells in the critical timeline are selectively replaced with a cell containing a low leakage transistor (LL cell) without interfering with the design metrics of the design. By blocking the lower aspect of the function, the design is made using LL cells and other self-adhesive cells are used to integrate the last few timing channels. It was noted that using only LL cells would increase the number of cells and the total volume. Therefore, using the self-adhesive cell block of high AF reduces the dynamic performance. The strategy, which incorporates these two features, allows for faster integration of design and application of appropriate workplace reduction strategies.

The die size of this chip is determined primarily by the centralized component and the repository and was not highly dependent on the assembling method. Additionally, CBC performance trading allows for the creation of time and a way to integrate all of the upgraded chip to integrate full chip block chain and CBC block chain independently without further ado. The first parameter to be adjusted was the height of the signal line repetition so that by protecting half all full-chip wires and minimizing the mirror junction using a set of each predefined cable width and space widths wider than the minimum process process and space. It is now designed as full chip path as possible. Also, recurring distances at different levels have been adjusted to have easier relationships with each other. For example, the repetitive metal8 range was twice the repetitive metal6 distance, which is twice as much as the repetitive metal4 range.

A visual duplication approach was used to increase the productivity of the project. Visual repetitions are figurative annotations placed on the phone and contain information about the recurring cells that they represent. The Extrusion and Time tool detects these annotations and can calculate delays and endings as if a real recurring cell was placed in a specified location, without the maximum header listing or termination. Repeaters were kept in visual format until about a quarter of the tape outs were too late for the project. Once the design is stable, a real repeater is added to the network list based on the repeter's location. By performing a virtual repetition, the integration team was able to respond quickly to the latest design changes while maintaining acceptable accuracy in the time model.

The Virtual Repeater Insertion Tool minimizes total delays while completing the target set with each receiver machine and repetitive input. All full chip duplicates are placed in the space between the full chip blocks. The system has a recurring grid. This is a narrow horizontal or vertical block placed in the program space indicating the location of the official repository. These are separated by a repetitive tone of the full chip track path in that area. For example, in a horizontal area, repeating stations were available at about 600u separately. Metal4 wire requirements every time it passes a channel, Metal6 wire needs to repeat on all other channels, and Metal8 wire can skip 3 channels before a replay is required. The Virtual Repeater Installation Tool was restricted to repeat repeaters only in Keep in Region when the repetitive channel location is not set.

Marketing time is an important parameter of this project, so as much automation was needed to use the full chip route and repeat. However, the general reversal of this slow compound is due to the variation in the results produced by the changing instruments. The Auto-based Route specification method and the well-defined control method of the Repeater Insertion Tool have helped to control variability and produce predictable results.

Auto Router allows you to specify route specifications with different levels of granularity inside. In the early stages of the project, clarification was a command to pair a simple layer. However, as the design was more stable and more routes over time, additional obstacles were presented to the route in the form of topology guidelines, a "snow" successfully route. By the time the design was almost integrated, almost every FC network had topology specifications attached to avoid unnecessary diversity.

The visual repetition is converted to visual repetition quarterly just before the tape out, so the repetitive installation result is predictable, and if you set the location of the visual repetition the next time you use the tool. But I had to be able to reproduce it. The control file system is designed for this purpose, allowing the user to specify how many first or last repetitions are included in a particular block PIN. You should use the subset of recurring channels to complete a certain repetition or write more. Automatic gradient setting, such as a set of networks. By maintaining this control file, the visible recurring input tool has been able to produce results that can be very reproducible, albeit from the beginning of each integration cycle.

Block design and integration methods are key factors in bringing more than a billion transistor server processors to market. We have introduced a set of new strategies and methods used to design and integrate server processors to enable industry-leading performance with a rapid development schedule. The powerful use of cell-based design techniques has made the pipelines come together in early space-based space. The performance target was achieved through a block chain-reduction system, which includes a high-density cell design with high voltage. Using more ropes and half shields allows for more repetitive space for each metal layer, allows for larger block sizes, reduces the number of repetitions, and is within working blocks. It is no longer necessary to embed FC repeaters. This well-design (FC sound, EM, minimal effort to combine sensible heat) and allows for recycling of hard-core IP. Significantly separate the design integration of the block chain integration into the full chip level. The repetitive approach has reached the near-final quality of time at the beginning of the design cycle, with minimal disruption to the design process.

Using a comprehensive and integrated set of approaches adopted at the beginning of the design cycle, they were able to strategically distinguish a few aspects of IC design. The development of RTL, complete chip integration, time, cell-based composition, context, and repository form are almost identical. Solid disintegration from FC integration, timing, and work block integration expands FC's visual interface with larger working block sizes, pre-defined metal sharing, termination of embedded duplicate channels, and a specification base. This was achieved by reducing the time allocation to make the transaction calculated locally, schedule, performance, and complexity, able to provide a solid design with the best performance in the market while taking a break during development. a field of rice. Most of the new features described in this white paper are now part of the process of designing a processor, which provides the server processor with high performance and reliability in the market.

#### 2.1.2 Dual-Core Intel SoC Processor 65-nm 16-MB Shared On-Die L3 Cache

A 16MB single hole, 16-way associative cache for dual-core Intel SoC processor 7100 series using cell -0.624m2 of 65nm steel technology 8. Low power technology is used in the L3 repository to reduce both leaks and flexible performance. Sleep transistors are used in SRAM systems and peripherals to leak more than double the reservoir. Only 0.8% of the cache is unlocked to access the cache. Intensive Cache Safe Technology deployment using archives protects the archive from potential errors and unauthorized child deaths.

Jonathan Chang, Senior Member, IEEE et al. did an excellent job of demonstrating the use of 65-nm 16-MB Shared On-Die L3 Cache for Dual-Core Intel SoC Processor 7100 Series. The dual-core Intel SoC processor 7100 with LMB integrated storage up to 16MB is powered by 65nm process technology with 8-layer copper interconnect [3], [4]. This shows the dying image of the processor. It contains two cores, each containing 1MB L2. The processor has a total of 1.3 billion transistors, and each context has 100 million transistors.

The processor works at 1.25V and 3.5GHz. Supports 150W and 95W hot design power. The L3 repository and compatible mind set have different power source and context, PLL, and I / O. Here it shows four voltage sources for the processor. The front side bus can operate at 800 or 667 MT / s in 3 load configurations. Both L3 and L2 use the same 0 in the 624 m bit cell. Designed with SRAM arrays and their peripherals, the sleep transistors deliver an average power of 0.75 W / MB while always maintaining the archive content [5]. Total energy savings are more than double, with guaranteed silicon concentrations. Whenever possible, they use long-channel devices to further reduce power consumption. The power reduction option is applied to the same SRAM members to reduce power leaks in the inactive subarray. Aggressive clock entry, good sleep adjustment, and wake counters are used to reduce dynamic performance. Column duplicates are available for data and tag programs. Block redundancy is available in repository size. Intel Cache Safe Technology (formerly known as Pellston Technology) tracks random ECC events for each repository line and disables possible errors and repository lines that often die in children. A variety of test solutions are available to ensure performance.

Sensible repository size is 16MB. It's 19MB with ECC and no need. L3 Cache is an associative repository of 16 sets and 16 set modes. The repository line is 6 4 bytes with two blocks sent to the data bus. Each episode has 256 data bits, 32 ECC bits, and two idle bits. Each local address is 40 bits long. Cache size achieved by reducing the set. The set can be adjusted to 16K, 8K, and 4K. This summarizes the cache configuration of the three main configurations, 16M, 8M, and 4M. The established organization remains 16 in all three settings. Set reduction is used to achieve the target repository size. The data path and control concept associated with the tag list are designed to support the widest tag range from 4M configuration.

Low power consumption is one of the main objectives. Many low-energy technologies are used to achieve design objectives. N sleep design is used in the SRAM system. Sleep bias can be set between  $50 \, \text{and} \, 300 \, \text{mV}$ . The Psleep design was used in the repository peripherals such as decoders, WL drivers, and I / O repository. Floating bit beams are used in local bit lines. The shutdown method can be used with invalid subarrays in 4M and 8M configurations. The wake-up counter has been used to improve the performance of the sleeping design. Long channel devices are widely used to reduce power consumption. Here shows the n sleep design SRAM of the same members.

The bias circuit controls the temperature change of the visible area. Sleep bias is so structured and manifold in such a way that the variability in the visible area at process angles and temperatures is within the specification. Added nMOS diode and pMOS pulse to control temperature change of visible area use of the diode structure as sleep bias is described in [6] and [7]. In contrast, the visual support of this publication is largely controlled by the flexible electric current, and the diode structure is used to reduce flexibility.

When VSS visible exceeds transistor threshold voltage (Vt), MND is turned on because Vgs is greater than Vt. Since Vds is larger than Vt, the MPB pull function is also very important. As a result, virtual VSS is limited to 1Vt or less. As the temperature rises, the Vt of MND and MPB decreases, the transistor becomes more powerful, and the bit cell leaks more, preventing significant increases in visible ground. Cowardice. This indicates a change in the visual environment due to the temperature and fluctuations of the device. During closure, sleep bias is disconnected from the ground, the pMOS diode is shut off, and the visible ground floats upwards.

PMOS sleep is used in the scanner and I / O cache. This includes the repeating column (MUX), the write driver, and the sensor amplifier. Figure 9 shows the sleeping design of the decoder and the WL driver. Figure 10 shows the I-O Core repository psleep design. When repository I / O is in sleep mode, thin lines float to minimize leakage of the thin line. This also avoids DC throughout the MUX reading / write column when operated by Vcc. The Vcc decoder and Vcc repository for virtual I / O is a fixed setting, limited only to stay within a given Vcc drop point so that reasonable values should be found in the word line during sleep mode. The given drop from Vcc of the word is chosen to achieve reasonable energy savings without producing significant sound. The nMOS diode (MND) is used to limit the decrease in power in visible Vcc.

Slight line chargers are not included in the design of sleep transistors to avoid long charging times and to meet the strict line-of-line measurement requirements that amplify different sensors. The timer has been deliberately removed from sleep construction because time is of the essence. Whenever possible, long Le transistors are used in the timer without sacrificing the accuracy of the signal edge. With the cache peripheral psleep design, it saves up to about 6W. All 16 routes are contained in one block, mainly hiding the delay penalty by opening the sleep transistor and reducing the number of blocks and Subarray unlocked.

This indicates the allocation of unwanted bits to each part of the data repository line. Each component has two inactive columns, and each repository row can fix two random bugs. This repetition program also deals with errors in line-based bit cells. You can adjust up to 8 sets of bit positions. Three bits of local address used to control MUX no longer active. The defunct MUX bit is selected so that the total independent adjustment value remains the same in the 4M and 8M configurations. Particle size of part subarray. The now defunct MUX is used in the global data route. Unnecessary columns are used for each tag. You can fix a random error in any of the entries. Here, unnecessary bit allocation for each tag. A total of 4 possible locations can be adjusted independently of each other. Most SRAM cells are in sleep mode with reduced operating bias, which uses ECC technology and Intel Cache Safe to ensure the integrity of the repository. Complete post-silicon alignment specifications and statistical analysis are performed to ensure that the product meets the reliability specification. For the data system, each of the 8 bytes data is protected by SECDEDECC. Larger tag size is also protected by SECDEDECC. In addition, the database is protected by Intel Cache Safe Technology. If ECC adjustments are received after production, up to 32 repository lines or up to 2 modes per set may be disabled. This has little effect on performance. Cache line will be disabled until reset. Power repository line malfunction has

been used to correct Vccmin sensitivity to potential errors. The live history table (Pellston Engine line) traces the random ECC events of each repository line. Unlike previous uses, this flexible cache line functionality allows you to separate random cache holes. If the ECC error occurs for the first time in the cache line, it may be a soft error. If the ECC error occurs twice in the same area, it means it will not be a soft error and may be a physical problem as an error. Potential feature or low VCC sensitivity.

Cache security technology is enabled for both self-testing of power and normal operation of. When a 1-bit ECC error is detected, the ECC intelligence informs the Pellston engine of the error information. This includes a set of Global Bus Queue (GBSQ) and route information. If the specified set and route meet the error first, the input is inserted into the Pellston engine line. Cash method is not disabled or cleared by default. If the error is the second error in the same area, the Pellston engine intervenes and deactivates the corresponding archive lines. Many features of the test are performed to ensure that the 16MB -L3 cache is checked and executed. PBIST is widely used in both error correction and silicon test cover. Low yield analysis, pWWTM, and stability testing methods are used. A series of indie diversity was available to employ indie diversity. To fix the speed limit there are many clock circuits.

The reported processors have a large on-die L3 repository and transistors x86 processors. Low power design allows you to save more than twice as much energy in your repository. Extensive design, reliability, and testing capabilities ensure warranty production and reliability. The processor is marked to meet the power envelope and frequency terms.

#### 2.2 Power Reduction Techniques for an 8-core SoC

Stefan Rusu et al. did an excellent job of introducing power reduction solutions and managing the 45nm, 8-core Nehalem-EX processor. Using multiple clocks and voltage sources to reduce power consumption. Long station equipment and cache sleep mode are used to reduce leakage. Core acquisition and cache improve productivity yield and allow for a wide range of products from the same silicon chip. Clock and Power gating reduce power consumption of invalid blocks. Microcontroller Only controls voltage and frequency, as well as current events and temperature driving points. Load power is reduced by switching off the I / O connection of the power controller and the switch phase to improve the efficiency of power conversion.

Power efficiency is the main design goal of this 45nm, 8-core, 16-thread SoC processor. The total performance of the hot design remains at 130W, in line with previous generation processors, but the number of cores per socket increases by 2 cores each year. The processor has 2.3B transistors, which are used in 45nm CMOS process technology using High-K metal gate dielectric transistors and nine layers of copper wires [8]. IOOO X for PMOS transistors compared to 65nm process production.

The processor is integrated into a 14-layer live grid system package (545), 1567-rand, 40 mil pitches, and an integrated heat exchanger. The processor supports multiple platform configurations, from dual processor options to quads up to 8 options. The image of the processor chip whose main block is marked [9]. The shared L3 repository is divided into eight pieces. Each piece of cache works with the processor core, but the entire L3 repository is considered by all cores as one large, shared repository. The upper side of the floor plan consists of four point-to-point quick path interconnect (QPI) connectors operating at 6.4 GT / s, while the lower side maintains a visible connector. The central channel consists of two memory controls, two harp links in the cache, an 8-hole router, a power control unit, and a visual system interface including the OFT control box. The Uncore Clock generator and

fuse box are also located in the center of the channel. Primary and repositioning is a method of crop improvement that has been made possible by placing many of the same contexts and the repository in one place. If one of the cores has a production feature, close the spine and restore that part as a low point. The same applies to large repositories that cannot be repaired by duplicate built-in repository. Key cache and cache fragments are disabled in horizontal alignment, but disabled cache fragments and key fragments do not need to be aligned. Few combinations are possible, which cover most of the chip width and allow for better recovery.

To allow all eight cores to be tested seamlessly, the chip is redesigned and each context will see the aligned cache piece as its dedicated repository. In this way, all eight cores use a test pattern simultaneously, allowing the tester to quickly determine which cores are appropriate and which cores need to be disabled. Ondie, a one-time electrically adjustable fuse used for content acquisition and storage. The initial die triage and merging are performed on the wafer type and re-validated during the final test.

The disabled context has a clock and power control and is logically disabled to avoid using power in a customer system with a function line that does not give value to the user. The deformed cocoon piece is also closed and powered down, reflecting infrared radiation back from the chip, with only six active cores. A light gray shade indicates that the flexibility and leakage are high and that photon emissions are increasing. Two closed cores are dark in the image because they do not emit infrared light. One bright spot for each course is due to the heat sensor, which is powered by a clean PLL voltage field and is not affected by the main power gates.

This shows a block diagram of the power control unit (PCU). The PCU is a small controller with a few circuit breakers that control the output of the main voltage and the main power gate, controls the transition between different operating conditions of the application, and controls the detection and response of thermal events. The PCU detects the output voltage of the main voltage and the sensor of temperature and power required in each context.

The microcontroller calculates the voltage ID bit that adjusts the frequency with the external power controller of the core PLL. The PCU also controls the temperature sensor by lowering the voltage and frequency to maintain the chip temperature within safe reliability limits. If the temperature or operating voltage exceeds the reliability limit, the PCU shuts down the PLL and the external power controller to protect the chip processor from catastrophic failure.

A guideline to reduce idle energy is to reduce energy consumption in unused blocks. An example of reducing the power consumption of an unused I / O connection. There is a platform setting where the I / O connection is not finalized. Dual processor platforms usually use only two or three links (of the 4 available on each chip) and leave the rest unused. The partially implemented quad processor platform also has multiple unconnected links. To detect these conditions, they implemented the connection detection circuit. It detects the presence of the Rx terminator at the other end of the link. At on the left side of the figure, there is an Rx term that pulls the connection to less than half the VCC level (the Rx termination resistor on the receiving chip is much lower than the pull-up resistor on the driver chip).

Stefan Rusu et al. did an excellent job of introducing power reduction solutions and managing a 45nm, 8-core Nehalem-EX processor. Using more watches and power sources to reduce energy consumption. Long channel equipment and cache sleep mode are used to reduce leakage. Critical discovery and repository improves production productivity and allows for a wide range of products from the same

silicon chip. Clock and Power gating reduce power consumption of invalid blocks. Microcontroller controls voltage and frequency only, as well as current events and temperature driving points. Loading capacity is reduced by turning off the I / O connection of the power controller and the switch phase to improve the efficiency of the power conversion.

Power efficiency is the main design goal of this 45nm, 8-core, 16-thread SoC processor. The total performance of the hot design remains at 130W, in line with previous generation processors, but the number of cores per socket increases by 2 cores each year. The processor has 2.3B transistors, which are used in 45nm CMOS process technology using High-K metal gate dielectric transistors and nine layers of copper wires [8]. IOOO X for PMOS transistors compared to 65nm process production.

The processor is integrated with a 14-layer grid system package (545), 1567-rand, 40 mil pitches, and an integrated temperature switch. The processor supports multi-platform configurations, from dual processor options to up to 8 options. The image of the processor chip whose main block is marked [9]. The L3 repository is divided into eight pieces. Each piece of cache works with the processor core, but the entire L3 repository is considered by all cores as one large, shared space. The upper side of the floor plan consists of four point-to-point quick path interconnect (QPI) connectors operating at 6.4 GT / s, while the lower side maintains a visible connector. The central channel consists of two memory controls, two harbor link connectors, an 8-hole router, a power control unit, and a visual system interface including the OFT control box. The Uncore Clock generator and fuse box are also available in the center of the channel. Basic and repositioning is a method of plant development that has been made possible by placing many similar themes and storage in one place. If one of the cores has a production feature, close the spine and replace that part as a low point. The same applies to large repositories that can be repaired with a built-in repetitive storage component. Core pieces and cache pieces are locked in a horizontal alignment, but disabled cache and key pieces do not need to be aligned. Few possible combinations, which cover most of the chip width and allow for better recovery.

To allow all eight cores to be easily tested, the chip is redesigned and each context will see a piece of aligned cache as its final dedicated area. In this way, all eight cores use a test pattern simultaneously, allowing the tester to quickly determine which cores are appropriate and which cores need to be disabled. Ondie, a one-time electrically adjustable fuse used for content acquisition and storage. The first triage of death and fusion is performed on a wafer type and re-confirmed during the final examination.

Disabled content has a clock and power control and is logically disabled to avoid using power on a client system with a performance line that does not give value to the user. The crippled cocoon piece is also closed and degraded, showing infrared radiation from the chip, which has only six active coils. A light gray shade indicates that fluctuations and leaks are high and that photon emissions are increasing. Two closed cores are dark in the image because they do not emit infrared light. One bright spot for each study is due to the heat sensor, which is powered by a clean PLL electric field and is not affected by large power gates.

This shows a block diagram of the power control unit (PCU). A PCU is a small controller with a few circuit breakers that control the output of the main voltage and the power gate, controls the transition between different operating conditions of the application, and controls the detection and response of thermal events. The PCU detects the output voltage of the main voltage and the sensor of temperature and power required in each context.

The microcontroller calculates the voltage ID bit that adjusts the frequency with the external power PLL controller. The PCU also controls the temperature sensor by lowering the voltage and frequency to maintain the chip temperature within safe reliability limits. If the temperature or operating voltage exceeds the reliability limit, the PCU shuts down the PLL and external power controller to protect the chip processor from catastrophic failure.

Guide to reducing inefficiency to reduce energy consumption in unused blocks. An example of reducing the power consumption of an unused I/O connection. There is a platform setting where the I/O connection is not completed. Dual processor platforms typically use only two or three links (out of 4 available per chip)

## 2.3 Parallel Mutual Information Based Construction of Genome-Scale Networks on SoC

Building a whole genetic network from big data genetics is an important issue for system biology. Some technologies have been developed, but most cannot handle genome-wide network reconstruction, and other technologies that can support it, require larger clusters. Sanchit Misra, et al. have done excellent research by proposing a solution to the Intel SoC Phi coprocessor [10], using its similarity involving multiple levels including multiple x86-based cores, multiple cables per core, and vector processing units. They also introduced a solution for Intel SoC processors. Our solution is based on TINGe [11], [12] how to update the same fast network using the same information and authorization tests [13] to assess statistical significance [11]. By building a 15,575 genetic network of the Arabidopsis plant from a 3,137 microarray test in just 22 minutes, we demonstrate the first consideration of a plant genome control network on a single chip. In addition, statistical comparisons of integrated data on Intel SoC Phi coprocessor provide lessons that can be applied to other domains.

Building or reversing genetic network engineering in genetic testing over multiple test conditions is an important issue for systematic biology. Such networks can be used to identify statistically significant relationships between genetics and model control models within a mobile system. Differences between such networks in different sets of conditions can be used to study genetics and speech patterns that are important to the behavior of an organism in all areas of interest. At the heart of allowing such programs is the problem of building networks from data. The input problem for network construction is a rectangle with lines such as lines, columns as shapes, and inputs that show a limited amount of statement after processing the statistics to eliminate the results. of sound and diversity testing, Gene expression matrix. The output is a graph, where the nodes represent the genes and the edges represent the relationships of interest. This may vary depending on the design of such a network. For example, the edge represents co-expression in the co-expression network and reflects the control effects on the genetic control network. In the Bayesian network, the network represents only the integrated feature of the hidden distribution of hidden opportunities.

When the G [i] viewing vector is loaded into the L1 spinal cord, it ensures that all pairs (G [i], G [j]) are processed in the same context. Hyper-threading on the core shares L1cache, so assign hyper-threading to work with the same G [i] and different G [j] viewers. This shows an example of a multi-threaded n<sup>1</sup>/<sub>4</sub> 16 method with 5 cores with 4 strands of each spine. loop span line 312 diagram. 1 calculates the upper triangle of the 1616 matrix represented by the cells shown in white. For each line

in the matrix, Cz (where z 2 f0; 1; 2; 3; 4g) refers to the nucleus to which the line is assigned. Number in a cell means the corresponding hyper-thread of the core to which that cell is assigned. Assign 1 context for each row in the first combined 5-row block. To spread the load on each course, assign one theme to each row, while releasing the cores distribution plan for each subsequent block in row 5. The MI figure does enough work to hide memory delays and does not require cache blocking. Additionally, the approval test section requires a predefined vector observation Y (row 7) to be in the L2 repository.

Adjustment of Scalar static instructions, as well as co-processor and vector-enabled launch of the CPU. Clearly, the use of vectorised significantly reduces the number of commands required. However, there are a few reasons why vectorization reduction instructions are incorrect. The critical area has instructions for accessing memory with very high density (88 percent or 69 percent, of vector usage). Most of these memory access W and P'XY, which can be found in the L2 repository. In addition, access to memory is rare. Many uncommon access is classified as L2 and requires aggressive downloads from the co-processor. However, adding a download to P'XY affects performance, so you can add a download to W. This is because (i) the total number of commands when you add this download is large, (ii) too many preload instructions that cause the download cache block, and (iii) the download delays for other required commands. It may be due to inability to hide. In addition, the amount of vectorization is limited, as shown in the table. Some commands in both processors are scalar commands. Additionally, for co-processor and CPU, approximately 50% and 35% of vector commands are low vector power distributions, respectively. Under appropriate vectorization conditions, the coprocessor only needs, which is part of the CPU cycle calculation. However, because there is no vectoring space in this loop, the number of cycles required to perform the same amount of work when both processors work in the same context is not significantly different, there is no. If both processors use all cores, the higher the number of cores in the co-processor the better the performance.