# Simulation based Design of Double Gate TFET Structure for better Analog performance by Gate Metal Work Function Modulation

This thesis is submitted for the partial fulfilment of the requirement for the Degree of Masters of Engineering (M.E) in the Department of Electronics and Tele-Communication Engineering (ETCE) under the Specialization of Electron Devices.

#### By:

#### **Snehashis Biswas**

(UNIVERSITY REGISTRATION NO: 154083 of 2020-21)

(EXAMINATION ROLL NO: M4ETC22014)

UNDER THE GUIDANCE OF

**Prof. Subir Kumar Sarkar**

DEPARTMENT OF ELECTRONICS & TELECOMMUNICATION ENGINEERING

JADAVPUR UNIVERSITY

**KOLKATA - 700032**

August 2022

### FACULTY OF ENGINEERING AND TECHNOLOGY JADAVPUR UNIVERSITY

#### **CERTIFICATE**

This is to certify that the thesis entitled, "Simulation based Design of Double Gate TFET Structure for better Analog performance by Gate Metal Work Function Modulation" submitted by Snehashis Biswas (Roll No.: 002010702014) of Jadavpur University, Kolkata is a record of legitimate research conducted under my supervision and guidance that may be accepted in partial completion of the requirements for the Master of Engineering in Electronics and Tele-communication Engineering with a specialisation in Electron Devices from the Institute. Any other paper submitted for the award of a degree to any other University or Institute does not include the research results reported in this thesis.

#### Prof. Subir Kumar Sarkar

Supervisor & Professor

Department of Electronics &

Telecommunication Engineering

Jadavpur University, Kolkata-700032

.....

#### **Prof. Manotosh Biswas**

Head of Department of Electronics & Telecommunication Engineering Jadavpur University, Kolkata - 700032

#### Prof. Chandan Mazumdar

Dean

Faculty Council of Engineering

& Technology

Jadavpur University, Kol-700032

## FACULTY OF ENGINEERING AND TECHNOLOGY JADAVPUR UNIVERSITY

#### **CERTIFICATE OF APPROVAL\***

The foregoing thesis is hereby approved as a credible study of an engineering subject and presented in a manner satisfactory to authorization acceptance as a pre-requisite to the degree for which it has been submitted. It is understood that by this approval the undersigned do not necessarily endorse or approve any statement made, opinion expressed or conclusion drawn there in but approve the thesis only for which it is submitted.

| Committee on Final Examination for the Evaluation of the Thesis: |  |  |  |

|------------------------------------------------------------------|--|--|--|

| Signature of External Examiner                                   |  |  |  |

| Signature of Project Supervisor                                  |  |  |  |

\*Only in the case thesis is approved

### FACULTY OF ENGINEERING AND TECHNOLOGY JADAVPUR UNIVERSITY

### DECLARATION OF ORIGINALITY AND COMPLIANCE OF AN ACADEMIC THESIS

I hereby certify that this thesis entitled, "Simulation based Design of Double Gate TFET Structure for better Analog Performance by Gate Metal Work Function Modulation".

**\***

There has been no submission of this work to any other institute for any degree.

All information was gathered and presented in compliance with academic regulations and the institute's ethical Code of Conduct.

I further declare that, as required by the rules and conduct, I have given correct credit whenever I have utilized materials that are not unique to this work by citing them in the thesis text and providing their information in the list of references.

#### **SNEHASHIS BISWAS**

Roll No.: 002010702014

Thesis Title: "Simulation based Design of Double Gate TFET Structure for better Analog Performance by Gate Metal Work Function Modulation".

Signature of Student

Snehashis Biswas

Acknowledgements

I feel immense pleasure in expressing my sincere gratitude to my thesis supervisor Dr.

Subir Kumar Sarkar for his invaluable guidance and advice during every stage of diffculty.

I am very grateful to him for creating strong interest in the work and continuous

encouragement and support without which, it would not be possible for me to complete my

work successfully amid this pandemic. He has helped to develop a research perspective.

The intellectual and personal growth that I have experienced under his supervision cannot

be overstated. I sincerely extend heartfelt thanks to my teachers at Jadavpur University,

I would like to thank all my friends and my seniors who supported me during my thesis

work. Finally, I express my sincere thanks to my parents for their continuous support and

faith they have on me for those all those thick and thin moments. I forever owe utmost

gratitude to the Almighty-GOD whose divine light and warmth provided me to inspiration,

faith and strength to carry on my work.

Signature: .....

**SNEHASHIS BISWAS**

M.E in Electron Devices

Department of ETCE, Jadavpur University

Kolkata - 700032, West Bengal, India

#### **List of CONTENTS**

| Contents                                                   |                                       |

|------------------------------------------------------------|---------------------------------------|

| List of Figures · · · · · · · · · · · · · · · · · · ·      | · · · · · · · · · · · · · · · · · · · |

| List of Abbreviation • • • • • • • • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • |

| Abstract                                                   | VII                                   |

| Chaper 1                                                   | 1-6                                   |

| Introduction                                               | 1                                     |

| Tunnel Field Effect Transistors                            |                                       |

| Motivation                                                 | 5                                     |

| Current Scenario                                           | 5                                     |

|                                                            |                                       |

|                                                            | 6                                     |

| 211 <b>4</b> 525                                           |                                       |

| Chapter 2                                                  | 7-47                                  |

| Literature Review                                          |                                       |

| Overview of MOSFET                                         | 8                                     |

| Types of MOSFET                                            | 10                                    |

| Operational regions of MOSFET                              | 12                                    |

| Analytical model description of MO                         | OSFET                                 |

| Advantages of MOSFET and its sui                           | table applications                    |

| Power consumption in MOSFETS .                             |                                       |

| MOSFET scaling and its consequer                           | aces                                  |

| Short Channel Efects                                       |                                       |

| 2D Electric field profile                                  |                                       |

|                                                            | BL)                                   |

| _                                                          | on carrier mobility                   |

| _                                                          | he channel                            |

|                                                            |                                       |

| Impact on ionization                                       | 24                                    |

I

| Parasitic bipolar effect                       |  |

|------------------------------------------------|--|

| Hot carrier effect (HCE)                       |  |

| Gate oxide charging                            |  |

| Channel Length Modulation                      |  |

| Punch through                                  |  |

| Body Effect                                    |  |

| Channel Length Modulation                      |  |

| Velocity Saturation                            |  |

| Subthreshold Slope and Avg. Subthreshold Slope |  |

| Evolution of advanced MOSFET structures        |  |

| Silicon On Insulator (SOI) MOSFET              |  |

| Multi-gate MOSFET                              |  |

| Gate work function engineering                 |  |

| <b>Chapter 3</b>                               |  |

| Tunnel Field Effect Transistors                |  |

| MOSFETs vs TFETs                               |  |

| Working Principle                              |  |

| Tunneling Mechanisms                           |  |

| Line Tunneling                                 |  |

| Point Tunneling                                |  |

| Line Tunneling Vs Point Tunneling              |  |

| Conclusion                                     |  |

| <b>Chapter 4</b>                               |  |

| Simulation                                     |  |

| Silvaco Atlas TCAD Simulation Basics           |  |

|                                                |  |

| (           | Chapter 5                           | 58-69 |

|-------------|-------------------------------------|-------|

| Double Gate | TFET (DG-TFET)                      |       |

| Propo       | osed Structure                      | 58    |

| Device      | ce Simulation Setup                 | 59    |

| Electr      | tric Field vectors                  | 59    |

| Electi      | tric Field Variations               | 60    |

| Electi      | tron Concentration Variations       | 62    |

| Poten       | ntial Variations                    | 63    |

|             | gy band diagrams                    |       |

| _           | neling                              |       |

|             |                                     |       |

|             | hreshold Swing                      |       |

|             | shold Voltage                       |       |

|             | neling Rate                         |       |

|             | Current and $I_{ON}/I_{OFF}$        |       |

|             | clusion                             |       |

|             | pter 6                              | 70-74 |

|             | log/RF Performance of DG-TFET       |       |

|             | duction                             |       |

| Trans       | sconductance of DG-TFET             | 70    |

| Capa        | acitances of DG-TFET                | 71    |

| Unity       | y Gain Bandwidth Product of DG-TFET | 72    |

| Trans       | sfer Characteristics of DG-TFET     | 72    |

| Conc        | clusion                             | 74    |

| Cha         | pter 7                              | 75-80 |

| Conc        | clusion and Future Work             |       |

| Conc        | clusion                             | 75    |

| Futur       | re Possibilities                    | 75    |

| Refer       |                                     | 77    |

#### **List of Figures**

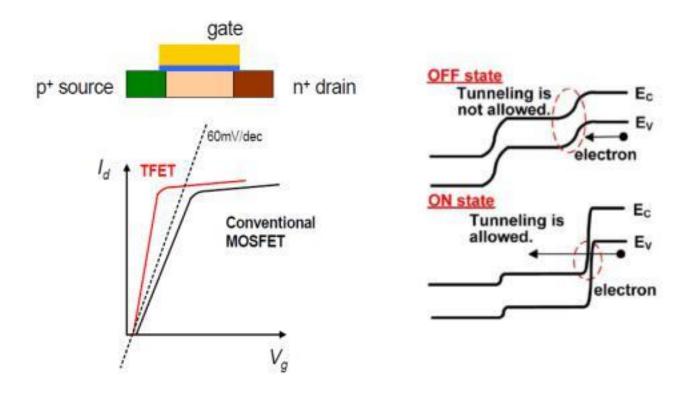

Id~Vg curve of TFET

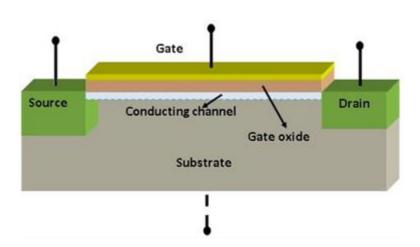

Basic MOSFET structure

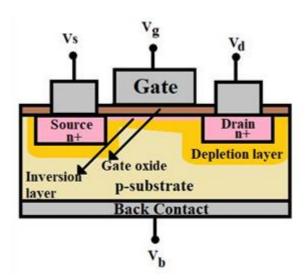

Schematic representation of n-channel MOSFET

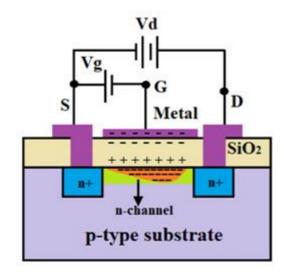

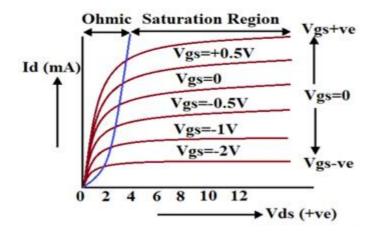

N-channel depletion mode MOSFET

N-channel depletion mode MOSFET current-voltage characteristics

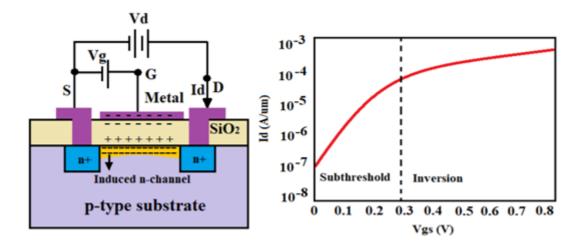

Basic n-channel Enhancement mode MOSFET structure

N-channel Enhancement mode MOSFET's Id-Vgs characteristics

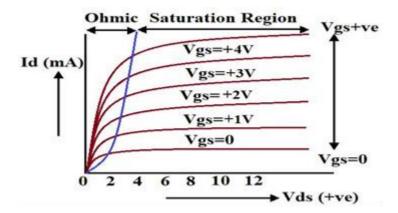

Current-Voltage characteristics of n-channel Enhancement mode MOSFET

Different regions of operation in drain current characteristics of MOSFET

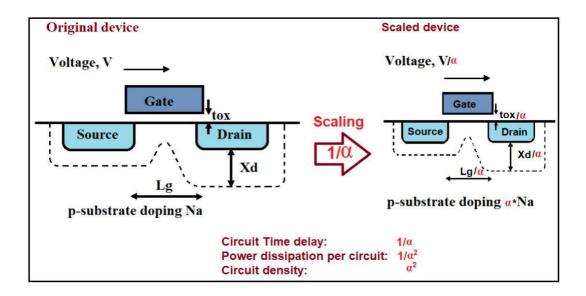

Scaling rule

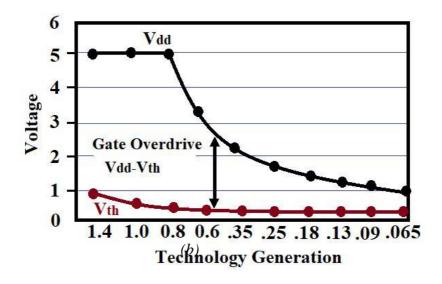

Scaling trend of supply voltage

Moore's law

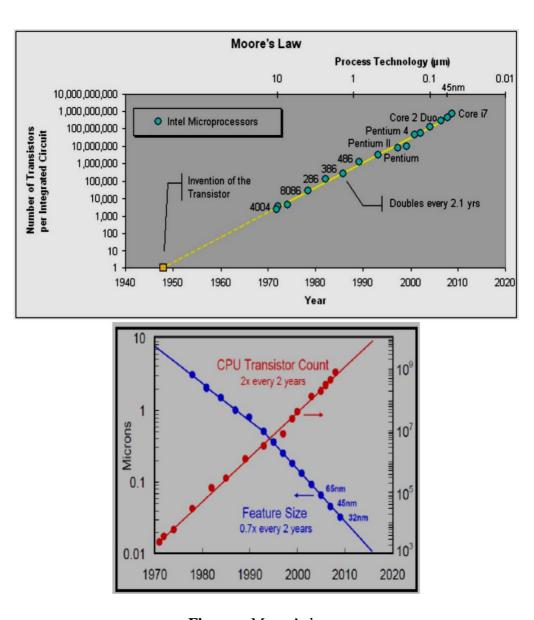

Surface potential variation along lateral position

Saturation in carrier velocity with incremented gate voltage

Generation of electron-hole pairs due to electric field induced impact ionization

Channel length modulation and effect on drain current characteristics of MOSFET

Body Effect in short channel devices

Channel Length Modulation in short channel devices

Variation of output characteristics due to Velocity Saturation in short channel devices

Cross-sectional representation of SOI MOSFET

Cross-sectional view of Partially Depleted SOI MOSFET

Cross-sectional view of Fully Depleted SOI MOSFET

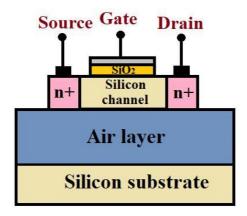

Schematic of Silicon On Nothing (SON) MOSFET

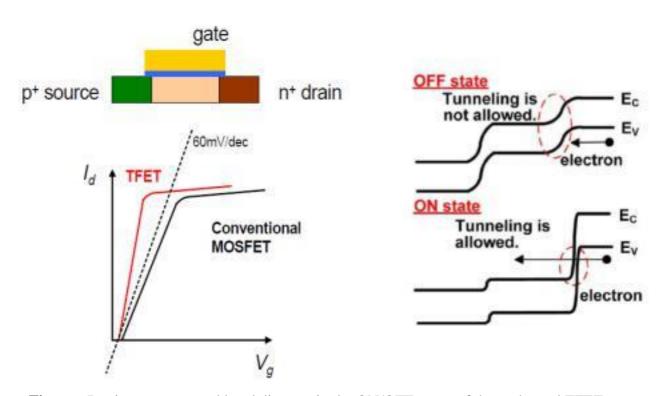

Device structure and band diagram in the ON/OFF states of the n-channel TFET

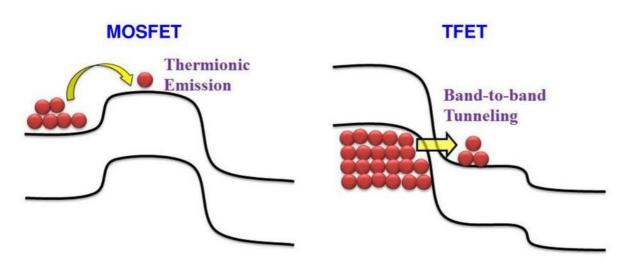

Working principle of MOSFET vs TFET

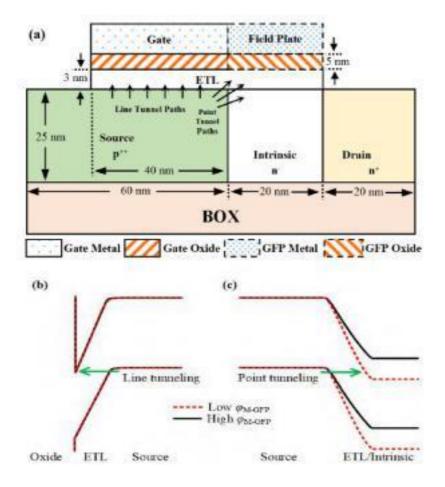

Energy Band Diagram for Line Tunneling and Point Tunneling

Point Tunneling from Source to Channel

Line Tunneling and Point Tunneling happening in a single structure

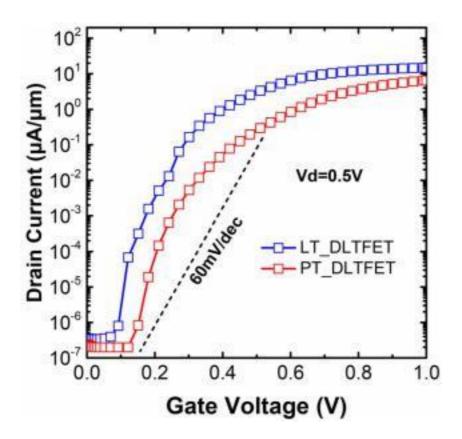

Drain Current Comparison between Line Tunneling and Point Tunneling

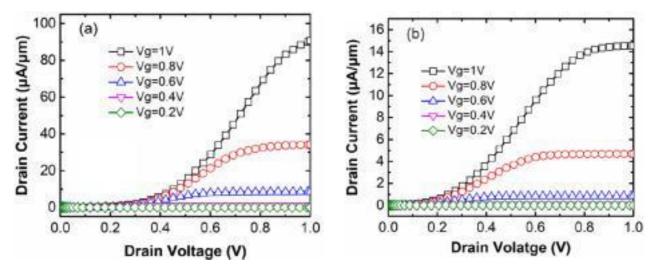

Output Characteristic Comparison between Line Tunneling and Point Tunneling

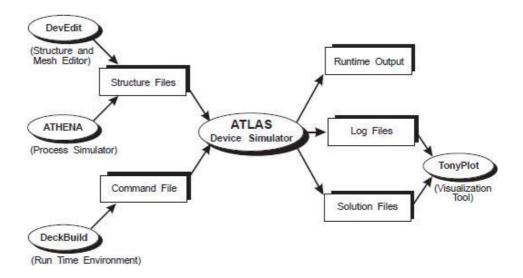

Inputs and Outputs of Atlas device simulator

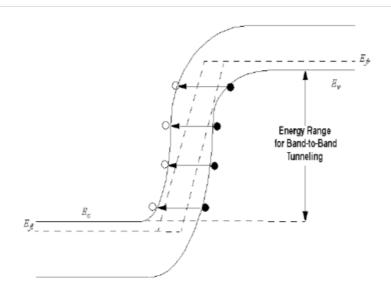

Schematic of non-local band to band tunnelling

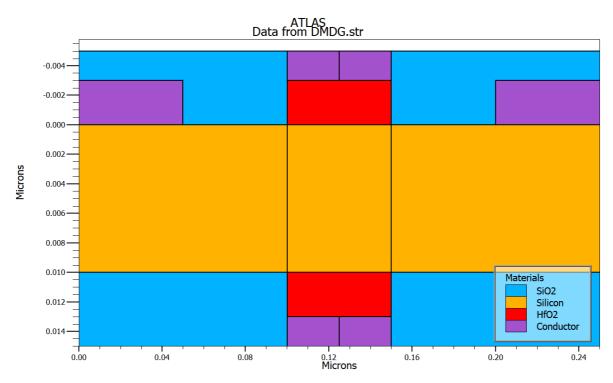

Proposed DG-TFET 2D model

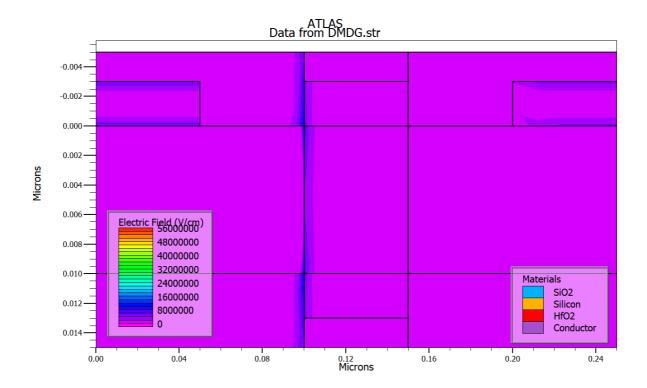

Electric Field

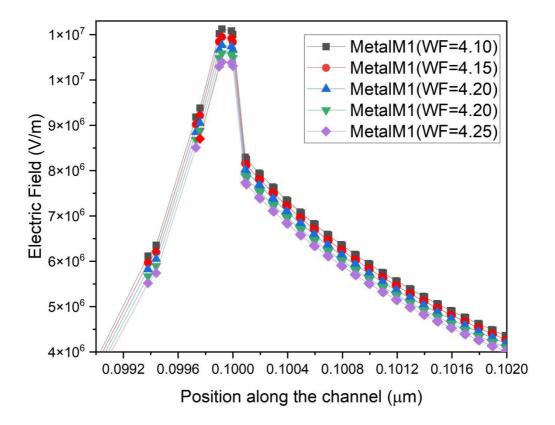

Electric Field Variation with different work functions at gate oxide width of 2nm

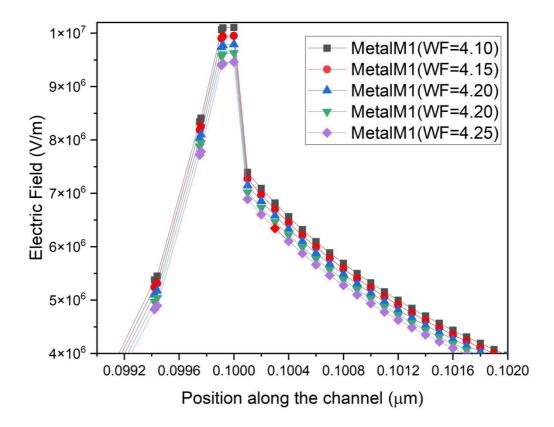

Electric Field Variation with different work functions at gate oxide width of 3nm

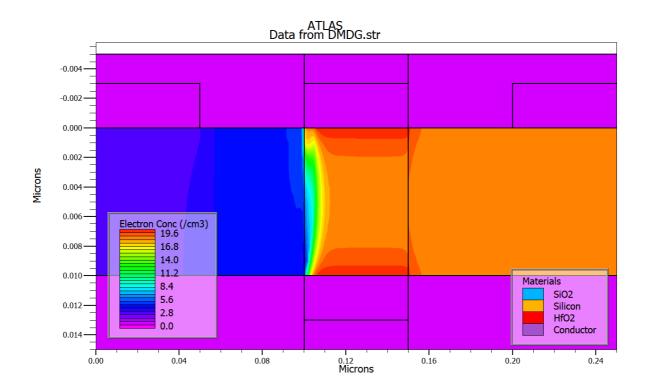

Electron Concentration when DG is ON

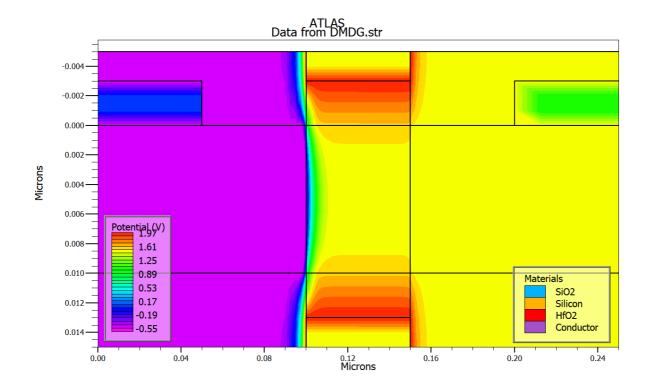

Potential variation

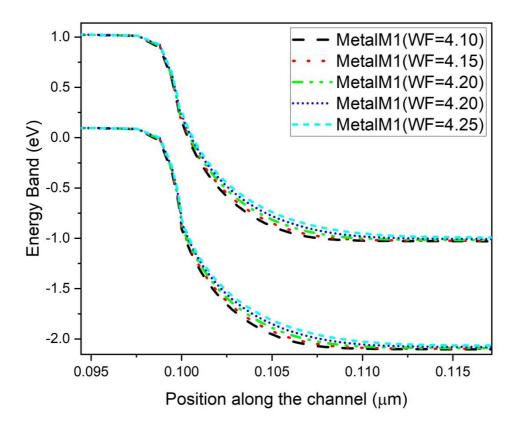

**Energy Band Diagram**

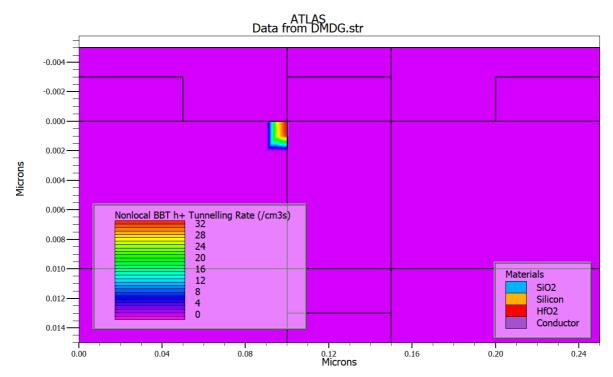

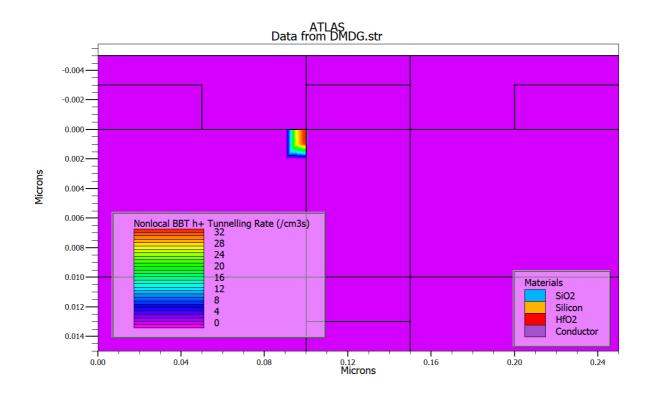

Hole Tunneling in Double Gate TFET

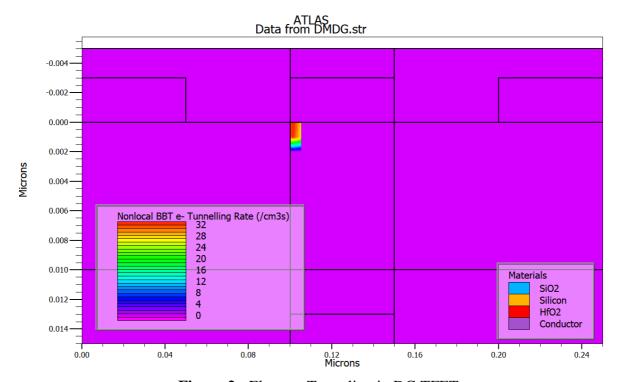

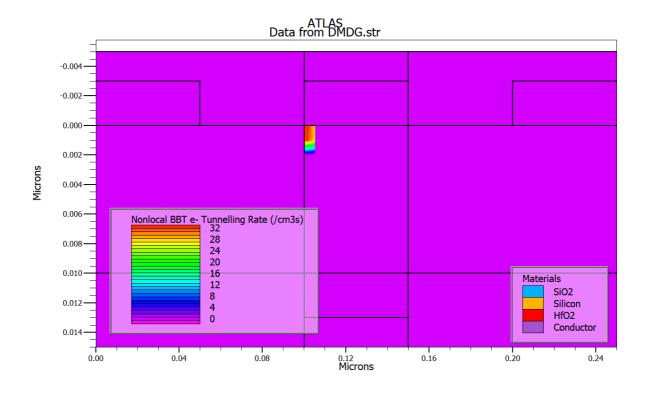

Electron Tunneling in DG TFET

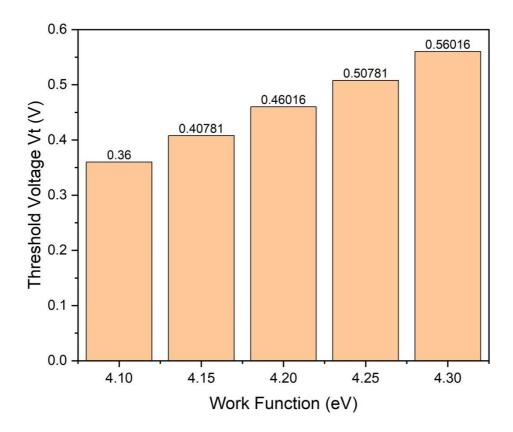

Threshold Voltage Variation with different Gate Metal Work Function at Gate Oxide width of 2nm

Non-Local Band to Band Tunneling of Hole

Non Local Band to Band Tunneling of Electron

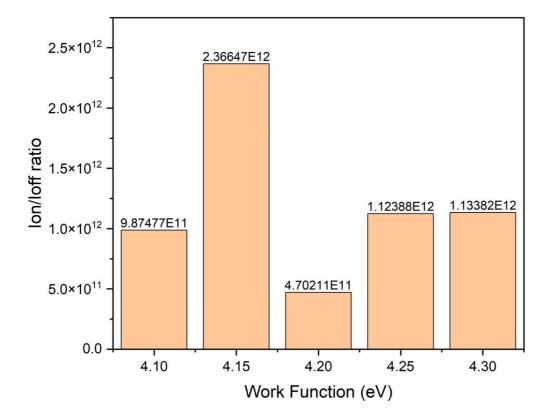

Ion/Ioff ratio Variation with different Gate Metal Work Function at Gate Oxide width of 3nm.

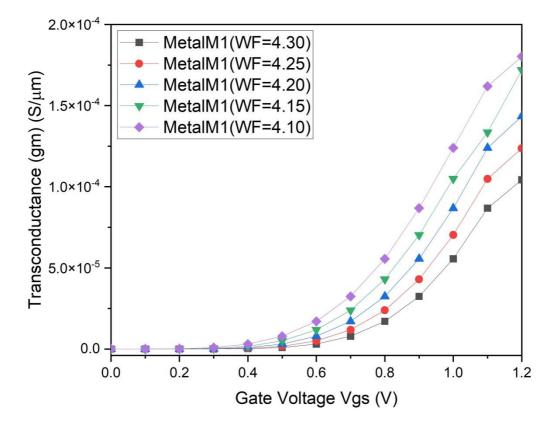

$g_m$  vs  $V_{gs}$  for various gate metal work function

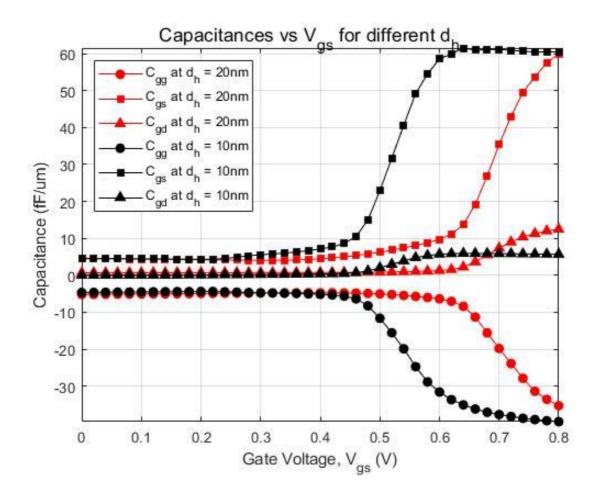

$C_{gg},\,C_{gs}$  and  $C_{gd}$  vs  $V_{gs}$  for various drain heights, dh

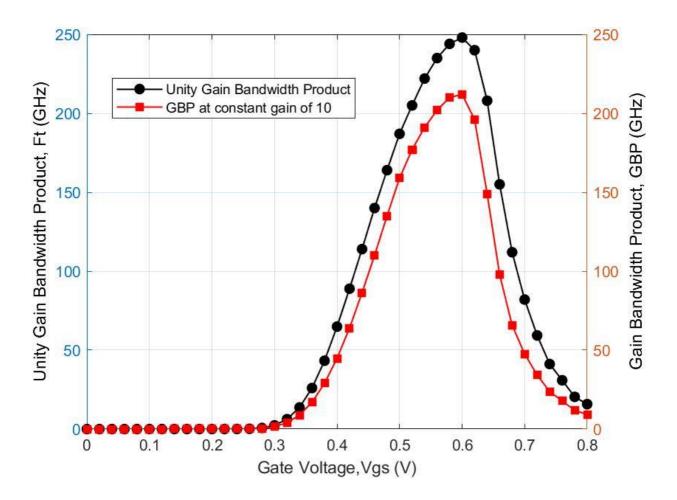

Variation of  $f_T$  and GBP with  $V_{\rm gs}$  for  $d_h=20~\text{nm}$

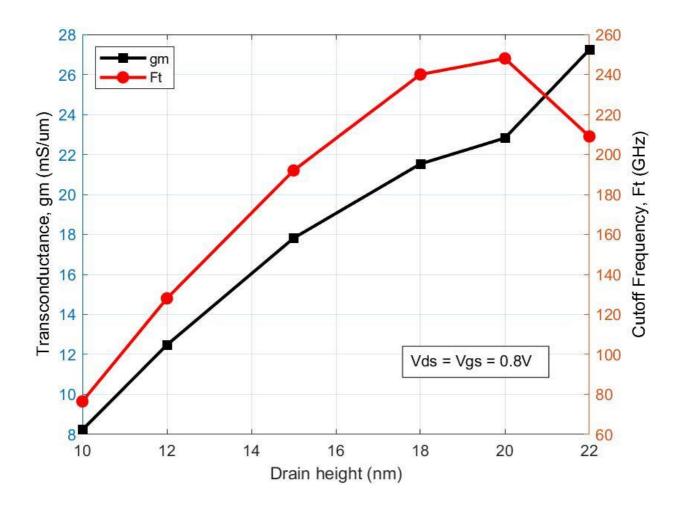

Impact of  $d_h$  on  $g_m$  and  $f_T$  of the DG-TFET

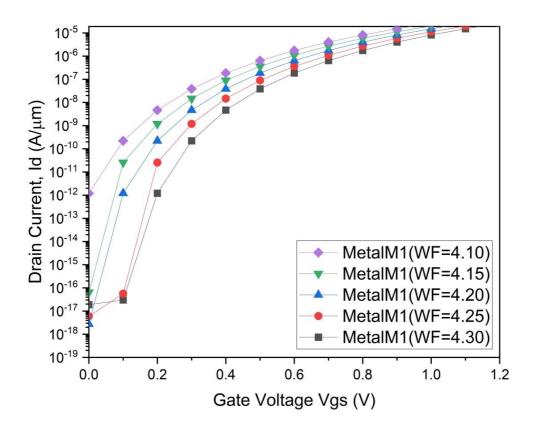

I<sub>D</sub> vs V<sub>GS</sub> of DG-TFET at different Gate Metal Work Function

#### List of Abbreviations

VLSI Very Large Scale Integration

ULSI Ultra Large Scale Integration

MOSFET Metal Oxide Semiconductor Field Effect Transistor

CMOS Complementary Metal Oxide Semiconductor

FET Field Effect Transistor

SCE Short Channel Effect

DIBL Drain Induced Barrier Lowering

TVRO Threshold Voltage Roll Off

HCE Hot Carrier Effect

SOI Silicon On Insulator

FD SOI Fully Depleted Silicon on Insulator

PD SOI Partially Depleted Silicon on Insulator

BOX Buried Oxide

SON Silicon on Nothing

DG Double Gate

TG Tri gate

GAA Gate All Around

DG TFET Double Gate Tunnel Field Effect Transistor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

TFET Tunnel Field Effect Transistor

#### **Abstract**

In this thesis, we have proposed a Double gate tunnel field-effect transistor (DG-TFET) to enhance the Analog/RF performance. The proposed structure has been optimized through simulations. The DG-TFET shows both point and line tun-neling. 2-D Simulations are carried out in Silvaco TCAD ATLAS tool using nonlocal band to band tunneling models. The optimized DG-TFET provides a low threshold voltage of 0.36 Volt, a low subthreshold swing (SS) of 17.55 mV/decade and a high  $I_{ON}$  / $I_{OF}$  f of 2.5 x  $10^{12}$ . Furthermore, the proposed device achieves a maximum transconductance,  $g_m$  of 1.75 x  $10^{-4}$  S/ $\mu$ m, an electric field, EF of 1x  $10^{7}$  V/m and a potential of 1.58 V. Here we shown, Design and Performance Investigation of Analog Performance of Double Gate TFET structure in this thesis.

Keywords: Band-to band tunneling (BTBT), inverter, line tunneling, sub-threshold swing (SS), transconductance, Tunnel Field Effect Transistor (TFET)

#### Chapter 1

#### Introduction

The vogue to follow the renowned Moore's Law has led to an enormous reduction in the dimensions of the transistors. This drastic reduction in transistor size, on the bright side, helped in packaging a huge amount of functionality in the ICs. However, on the pitfall, such scaling has surged the power dissipation and introduced various short channel effects (SCEs) in MOSFETs.

#### **Tunnel Field Effect Transistors**

The tunnel field-effect transistor (TFET) has proven to be one of the potential successors of MOSFET, due to the resemblance of their basic structures. Working of TFET is based on the band-to-band tunneling phenomenon, which is evidently different from that of MOSFET.

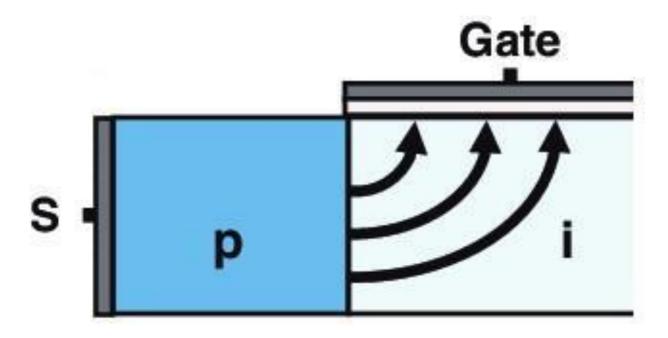

Basically a TFET is a reversed-biased p-i-n diode with gate modulation of tunneling probability. A typical TFET structure with band diagram is as shown in Figure. at off state, the potential barrier between channel and the source is so wide that no tunneling occurs. In the on-state, gate voltage modulate the potential barrier and makes it narrow to allow a significant tunneling current. Theoretical analysis showed that the SS value of TFET can be reduced to below 60mV/dec. More recently several groups have shown experimental results and confirmed that in a certain bias range the SS can be reduced below 60mV/dec.

Making the gated tunnelling process more effective while successfully suppressing numerous leakage paths is the main challenge with TFET. The bandgap energy, reduced effective mass, and electrical field within the tunnel barrier are three variables in the exponential term that have a significant impact on the likelihood of tunnelling, as shown in equation. Low tunnel barrier height is preferred by an efficient tunnelling process, which is dictated by the bandgap energy, and In an abrupt pn junction, a short tunnel width typically translates to a large electrical field. The decreased effective mass is mostly reliant on the material and highly sensitive to bandstructure alteration caused by quantum confinement, strain effect, etc.

**Figure :** Device structure and band diagram in the ON/OFF states of the n-channel TFET, desired Id~Vg curve of TFET is shown.

Use of tiny bandgap material is the simplest technique to improve TFET performance. Devices employing silicon germanium alloy or pure germanium as the source material have clearly reduced SS and increased driving current. It is essential to build an abrupt junction in order to strengthen the electrical field.

Unfortunately, there hasn't been much success so far in creating acute junctions in FET structures. Ion implantation dopant atoms' high energy tail is difficult to remove, and the high temperature annealing process that follows to repair implantation damage can quickly result in a widened doping profile that prevents the creation of abrupt junctions. Additionally, source to drain junction leakage current affects a TFET's SS and off-state current negatively. There are numerous techniques to prevent leakage current between the source and drain, such as using a thin channel body (10nm), a gate-all-around construction (nanowire), and a high K dielectric to maximise gate to channel coupling.

Due to the similarities in their fundamental architectures, the tunnel field-effect transistor (TFET) has emerged as one of the viable alternatives to MOSFET. The band-to-band tunnelling process underlies TFET operation, which is clearly distinct from MOSFET operation.

TFETs are a fantastic choice for low-power applications like memory devices since they can produce subthreshold swings (SS) lower than 60 mV/decade. Additionally, TFETs only rely on the band overlapping required for band-to-band tunnelling because MOSFETs have the thermionic emission threshold for channel construction. High ION/IOF F can be achieved with TFETs. TFETs can dissipate relatively little dynamic power since they have low supply voltage requirements and low threshold voltages.

To improve TFET performance, many researchers tried to structure engineer them. To enhance the ION, some researchers have experimented with lower bandgap materials. However, this could cause the IOF F current to increase significantly, which would result in more static power dissipation. Other research attempted to model TFETs to boost ION while maintaining a low IOF F, but at the same time the complexity of the process rose. The ON current was increased by a few researchers that attempted to engineer the channel from conventional to L-channel to U-channel by enabling both line and point tunnelling to enter the picture.

TCAD simulations of TFETs, like the one in this thesis, are significant in a number of ways. In order to better understand the device physics and the tunnelling likelihood inside the device, we have presented the Electric eld vector distributions. Using 1D or 2D cross-sections, it aids in our ability to look through the apparatus. We have taken steps toward optimising the device settings at various drain heights through simulations.

In this thesis, we present a simulation-based, definitive TFET structure engineering that will aid in the creation of future models and a deeper comprehension of the device.

The central issue with TFET is to make the gated tunneling process more efficient with various leakage path successfully suppressed. As seen in equation, tunneling probability is highly sensitive to three variables in the exponential term: bandgap energy, reduced effective mass and the electrical field within tunnel barrier. Efficient tunnel process favors low tunnel barrier height, which is determined by the bandgap energy, short tunnel width, which normally translates to high electrical field within an abrupt pn junction. The reduced effective mass is mainly material dependent and very sensitive to bandstructure modification by quantum confinement, strain effect, etc.

The most straightforward way to boost the TFET performance is to adopt small bandgap material. Devices with replacement of the source material by silicon germanium alloy or pure gemanium have shown obvious reduction of SS and increase of the drive current. To increase the electrical field strength it is critical to fabricate abrupt junction.

Unfortunately so far little success has been made in producing sharp junction in a FET structure. It is hard to eliminate the high energy tail of ion implantation dopant atoms, and subsequent high temperature annealing process to repair implantation damage can easily result in broadened doping profile preventing formation of abrupt junction. Furthermore, source to drain junction leakage current has negative effect on off-state current and SS of a TFET. Suppression of leakage current between source and drain can be done in many ways, for example, thin channel body (<10nm), gate-all-around structure (nanowire), in combination with high K dielectric to increase gate to channel coupling.

#### Motivation

TFETs can achieve subthreshold swings (SS) lower than 60 mV/decade, which enables TFET to be a great candidate for low-power applications like memory devices. Also, TFETs does not possess the thermionic emission threshold present in MOSFETs for its channel formation and solely rely on the band overlapping which is necessary for the band-to-band tunneling. With TFETs, very high  $I_{ON}$  / $I_{OF}$   $_{F}$  is achieve-able. Having low threshold voltages and low supply voltage requirements, TFETs are able to dissipate very low dynamic power.

The major pitfalls of TFETs are its low ON current and its am-bipolar current nature, which we have tried to improve through structural engineering.

#### **Current Scenario**

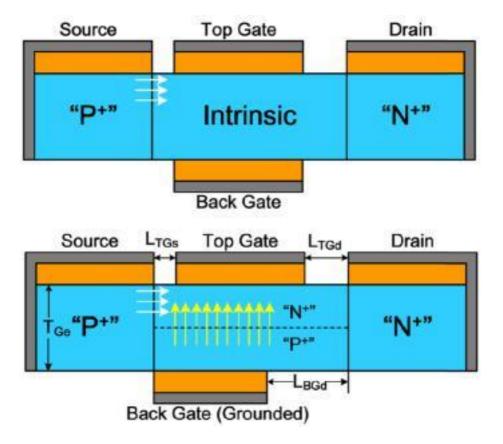

Many researchers tried to structure engineer TFETs for better performance . Some of the researchers have tried using lower bandgap materials to improve the  $I_{ON}$  . However, with this the  $I_{OFF}$  current could rise significantly thereby leading to higher static power dissipation. Other studies tried to model TFETs to improve  $I_{ON}$  by keeping  $I_{OFF}$  low but the process complexity increased simultaneously. Few of the researchers tried to engineer the channel from conventional to L-channel to U-channel allowing both line and point tunneling to come into the picture thereby increasing the ON current.

#### 1.4 Objective

TCAD simulations of TFETs such as the one presented in this thesis are important in various ways. We have presented the Electric eld vector distributions which help up better understand the device physics along with the tunneling probability inside the device. It helps us to see through the device using 1D or 2D cross-sections.

Through simulations we have approached towards the optimization of the device parameters for various drain height. In this thesis, we have given a simulation based conclusive TFET structure engineering that will help in the future model development and understanding the device better.

#### **Thesis Organization**

This Thesis is oriented as follows:

**Chapter 1:** Gives an overview of the basic topics related to this thesis and explanation of certain keywords mentioned in the abstract.

**Chapter 2:** Provides an extensive overview of the small geometry devices and their journey of evolution beginning from long channel MOSFETs to recent short channel devices. Several consequences arising due to such device dimension miniaturization.

**Chapter 3:** This chapter is about Basics of TFET,MOSFETs vs TFETs,Working principle of TFET,Working Principle of MOSFETs vs TFET, Tunneling Mechanism, Line tunneling and Point tunnelling etc.

**Chapter 4:** The method of simulation used in this project is explained in this particular chapter. As Silvaco Atlas TCAD has been used for simulations, most of its syntax has been discussed

**Chapter 5:** Describes the structure of the proposed TFET and its operation. It includes the device physics part to explain the working of TFETs with the band to band tunneling phenomenon between the source and channel. Also, the two types of tunneling mechanisms are illustrated in the proposed structure. It also includes I-V, C-V characteristics, energy band diagrams, electric field plots etc

**Chapter 6:** Describes the discussion of the Analog parameter characteristics for the proposed structure characteristics along with  $g_m$ ,  $f_T$  and Gain bandwidth product for the proposed structure.

**Chapter 7:** Provides a summary of the work done and the future scope for newer research areas for this proposed structure.

#### Chapter 2

#### **Literature Review**

The last few decades have witnessed a phenomenal growth in the microelectronics industry being obsessed by the continuous shrinking of device dimension to increase the device integration density with subsequent reduction in manufacturing cost. The future of VLSI as predicted by Moore since 1965 with proportional device downscaling also portrays its progress through high operating speed VLSI circuits and minimum power consumption. However, aggressive downscaling of conventional MOS technology suffers the limitations of complex fabrication techniques and the associated cost. Moreover, ultra nano-scaled device physics also require lucid concept of quantum mechanical laws. Such small scaled devices when integrated on a single chip may loss its functional competency and degrade the overall circuit operation. These challenges are driving the researcher community to investigate non-conventional MOS structures that can circumvent the scaling limitations and allow further miniaturization without compromising the device performance. While some of these devices employ the principle of quantum mechanical phenomena and are referred as revolutionary nanoelectronic devices (quantum well, quantum wire, quantum dot based devices e.g. HEMT, Spintronics, SET, etc.), the other group of scaled devices with geometrical modifications and improvisation in material properties in existing technology fall under the category of evolutionary nano-devices (e.g. Carbon Nanotube FETs, heterojunction based FETs, Nanowire FETs, Ge channel devices, strained channel FETs, structurally refined FETs, etc.). Incessant research exploration in pursuit of such non-conventional devices can satisfy Moore's scaling trend and realize superior functionality by suppressing inevitable short channel effects in terms of drain induced barrier lowering, threshold voltage roll off, hot carrier effect, to mention a few [72]. The architecture, operating principles, analytical modeling approaches of such devices are quite different from conventional ones and have been focused in the present thesis highlighting the available options of further scaling and proper device optimization.

#### Overview on Metal Oxide Semiconductor Field Effect Transistor (MOSFET)

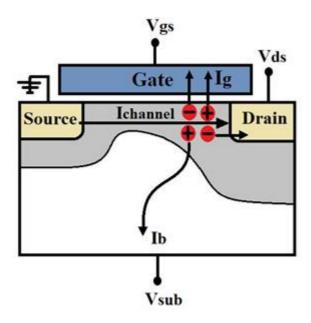

The Metal Oxide Semiconductor Field Effect Transistor (MOSFET) has earned commendable popularity since 1970s owing to its simple architecture, reduced fabrication cost, minimized power consumption, inherent high input impedance, momentous speed of operation and improved noise immunity. Superior scalability of MOSFET device for incremented transistor count/chip as predicted by Moore's law has marked the evolution of semiconductor industry from the era of sub-micron to present sub-nano regime. The fundamental principle of MOSFET was proposed by Julius Edgar Lilienfeld in the year 1925 which performs the basic operations of amplification and switching of electronic signals. The name MOSFET itself gives a clue to the MOS capacitor based working principle of the device with the dielectric layer of silicon dioxide (SiO2) being sandwiched between the metal gate electrode and bulk silicon substrate that act as terminals/plates of capacitor. The schematic of basic MOSFET structure is illustrated in figure 2.2.1. It consists of four terminals depicted as heavily doped source and drain, metal gate and lightly doped silicon body. Depending upon the type of dopants of source and drain regions that determine the type of channel formed, MOSFET can be categorized as p-channel and

Figure. - Basic MOSFET structure.

n-channel variants. p-type substrate and heavily doped source/drain with

n+ impurities realize n-channel MOSFET where electrons act as majority carriers in the induced channel. Similarly, for p-type MOSFET, holes act as the majority carriers within the induced p-channel where n-type substrate and p+ source/drain form the basic structure. The conducting channel is actually a layer of inversion charge formed at the interface of oxide-semiconductor and bears the flow of carriers from the source towards the drain region on application of suitable drain bias. An n-channel MOSFET with heavily doped n+ source and drain regions being diffused or ion-implanted into the lightly doped silicon substrate is presented in figure. A dielectric layer of silicon dioxide is grown over the silicon body between the source and drain regions followed by metal gate deposition to dielectrically insulate the gate electrode from the device. This isolation ensures high input impedance of MOSFET in order of Mega ohms or approximately infinite preventing flow of carriers from the gate to the device itself. MOSFET is also termed as the gate controlled resistor where the induced channel and its conductivity depend upon the gate potential and its variation respectively. The device is symmetrical with respect to source and drain which being doped with same dopants can be interchanged easily depending upon the direction of current flow within the device as per the external applied bias. However, the high input impedance of the device induces considerable static charges that may hamper the functionality of MOSFET unless taken care of or handled cautiously.

**Figure.** - Schematic representation of n-channel MOSFET.

#### **Types of MOSFET**

Depending upon the process of channel formation in MOSFET, it can operate either in Depletion mode or Enhancement mode.

#### **Depletion mode MOSFET**

The existence of preformed channel between the source and drain regions under zero bias condition of depletion mode MOSFET distinguishes it from broadly used enhancement mode equivalent. It acts as 'normally switched on' device and a suitable gate voltage is required to switch the device to OFF state condition. Unlike enhancement type MOSFET, the channel of depletion mode MOSFET is diffused with same type of dopants used for source/drain diffusion regions. Considering n-channel depletion type MOSFET, application of negative gate voltage makes the channel depleted of charge carriers thus reducing the drain current while positive gate voltage increases the number of charge carriers that contribute to incremented drain current of the device. The schematic diagram and current voltage characteristics of n-channel depletion mode MOSFET are represented in the below figure.

**Figure** - Representation of n-channel depletion mode MOSFET and its current-voltage characteristics.

The opposite behavior is exhibited by p-channel depletion mode MOSFET. This type of device bears close resemblance to JFET with low resistance channel extending between source and drain and pre-doped with electrons and holes for n-channel and p-channel device respectively. However, the conductivity of depletion type MOSFET is much less relative to enhancement mode counterpart. It can be operated as enhancement mode MOSFET also although vice versa is not applicable.

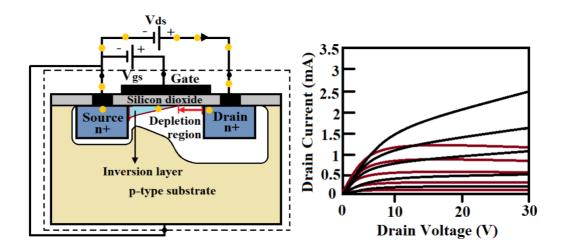

#### **Enhancement mode MOSFET**

The distinct feature of Enhancement mode MOSFET is its undoped or very lightly doped channel region that remains non-conductive under zero bias gate condition. For n-channel enhancement type MOSFET as depicted in figure 2.2.4 (a), applying positive gate voltage generates a vertical electric field from the gate towards the channel that attracts the minority electrons of the p-type substrate at the semiconductor/oxide interface and pushes the holes within the body. This increases the thickness of the channel and reduces its resistivity to enhance the drain current conduction. The voltage at which the channel is fully inverted is referred as the threshold voltage Vth while subthreshold condition exists for range of voltage before inversion condition is achieved as presented

**Figure.** - Representation of (a) basic n-channel Enhancement mode MOSFET structure and (b) its Id-Vgs characteristics

**Figure-** Representation of (c) Current-Voltage characteristics of n-channel Enhancement mode MOSFET.

Figure. - (b). As the gate bias crosses the threshold voltage, electron rich n-type channel under inversion condition prevails facilitating a continuous flow of device current from drain to source once a suitable positive drain bias is applied.

Thus, it can be inferred that for n-channel enhancement MOSFET as positive gate voltage increases, the channel resistivity is lowered resulting effective enhancement in channel current thereby justifying the name Enhancement mode MOSFET. The device acts as 'Normally open' switch with zero/negative gate voltage while it turns 'ON' under positive gate bias condition. The low resistivity of the device in 'ON' state condition and high 'OFF' state resistance with extremely high gate resistance also make it suitable for applications in power switching circuits and as CMOS logic gates. The Id versus Vds characteristics of n-channel enhancement mode MOSFET is shown in figure. (c).

#### **Operational regions of MOSFET**

The principle operation of MOSFET can be explained by the theory of MOS capacitor. Considering n-channel Enhancement MOSFET, a positive gate voltage will induce positive charges being accumulated at gate surface acting as one plate while corresponding negative charges are induced in the opposite plate of p-type substrate at oxide/semiconductor interface. The negative charges are due to the minority carriers (electrons) and are dependent on the gate bias. Hence, with increase in gate voltage, more number of minority carriers are attracted thereby decreasing the hole density below the gate region.

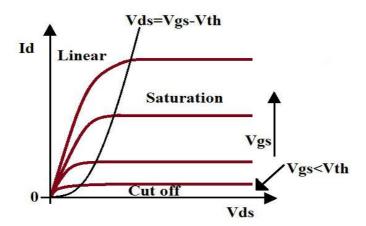

The condition of 'channel inversion' is achieved on further increase in gate bias where presence of large number of free electron carriers decreases the effective channel resistance and contribute to device current with appropriate drain bias. The MOSFET operational regions depending upon the applied gate voltage are enlisted below and also illustrated in figure.

- **a. Cut-off region**: When the applied gate to source voltage (Vgs) is less than the specified device threshold value, MOSFET exhibits no current conduction and acts as 'open circuit'. This region is referred as cut off region of MOSFET and the same is depicted in figure.

- **b.** Linear or ohmic region: When the applied gate bias (Vgs) is greater than the threshold value provided the drain to source voltage (Vds) is more than Vgs, the drain current increases linearly with Vds through the

**Figure. -** Illustration of different regions of operation in drain current characteristics of MOSFET.

Device and it acts like voltage controlled resistor whose value in turn is dependent on Vgs. This mode of operation is linear or ohmic region and is utilized for MOSFET signal amplification.

**Saturation region:** Keeping the gate to source voltage well above the threshold value, as the drain bias reaches the saturation voltage, i.e. Vds=Vgs-Vth, the drain current reaches its maximum value acquiring constant current region. The transistor under this region switches to 'fully ON' state and acts as closed circuit. This region is referred to as saturation region finding application in digital switching circuits.

#### **Analytical model description of MOSFET**

As already described in the principle of MOSFET conduction mechanism is based on the condition of channel inversion induced by applying suitable bias on the gate electrode of the device. It generates a vertical electric field underneath the gate terminal and modulates the flow of carriers from the source to drain through the conducting channel. Here, proper gate bias (Vgs) refers to the gate to source voltage at which the semiconductor channel is inverted to maintain the subsequent conduction and is termed as the threshold voltage (Vth). When applied Vgs is not sufficient to achieve the inversion region, i.e. Vgs < Vth, the absence of conducting channel prevents the current flow through the device until the gate bias exceeds Vth. Once the applied Vgs is chosen to be higher than the device threshold value, a large number of minority carriers (electrons in case of n-channel MOSFET) get attracted owing to the induced

vertical field towards the interface of oxide/semiconductor and an inverted channel is formed supporting an effective device current flow.

The four physical components of threshold voltage of MOSFET as identified for almost all practical purposes comprises of :

i) The workfunction difference ( $_{gc}$ ) between the gate electrode and semiconductor channel

Depending on the material of the gate terminal, the workfunction difference is given by:

$$gc_f$$

(substrate)  $_m$  (metal gate)...... (1)

$$gc_f$$

(substrate)<sub>f</sub>(polysilicon gate)..... (2)

ii) The gate terminal voltage component required to adjust the surface potential (f)

$_f$  presents the component of externally gate voltage required to achieve surface inversion by altering the surface potential by  $2_f$ .

#### Advantages of MOSFET and its suitable applications

Incessant research in the domain of semiconductor industries have already brought several ground breaking techniques for feasible fabrication of scaled MOSFET devices with drastically improved performance. The extreme low power consumption, momentous speed of operation, small area requirement of MOSFETs with higher integration density and low cost make it a potential choice for complex high performance IC designs. MOSFET acts as suitable electronic switch or commonsource amplifier for its low power consumption and as ideal buffer amplifier for its high input impedance. Its ability to capture weak signal for its excellent noise immunity and also its elevated scalability with increased package density as compared to BJT make it a sole choice for future applications. However, one vital limitation of MOSFET is the poor frequency response with respect to BJT owing to the presence of numerous parasitic capacitances.

#### **Power consumption in MOSFETS**

For an inverter, the dynamic power consumed can be given as:

$$P_{DYN} = f_{CLK} C_L V_{DD}^2$$

We can see that the dynamic power has square dependence on  $V_{DD}$ . Hence if we for example, say scale down  $V_{DD}$  by 2, the dynamic power of the inverter will come down 4 times. The constant here is the activity factor of the particular node, which is defined as the probability of a particular node switching.  $f_{CLK}$  is the frequency of the clock signal applied.  $C_L$  is the load capacitance (contribution of all parasitic capacitance of the inverter).

The static/steady state power dissipated in the inverter is given as:

$I_{\text{LEAK}}$  denotes the leakage current through the transistors when they are in Off State.

The power consumption of an operating MOSFET can be categorized into two types: Active Power consumption and Dynamic Power consumption.

#### **Static Power Consumption**

The existence of leakage current in a device due to the presence of certain parasitic components is mainly responsible for the static power consumption. The parasitic components refer to the gate to source leakage, gate to drain leakage, direct drain to source leakage and drain to bulk leakage that contribute to the overall leakage current  $(I_l)$  of the device. Thus, the static power consumption can be expressed by:

Total Power = Dynamic Power + Static Power

Dynamic Power =  $A * C * V_{dd} 2 * f$

Static Power = V \* I<sub>leak</sub>

$I_{\text{leak}}$  = Leakage current from sub-threshold, gate oxide leakage and reverse biased diodes

A = Fraction of gates actively switching (switching activity passed to power tools as SAIF file)

C = Total capacitive load of all gates

Vdd = Supply voltage

f = Frequency of operation

$P_{st}$   $I_lV_{dd}$   $(I_{d,l}I_{g,l})V_{dd}$  with  $V_{dd}$  denoting the supply voltage.

The chief source of leakage current ( $I_{g,l}$ ) is the tunneling of carriers through the gate dielectric of MOSFET and its intensity is determined by the thickness of the dielectric and the barrier height. Although, conventional silicon dioxide is preferred in MOSFET devices for ease of fabrication, however, to keep in pace with the aggressive scaling demands, the proportionate downsizing of the oxide thickness has resulted higher tunneling possibility of carriers through the dielectric thereby increasing the leakage current. An effective solution to this problem as proposed in contemporary research reports is the application of high-k gate stack in MOSFET that will achieve the same range of oxide capacitance using thicker layer of oxide and will consequently prevent the tunneling of carriers through the gate oxide.

On the other side, the leakage across the drain side (  $I_{d,l}$  ) has mainly three following components:

- a. leakage from the drain region to bulk which is referred as gate induced drain leakage

- b. leakage due to transfer of carriers from source to drain directly

- c. leakage under subthreshold condition between source and drain regions

Thus,  $I_{d,l}$  can be represented as:  $I_{d,l}I_{direct,t}I_{GIDL}I_{sub,th}$

#### **Dynamic Power Consumption:**

This sort of power consumption is mainly attributed to the switching action of the MOSFET. Applying proper gate bias switches the device to ON state condition, while some built up charges in the channel region are transported to the source/drain contacts and across the gate terminal. As the device is turned OFF on removal of supply voltage, these charges are required to be emptied from the device. However, this phenomenon is irreversible in nature resulting dissipation of power.

Considering f as the switching frequency, the dynamic power consumption is expressed as :  $P_{dy} f C_{ox} V_{dd}^2$ . Here,  $C_{ox}$  is the gate capacitance which stores the energy for charging and discharging the device while switching.

#### **Total Power dissipation**

Pdp+Pdn =

$$(C_L/tp) (V_{DD})^2$$

=  $C_L f. (V_{DD})^2$

Taking node activity factor α into consideration:

The power dissipation=  $\alpha C_{L}$  f.  $(V_{DD})^2$

#### **MOSFET** scaling and its consequences:

The progressive advancements in modern digital world and computational speed are driven by the advent of Integrated Circuits introduced by Jack Kilbey at Bell Labs. This momentous growth is further sustained by uninterrupted device scaling or miniaturization following the exponential trend of Moore's law. The incessant improvisation in scaling techniques accompanied by increased device density on a single chip have resulted boosted computing capability and high performance systems at affordable price. As per the scaling rule of MOSFET published by Dennard, the scaling parameter  $\alpha$  is used along with a multiplying factor of  $1/\alpha$ . While the doping concentrations are scaled by the factor  $\alpha$ , the voltages are multiplied by  $1/\alpha$  to maintain the internal electric field unaffected.

**Figure.** - (a) Scaling rule; (b) Scaling trend of supply voltage.

Again the speed of the circuit gets boosted by the factor  $\alpha$  with consequent lowering of power dissipation by  $\alpha 2$ . The scaling law is depicted in figure (a). The technology trend with scaling as illustrated in figure (b) shows that threshold voltage reduction does not follow the Dennard's Rule because of the gate overdrive. To keep pace with scaling trend, device feature size is scaled every year and the number of transistors on chip gets doubled every two years as predicted by Moore's law.

This is reflected in the evolution of nanotechnology and nano-electronics from microregime as transistor feature size is scaled from micrometer to 100nm orders. The success of the IC industry is credited by the reduction in feature size without compromising the scaled device performance.

Figure. - Moore's law

International Technology Roadmap for Semiconductor (ITRS) has defined the trend of device miniaturization with future technology nodes. In figure, MOSFET scaling trend indicates the fact that with transition to each technology node, MOSFET feature size is gradually decreasing which in turn increases the integration density and its associated cost by half every two years. The major hindrance to this high package density is the increased power consumption which is now being aimed to be suppressed by adopting some ingenious techniques. Supply voltage scaling is one of the viable options to reduce the dynamic power consumption. The bias voltage has been scaled from 1.2V to 1V abiding scaling rules as per the scaling trend of 2005 to 2011. Hence, the threshold voltage is to be scaled down also to a range of 0.5V-0.6V to maintain high driving capability of the device. However, due to transistor control reasons,

This voltage cannot be scaled below 0.45V till the end of the road-map. Although a series of benefits including high integration density ICs, improved speed of operation, high complexity at reduced cost have fomented the non-stop scaling trend, there is obviously some high price that needs to be paid off to reap such radical advantages. It has been found that the normal device performance is affected by daunting short channel effects (SCEs) which degrade the efficiency of the device as its feature size is gradually reduced. This performance deterring phenomenon can be explained by the lose of electrostatic gate control over the channel due to charge sharing phenomenon between source and drain of short channel device [93-94]. Due to this reduced gate control, the device threshold voltage characteristics and subthreshold slope becomes function of channel length. Some adverse SCEs can be summarized as threshold voltage degradation, hot carrier effect, drain induced barrier lowering, random dopant fluctuation etc. Apart from such limitations, reduction in feature size also impinges the need for much higher resolution of photo-lithography, excellent process control, enhanced reliability, thinning of gate oxide layer, interconnect formation that complicates the actual fabrication of such miniaturized devices. In addition to such practical challenges, design, testing and packing of ICs containing billions of transistors pose a high alarm to the microelectronics industry.

Hence, refinement in IC technology with expensive revolutionary techniques is to be allowed in such a way that significant performance improvement can be achieved with a feasible computing hardware practically. CMOS based circuits have earned polarity due to the low power consumption of CMOS technology suitable for portable consumer applications where battery life is the major concern. Such low power

dissipation is also desirable in highly complicated circuits where however, it is very difficult to maintain the normal room temperature operating condition. With rise in temperature, the silicon becomes intrinsic in nature and the free carrier concentration within the conduction band gets dependent on the thermally generated carriers leading to device breakdown. Thus, heat sink techniques are applied which however are not fully capable to dissipate the waste heat. Hence CMOS based circuits need proper thermal management to control the power dissipation efficiently.

Thus, it can be inferred that with continuous scaling of device feature size, several complexities hamper the overall performance as well as the intrinsic properties of the device. Such affects are vulnerable in nature and cumulatively referred as short channel effects. The detrimental SCEs are discussed in detail in the following section.

#### **Short Channel Effects:**

As the dimension of the effective length of the MOSFET channel becomes comparable to its source and drain junction depths, it is referred to as the short channel MOSFET. As the long channel MOSFET approaches the short channel dimension with gradual downscaling of the channel, several vulnerable effects crop up which in turn deteriorate the performance of the scaled device. Such adverse effects are collectively termed as 'short channel effects (SCEs)' which again can be categorized as described below depending on their physical origin.

#### (a) 2D Electric field profile:

Unlike long channel MOSFET, where the current flow between the source and the drain through the conducting channel is reliant only on the vertical electric field; in short channel MOSFET, both the vertical and horizontal electric fields existing within the channel control the device current. This in turn limits the application of 1D Gradual Channel Approximation (GCA) concept to account for some of the device characteristics as evident in nano-scale regime. The significance of such two dimensional electric field distribution is elaborately described below.

#### (1) Drain Induced Barrier lowering (DIBL):

The effect of drain induced barrier lowering (DIBL) common in short channel MOSFET devices is manifested by threshold voltage degradation /roll off which reveals a sharp decay in threshold voltage value as function of drain to source voltage with reduction in device channel length. The close proximity of the source and drain regions in short channel MOSFET makes the source and drain depletion regions to approach each other with consequent increase in horizontal electric field which otherwise could be ignored in GCA approach. Under such situation, the total charge within the channel is governed by both the gate to source voltage and applied drain bias and such condition is termed as '2D charge sharing'.

With gradual decrease in channel length, the horizontal electric field increases and eventually the gate loses control over the device channel charge which is finally being governed by the gate and drain voltages. Hence, under such circumstances, a small gate voltage is now required to attain the condition of inversion indicating a roll off in device threshold voltage with continuous scaling of channel length.

The concept of threshold voltage degradation can be further explained by the alternate prospective of surface potential barrier within the channel between the source and the drain. When the applied gate to source bias is less than the threshold voltage of long channel MOSFET device, surface inversion is not achieved and the potential barrier is high enough to prevent the flow of carriers from source to drain region in the absence of inverted channel. When suitable gate voltage is applied to reach the condition of inversion, the potential barrier gets lowered allowing the thermionic emission of carriers from source towards the channel driven by the electric field. Thus, it can be inferred that the applied gate bias solely controls the potential barrier height in case of long channel MOSFETs which however follows a complex nature in case of short channel MOSFET where both the gate and drain biases modulate the barrier height. Thus, under such circumstance, even if the gate voltage is lower than the threshold voltage, the applied drain bias tends to lower the potential barrier facilitating the flow of carriers from source to the drain region thus resulting an undesired subthreshold current conduction. Such phenomenon of barrier lowering due to applied drain bias leading to current flow in subthreshold state is termed as drain induced barrier lowering and is recognized as one of the detrimental short channel effects as shown in figure.

As the drain bias increases, the depletion region across the drain encroaches into the channel gradually leading to the lowering of potential barrier height;

**Figure.** - Surface potential variation along lateral position.

Thereby attaining subthreshold conduction at lower value of gate voltage. DIBL is usually measured as the difference of threshold voltage between a low and a high drain bias. Thus, a device with high value of calculated DIBL exhibits high threshold voltage decay and increased OFF state leakage conduction.

#### (2) Effect of gate induced electric field on carrier mobility:

With the progressive reduction in transistor channel length, the thickness of the gate oxide is also downscaled proportionately in addition to other physical dimensions of the device. With gradual scaling of gate oxide thickness, the vertical electric field intensity as directed from the gate electrode increases towards the channel making the transverse electric field dominant. This in turn pushes the electrons towards the oxide-substrate interface which suffers collision and gets scattered rapidly degrading the mobility of the electrons in silicon crystal. As the electrons move along the channel being very close to the interface, a small increase in transverse electric field will eventually lower the surface mobility to almost half of the bulk mobility.

#### (b) High electric field strength within the channel

With the shortening of channel length, a notable increase in the electric field is observed as the voltage source are not scaled proportionately. Hence, a series of vulnerable effects are observed in such short channel devices due to this uncontrolled rise in electric field which may ultimately cause device breakdown.

Saturated carrier velocity: One of the significant consequences of high channel electric field is the saturated carrier velocity. At lower values of electric field, the carrier velocity exhibits a linear dependency on channel electric field. However, as the channel length is gradually scaled, the electric field within the channel increases and as it reaches a critical value, the carrier velocity gets saturated. The linear relation of carrier velocity with electric field thus no longer exists at such high electric field due to increased scattering of such highly energized carriers which now takes longer transit time to flow through the channel. Drift velocities of both electrons and holes get saturated at above 100kV/cm of applied electric field while for short channel devices, the drain side electric field attains value as high as 400kV/cm.

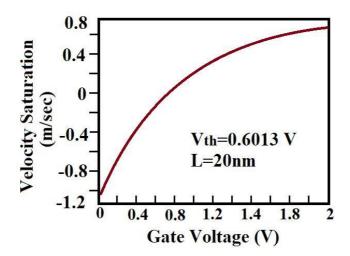

Figure - Saturation in carrier velocity with incremented gate voltage

**Impact on ionization:** The electric field induced impact ionization at the drain end is another adverse SCE due to the application of sufficiently high electric field in a short channel MOSFET. With channel length reduction, the electric field increases considerably at the drain side and initiates the impact ionization phenomenon. The carriers while moving from the source towards the drain under the influence of high electric field gain sufficient kinetic energy to knock an electron from its bound state in valence band and promote it to a free state in the conduction band thus generating an electron-hole pair as depicted in figure.

Figure. - Generation of electron-hole pairs due to electric field induced impact ionization

Electrons generated in such way regain more kinetic energy from the high channel electric field and create more electron-hole pairs cumulatively. The generated electrons from electron-hole pairs get accelerated towards the positively biased drain side while holes migrate to the substrate resulting parasitic substrate current. The accumulation of holes in the substrate creates a voltage drop which may be sufficient to forward bias the normally reverse biased source/substrate junction. When it exceeds the junction built-in potential value, the junction becomes forward biased injecting several electrons from the source to the channel thereby increasing the current. The electrons thus newly injected; again come under the influence of existing high electric field at the drain side and gain sufficient kinetic energy to initiate the electron-hole pair generation. Thus, this high electric field induced impact ionization is referred as a cumulative process and acts as a major performance deterrent factor for short channel devices.

## Parasitic bipolar effect:

This parasitic bipolar effect is an after effect of impact ionization where excess electron hole pairs are generated repeatedly at the drain end under the influence of high electric field. While the electrons get swept towards the drain side of nMOS, the generated holes are accumulated within the p-substrate. The injected holes build a net positive charge in the substrate with respect to the grounded source which in turn forward biases the otherwise reverse biased source/substrate junction. Thus, a parasitic transistor is created with n-type source, p-type substrate and n-type drain giving rise to the parasitic bipolar

effect. Such forward bias of the substrate/source junction encourages further injection of electrons from n-type source to the p-type substrate below the inverted channel of nMOS transistor. These newly injected electrons when reaches the vicinity of high electric field at the drain side again participate in impact ionization resulting avalanche multiplication of carriers. The positive feedback of parasitic bipolar effect to impact ionization threatens the device reliability even at low drain bias

## **Hot carrier effect (HCE):**

The term 'hot electron' is first used by Conwell [99] to describe the behavior of electrons under non equilibrium condition in semiconductor crystal. Incessant trend of device miniaturization tends to raise the intensity of horizontal electric field between the source and drain and may be sufficient enough to heat the carriers across the drain end. Such electrons are termed as 'hot electrons' which gain sufficient kinetic energy at the expense of potential energy and overcome the potential barrier between the channel and the gate oxide. Existence of high electric field across the drain end of short channel MOSFETs enables these hot electrons to penetrate into the gate oxide resulting the gate current which in turn reduces the input impedance of the device. Some of the injected hot electrons also get trapped within the gate dielectric as fixed oxide charges and deteriorate the channel/oxide interface states. These hot carriers have severe adverse effect on device performance resulting device heating, degraded subthreshold slope, reduced transconductance and high leakage current

## **Gate oxide charging:**

It can be well understood from the previous discussion that continuous scaling of device channel length increases the horizontal as well as vertical electric field within the channel region and at times becomes high enough to heat the carriers and generate hot electrons. Such hot carriers acquire high kinetic energyand surmount the potential barrier existing across the oxide-channel interface and penetrate the gate dielectric. These build-up charges eventually degrade the quality of the oxide layer and the prolonged transport of carriers into the oxide ultimately causes the electrical breakdown of the oxide. This long term degradation phenomenon is called time dependent destructive breakdown (TDDB) or hot electron ageing. To combat such alarming issue, conventional silicon dioxide gate dielectric is being replaced by high-k gate oxides like HfO2, Al2O3, TiO, ZrO with higher relative permittivity. Application of such high-k dielectrics aids realization of same

gate capacitance with thicker gate oxides, thereby lowering the probability of such breakdown issues and hence the device reliability threat associated with scaled gate oxides.

Some of the SCEs encountered due to the decrease in physical distance between the source and drain of short channel MOSFET are summarized below:

**Channel length modulation:** The channel length modulation (CLM) arises from the shortening of the effective channel length of short channel MOS affecting the drain current characteristics of the device

**Figure**. - MOSFET structure showing channel length modulation and its effect on drain current characteristics of the device.

As the drain bias is increased, the depletion width at the drain end intrudes into the channel leading to the reduction in effective device channel length which now becomes equal to the actual channel length minus the depletion region width of the source and drain region.

The effect of this channel length modulation is clearly evident in output characteristics of short channel MOSFET as shown in figure. where the current increases beyond saturation exhibiting a finite non-zero slope. The CLM effect is more pronounced in short channel device with low doped substrate than in long channel devices.

## Punch through:

Punch through is considered as the ultimate consequence of channel length modulation. In short channel devices, continuous increase in drain bias widens the reverse biased drain-substrate depletion region which gradually approaches the source depletion region and merges at a certain drain bias. The effective channel length thus becomes zero and such phenomenon is termed as punch through.

The channel current under this condition increases rapidly with increase in drain bias raising the output conductance and consequently limiting the maximum operating voltage of the device.

Apart from the adverse SCEs discussed so far, some other challenging issues like source-drain resistance, gate leakage current, random dopant fluctuation and complicated fabrication techniques, affect the overall function of scaled devices.

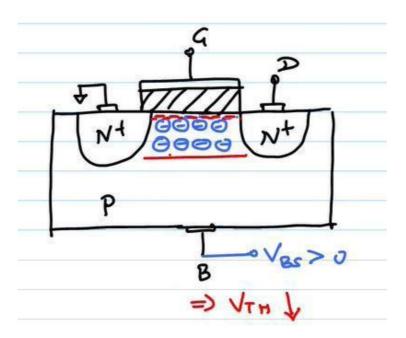

## **Body Effect**

The effect of body effect for short channel transistors is shown in below Figure

**Figure.** - Body Effect in short channel devices

The body bias  $(V_{BS}>0)$  acts as a back gate for the transistor and helps in channel formation even before the gate voltage is applied. So now  $V_{GS}$  has to now less work to invert the channel. Hence the  $V_T$  decreases with body bias ( $V_{BS}>0$  for n-channel MOSFET).

## **Channel Length Modulation:**

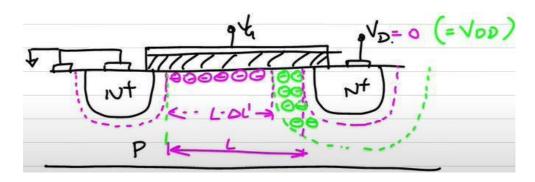

With decrease in the size of the transistor channel length also decreases creating a room for another type of short channel effect known as channel length modulation. This is depicted in Figure

Figure. - Channel Length Modulation in short channel devices

It is evident from above that when we apply a drain potential,  $V_{DS}$ , the depletion region in the N+ region eats into the channel and depletes the channel to some extent, therefore now  $V_{GS}$  has to do less work to invert the channel. So again in this case,  $V_T$  decreases. Since this phenomenon is e ective when  $V_{DS}$  is large, hence it can be seen in saturation region. The current equation for MOSFET in saturation was given as:

$$I_{DS} = \frac{1}{2n} C_{ox} \frac{W}{L} (V_{GS} - V_T)^2$$

Now the new drain current equation becomes

$$I_{DS} = \frac{1}{2n} C_{ox} \frac{W}{L} (V_{GS} - V_T)^2 (1 + V_{DS})$$

where is the CLM parameter whose units are in V<sup>1</sup>

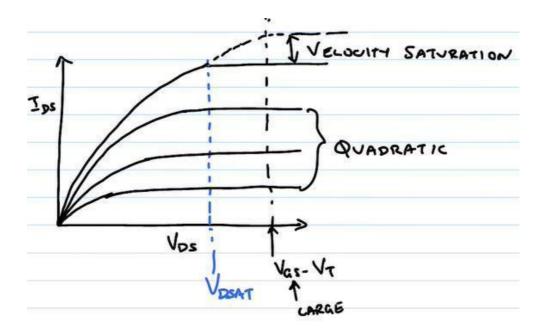

## **Velocity Saturation**

Velocity saturation is the phenomenon where due to supply voltages being dropped for downsizing of transistors, so as to avoid breakdown of the device operation; the velocity tends to saturate for a particular  $V_{ds}$  value. This saturation of  $V_{ds}$  makes the device operation to go into saturation well before the long channel device with same parameters could go into saturation. This is depicted in the Figure below:

**Figure.** - Variation of output characteristics due to Velocity Saturation in short channel devices

## Subthreshold Slope and Avg. Subthreshold Slope

The subthreshold swing is de ned by  $S=\left(dlogI_D/dV_{GS}\right)^{-1}$  in units of mV/decade, and in the MOSFET, it is independent of  $V_{GS}$  below the threshold voltage. For the TFET, the tunnel current can be described.

Several ways to de ne subthreshold swing have been proposed for the TFET. The most often used method, as illustrated by the reports summarized is to give the tangential inverse slope of the  $I_D$ - $V_{GS}$  curve at the steepest part of the characteristic. Bhuwalka and Boucart and Ionescu have proposed an equation, which will provide an average swing

$$S = \frac{V_{TH} - V_{OFF}}{log(\frac{I_{TH}}{I_{OFF}})}$$

where  $V_{T\,H}$  is the threshold and  $V_{OF\,F}$  is the voltage below threshold at which the OFF current,  $I_{OF\,F}$  is a minimum. Here, the problem is to de ne the threshold voltage and for this constant current method can be applied. For example, as in the MOSFET, the threshold current can be de ned as  $I_{T\,H}=10^{-7}=L_G$  ampere, where the gate length  $L_G$  is given in nanometers.

A new definition for the TFET threshold voltage, proposed by Boucart and Ionescu has the threshold voltage de ned as the voltage where the  $I_D\{V_{GS} \text{ or } I_D\{V_{GS} \text{ characteristics}\}$  transitions between quasi-exponential and linear dependence on the drain current. In this method, two threshold voltages are determined. This de nition has the disadvantage that it depends strongly on the TFET junction design and gate geometry.

We propose a practical definition for effective subthreshold swing which anticipates the voltage scaling attribute of low-subthreshold-swing devices. First, de ne the threshold voltage to be half the supply voltage, i.e.,  $V_{T\,H}=V_{DD}/2$  and  $I_{T\,H}=I_D(V_{GS}=V_{DD}/2)$ . In this definition, the o-voltage equals zero, the o-current becomes the drain current at  $V_{GS}=0$ , and the e ective subthreshold swing is simply de ned by  $S=V_{DD}/[2\log(I_{T\,H}/I_{OF\,F})]$ . Basic direct current (dc) performance of the TFET is then characterized by specifying oncurrent, supply voltage, and effective S.

#### **Evolution of advanced MOSFET structures**

The aggressive downscaling of planar MOSFET structures suffers from several short channel effects which sought for the evolution of non-conventional device architectures to keep pace with the scaling trend specified by ITRS. Fabricational complexities and functional limitations of traditional MOS at low dimension make it unsuitable for implementation in nano-scaled integrated circuits. Further diminution of MOSFET feature size faces various challenging issues in terms of saturation current while lowering the leakage conduction, reducing the power supply and achieving uniform device parameters within the chip. Hence new alternative devices referred as "non-classical CMOS" with newer structural designs and materials pave a new path towards the explosive growth in microelectronics industry.

Here, some advanced MOSFET architectures and their structural benefits are described below:

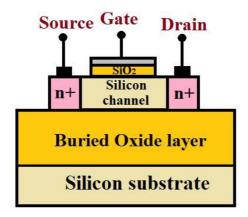

## **Silicon On Insulator (SOI) MOSFET:**

The main inspiration to switch from conventional MOS to Silicon On Insulator (SOI) MOSFET technology is to widen the scalability of CMOS with enhanced

**Figure.** - Cross-sectional representation of SOI MOSFET.

device performance so that they can override the future silicon technology. Like MOSFET, it also maintains silicon as the starting material for fabrication of integrated circuits owing to the low cost of silicon and its ability to form a good quality oxide with smooth interface over device channel.

The exclusive feature of SOI structure is the existence of a thick layer of silicon dioxide (orders of 100 nm) embedded between thin layer of silicon channel (orders of 10 nm) and silicon substrate. The thick oxide layer referred as the buried oxide layer (BOX) can be grown by oxidation or by implantation of oxygen into the silicon wafer. The thin silicon film over the BOX layer is the 'silicon channel' while relatively thicker silicon layer below the BOX is the 'SOI body'. The cross-sectional view of SOI MOSFET is shown in figure.

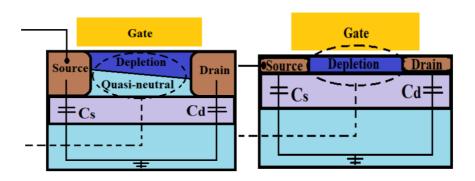

Figure. - Cross-sectional view of (a) PD SOI MOSFET and (b) FD SOI MOSFET.

Depending upon the thickness of the silicon channel, SOI MOSFET can be operated either in partially depleted (PD) or fully depleted (FD) mode of regime

as shown in figure In partially depleted SOI structure, the depletion region does not fully cover the silicon film hence leaving undepleted neutral silicon layer even when the device is operating under inversion condition on application of suitable bias voltage. Thus, the thickness of the silicon film exceeds the maximum gate depletion width and this undepleted region at the back interface acts as a floating body in PD SOI MOSFET. In contrast to this, in FD SOI MOSFET, the silicon film with thickness less than the gate depletion width causes the entire silicon channel to be depleted even before achieving the threshold condition. The relatively thinner silicon film eliminates the floating body effects while the presence of very thick buried oxide reduces the junction capacitance in FD SOI. Some of the notable advantages of SOI MOSFET are reduction in source-substrate and drain substrate parasitic capacitance with momentous improvement in speed, power consumption and performance gain of the circuits, additional isolation between adjacent SOI devices due to the existence of thick BOX layer which in turn

facilitates higher package density, prevention in latch up and latch up induced device breakdown, reduction in p-n junction leakage current due to the thin silicon film and its reduced source/drain junction depths, high immunity to SCEs and highly energized radioactive elements being blocked by the thick BOX layer. However, ultra-low dimensional SOI MOSFET performance is also limited by some challenging issues that degrade the short channel characteristics of the device. PD SOI MOSFET exhibits 'Kink effect' resulting drain current overshoot in DC circuits due to the combined action of floating body effect and parasitic bipolar effects which are very difficult to suppress. Again the fabrication of ultra-thin films of FD SOI requires complicated design processing and also excellent interface quality is needed at BOX/channel interface to reduce scattering. SOI is further subjected to self- heating phenomenon due to lower thermal conductivity of silicon dioxide of BOX that has a serious impact on device reliability and performance

## Silicon On Nothing (SON) MOSFET:

Silicon On Nothing (SON) is considered as an improvised alternative to SOI MOSFET with enhanced scalability based on the concept of buried layer engineering. In contrast to SOI, the buried oxide layer in SON MOSFET is replaced by air gap beneath the silicon channel as shown in figure. Such structure

has been proved to provide excellent imperviousness to short channel effects with improved electrical characteristics thereby satisfying the aggressive scaling requirements of ITRS.

Figure. Schematic of Silicon On Nothing (SON) MOSFET.

Researchers have explored SON technology both experimentally and analytically as a lucrative option for future low power applications. The lower dielectric permittivity of the buried 'air' layer reduces the parasitic junction capacitance across the source/substrate and drain/substrate junction resulting high speed operating devices. It also offers the highest electrostatic isolation from undesirable field line penetration to the active channel region. Electrostatic coupling is also reduced through the lower dielectric air layer relaxing the requisite of ultra thin silicon film. Additional inherent features of SON include reduced power consumption, immunity to radioactive elements, improved scalability, low noise performance and faster switching performance at reduced cost.

## **Multi-gate MOSFET:**

As already discussed, unlike long channel MOSFETs where current conduction is dominated by gate induced electric field, short channel MOSFETs experience two dimensional charge sharing with gate and drain electric field lines controlling the channel charge. Thus, the sole gate controllability over the device channel is suppressed leading to several inevitable short channel effects. Recently, multi gate MOSFET structures are emerging as potential solution to prevent the intrusion of drain side electric field lines into the channel and control the SCEs effectively. The existence of more than one gate increases the driving current capability of the device, improves the subthreshold characteristics and hence enhances the device scalability. Double-gate, tri-gate, FinFET, quadruple gate, gate all around are some of the special multi gate configuration of MOSFET structures. The double gate geometry is suggested in 1984 by Hayashi to achieve high transconductance and improved subthreshold slope with enhanced gate control. Double gate structures can be operated either as tied or independent gate. In tied gate mode, both the front and back gates are biased with the same voltage whereas in independent gate mode, the gate electrodes are independently connected to separate bias voltages. Hence, in independent mode, the front gate threshold voltage is controlled using back gate bias in contrast to tied gate mode, where the channel charge is controlled by both the gates simultaneously. Although, experimental demonstration of double gate structures has been reported in literature, existence of silicon film between the front and back gates with thickness less than the physical gate length involves complicated fabrication processes and hence commercially not so popular [15]. Trigate MOSFET is another popular structure where the active channel is wrapped by the gate on all three sides: the two side surfaces with height H and the top surface with width W. The three surfaces in

trigate configuration thus control the channel charge conduction while its corners where the side surfaces meet the top one act as critical contributor towards device operation. In FinFET, the top surface is covered by the thick layer of oxide and hence does not contribute to the conduction of the channel. FinFET has aspect ratio higher than tri-gate with 'fin width' being determined by the height and width and 'fin height' being defined by thickness of the active channel. Such gate structure modulation is further extended to gate all around configuration with gate electrode encircling the channel on all sides. Due to its unique device geometry of gate wrapped channel, the gate electrostatic control and subthreshold behavior of the device is highly improved with consequent suppression of undesirable short channel effects in comparison to single and double gate counterparts.

# Gate work function engineering: Emerging performance boosting technique of scaled devices:

It is quite evident from the previous discussion that downscaling of device feature size for progressive growth of VLSI industry faces the unavoidable detrimental SCEs and associated bottlenecks that are constantly degrading the overall performance of the devices. Hence, to improve the device functional competence, novel device architectures with modulated material property are being propounded by device engineers and researchers satisfying the aggressive specifications of ITRS requirements. Gate work function engineering is another possible solution to combat the adverse SCEs while enhancing the device performance effectively thereby opening a new research avenue to explore.

Recently, metal gates are replacing the standard polysilicon gates and emerging as a suitable alternative to suppress the undesirable SCEs, polysilicon depletion effects, boron penetration, etc. However, metal gates have some inherent limitations including thermal or chemical instability with high-k gate dielectric, annealing needed to passivate the interface charges trapped unintentionally, problems related to plasma layer damage due to cross-contamination, deposition of material and reactive ion etching (RIE) and adequacy in the availability of metal work-functions.