[3+2]

## M.TECH. VLSI AND MICRO ELECTRONICS FIRST YEAR FIRST SEMESTER - 2024 Subject : ADVANCED ANALOG IC DESIGN

Time: 3 hours Full Marks: 100

Instructions: Answer any five questions and write answers of all parts of a question together

- 1.a) Write the drain current expression and list the large signal model parameters of a long channel nMOSFET. [5] b) Explain channel length modulation. [5] c) Explain the change of threshold voltage with the application of body bias. [5] d) In a long channel nMOSFET calculate the threshold voltage when a body bias of 5V is applied. Given that V<sub>FB</sub>=0.2V, N<sub>A</sub>=10<sup>17</sup>/cc, t<sub>ox</sub>=10nm ε<sub>Si</sub>=11.9ε<sub>0</sub>, ε<sub>ox</sub>=3.9ε<sub>0</sub>, ε<sub>0</sub>=8.85×10<sup>-12</sup> F/m . [5]

2.a) Draw and explain the MOS diode as an active resistor. Find the expression for the resistance offered. [5+5] b) Draw and explain the n-channel current mirror. Discuss three non-ideal effects that cause the current mirror deviate from the ideal situation. [4+6]

3.a) Explain the advantages of Differential amplifier over single ended amplifier. [5]

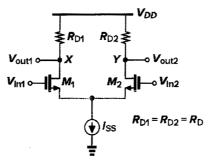

- b) Draw the block diagram of an OPAMP and briefly explain the function of each stage. [5] c) From the large signal analysis of the basic nMOS differential pair of below Fig. derive the expression for the differential voltage gain. [10]

- 4. a) List the requirements to design an OP-Amp. [5]

- b) Explain the large signal transconductance characteristics of a CMOS differential amplifier. [10]

- c) Draw a CMOS differential amplifier with current mirror load. Write the expression for ICMR. [5]

- 5.a) Explain Miller effect in common source amplifier. If the gate-drain capacitance is 1pF and gain of the amplifier is -50 then calculate the Miller capacitance at the input side of the amplifier.

- b)Draw and explain Cascode Amplifier to avoid Miller effect. [10]

- c)Draw a simple Cascode amplifier with active load. How can it reduce the Miller effects? [2+3]

- 6.a) What are the advantages and disadvantages of BiCMOS over MOSFET and BJT. [5]

- b) Draw and calculate the composite transconductance of Darlington pair BiCMOS circuit. [2+5]

c) Explain a BiCMOS current mirror. [8]

- 7. a) Discuss the primary advantages and disadvantages of switched capacitor circuits. [5]

- b) Design a resistance with the help of a switched capacitor.

c) For a parallel switched capacitor circuit of a resistor if clock frequency is 250KHz, C<sub>1</sub>=C<sub>2</sub>=C, find the value of capacitor to design a 1MΩ resistor.