## MODELING OF DEVICES FOR MODERN VLSI CIRCUITS AND VLSI CIRCUIT DESIGN

# Thesis Submitted by Sudipta Ghosh

**DOCTOR OF PHILOSOPHY (ENGINEERING)**

Electronics and Telecommunication Engineering Department

Faculty Council of Engineering & Technology

Jadavpur University

Kolkata, India

### JADAVPUR UNIVERSITY KOLKATA- 700032

INDEX NO. 178/17/E

#### 1. Title of the thesis:

## MODELING OF DEVICES FOR MODERN VLSI CIRCUITS AND VLSI CIRCUIT DESIGN

## 2. Name, Designation & Institution of the Supervisors:

#### Prof. P. Venkateswaran

Professor & Former Head Department of Electronics and Telecommunication Engineering Jadavpur University Kolkata-700032, India

#### Prof. Subir Kumar Sarkar

Professor & Former Head Department of Electronics and Telecommunication Engineering Jadavpur University Kolkata-700032, India

#### 3. List of Publications:

### **Journal Publications (5)**

- 1. **Ghosh. Sudipta**, Saha. Priyanka, Mukherjee. Adrija, Bose, Sayan. Venkateswaran, P., Sarkar. Subir Kumar, "Analytical Modeling of Core–Shell Junctionless RADFET dosimeter of Improved Sensitivity" Silicon (2022), 1876-9918, <a href="https://doi.org/10.1007/s12633-022-01690-y">https://doi.org/10.1007/s12633-022-01690-y</a>. [I.F:2.67, SCI Journal]

- 2. **Sudipta Ghosh**, P. Venkateswaran, and Subir Kumar Sarkar, "Analysis of circuit performance of Ge-Si hetero structure TFET based on analytical model", Circuit World, ISSN: 0305-6120. <a href="https://doi.org/10.1108/CW-08-2020-0175">https://doi.org/10.1108/CW-08-2020-0175</a>, 2021. [I.F:0.875, SCI Journal]

- 3. Sourav Guha, Prithviraj Pachal, **Sudipta Ghosh**, Subir Kumar Sarkar, "Analytical model of a novel double gate metal-infused stacked gate-oxide tunnel field-effect transistor (TFET) for low power and high-speed performance", Superlattices and Microstructures, Volume 146, 2020, ISSN 0749-6036, doi.org/10.1016/j.spmi.2020.106657. [Impact. Factor:2.658, SCI Journal]

- 4. S Nath, A K Chakravarty, **S Ghosh** and S K Sarkar, "FPGA Placement Optimization using Firefly Algorithm", Advances in Industrial Engineering and Management, American Scientific Journal, ISSN: 2222-7059Vol. 6, no. 2, pp. 97-102, 2017 Peer Reviewed Journal [Impact.Factor:1.60, DOAJ Indexed]

- 5. **S Ghosh**, S Nath and S K Sarkar "Performance Study of PSO Variants and its' Comparison with Firefly Algorithm in the context of VLSI Global Routing", SSRG International Journal of Electronics and Communication Engineering, Special Issue, ISSN: 2348 8549., pp. 63-77, 2015.Peer Reviewed Journal. [Impact.Factor:0.72, SCOPUS]

#### **Conference Publications (6)**

- 1. **Sudipta. Ghosh**, A. Jana, A. K. Agnihotri, S. Kundu, D. Das and S. K. Sarkar, "DC and Analog/RF Performance Comparison of Renovated GAA JLFET Structures," 2022 IEEE VLSI Device Circuit and System (VLSI DCS), 2022, pp. 80-84, doi: 10.1109/VLSIDCS53788.2022.9811488.

- 2. **Sudipta. Ghosh**, S. Bose, W. Anwar, M. Banerjee, P. Venkateswaran and S. K. Sarkar, "DC and Analog/RF Performance Analysis of Gate-Drain Underlapped and Channel Engineered TFET," 2022 IEEE VLSI Device Circuit and System (VLSI DCS), 2022, pp. 70-74, doi: 10.1109/VLSIDCS53788.2022.9811483.

- 3. **Sudipta Ghosh**, S. Kundu, S. Guha, J. Ghosh, P. Pachal and S. K. Sarkar, "Effect of Body Thickness on Device Performance of Graded Channel Tri-Metal Double Gate Stack Gate TFET," 2020 IEEE VLSI DEVICE CIRCUIT AND SYSTEM (VLSI DCS), Kolkata, India, 2020, pp. 427-431, doi: 10.1109/VLSIDCS47293.2020.9179899.

- 4. **Sudipta Ghosh**, P. Pachal, R. Kumar, S. Kundu, J. Ghosh and S. K. Sarkar, "Performance enhancement of p-n-p-n TFET with spacer induced hetero-dieletric gate oxide" 2020 IEEE VLSI DEVICE CIRCUIT AND SYSTEM (VLSI DCS), Kolkata, India, 2020, pp. 1-5, doi: 10.1109/VLSIDCS47293.2020.9179943.

- 5. **Sudipta. Ghosh**, S. Nath, R. Biswas, P. Venkateswaran, J. K. Sing and S. K. Sarkar, "PSO Variants and its Comparison with Firefly Algorithm in Solving VLSI Global Routing Problem," 2018 IEEE Electron Devices Kolkata Conference (EDKCON), Kolkata, India, 2018, pp. 513-518, doi: 10.1109/EDKCON.2018.8770397.

- 6. S Nath, **Sudipta Ghosh** and S K Sarkar, "A Novel Approach to Discrete Particle Swarm Optimization for Efficient Routing in VLSI Design", 4th IEEE International Conference on Reliability, Infocom Technologies and Optimization, Noida, India, 2014.

#### **4. List of Patents:** NIL

## 5. List of Presentations in National/International Conferences:

1. **Sudipta Ghosh**, P. Pachal, R. Kumar, S. Kundu, J. Ghosh and S. K. Sarkar, "Performance enhancement of p-n-p-n TFET with spacer induced hetero-dieletric gate oxide" 2020 IEEE VLSI DEVICE CIRCUIT AND SYSTEM (VLSI DCS), Kolkata, India, 2020, pp. 1-5, doi: 10.1109/VLSIDCS47293.2020.9179943.

## **Statement of Originality**

I, Sudipta Ghosh, registered on 31st July, 2017, do hereby declared that the thesis entitled "Modeling of Devices for Moder VLSI Circuits and VLSI Circuit Design" contains literature survey and original research work done by undersigned candidates as part of Doctoral studies.

All information in this thesis have been obtained and presented in accordance with existing academic rules and ethical conduct. I declare that, as required by these rules and conduct, I have fully cited and referred all materials and results that are not original to this work.

I also declared that I have checked this thesis as per the "Policy on Anti Plagiarism, Jadavpur University, 2019", and the level of similarity as checked by iThenticate software is 1%.

Signature of Candidate:

Date: 16.04.2024

Certified by Supervisor:

(Signature with date, seal)

Dr. P. Venkateswaran

PROFESSOR

Dept. of Electronics & Tele-Comm. Engg.

JADAVPUR UNIVERSITY

Kolkata-700 032.

Certified by Supervisor:

(Signature with date, seal)

### Dedicated 7o

My Grand Parents Late Monimohan Ghosh & Late Bina Ghosh

My Parents

Late Ashim Kumar Ghosh & Late Ila Gosh My Elder Sister

Late Soma Ghosh

For their heavenly blessings

And

My Wife

Smt. Shrabani 7arafder

For their constant support, cooperation and selfless sacrifice

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere love and gratitude to my supervisors, **Prof. Subir Kumar Sarkar**, and **Prof. P. Venkateswaran** from Jadavpur University, Department of Electronics and Telecommunication Engineering, Kolkata-700032, for their tremendous guidance, sound counsel, ongoing support, kind actions, and inspirations over the course of my research work. They have not only helped me get the thesis to this point, but also extended their helping hands whenever I needed them.

I would also like to take this opportunity to thank the Faculty Council of Engineering and Technology, Head of the Department, and all faculty members of Department of Electronics and Telecommunication Engineering at Jadavpur University for allowing me to continue my research and for providing me with various inputs and guidance when I needed it.

I would also like to thank Director Sir, Principal Sir and HOD Sir (Dept. of ECE) of Meghnad Saha Institute of Technology for extending their immense support on pursuing my research work. I will remain indebted to all my colleagues of Department of ECE, especially Dr. Manash Chanda and Dr. Sudip Dogra for their continuous support and motivation, that paved the way to complete my research endeavor successfully.

I would especially like to acknowledge Dr. Manash Chanda and Dr. Priyanka Saha and would always remain indebted to them for their constant technical supports, guidance, suggestions and help in my Ph.D. journey.

I would extend special thanks to my fellow research scholars Mr. Subhrapratim Nath, Dr. Anup Dey, Dr. Dinesh Kumar Dash, Mr. Bijoy Goswami, Dr. Subhasis Roy, Mr. Abir Jana, Ms. Komal Kumari for their continuous emotional supports and efforts to the laboratory making an interesting place to work.

I would like to thank Mr. Suman Mandal & family for their love, affection and emotional touch during my journey of Ph.D. work.

I would like to express my love and respect to my elder sister for her endless support and sacrifice without which the work could never been completed successfully.

Finally, heartful thanks to everyone for whom this thesis would have seen the light of the day.

(Sudipta Ghosh)

April, 2024 Jadavpur University Kolkata-700 032

### **ABSTRACT**

The ever-ending advancement in the fields of electronics, wireless communication and internet-of-things (IoT) fueled by a steady, uninterrupted growth of complementary metal oxide semiconductor technology has called for sustainable development of the downscaling of solid-state devices in sub-micrometer regime. As a result, the industry gets privileged with a profound escalation in packaging density and device performance. Moreover, the cost-perfunction of modern state-of-art electronic modules has been drastically reduced, setting marks for economic precedence with every upgraded technological node. The scalability of devices acts as a boon for device performances with zero static power consumption, high integration density, lesser physical space, and simple process steps and layout design, driving the CMOS technology an integral part in our everyday life, starting from handheld electronics to transportation and communication.

However, the rapid cadence of device downscaling is no longer feasible in the sub-100 nm regime to fortify Moore's law, pursuing the conventional scaling strategies. Several device scaling issues stem from gate leakage, variabilities and reliabilities, and after all, short channel effects like drain induced barrier lowering (DIBL), gate induced drain leakage (GIDL), mobility degradation, and random dopant induced threshold voltage fluctuation. Nevertheless, the rise in leakage current restricts threshold voltage scaling further, posing barrier to supply voltage scaling, which is essentially required for high-speed ICs.

In the late 90s, the increasing demand for low-power technologies due to the extensive use of wireless and portable appliances forced Dennard's scaling theory to be practically implemented. Furthermore, the world-wise use of power-hungry smart gadgets calls for reduced power matrices (both active and standby power) by downscaling the supply voltage below 0.5V without compromising the circuit performance. This scenario motivated the researchers to explore new engineering concepts and novel device structures with better scalability and performance. Therefore, a series of researches have been carried out with the Bulk MOSFET technology improvising new structural engineering and amalgamation of novel materials, as well as, looking for alternative devices with the merit of below 60 mV/decade subthreshold swing. As a result, some impressive device structures come up as potential alternatives to overcome the encumbrances associated with nanostructures. For example, Silicon-on-Insulator (SOI) and Silicon-on-Nothing (SON) Metal Oxide Semiconductor attracted significant attention due to their higher scalability and lowered parasitic effects than

conventional MOSFETs. However, the SOI/SON-based circuit couldn't offer the best power-speed performance as expected, resulting in a further quest for new structures. Junctionless Transistors (JL FET) emerge as one of the best solutions due to their insusceptibility against short channel effects and simple fabrication process. However, despite its significant contribution to the VLSI domain, the device still suffers from degraded subthreshold swing, owing to its thermionic constraints, leading to an expensive power budget.

Hence, a MOSFET-like structure with alternative energy-efficient technology becomes inevitable to sustain CMOS logic design in future. The Tunnel Field Effect Transistor (TFET), one of the potential contenders, takes the privilege of quantum mechanical tunneling and ballistic transport phenomena driven by low power supply, offering a minimal power-speed product earnestly required for today's cut-in technological nodes. Moreover, the device is compatible with the latest fabrication technology, favoring ultra-high-density packaging to integrate billions of transistors in a single chip. However, two major constraints include low drive current and ambipolar conduction forbidding the device implementation in VLSI circuits.

VLSI Global routing is another back-end design aspect of optimizing the power-delay expenditure in today's level-headed industrial VLSI research. With ever-increasing layout complexity, the routing of interconnects gets more complicated and tedious task. Therefore, the routing problem during VLSI physical design is considered an NP-hard problem, where the solution lies in finding the minimal cost of Rectilinear Steiner Tree from the graph comprising all the terminal nodes to be electrically connected. In order to have an acceptable solution by Global routing, we need to shrink the core area and the critical path delay, where delay precisely depends on the total interconnected wire length and the number of vias used in a three-dimensional VLSI system. Swarm intelligence, inspired by the intellectual activity of the biotic creators of nature, is one of the emerging and promising optimization tools that may be implemented in this field to optimize interconnect lengths in achieving the desired performance (speed) of modern ICs.

Therefore, the present dissertation circumscribes comprehensive performance evaluations of TFET to register its footprint as a potential candidate in low-power, high-speed VLSI design. The multi-gate structure with work function engineering, implementation of stacked gate oxide to bar gate leakage, pocket implantation as channel engineering, and use of low bandgap material to construct heterostructures are strategically procured to escalate the drive current and submerge the ambipolar conduction of elementary TFETs, count on the derived analytical

model to justify the superiority of the proposed architectures over the conventional ones. Hence, the analytical results are validated through effective simulation to substantiate the accuracy of the proposed models. Moreover, the device-circuit interaction is investigated thoroughly by implementing the proposed TFET based inverter. The outcome revealed an excellent power-delay product (PDP) matric compared to the conventional CMOS logic to legitimize the worthiness of the proposed structure in energy harvesting applications. In addition, the responses of a core-shell junctionless transistor, deployed in circuit application as a robust radiation sensor in VLSI circuits, have been thoroughly examined and the outcomes are verified by both theoretically and simulation process.

Nevertheless, in the back-end design, swarm intelligence promises a near satisfactory solution to the global routing problem. Two new variants of discrete particle swarm optimization (DPSO) are formulated to optimize wire lengths, and finally, proposed variants of PSO have been compared with the Firefly algorithm in terms of optimization of timing budget by minimizing the interconnect delay as a primary concern. The merits of the proposed algorithms have been inspected through time complexity, computational load, and convergence rate as well.

## Table of Contents

| Cor          | itents                                              | Page No.       |

|--------------|-----------------------------------------------------|----------------|

| Ackn<br>Abst | nowledgements<br>ract                               |                |

| List         | of Figures<br>of Tables<br>of Abbreviations         | v<br>xi<br>xii |

| Chap         | oter 1: Introduction and Organization of the Thesis | 1-30           |

| 1.1.         | Introduction and Motivation                         | 1              |

| 1.2.         | Motivation                                          | 8              |

| 1.3.         | Literature Review                                   | 10             |

| 1.4.         | Organization of the Thesis                          | 18             |

|              | Reference                                           | 20             |

| Chap         | oter 2: Fundamentals of Semiconductor Devices and   |                |

|              | VLSI Physical Design                                | 31-78          |

| 2.1.         | Introduction                                        | 31             |

| 2.2.         | Semiconductor Devices                               | 33             |

| 2.2          | 2.1. Overview of MOSFET                             | 34             |

| 2.2          | 2.2. MOSFET Models                                  | 38             |

| 2.2          | 2.3. Analytical Modeling Approach of MOSFET         | 39             |

| 2.2          | 2.4. MOSFET Scaling                                 | 40             |

| 2.2          | 2.5. Short Channel Effects (SCEs)                   | 43             |

|              | 2.2.5.1. Reduction of Effective Threshold Voltage   | 43             |

|              | 2.2.5.2. Drain induced Barrier Lowering (DIBL)      | 44             |

|              | 2.2.5.3. Off-State Leakage Current                  | 44             |

|              | 2.2.5.4. Impact Ionization                          | 45             |

|              | 2.2.5.5. Drain Punch Through                        | 45             |

|              | 2.2.5.6. Hot Carrier Effect                         | 46             |

|              | 2.2.5.7. Velocity Overshoot Effect                  | 46             |

|              | 2.2.5.8. Surface Scattering                         | 47             |

|              | 2.2.5.9. Velocity Saturation                        | 47             |

|              | 2.2.5.10. Channel Length Modulation                 | 47             |

|              | 2.2.5.11. Gate Induced Drain Lowering (GIDL)        | 48             |

|              | 2.2.5.12. Parasitic Bipolar Effect                  | 48             |

| 2.2.5.13. Subthreshold Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 48                                                                   |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|

| 2.2.6. Structural Remedies of Short Channel Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49                                                                   |  |

| 2.2.6.1. SOI MOSFET (Silicon on Insulator)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |  |

| 2.2.6.2. SON MOSFET (Silicon on Nothing)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49<br>53                                                             |  |

| 2.2.7. Overview of TFET (Tunnel Field Effect Transistor)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54                                                                   |  |

| 2.2.8. TFET Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 55                                                                   |  |

| 2.2.9. TFET V-I Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56                                                                   |  |

| 2.2.9.1. Qualitative Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56                                                                   |  |

| 2.2.9.2. Characteristics Curves                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61                                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65                                                                   |  |

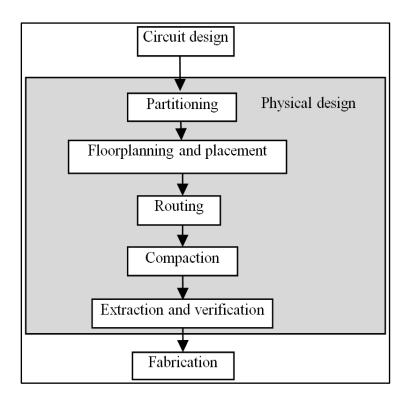

| 2.3. VLSI Physical Design Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 66                                                                   |  |

| 2.3.1. VLSI Physical Design Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 67                                                                   |  |

| 2.3.1.1. Partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68                                                                   |  |

| 2.3.1.2. Floorplanning and Placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |  |

| 2.3.1.3. Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 68                                                                   |  |

| 2.3.1.4. Compaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 69                                                                   |  |

| 2.3.1.5. Extraction and Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 69<br>70                                                             |  |

| 2.3.2. VLSI Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70                                                                   |  |

| 2.3.3. Swarm Intelligence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 72                                                                   |  |

| Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 74                                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                      |  |

| Chanton 2. Evaluring the Impact of Cate and Channel Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                      |  |

| Chapter 3: Exploring the Impact of Gate and Channel Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 70_116                                                               |  |

| Chapter 3: Exploring the Impact of Gate and Channel Engineering on the Output Performances of TFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79-116                                                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>79-116</b><br>80                                                  |  |

| on the Output Performances of TFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                      |  |

| on the Output Performances of TFETs  3.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 80                                                                   |  |

| on the Output Performances of TFETs  3.1. Introduction 3.2. Reviewing the Relevant Works                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80                                                                   |  |

| on the Output Performances of TFETs  3.1. Introduction 3.2. Reviewing the Relevant Works 3.3. Performance Enhancement of Graded Channel Tri-metal                                                                                                                                                                                                                                                                                                                                                                                                      | 80<br>81                                                             |  |

| on the Output Performances of TFETs  3.1. Introduction 3.2. Reviewing the Relevant Works 3.3. Performance Enhancement of Graded Channel Tri-metal Double Gate TFET with Stack Gate Architecture                                                                                                                                                                                                                                                                                                                                                        | 80<br>81<br>87                                                       |  |

| on the Output Performances of TFETs  3.1. Introduction 3.2. Reviewing the Relevant Works 3.3. Performance Enhancement of Graded Channel Tri-metal Double Gate TFET with Stack Gate Architecture 3.3.1. Device Structure 3.3.2. Analytical Modeling                                                                                                                                                                                                                                                                                                     | 80<br>81<br>87<br>87                                                 |  |

| on the Output Performances of TFETs  3.1. Introduction 3.2. Reviewing the Relevant Works 3.3. Performance Enhancement of Graded Channel Tri-metal Double Gate TFET with Stack Gate Architecture 3.3.1. Device Structure 3.3.2. Analytical Modeling 3.3.2.1. Modeling of Surface Potential                                                                                                                                                                                                                                                              | 80<br>81<br>87<br>87<br>88                                           |  |

| on the Output Performances of TFETs  3.1. Introduction 3.2. Reviewing the Relevant Works 3.3. Performance Enhancement of Graded Channel Tri-metal Double Gate TFET with Stack Gate Architecture 3.3.1. Device Structure 3.3.2. Analytical Modeling 3.3.2.1. Modeling of Surface Potential 3.3.2.2. Modeling of Electric Field                                                                                                                                                                                                                          | 80<br>81<br>87<br>87<br>88<br>88                                     |  |

| on the Output Performances of TFETs  3.1. Introduction 3.2. Reviewing the Relevant Works 3.3. Performance Enhancement of Graded Channel Tri-metal Double Gate TFET with Stack Gate Architecture 3.3.1. Device Structure 3.3.2. Analytical Modeling 3.3.2.1. Modeling of Surface Potential 3.3.2.2. Modeling of Electric Field                                                                                                                                                                                                                          | 80<br>81<br>87<br>87<br>88<br>88<br>91                               |  |

| on the Output Performances of TFETs  3.1. Introduction 3.2. Reviewing the Relevant Works 3.3. Performance Enhancement of Graded Channel Tri-metal Double Gate TFET with Stack Gate Architecture 3.3.1. Device Structure 3.3.2. Analytical Modeling 3.3.2.1. Modeling of Surface Potential 3.3.2.2. Modeling of Electric Field 3.3.2.3. Modeling of Drain to Source Current                                                                                                                                                                             | 80<br>81<br>87<br>87<br>88<br>88<br>91<br>93                         |  |

| 3.1. Introduction 3.2. Reviewing the Relevant Works 3.3. Performance Enhancement of Graded Channel Tri-metal Double Gate TFET with Stack Gate Architecture 3.3.1. Device Structure 3.3.2. Analytical Modeling 3.3.2.1. Modeling of Surface Potential 3.3.2.2. Modeling of Electric Field 3.3.2.3. Modeling of Drain to Source Current 3.3.3. Results and Discussions                                                                                                                                                                                   | 80<br>81<br>87<br>87<br>88<br>88<br>91<br>93                         |  |

| 3.1. Introduction 3.2. Reviewing the Relevant Works 3.3. Performance Enhancement of Graded Channel Tri-metal Double Gate TFET with Stack Gate Architecture 3.3.1. Device Structure 3.3.2. Analytical Modeling 3.3.2.1. Modeling of Surface Potential 3.3.2.2. Modeling of Electric Field 3.3.2.3. Modeling of Drain to Source Current 3.3.3. Results and Discussions 3.4. Performance Enhancement of p-n-p-n TFET with Spacer                                                                                                                          | 80<br>81<br>87<br>87<br>88<br>88<br>91<br>93                         |  |

| on the Output Performances of TFETs  3.1. Introduction 3.2. Reviewing the Relevant Works 3.3. Performance Enhancement of Graded Channel Tri-metal Double Gate TFET with Stack Gate Architecture 3.3.1. Device Structure 3.3.2. Analytical Modeling 3.3.2.1. Modeling of Surface Potential 3.3.2.2. Modeling of Electric Field 3.3.2.3. Modeling of Drain to Source Current 3.3.3. Results and Discussions 3.4. Performance Enhancement of p-n-p-n TFET with Spacer and Hetero-gate oxide                                                               | 80<br>81<br>87<br>87<br>88<br>88<br>91<br>93<br>93                   |  |

| on the Output Performances of TFETs  3.1. Introduction 3.2. Reviewing the Relevant Works 3.3. Performance Enhancement of Graded Channel Tri-metal Double Gate TFET with Stack Gate Architecture 3.3.1. Device Structure 3.3.2. Analytical Modeling 3.3.2.1. Modeling of Surface Potential 3.3.2.2. Modeling of Electric Field 3.3.2.3. Modeling of Drain to Source Current 3.3.3. Results and Discussions 3.4. Performance Enhancement of p-n-p-n TFET with Spacer and Hetero-gate oxide 3.4.1. Proposed Device Structure                              | 80<br>81<br>87<br>87<br>88<br>88<br>91<br>93<br>93                   |  |

| on the Output Performances of TFETs  3.1. Introduction 3.2. Reviewing the Relevant Works 3.3. Performance Enhancement of Graded Channel Tri-metal Double Gate TFET with Stack Gate Architecture 3.3.1. Device Structure 3.3.2. Analytical Modeling 3.3.2.1. Modeling of Surface Potential 3.3.2.2. Modeling of Electric Field 3.3.2.3. Modeling of Drain to Source Current 3.3.3. Results and Discussions  3.4. Performance Enhancement of p-n-p-n TFET with Spacer and Hetero-gate oxide  3.4.1. Proposed Device Structure 3.4.2. Analytical Modeling | 80<br>81<br>87<br>87<br>88<br>88<br>91<br>93<br>93<br>97             |  |

| 3.1. Introduction 3.2. Reviewing the Relevant Works 3.3. Performance Enhancement of Graded Channel Tri-metal Double Gate TFET with Stack Gate Architecture 3.3.1. Device Structure 3.3.2. Analytical Modeling 3.3.2.1. Modeling of Surface Potential 3.3.2.2. Modeling of Electric Field 3.3.2.3. Modeling of Drain to Source Current 3.3.3. Results and Discussions 3.4. Performance Enhancement of p-n-p-n TFET with Spacer and Hetero-gate oxide 3.4.1. Proposed Device Structure 3.4.2. Analytical Modeling 3.4.2.1. Modeling of Surface Potential | 80<br>81<br>87<br>87<br>88<br>88<br>91<br>93<br>93<br>97<br>97<br>99 |  |

| 3.4.3. Results and Discussions<br>References                                                   |               |  |

|------------------------------------------------------------------------------------------------|---------------|--|

| Chapter 4: Device-Circuit Interactions of Heterojuncti TFET for Energy Harvesting Applications | on<br>117-160 |  |

| 3.1. Introduction                                                                              | 116           |  |

| 3.2. Reviewing the Relevant Works                                                              | 119           |  |

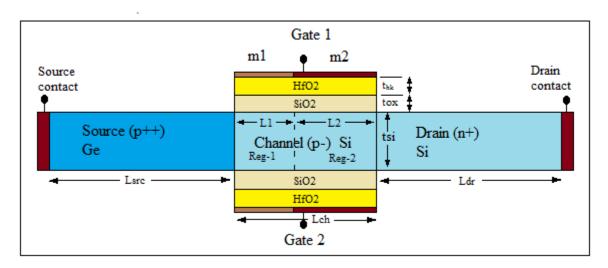

| 3.3. Proposed Device Structure                                                                 | 127           |  |

| 3.4. Analytical Modeling                                                                       | 128           |  |

| 3.4.1.Surface Potential                                                                        | 128           |  |

| 3.4.2. Electric Field                                                                          | 132           |  |

| 3.4.3. Drain Current                                                                           | 133           |  |

| 3.4.4. Tunneling Length Calculation                                                            | 136           |  |

| 3.5. Results and Discussions                                                                   | 137           |  |

| 3.6. Circuits Level Analysis                                                                   | 146           |  |

| References                                                                                     | 152           |  |

| Chapter 5: Sensitivity Analysis of Core-Shell Junctionless MOSFET as Radiation Sensor          |               |  |

| 5.1. Introduction                                                                              | 161           |  |

| 5.2. literature Survey                                                                         | 162           |  |

| 5.3. Device Structure and Radiation Dose profiles                                              | 171           |  |

| 5.4. Analytical Model Formulation                                                              | 173           |  |

| 5.4.1. Surface Potential Model                                                                 | 173           |  |

| 5.4.2. Modeling of Drain Current                                                               | 178           |  |

| 5.4.3. Calculation of Sensitivity and its correlation with                                     |               |  |

| Threshold Voltage-Shift                                                                        | 179           |  |

| 5.5. Results and Discussions                                                                   | 182           |  |

| References                                                                                     | 194           |  |

| Chapter 6: Performance Comparison of a Proposed PSO Variant with                               |               |  |

| Firefly Algorithm in Optimization of Global Ro                                                 | uting 202-234 |  |

| 6.1. Introduction                                                                              | 203           |  |

| 6.2. Literature Survey                                                                         | 204           |  |

| 6.3. Problem Statements                                                                        | 212           |  |

| 6.3.1. Global Routing in VLSI Physical Design                                                  |               |  |

| 6.3.2. Rectilinear Stainer Tree Problem                                                        |               |  |

| 6.4.                                     | Proposed Algorithms and Pseudo Codes   | 213     |

|------------------------------------------|----------------------------------------|---------|

| 6.4.1. Particle Swarm Optimization (PSO) |                                        | 213     |

|                                          | 6.4.1.2. Operators and Proposed Model  | 213     |

|                                          | 6.4.1.2. Pseudo Code of Proposed Model | 216     |

| 6.4                                      | 1.2. Firefly Algorithms                | 216     |

|                                          | 6.4.2.1. Operators and Basic Model     | 216     |

|                                          | 6.4.2.2. Pseudo Code                   | 218     |

| 6.5.                                     | Experimental Setups                    | 218     |

| 6.6.                                     | Results and Discussions                | 220     |

| 6.6                                      | 5.1. Experiment 1                      | 220     |

| 6.6                                      | 5.2. Experiment 2                      | 225     |

| References                               |                                        | 229     |

| Chap                                     | oter 7: Conclusions and Future Scopes  | 235-242 |

| 7.1.                                     | Conclusion                             | 235     |

| 7.2.                                     | Future Scope of the Work               | 241     |

## List of Figures

| Figure No     | Description                                                       | Page No. |

|---------------|-------------------------------------------------------------------|----------|

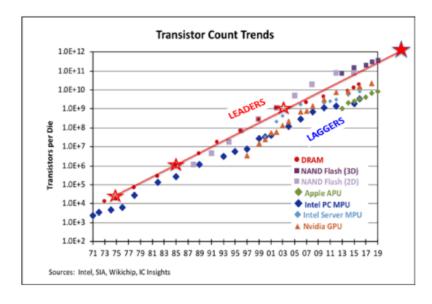

| Fig. 1.1      | The trend of semiconductor products as per the ITRS roadmap       | 2        |

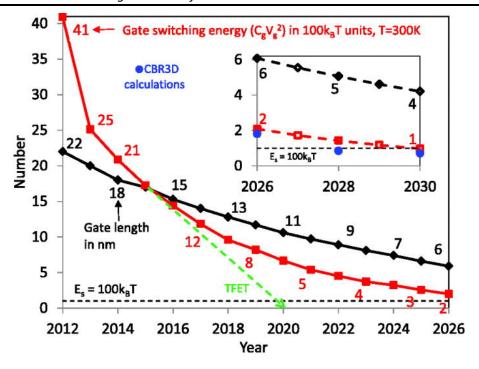

| Fig. 1.2      | The trend of technology node speculated by the ITRS roadmap       | 3        |

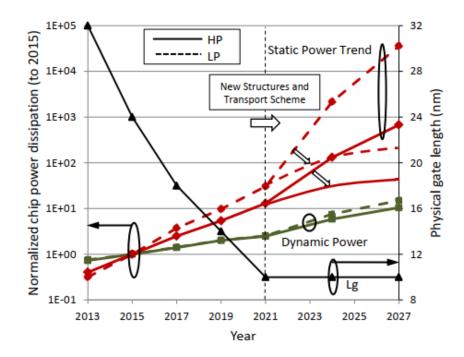

| Fig. 1.3      | Trends of Static and Dynamic power dissipation profiles with      |          |

|               | the decreasing technology nodes considering high-performance      |          |

|               | (HP) and low-performance (LP) devices                             | 4        |

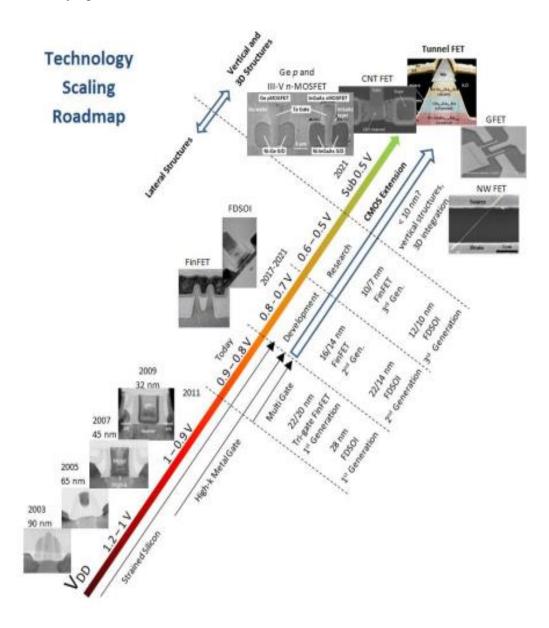

| Fig. 1.4      | Technology scaling roadmap: evolution of short channel devices    | 5        |

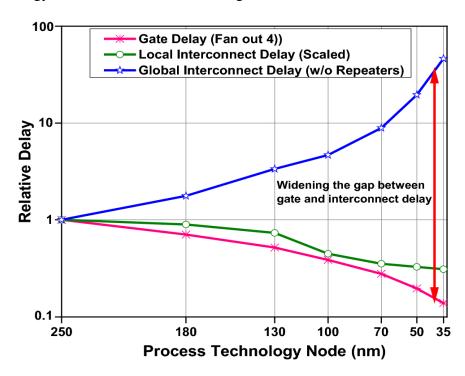

| Fig. 1.5      | Trends of relative delays with process technology considering     |          |

|               | the possible parameters predicted in the ITRS roadmap             | 7        |

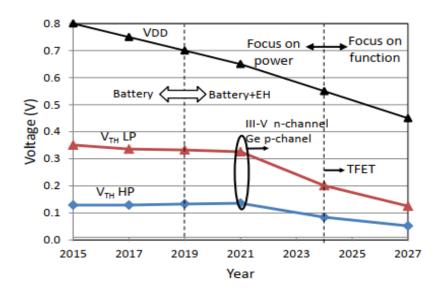

| Fig. 1.6      | Threshold voltage trend of high and low-performance CMOS          |          |

|               | technology [18]                                                   | 9        |

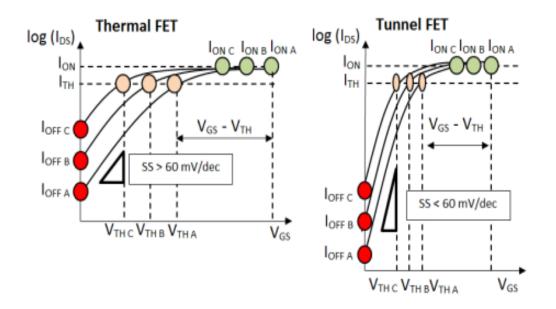

| Fig. 1.7      | Subthreshold characteristics of MOSFET vs. TFET                   | 9        |

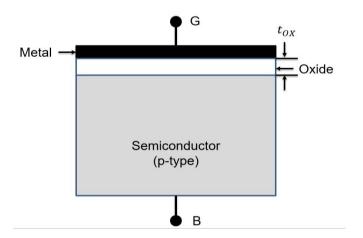

| Fig. 2.1      | Schematic view of MOS capacitor                                   | 34       |

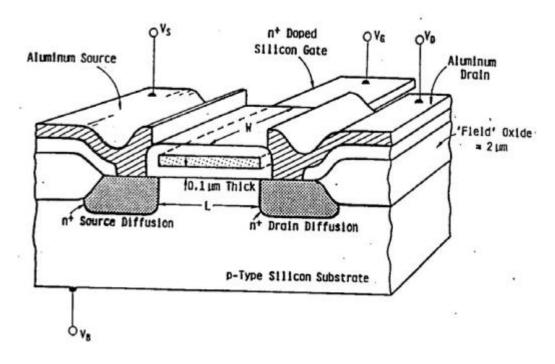

| Fig. 2.2      | Cross-sectional view of MOS Transistor [2.5]                      | 35       |

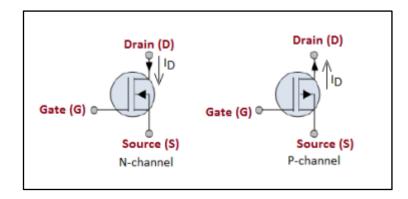

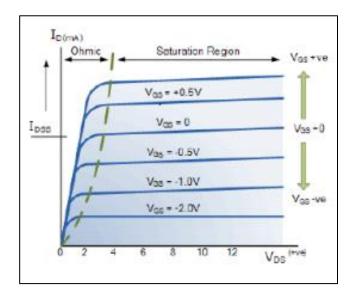

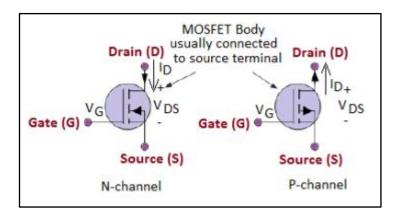

| Fig. 2.3      | Symbols of n and p-type Depletion type MOSFET                     | 35       |

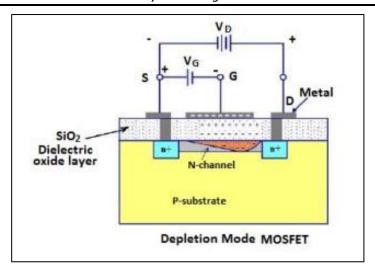

| Fig. 2.4      | Schematic view of a depletion-type n-channel MOSFET               | 36       |

| Fig. 2.5      | Drain characteristics of a depletion-type n-channel MOSFET        | 36       |

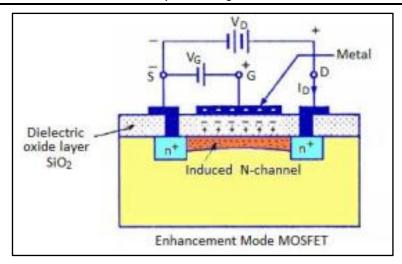

| Fig. 2.6      | Cross-sectional view of an Enhancement-type n-channel MOSFET      | 37       |

| Fig. 2.7      | Symbols of an n- and p-type Enhancement MOSFET                    | 37       |

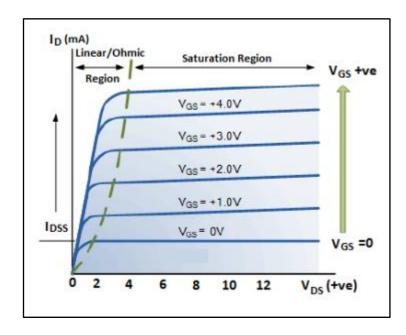

| Fig. 2.8      | Drain current characteristics of an Enhancement-type n-MOSFET     | 37       |

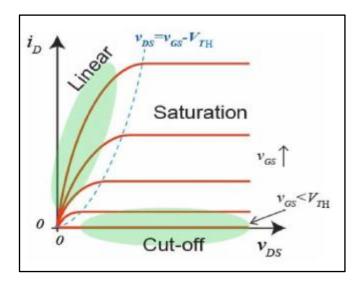

| Fig. 2.9      | Regions of operation an E-type n-MOSFET                           | 38       |

| Fig. 2.10 (a) | Moore's law of scaling                                            | 41       |

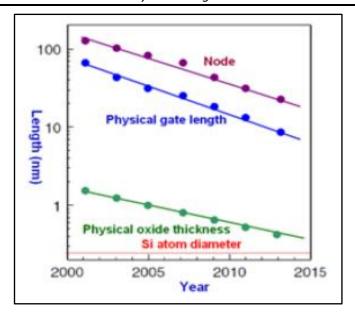

| Fig. 2.10 (b) | Gate length shrinking with scaling years (Courtesy ITRS 2010)     | 42       |

| Fig. 2.11     | The relationship between the trend of supply voltage scaling and  |          |

|               | threshold voltage                                                 | 42       |

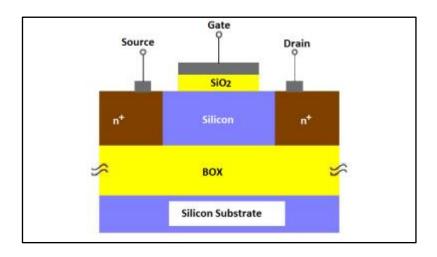

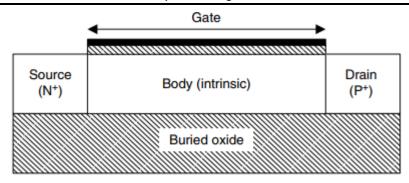

| Fig. 2.12     | Cross-sectional view of Silicon on Insulator MOS (SOI MOS)        | 49       |

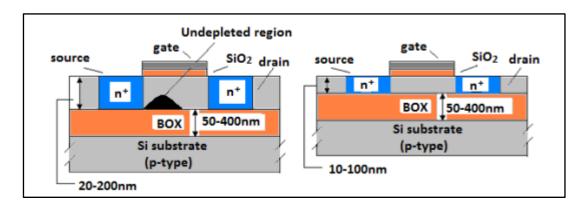

| Fig 2.13      | Cross-sectional views of Partially depleted and Fully-depleted SO | [        |

|               | MOSFETs                                                           | 50       |

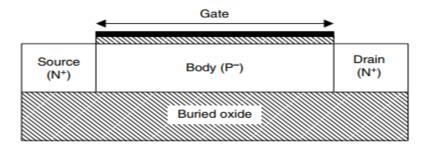

| Fig 2.14 (a)  | View from the cross-section of an n-channel MOSFET                | 55       |

| Fig 2.14 (b)  | View from the cross-section of an n-channel TFET                  | 55       |

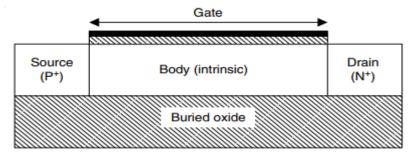

| Fig. 2.14 (c) | View from the cross-section of an p-channel TFET                  | 56       |

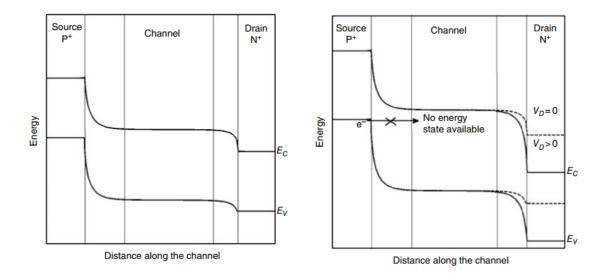

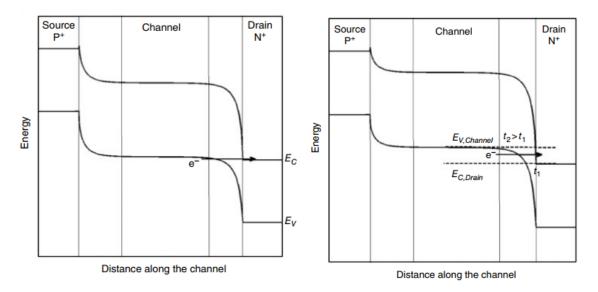

| Fig. 2.15 (a) | Under unbiased conditions, the band diagram of a TFET is in                                 |    |

|---------------|---------------------------------------------------------------------------------------------|----|

|               | an equilibrium state                                                                        | 56 |

| Fig. 2.15 (b) | The band diagram of a TFET is in the off state for Vds>0 and Vgs=0                          | 56 |

| Fig. 2.16 (a) | Band alignment of an n-TFET at the onset of drain current                                   | 57 |

| Fig. 2.16 (b) | Further band bending ensures an exponential rise in drain current                           | 57 |

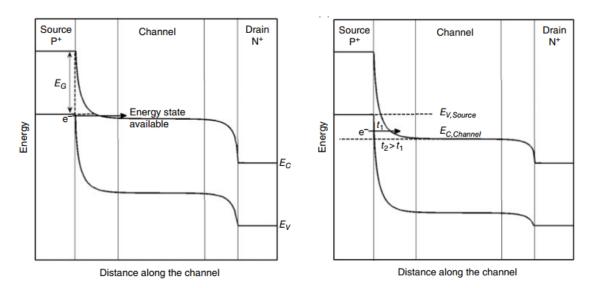

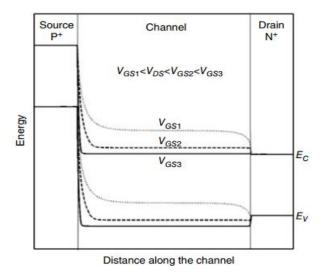

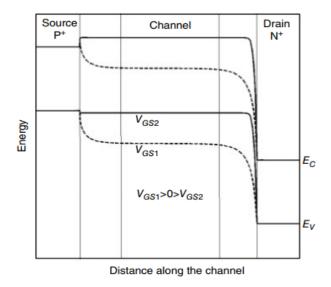

| Fig. 2.17     | Band diagram pointing the pining of the channel condition with the                          |    |

|               | biasing conditions Vgs > Vds                                                                | 58 |

| Fig. 2.18 (a) | Band diagram of an n-channel TFET for Vgs=0                                                 | 60 |

| Fig. 2.18 (b) | For Vgs < 0 the valence band of the channel moves upward                                    |    |

|               | compared to the conduction band of the drain                                                | 60 |

| Fig. 2.18 (c) | At a specific negative gate voltage, the channel's valence band aligns                      |    |

|               | with the drain's conduction band, and electron tunnelling from the                          |    |

|               | channel to the drain begins                                                                 | 60 |

| Fig. 2.18 (d) | An exponential rise in drain current results from a further drop in                         |    |

|               | Negative gate voltage                                                                       | 60 |

| Fig. 2.18 (e) | The channel potential becomes pinned with the source potential                              |    |

|               | as the gate voltage continues to drop                                                       | 61 |

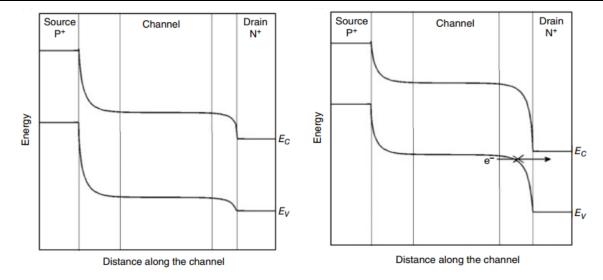

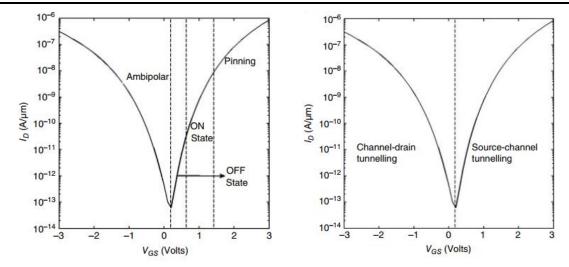

| Fig. 2.19 (a) | A TFET device's transfer characteristics showing its ON, OFF, and                           |    |

|               | ambipolar conduction states                                                                 | 62 |

| Fig. 2.19 (b) | This diagram illustrates the source-channel and drain-channel                               |    |

|               | tunnelling currents caused by positive and negative gate bias,                              |    |

|               | respectively                                                                                | 62 |

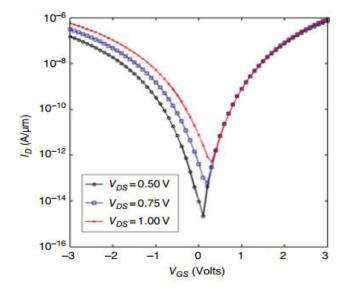

| Fig. 2.19 (c) | The variation of ambipolar conduction due to different drain-                               |    |

|               | to-source voltages $(V_{ds})$                                                               | 62 |

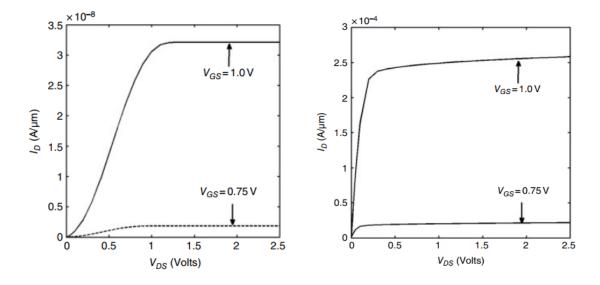

| Fig. 2.20 (a) | Output characteristics of TFET for two different gate voltages                              | 64 |

| Fig. 2.20 (b) | Comparison of n-TFET and MOSFET output characteristics                                      | 64 |

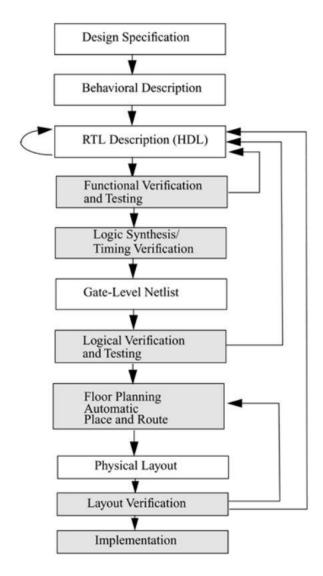

| Fig. 2.21     | VISI Design Flow                                                                            | 66 |

| Fig. 2.22     | VLSI Physical Design Cycle                                                                  | 67 |

| Fig. 3.1      | Two-dimensional illustration of the planned TMDG-TFET                                       | 87 |

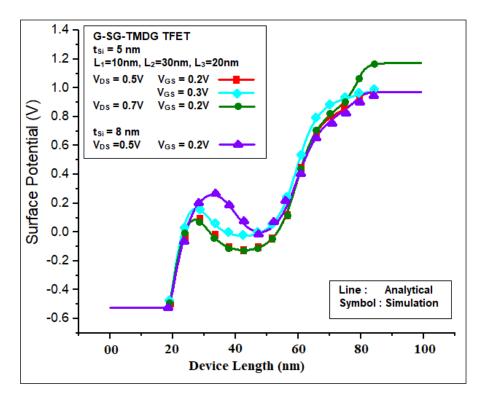

| Fig. 3.2      | Surface Potential Profile for Different Gate Voltages                                       |    |

|               | (at Constant $V_{\rm DS}\!)$ and Different Drain Voltages for the Proposed                  |    |

|               | Structures ( $t_{si}$ =8nm and 5nm) (at constant $V_{GS}$ )                                 | 94 |

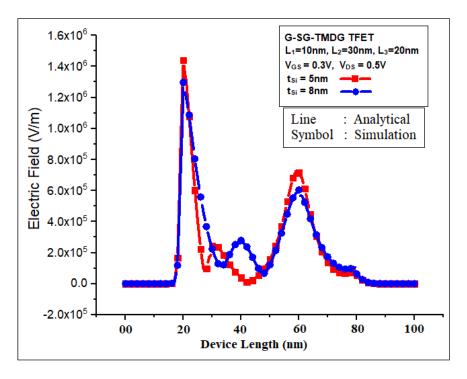

| Fig. 3.3      | The proposed structures' ( $t_{\rm si}$ =8nm and 5nm) electric field profiles               |    |

|               | along their channel lengths for $V_{\text{GS}}\!\!=\!\!1V$ and $V_{\text{DS}}\!\!=\!\!0.5V$ | 95 |

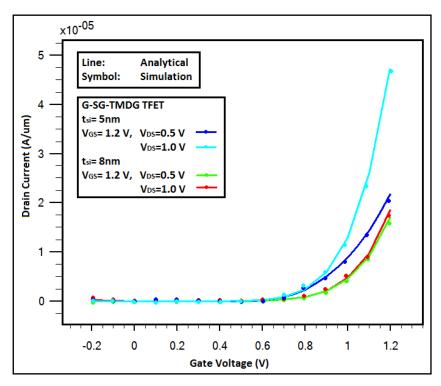

| Fig. 3.4    | $I_{\mathrm{D}}$ - $V_{\mathrm{GS}}$ properties of the suggested device structures                              |     |

|-------------|-----------------------------------------------------------------------------------------------------------------|-----|

|             | (tsi=8nm and 5nm) at constant $V_{\rm GS}$ for various $V_{\rm DS}$                                             | 96  |

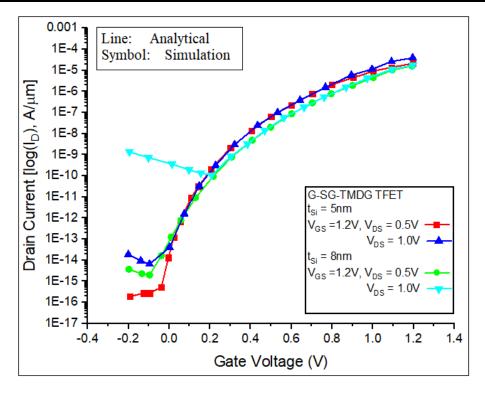

| Fig. 3.5    | Semi-Logarithmic Scale $I_{\text{\scriptsize D}}$ - $V_{\text{\scriptsize GS}}$ Characteristics of the Proposed |     |

|             | Device Structures (tsi=8nm and 5nm) for Varying $V_{\rm DS}$ at Constant $V_{\rm GS}$                           | 97  |

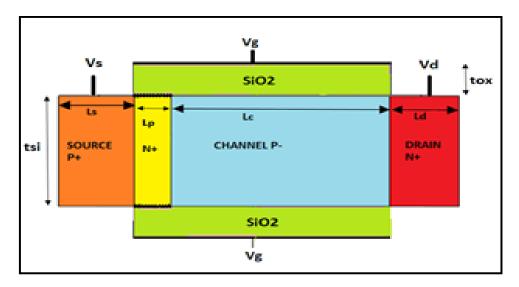

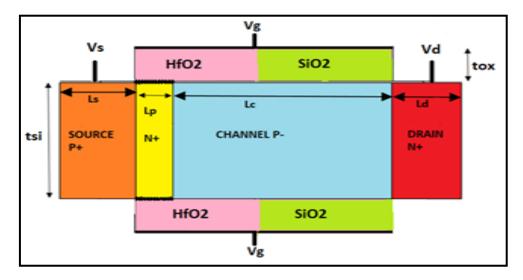

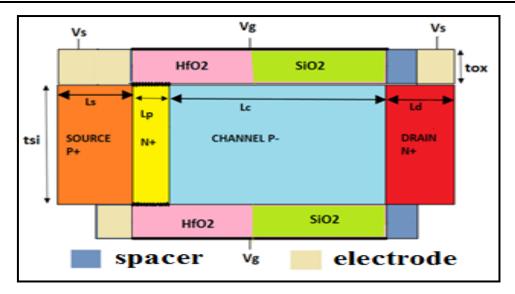

| Fig. 3.6(a) | Double gate p-n-p-n TFET device cross-section (SiO <sub>2</sub> as gate oxide)                                  | 98  |

| Fig. 3.6(b) | Double gate p-n-p-n TFET device cross-section (hetero oxide                                                     |     |

|             | as gate oxide)                                                                                                  | 98  |

| Fig. 3.6(c) | Double gate p-n-p-n TFET device cross-section (hetero gate oxide                                                |     |

|             | and spacer induced)                                                                                             | 99  |

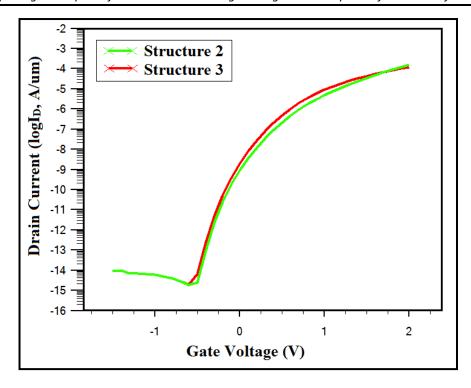

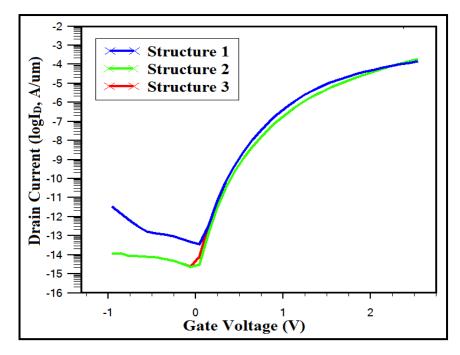

| Fig. 3.7(a) | $I_D\text{-}V_{GS}$ Characteristics of One-sided spacer induced p-n-p-n TFET                                    |     |

|             | and two-sided spacer induced p-n-p-n TFET (spacer: HfO <sub>2</sub> )                                           | 105 |

| Fig. 3.7(b) | $I_{D}\text{-}V_{GS}$ Properties of conventional p-n-p-n TFET and one-sided and                                 |     |

|             | two-sided spacer induced TFETs (spacer material: HfO <sub>2</sub> )                                             | 105 |

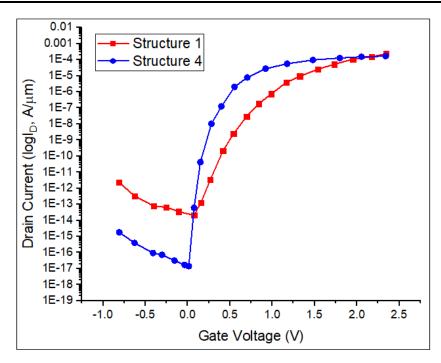

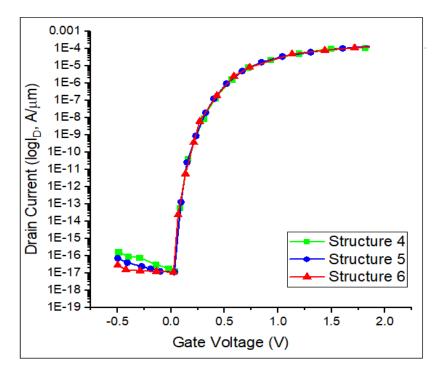

| Fig. 3.8(a) | $I_{D}\text{-}V_{GS}$ properties of p-n-p-n TFET and p-n-p-n TFET hetero-gate oxide                             | 107 |

| Fig. 3.8(b) | $I_D\text{-}V_{GS}$ properties of p-n-p-n TFET with hetero-gate oxide and                                       |     |

|             | hetero-gate oxide p-n-p-n TFET with spacer                                                                      | 107 |

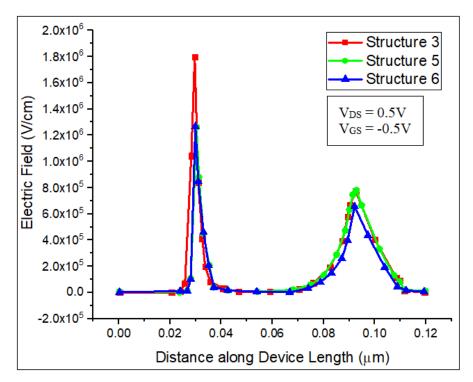

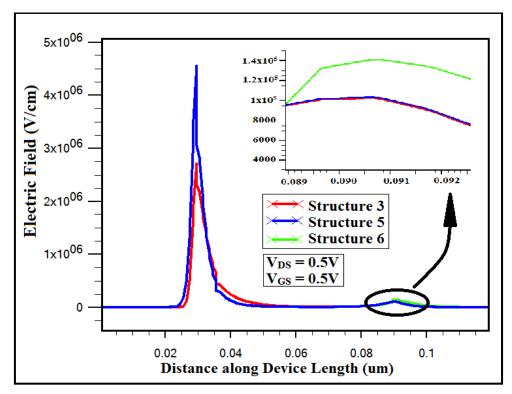

| Fig. 3.9(a) | The suggested structures 3, 5, and 6's electric flux density profile                                            |     |

|             | in reverse tunnelling mode                                                                                      | 108 |

| Fig. 3.9(b) | The proposed structures 3, 5, and 6 have electric field profiles while                                          |     |

|             | they are in forward tunnelling mode. Figure's inset displays the Field                                          |     |

|             | intensity at the Channel-Drain Junction                                                                         | 109 |

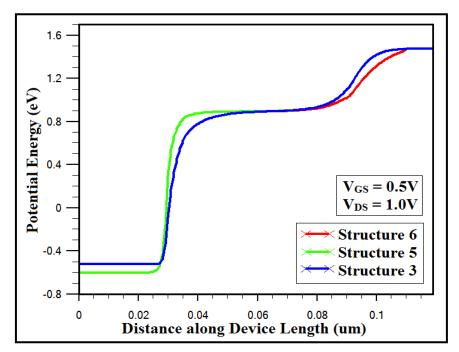

| Fig. 3.10   | The suggested structures 3, 5, and 6 have surface potential profiles at                                         |     |

|             | $V_{GS}$ = 0.5V and $V_{DS}$ = 1.0V.                                                                            | 110 |

| Fig. 4.1    | 2-Dimension cross-section representation of the proposed                                                        |     |

|             | TMDG-TFET                                                                                                       | 128 |

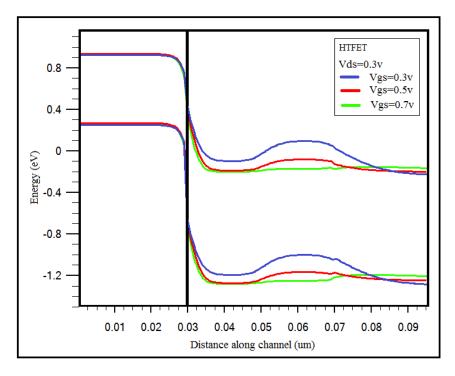

| Fig. 4.2    | HTFET energy band diagram for constant drain voltage with                                                       |     |

|             | various gate biasing                                                                                            | 138 |

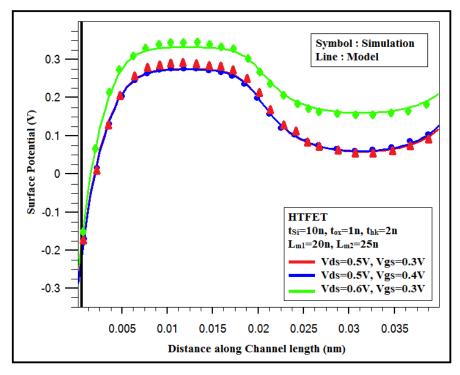

| Fig. 4.3    | Surface Potential profile for various Gate voltages (at constant $V_{DS}$ )                                     |     |

|             | and various Drain voltages over the proposed heterostructure's                                                  | 139 |

|             | channel length ( $t_{si}$ =10nm, $t_{hk}$ =2nm, and $t_{ox}$ =1nm) (at constant $V_{GS}$ )                      |     |

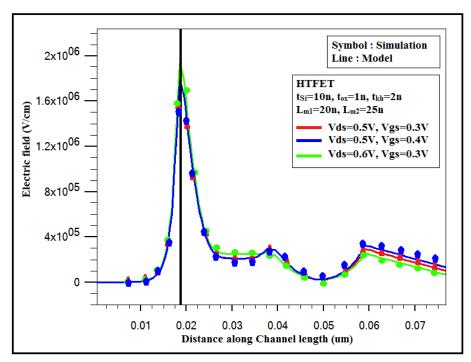

| Fig. 4.4(a) | Electric field profile for different $V_{\text{GS}}$ and $V_{\text{DS}}$ along the proposed                     |     |

|             | heterostructure's channel length ( $t_{si}$ =10nm, $t_{hk}$ =2nm, and $t_{ox}$ =1nm)                            | 140 |

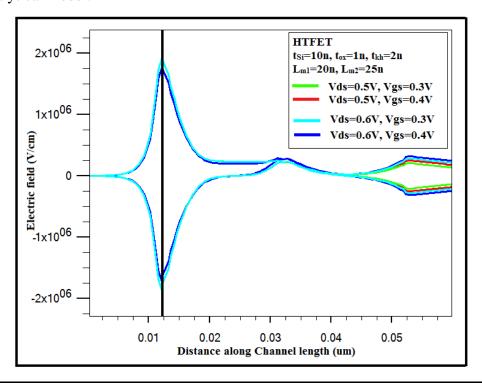

| Fig. 4.4(b) | Comparison of the electric field profile along the proposed                                                     |     |

|             | heterostructure's channel length for different $V_{\rm GS}$ and $V_{\rm DS}$ values                             |     |

|              | $(t_{si}=10$ nm, $t_{hk}=2$ nm, and $t_{ox}=1$ nm)                                           | 141 |

|--------------|----------------------------------------------------------------------------------------------|-----|

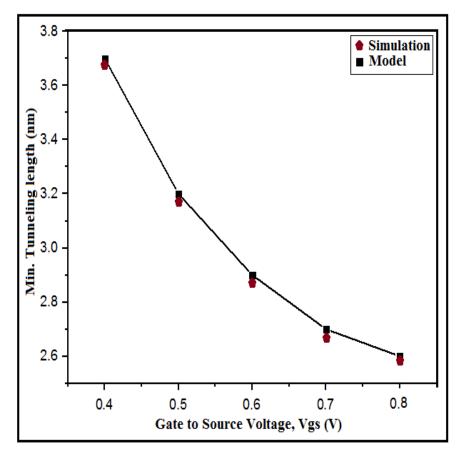

| Fig. 4.5     | Data that was calculated and simulated to show how gate voltages                             |     |

|              | affected the minimum tunnelling length                                                       | 142 |

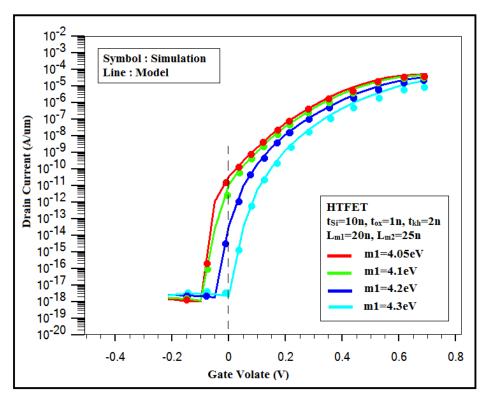

| Fig. 4.6(a)  | $I_{\mathrm{D}}$ - $V_{\mathrm{GS}}$ properties of the suggested HTEF for a constant metal-2 |     |

|              | work function and a variable metal-1 work function (4.6eV)                                   | 143 |

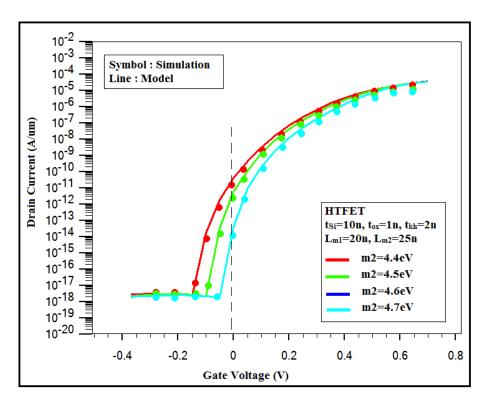

| Fig. 4.6(b)  | $I_{\mathrm{D}}$ - $V_{\mathrm{GS}}$ properties of the proposed HTEF for a constant metal-1  |     |

|              | work function and variable metal-2 work function (4.2eV)                                     | 144 |

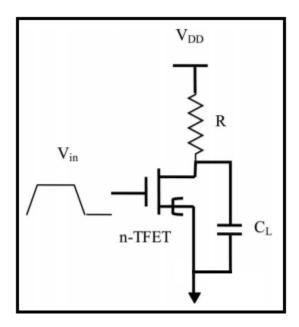

| Fig. 4.7     | Circuit for a resistive load inverter with a suggested HTFET                                 | 146 |

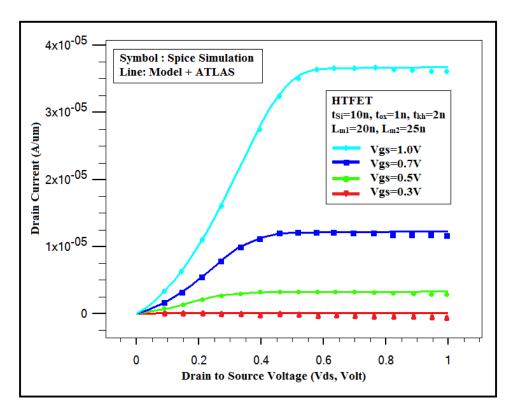

| Fig. 4.8     | Drain characteristics of the proposed HTFET device                                           | 147 |

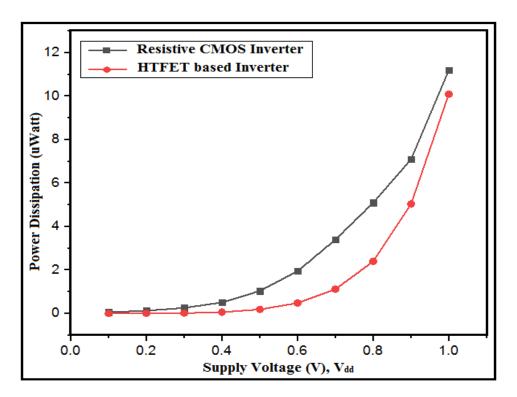

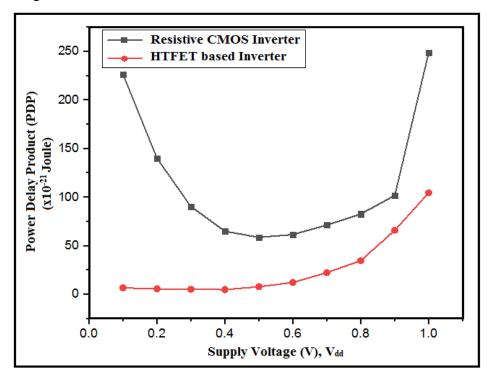

| Fig. 4.9     | CMOS inverter and TFET-based inverter power dissipation                                      |     |

|              | characteristics for a range of supply voltages                                               | 148 |

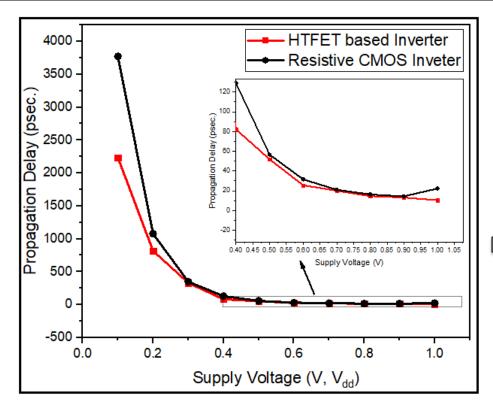

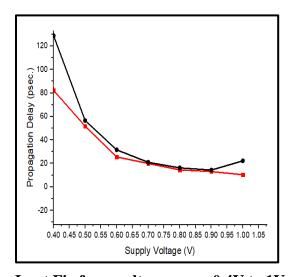

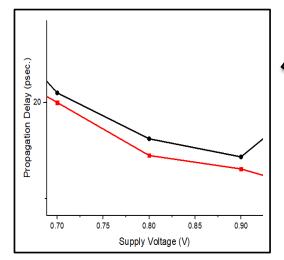

| Fig. 4.10    | CMOS inverter and TFET-based inverter delay characteristics                                  | 149 |

| Fig. 4.11    | Power Delay Product of CMOS inverter and TFET based inverter                                 | 150 |

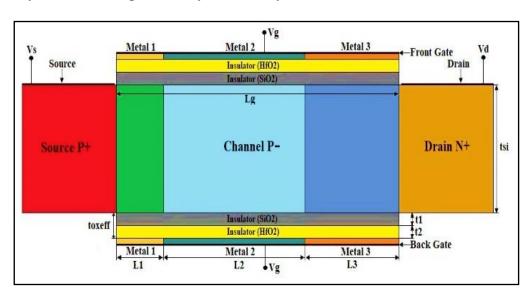

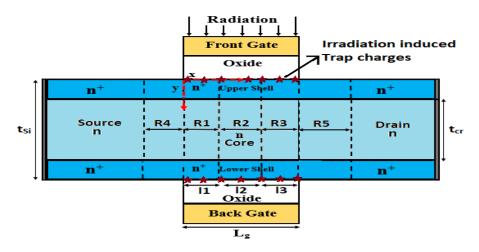

| Fig. 5.1     | View of the Core-Shell double gate junctionless MOSFET                                       |     |

|              | (C-S DGJL MOSFET) structure from a cross-section that has                                    |     |

|              | been subjected to radiation                                                                  | 172 |

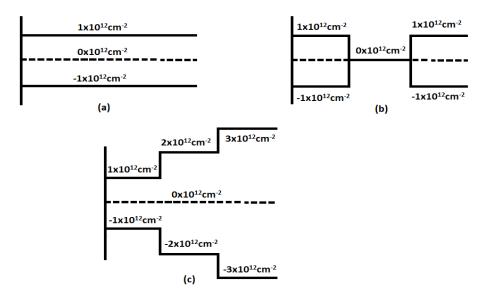

| Fig. 5.2 (a) | Total trap charge density and uniform charge distribution                                    |     |

|              | profile (both positive and negative) (b) non-uniform charge                                  |     |

|              | distribution profile taking into account various total trap charge                           |     |

|              | densities (c) a step profile with a non-uniform charge distribution                          |     |

|              | that takes total trap charge density into account                                            | 173 |

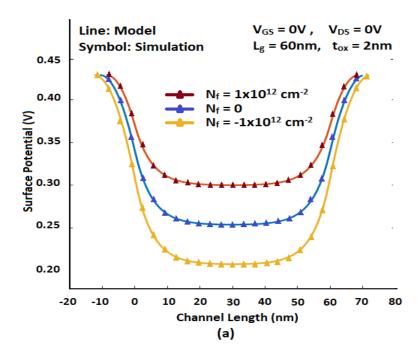

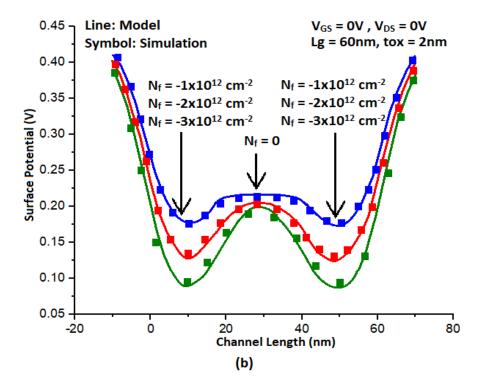

| Fig. 5.3 (a) | Surface potential variation over the length of the channel of the                            |     |

|              | C-S JLDG MOSFET due to uniform trap charge distribution is                                   |     |

|              | shown in Fig. 5.2(a) with the design parameters tsi=10nm, tox=2nm,                           |     |

|              | tcr=8nm, lg=60nm, and Nd=5x10 <sup>18</sup> cm <sup>-3</sup>                                 | 182 |

| Fig. 5.3(b)  | Surface potential variation over the length of the channel of a                              |     |

|              | C-S JLDG MOSFET due to non-uniform trap charge distribution                                  |     |

|              | is shown in Fig. 5.2(b) with design parameters tsi=10nm, tox=2nm,                            |     |

|              | tcr=8nm, lg=60nm, and Nd=5x10 <sup>18</sup> cm <sup>-3</sup>                                 | 183 |

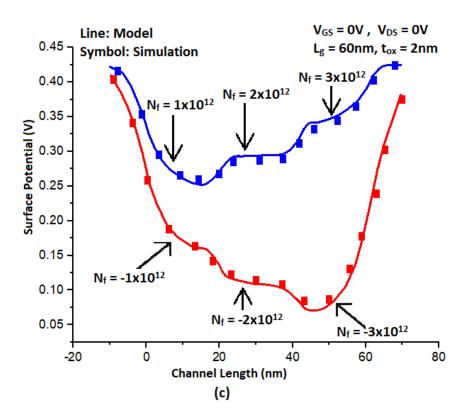

| Fig. 5.3(c)  | Surface potential variation over the length of the channel of the                            |     |

|              | C-S JLDG MOSFET due to non-uniform trap charge distribution                                  |     |

|              | is shown in Fig. 5.2(c) with the design parameters tsi=10nm,                                 |     |

|              | tox=2nm, tcr=8nm, lg=60nm, and Nd=5x10 <sup>18</sup> cm <sup>-3</sup>                        | 184 |

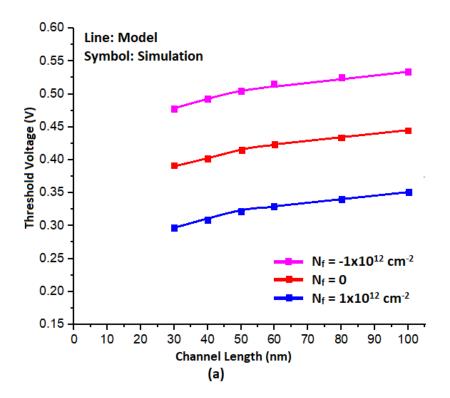

| Fig. 5.4(a)  | Threshold voltage profile along the channel length that incorporates the                     |     |

|              | effects of the trap charge brought about by absorbed radiation doses                                       | 185 |

|--------------|------------------------------------------------------------------------------------------------------------|-----|

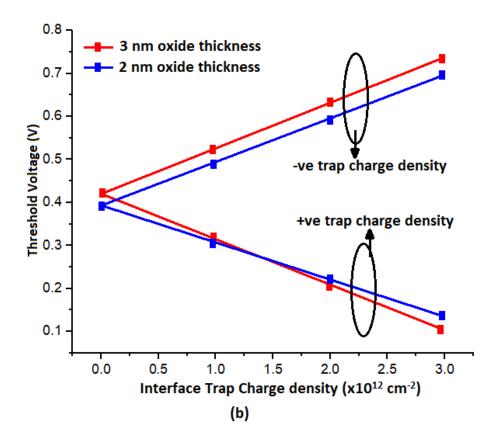

| Fig. 5.4(b)  | Profile of variations of Threshold voltage vs. interface trap charge                                       |     |

|              | densities for two distinct oxide thicknesses                                                               | 186 |

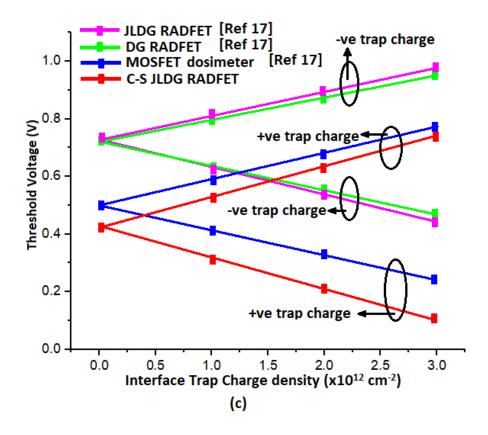

| Fig. 5.4(c)  | Comparison of variations of Threshold voltage profile vs. interface                                        |     |

| <b>G</b> , , | trap charge densities for different devices under consideration                                            |     |

|              | in the article                                                                                             | 187 |

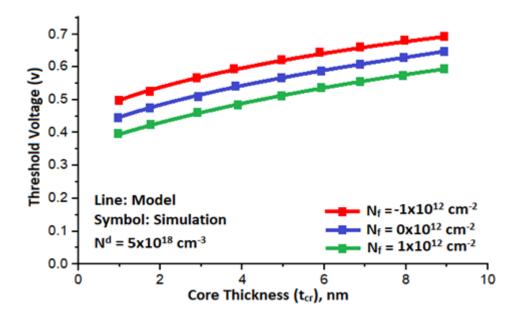

| Fig. 5.4(d)  | Threshold voltage variation profile with $N_d$ doping at $5 \times 10^{18} / \text{cm}^3$                  |     |

|              | in the shell                                                                                               | 188 |

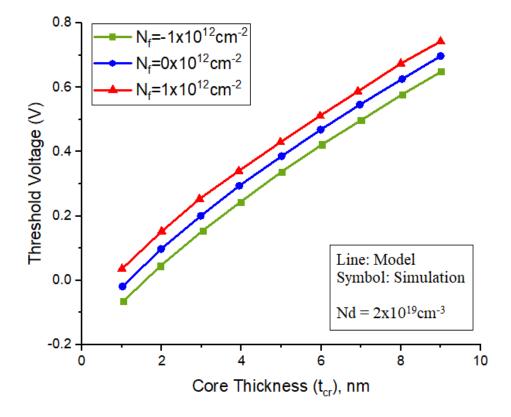

| Fig. 5.4(e)  | Profile of changes in threshold voltage in relation to core thickness                                      |     |

|              | using the Nd=2x10 <sup>19</sup> /cm <sup>3</sup> shell doping                                              | 188 |

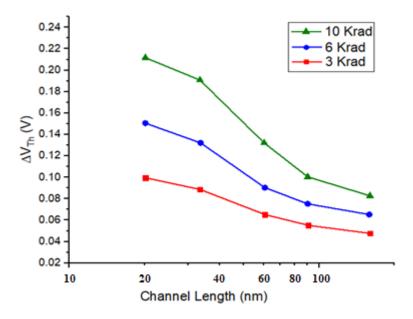

| Fig. 5.4(f)  | Profile showing the threshold voltage shift for devices with varied                                        |     |

|              | gate lengths under the influence of radiation doses                                                        | 189 |

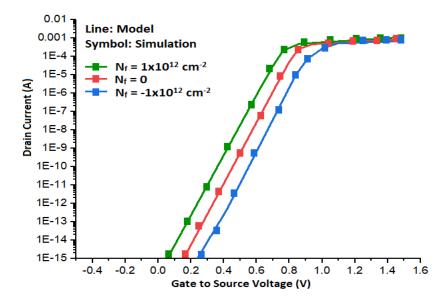

| Fig. 5.5(a)  | $I_{\text{D}}$ – $V_{\text{GS}}$ characteristics of C-S JLDG MOSFET for negative and                       |     |

|              | positive trapped charge concentrations ( $l_g$ =60nm, $t_{Si}$ =10nm, $t_{cr}$ =8nm,                       |     |

|              | $t_{ox}$ =2nm, $N_d$ =5x10 <sup>18</sup> cm <sup>-3</sup> , $V_{gs}$ =0.5V, $V_{ds}$ =1.0V)                | 189 |

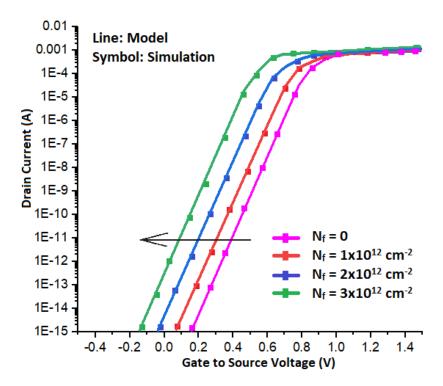

| Fig. 5.5(b)  | $I_{\text{D}}$ – $V_{\text{GS}}$ characteristics of C-S JLDG MOSFET with variation of positive             |     |

|              | trapped charge concentrations ( $l_g$ =60nm, $t_{Si}$ =10nm, $t_{cr}$ =8nm,                                |     |

|              | $t_{ox}$ =2nm, $N_d$ =5x10 <sup>18</sup> cm <sup>-3</sup> , $V_{gs}$ =0.5V, $V_{ds}$ =1.0V)                | 189 |

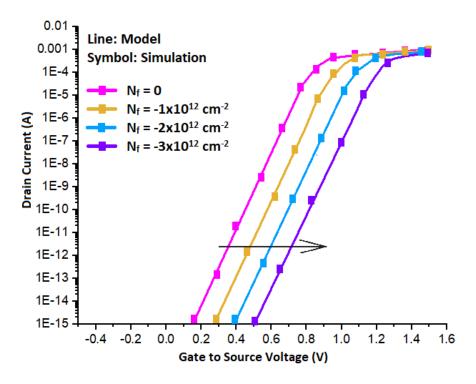

| Fig. 5.5(c)  | $I_{\text{D}}$ – $V_{\text{GS}}$ characteristics of C-S JLDG MOSFET with variation                         |     |

|              | of negative trapped charge concentrations ( $l_g$ =60nm, $t_{Si}$ =10nm,                                   |     |

|              | $t_{cr}$ =8nm, $t_{ox}$ =2nm, $N_d$ =5x10 <sup>18</sup> cm <sup>-3</sup> , $V_{gs}$ =0.5V, $V_{ds}$ =1.0V) | 190 |

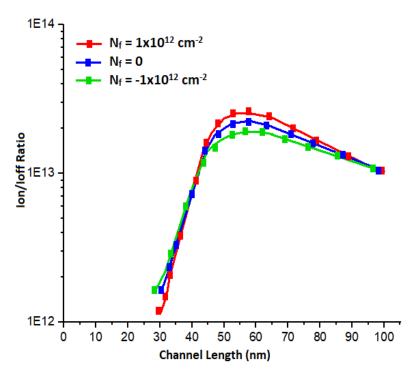

| Fig. 5.6     | $I_{\mathrm{ON}}/I_{\mathrm{OFF}}$ ratio of the suggested device for various trap charge                   |     |

|              | concentrations and channel lengths                                                                         | 191 |

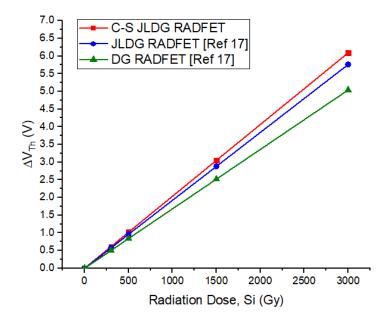

| Fig. 5.7     | Threshold voltage-shift profiles for the C-S JLDG RADFET                                                   |     |

|              | (Proposed Structure), JLDG RADFET [5.17], DG RADFET [5.17],                                                |     |

|              | and calibrated data for the DDGAA RADFET [5.29] and Single gate                                            |     |

|              | RADFET [5.29] were compared against absorbed radiation doses                                               | 191 |

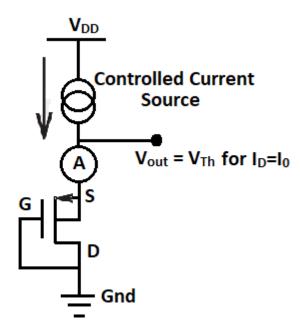

| Fig. 5.8     | Circuit design for the C-S JLDG RADFET's sensitivity measurement                                           |     |

|              | in terms of $V_{Th}$                                                                                       | 194 |

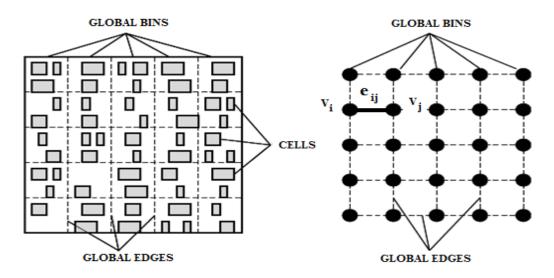

| Fig. 6.1     | Representation of routing region layout in a grid graph                                                    | 219 |

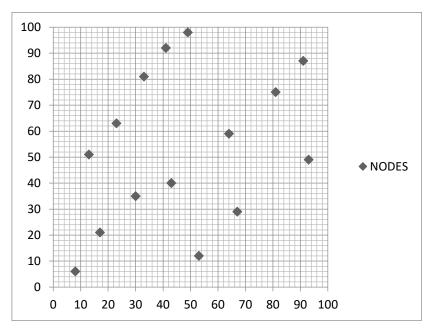

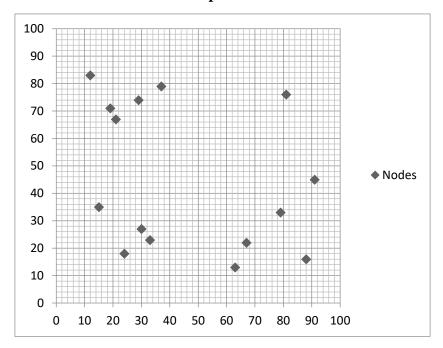

| Fig. 6.2     | SET 1: Nearly Uniform distribution of terminal nodes on                                                    |     |

|              | 100x100 search space                                                                                       | 220 |

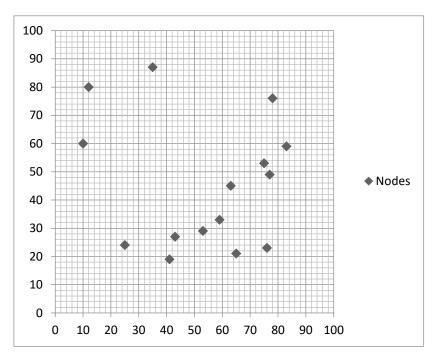

| Fig. 6.3     | SET 2: Clumped distribution of terminal nodes on 100x100                                                   |     |

|              | search space                                                                                               | 220 |

| Fig. 6.4  | SET 3: Bivariate distribution of terminal nodes on 100x100  |     |

|-----------|-------------------------------------------------------------|-----|

|           | search space                                                | 221 |

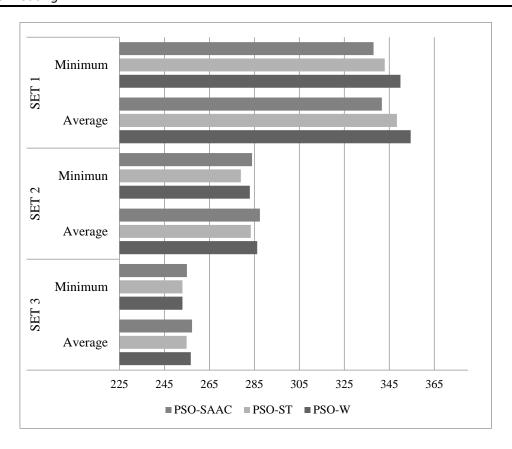

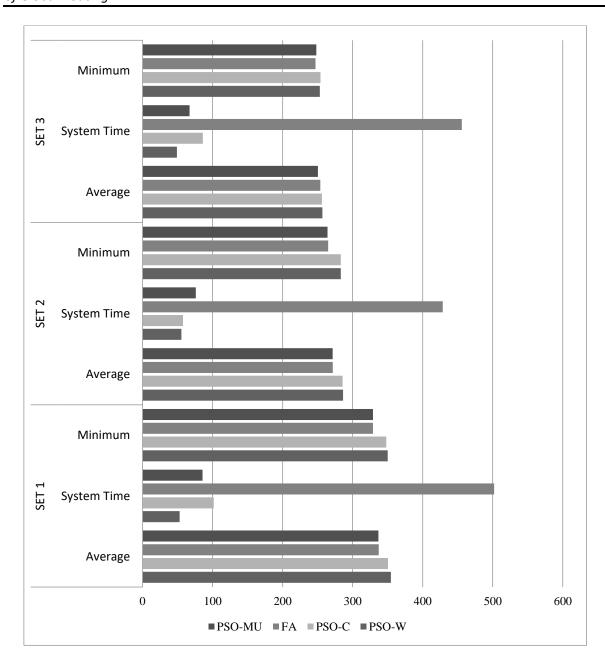

| Fig. 6.5  | Comparison of proposed PSO variants with existing           |     |

|           | PSO-W on varied distribution of terminal nodes              | 222 |

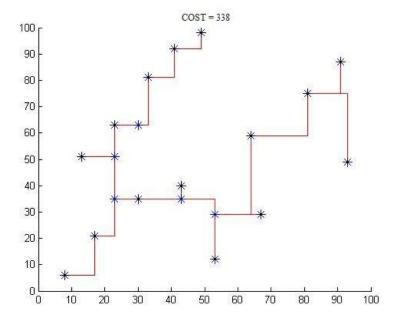

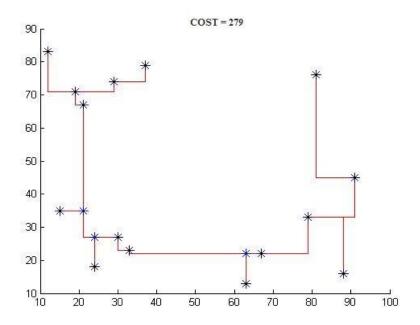

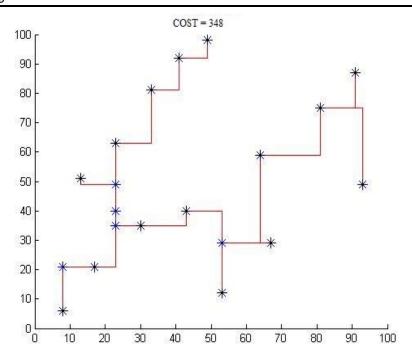

| Fig. 6.6  | Minimum 'cost' Steiner Tree obtained for PSO-SAAC in Set 1  | 222 |

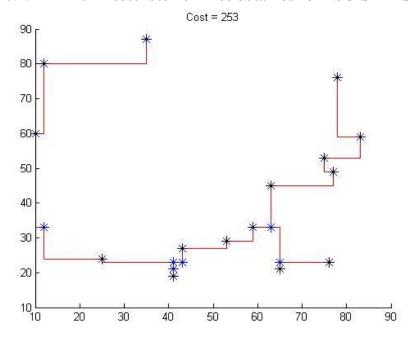

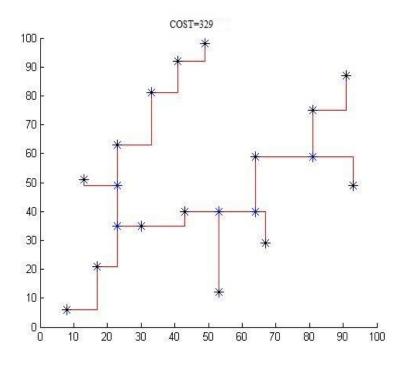

| Fig. 6.7  | Minimum 'cost' Steiner Tree obtained for PSO-ST in Set 2    | 223 |

| Fig. 6.8  | Minimum 'cost' Steiner Tree obtained for PSO-ST in Set 3    | 223 |

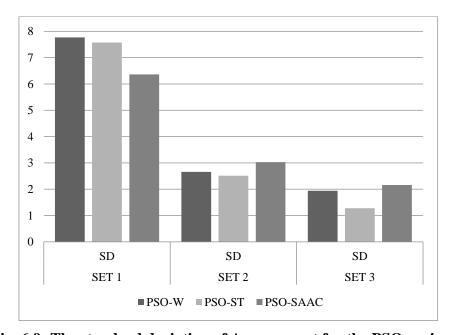

| Fig. 6.9  | The standard deviation of Average cost for the PSO variants | 224 |

| Fig. 6.10 | Minimum 'cost' Steiner Tree obtained for PSO-W in Set 1     | 224 |

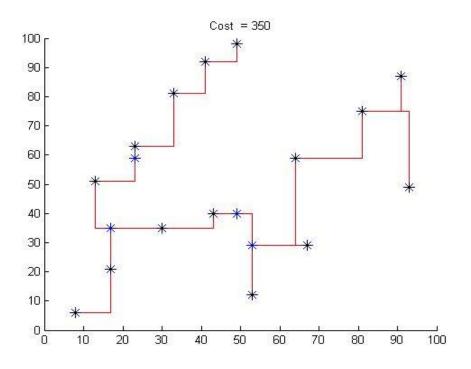

| Fig. 6.11 | Minimum 'cost' Steiner Tree obtained for PSO- C in Set 1    | 226 |

| Fig. 6.12 | Minimum 'cost' Steiner Tree obtained for FA in Set 1        | 226 |

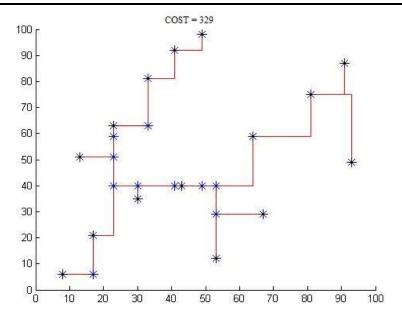

| Fig. 6.13 | Minimum 'cost' Steiner Tree obtained for PSO-MU in Set 1    | 227 |

| Fig. 6.14 | Comparison of proposed PSO-MU with PSO-W, PSO-C, and FA     | 228 |

## List of Tables

| Table No  | Description                                        | Page No. |

|-----------|----------------------------------------------------|----------|

| Table 3.1 | Data for Proposed Model Parameters                 | 88       |

| Table 3.2 | Extracted Parameters of Proposed Structures        |          |

|           | through Simulation                                 | 110      |

| Table 4.1 | Design Considerations for the Suggested Model      |          |

|           | and Simulation                                     | 137      |

| Table 4.2 | Study of Characteristics Parameters for Various    |          |

|           | Body Thickness                                     | 145      |

| Table 4.3 | Study of Parameters for Different High-K Oxide     |          |

|           | Thickness                                          | 145      |

| Table 4.4 | Comparative Analysis of Inverter Characteristic    |          |

|           | Parameters Based on CMOS and HTFET                 | 151      |

| Table 4.5 | Study Comparing Energy Gain                        | 152      |

| Table 5.1 | Design criteria for the suggested model and        |          |

|           | Simulation                                         | 172      |

| Table 5.2 | Comparison of the Performance of Various           |          |

|           | RADFET Dosimeters                                  | 193      |

| Table 6.1 | Comparison of PSO-SAAC with PSO-W and PSO-ST       | 221      |

| Table 6.2 | Comparison of PSO-MU with FA and other             |          |

|           | PSO Variants                                       | 225      |

| Table 6.3 | Standard Deviation of the g <sub>best</sub> Values | 227      |

## List of Abbreviations

VLSI Very Large Scale Integration

ULSI Ultra Large Scale Integration

SOC Silicon-on-Chip

MOSFET Metal Oxide Semiconductor Field Effect Transistor

D-MOSFET Depletion mode MOSFET

E-MOSFET Enhancement mode MOSFET

CMOS Complementary Metal Oxide Semiconductor

FET Field Effect Transistor

SCE Short Channel Effects

DIBL Drain Induced Barrier Lowering

HCE Hot Carrier Effect

SON Silicon-on-Insulator

FD SOI Fully-depleted Silicon-on-Insulator

PD SOI Partially-depleted Silicon-on-Insulator

BOX Buried Oxide

DG Double gate

DM Dual metal

TG Triple gate

GAA Gate-all-around

TFET Tunnel Field Effect Transistor

BTBT Band-to-band tunneling

EOT Effective Oxide Thickness

## CHAPTER 1

## Introduction and Organization of the Thesis

- 1.1. Introduction

- 1.2. Motivation

- 1.3. Literature Review

- 1.4. Organization of Thesis References

#### 1.1. Introduction

The ever-increasing technological demand of modern civilization calls for a tremendous advancement in every sphere of electronic applications, starting from industrial automation to home automation, automobile engineering to satellite communication, wireless communication to Internet-of-Things (IoT), and very precisely day-to-day consumer appliances and portable products. The first transistor was invented by Shockley, Barden, and Brattain in 1947 at Bell Lab [1.1], while the first integrated circuit was created by Jack Kilby at Texas Instruments in 1958 [1.2] posed remarkable impacts over the expansions of modern VLSI/ULSI industries. Integrated circuits, since then, have been the prime driving force behind the development of smart electronics, automated systems with high precision, faster communication systems with commendable security, and so on to quench the need of modern society. Therefore, the worldwide market started tiny, portable, flexible and smart electric goods that urge for low-standby power with high-speed operation. Thus, the ever-ending demand fuelled the realization of a single electronic module with complex functionalities, which entailed amalgamating a mighty number of devices into a single wafer to propel the IC industry from Very Large Scale to Ultra Large Scale Integration era.

Nevertheless, the assiduous demand for complex, multifunctional integrated circuits can only be possible by downscaling the device dimensions and integrating a hefty number of components on a solo piece of substrate. As a result, the dividends are earned in terms of minimum fabrication area and cost, enhanced circuit speed, multitasking ability, enriched packaging density, and minimal power consumption. Moreover, the feature of downscaling reinforced by CMOS technology performs a significant role in ameliorating the device's performances with improved processing speed while optimizing the area, power, and cost per function. Thus, the device scaling acts like a catalyst to uphold the growth of VLSI industries for future generation ultra-low-power, high-performance (speed) integrated circuits [1.3, 4, 5].

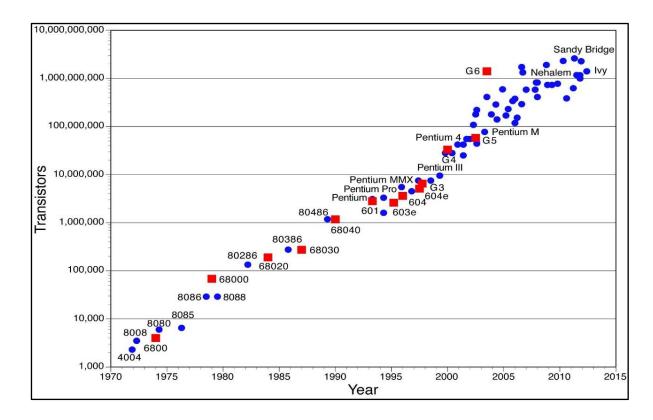

The paradigm shift from microelectronics to nanoelectronics has been possible due to the aggressive scaling of transistors, obeying the famous Moore's law, predicted by G. Moore. In the article "Creaming more components onto integrated circuits" [1.6], published in the electronics magazine of McGraw-Hill publication house, Gordon E. Moore, a co-founder of Intel Corporation, predicted that the number of transistors integrated into a chip will quadruple every two years in April 1965. Later the prediction was set as a target of miniaturization for the VLSI industry, continued shirking of device dimensions to increase the transistor count. Starting with thirty-two transistors integrated on a single chip, the market witnessed 65k components fabricated on the same platform, launched by Intel, after ten years of the forecast (Fig 1.1). The trend has continued, corroborating 14 nm technology in 2020 depicted in Fig 1.2.

Fig1.1: The trend of semiconductor products as per the ITRS roadmap.

Fig 1.2: The trend of technology node speculated by the ITRS roadmap.

Till the late 90s, the threshold voltage ( $V_{th}$ ) and the source voltage ( $V_{DD}$ ) scaled down in proportion to the physical dimension of the semiconductor devices, following fruitfully Dennard's scaling theory proposed in 1974 [1.7]. As a result, the dynamic power consumption is reduced by an order of four times with decreasing supply voltage, only possible through device miniaturization, endorsed by excellent materialistic and electrostatic properties of the dielectric constant, silicon dioxide ( $SiO_2$ ) used in MOSFETs.