# THREE PHASE CONVERTER SYSTEMS FOR ELECTRICAL MACHINES WITH SERIES CONNECTED DC BUS

Thesis submitted by DIPTEN MAITI

**Doctor of Philosophy (Engineering)**

Department of Electrical Engineering

Faculty Council of Engineering & Technology

Jadavpur University

Kolkata, India

2023

### **Index No. 20/16/E**

Title of the Thesis: **Three Phase Converter**

**Systems for Electrical Machines with Series Connected DC Bus**

Name, Designation & Institution

of the Supervisor:

Prof. (Dr.) Sujit K. Biswas

Designation: Former Professor Department: Electrical Engineering Institution: Jadavpur University,

Kolkata, 700032

List of Publications:

- 1. **D. Maiti** and S. K. Biswas, "Three-Phase Open-End Induction Motor Drive Interfaced to Higher Voltage DC Bus," in *IEEE Transactions on Industrial Electronics*, vol. 71, no. 2, pp. 1277-1285, Feb. 2024, doi: 10.1109/TIE.2023.3262874.

- 2. **D. Maiti** and S. K. Biswas, "Series Connected Open-End Winding Generator for Higher Voltage DC Supply," in *IEEE Transactions on Industrial Electronics*, Early Access, doi: 10.1109/TIE.2023.3288207.

List of Patents: NIL

List of Presentations in National/ NIL International/Conferences/Workshops:

## FACULTY OF ENGINEERING & TECHNOLOGY JADAVPUR UNIVERSITY

### "Statement of Originality"

I, Sri Dipten Maiti registered on 27th September, 2016 do hereby declare that this thesis entitled "Three Phase Converter Systems for Electrical Machines with Series Connected DC Bus" contains literature survey and original research work done by the undersigned candidate as part of Doctoral studies.

All information in this thesis have been obtained and presented in accordance with existing academic rules and ethical conduct. I declare that, as required by these rules and conduct, I have fully cited and referred all materials and results that are not original to this work.

I also declare that I have checked this thesis as per the "Policy on Anti Plagiarism, Jadavpur University, 2019", and the level of similarity as checked by iThenticate software is 2%.

Signature of the Candidate:

Date: 22-69-2024

Certified by Supervisor: (Signature with date & seal)

Dr. Sujit K. Biswas Former Professor & Head Department of Electrical Engineering Jadavpur University, Kolkata-700032

22/9/2023

# FACULTY OF ENGINEERING & TECHNOLOGY JADAVPUR UNIVERSITY

#### **CERTIFICATE FROM THE SUPERVISOR**

This is to certify that the thesis entitled "Three Phase Converter Systems for Electrical Machines with Series Connected DC Bus" submitted by Sri Dipten Maiti, who got his name registered on 27th September, 2016 for the award of Ph.D. (Engineering) degree of Jadavpur University is absolutely based upon his own work under the supervision of me, Prof. Sujit K. Biswas, Former Professor, Electrical Engineering Department, Jadavpur University and that neither his thesis nor any part of the thesis has been submitted for any degree/diploma or any other academic award anywhere before.

Prof. Sujit K. Biswas

(Signature of the Supervisor with date & Office Seal)

Dr. Sujit K. Biswas Former Professor & Head Department of Electrical Engineering Jadavpur University, Kolkata-700032 With the advancement in electrical technology, the transmission voltage level is being increased gradually. Usually, the AC voltage generated by conventional generating system is stepped up for transmission and then stepped down for usage at different level. However, power electronic interfaces and renewable energy generation systems have brought a shift in this, although the fundamental idea remains same. The voltage level is still increased for transmission. However, for renewable energy systems which usually are interfaced by power electronic converter for maximum power extraction requires power electronic solution for this voltage stepping up. The solution should be compact, efficient and low cost. Similar is the case for stepping down of the voltage. Thus the power frequency transformer is being replaced by solid state transformers. Multilevel inverters are used for interfacing high DC bus voltage. This reduces the semiconductor breakdown voltage requirement also. The output AC of the inverter is controlled by modulation index of the inverter.

Problem arises when a low voltage AC motor is driven from a higher voltage DC bus. Multilevel inverter being almost a default choice can be utilized with a low modulation index. However, the resulting speed control can become coarse. Besides, the dv/dt may become high for the AC machine winding when the inverter frequency becomes higher. Thus DC to AC better matching inverter is essential.

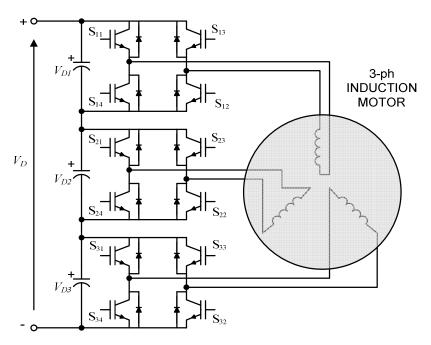

An inverter topology in this direction is proposed and investigated in this work. The DC bus voltage is divided into several smaller parts by capacitive voltage divider, each with its own inverter feeding one phase of the open end winding AC machine. The scheme thus divides the total DC bus into 1/3 and thus results in better voltage matching between the DC and AC sides.

The voltage divider created by capacitors when are loaded can have a unbalance in the voltages. However, present work shows that reasonable balance in the voltage will be maintained inherently by the operation of the motor drive system.

There is chance of zero sequence current due to the open end winding motor and inverter connection. Thus suitable switching strategy should be employed to restrict this

current. This work also investigated in this direction. Using a zero sequence current loop the zero sequence current is kept nearly zero in this work.

Generation of a higher voltage from a low voltage renewable energy generation is a popular topic to the researchers. For wind energy generation, usually offshore ones, requires long cable for transmission, thus higher voltage is more preferred in this case.

Present work proposes a rectifier system for generating higher voltage from a lower voltage generator. The voltage that can be generated is higher than the convention three limb three-phase rectifier with similar voltage boost rating. The extra voltage gain achieved by series connection of the rectifier outputs.

Once again there would be voltage balancing and zero sequence current issues here. These issues are also investigated and mitigating steps are proposed.

Both topologies are simulated on MATLAB SIMULINK tool and then validated experimentally. The voltage balancing, zero sequence current issues are shown and mitigated in software platform as well as hardware implementation.

**ACKNOWLEDGEMENT**

As I am on the course of putting the final touch to the thesis, I would like to

acknowledge the support and inputs from several people, without which, I would not

have reached this far. It is difficult to name them all and thanking them would trivialize

their support. Still, I must try this for the sake of my own self.

I express my deepest sense of gratitude to my research supervisor *Prof. Sujit K*.

Biswas for his guidance, suggestion and encouragement, despite the ups and downs in

his own life. I owe a large part of my life to him. His enthusiasm, energy, and matchless

passion for the subject have always inspired me. I learned and still learning the nuances

of the subject and life as well.

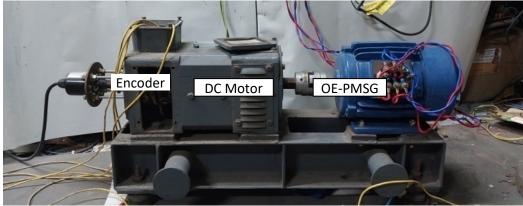

Although beyond the reach of us all, I would like to thank *Late Prof. Nirmal K*.

**Deb** with profound respect. He would have been a very happy person to see this thesis

come to see the light of the day. He helped and encouraged me, whenever I met him. He

designed and the PMSG used for a significant part of the thesis. May his soul rest in

peace.

I would like to thank Mr. Pravat Chandra for his support, suggestion, and

assistance during the fabrication of the experimental set-up. I am thankful to all faculties

and staff especially, Dipankar Naskar, Jayanta Bhattacharya, and Indrajit Naskar of

the Machines and Drives Laboratory of the Electrical Engineering Department for their

assistance.

I would also like to thank my juniors *Diptarshi*, *Koustuv* for their active support

during the experiments.

Last but not least, the moral support and sacrifice of my parents, my wife,

parent-in-laws motivated me to work harder for the realization of the thesis. During the

difficult time of the Covid-related lockdown and the helplessness due to the stagnancy

of my research work, they all stood by me through thick and thin. My daughter

sacrificed her time with her father. I feel indebted to her also.

September, 2023

Jadavpur University,

Kolkata

Dipten Maiti

ix

### Contents

| At  | stract                                                                     | vii  |

|-----|----------------------------------------------------------------------------|------|

| Ac  | Acknowledgement                                                            |      |

| Co  | ntents (This page)                                                         | xi   |

| Lis | st of figures                                                              | xiii |

| Lis | st of tables                                                               | XV   |

| Lis | st of abbreviations                                                        | xvi  |

| 1.  | Review of Topologies and Switching Strategies                              |      |

|     | 1.1. Introduction                                                          | 1    |

|     | 1.2. Converter structures for high voltage operation                       | 3    |

|     | 1.3. Pulse Width Modulation (PWM) Schemes                                  | 6    |

|     | 1.4. Developments in Open End Winding Machine                              | 10   |

|     | 1.5. Review of Series Parallel DC-DC Converters                            | 16   |

|     | 1.6. Other developments related to AC machine interfaced to higher voltage | 17   |

|     | 1.7. Research related to the generation of higher DC voltage               | 17   |

|     | 1.8. Scope and Organization of the thesis                                  | 20   |

| 2.  | Machine modeling for Simulation Study                                      |      |

|     | 2.1. Introduction                                                          | 23   |

|     | 2.2. Induction Machine model                                               | 23   |

|     | 2.3. Permanent Magnet Synchronous Generator model                          | 26   |

| 3.  | Operation of a Lower Voltage Induction Motor from Higher Voltage DC Bus    |      |

|     | 3.1. Introduction                                                          | 29   |

|     | 3.2. Proposed Scheme                                                       | 30   |

|     | 3.3. Output Voltage for the Proposed Topology                              | 32   |

|     | 3.4. Capacitor Voltage Balancing                                           | 33   |

|     | 3.5. Zero Sequence Current Suppression                                     | 37   |

|     | 3.6. Control Circuit                                                       | 38   |

|     | 3.7. Simulation Results                                                    | 40   |

|     | 3.8. Experimental Results                                                  | 44   |

|     | 3.9. Conclusion                                                            | 48   |

| 4.  | Generation of Higher DC Voltage from Lower Voltage AC Generator            |      |

|     | 4.1. Introduction                                                          | 51   |

|    | 4.2. Proposed Scheme                      | 52 |

|----|-------------------------------------------|----|

|    | 4.3. Capacitor Voltage Balancing          | 54 |

|    | 4.4. Performance Evaluation by Simulation | 55 |

|    | 4.5. Experimental Performance Evaluation  | 61 |

|    | 4.6. Conclusion                           | 66 |

| 5. | Conclusion and Future Scope               |    |

|    | 5.1. Overview and Conclusion              | 69 |

|    | 5.2. Scope for Future Work                | 71 |

| 5. | References                                | 73 |

## List of Figures

|                                                                                                                                                                             | Page no |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Fig. 1.1: (a) A single phase AC↔DC Converter (b) A Three phase AC↔DC Converter                                                                                              | 2       |

| Fig. 1.2: (a) Neutral Point Clamped AC↔DC Converter (b) Flying Capacitor AC↔DC Converter                                                                                    | 5       |

| Fig. 1.3: H-bridge AC↔DC Converter                                                                                                                                          | 5       |

| Fig. 1.4: (a) Carrier based Sinusoidal Pulse Width Modulation scheme for 1-phase converter (b) Carrier based Sinusoidal Pulse Width Modulation scheme for 3-phase converter | 7       |

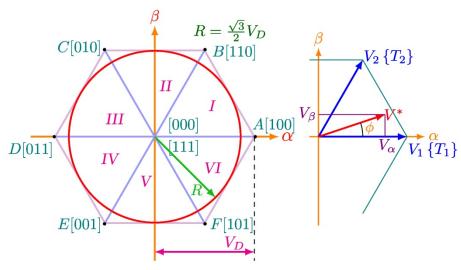

| Fig. 1.5 (a) Space Vector PWM (SVPWM) for a two level 3-phase converter (b) Duty Ratio Calculation for SVPWM                                                                | 8       |

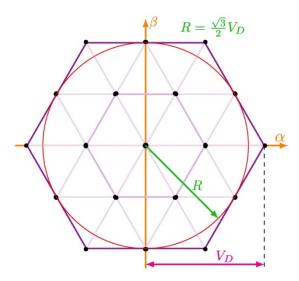

| Fig. 1.6: Space Vector PWM (SVPWM) for a three-level 3-phase converter                                                                                                      | 10      |

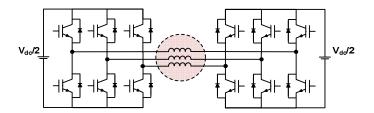

| Fig. 1.7: Open end winding machine with AC↔DC Converter fed by two level converters with isolated DC buses                                                                  | 11      |

| Fig. 1.8: Open end winding machine with AC↔DC Converter fed by two level converters with same DC bus                                                                        | 12      |

| Fig. 1.9: Space Vector PWM (SVPWM) for a three-level 3-phase converter without any zero sequence voltage generating states                                                  | 13      |

| Fig. 2.1: equivalent circuit of the induction machine in d, q, zero axis                                                                                                    | 24      |

| Fig. 2.2: Mathematical equivalent circuit of the PMSG in d, q, zero axis                                                                                                    | 27      |

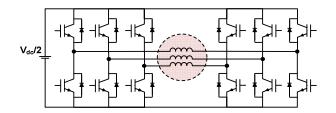

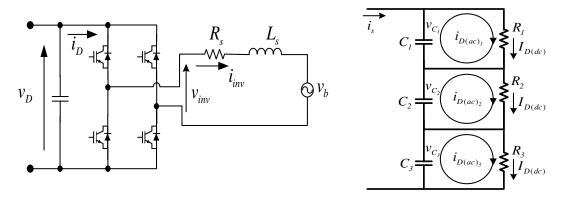

| Fig. 3.1: Proposed Scheme for driving a low voltage motor from higher voltage DC bus                                                                                        | 31      |

| Fig. 3.2 : (a) Per phase inverter circuit configuration with per phase motor winging as load (b) Per phase equivalent circuit from the DC source                            | 34      |

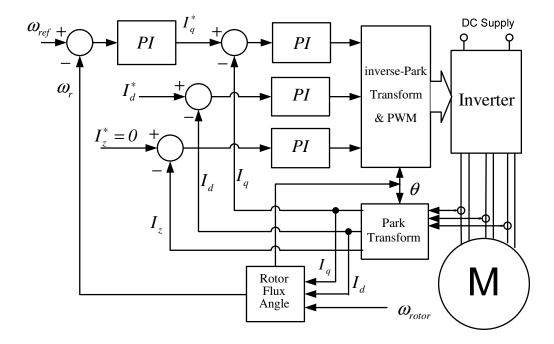

| Fig. 3.3: Field oriented control scheme for the proposed inverter                                                                                                           | 38      |

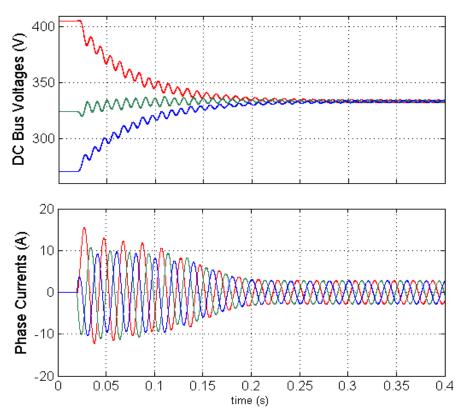

| Fig. 3.4: Capacitor voltage (upper trace) and stator current per phase for DOL starting of the induction motor for the proposed scheme                                      | 40      |

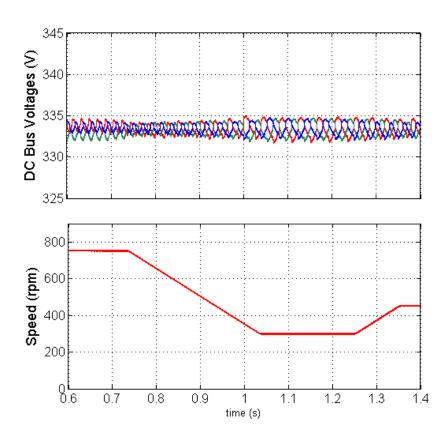

| Fig. 3.5: Capacitor voltage variation with respect to the change in speed of the induction motor                                                                            | 41      |

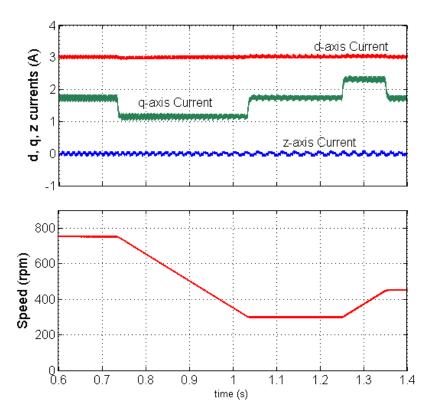

| Fig. 3.6: d, q, zero axis current variation with respect to the change in speed of the induction motor                                                                      | 42      |

| Fig 3.7: capacitor voltage (channel 1, channel 2, channel 3) and one phase current of the induction motor for DOL starting with unequal capacitor per phase                 | 43      |

| Fig 3.8 : Simulated three phase current waveform with and without zero sequence current control                                                                             | 43      |

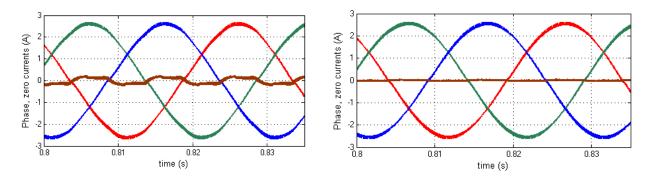

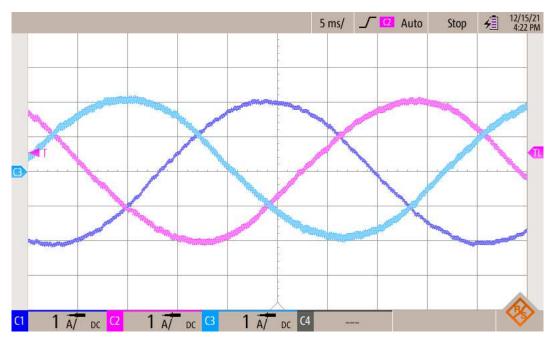

| Fig 3.9: Experimental phase current waveform with and without zero sequence current control                                                                                 | 44      |

| Fig 3.10: Experimental three phase current waveform with zero sequence current control                                                                                      | 45      |

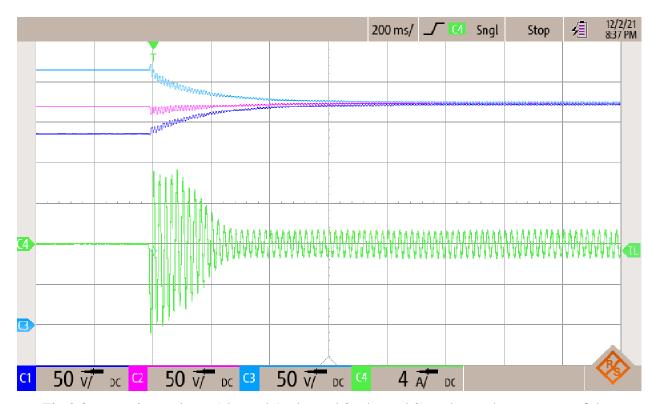

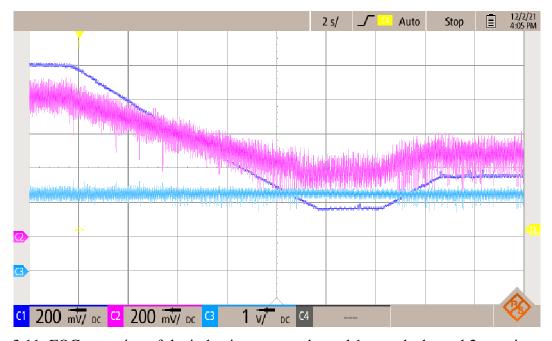

| Fig 3.11: FOC operation of the induction motor; channel 1: speed, channel 2: q-axis                                                                                         | 45      |

| current, channel 3: d-axis current                                                                                                                                                                                                                                |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

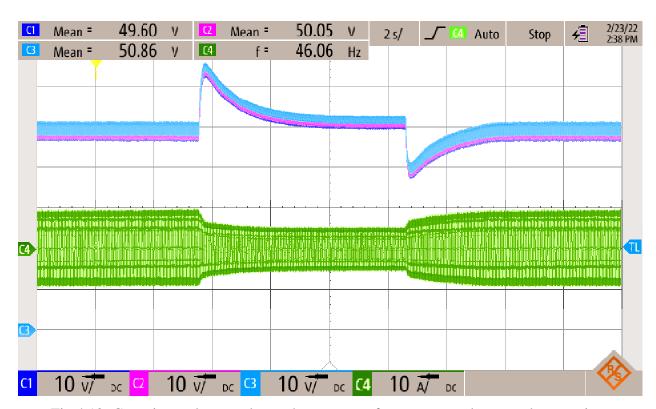

| Fig 3.12: FOC operation of the induction motor; channel 1: one phase current, channel 2, channel 3, channel 4: capacitor voltage for a speed variation                                                                                                            | 46 |

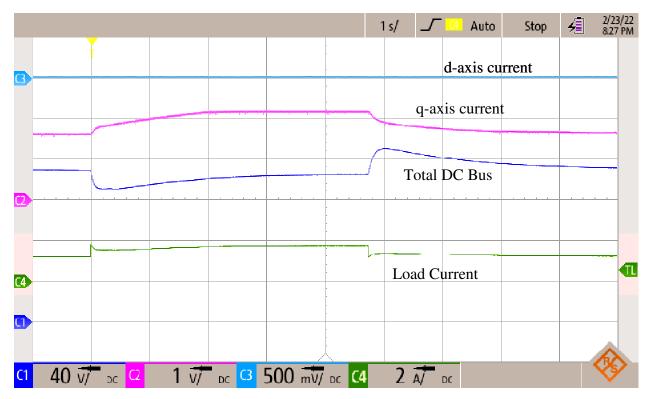

| Fig 3.13: FOC operation of the induction motor; channel 1: speed, channel 2: q-axis current, channel 3: d-axis current, channel 4: change in load current.                                                                                                        | 47 |

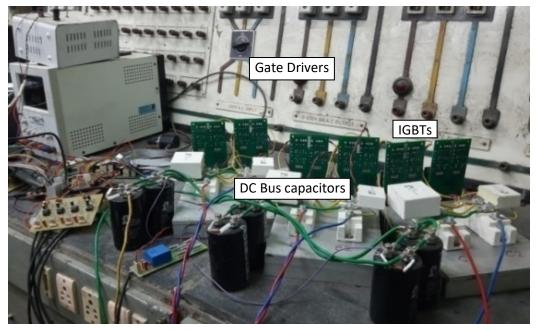

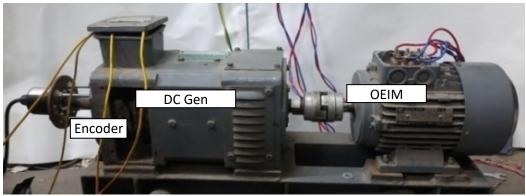

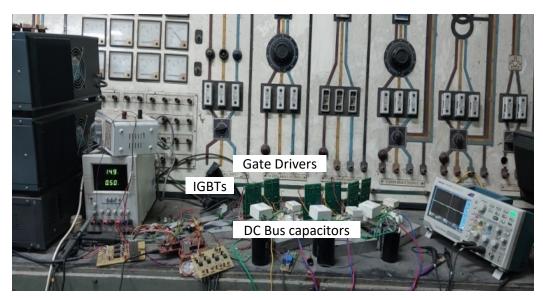

| Fig 3.14: Experimental setup.                                                                                                                                                                                                                                     | 48 |

| Fig. 4.1: Proposed scheme for open end winding PM synchronous generator for medium voltage dc supply                                                                                                                                                              | 52 |

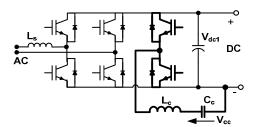

| Fig. 4.2: DC bus double frequency ripple reduction scheme.                                                                                                                                                                                                        | 55 |

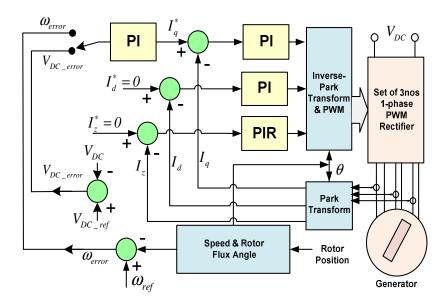

| Fig. 4.3: FOC Control loop structure with a zero sequence current control loop                                                                                                                                                                                    | 56 |

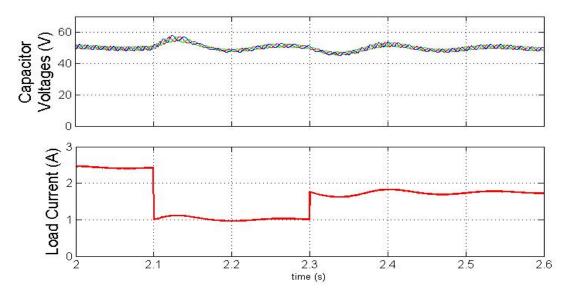

| Fig 4.4: Capacitor voltage variation with change in load current, with a constant voltage operation of the PMSG in the proposed scheme                                                                                                                            | 57 |

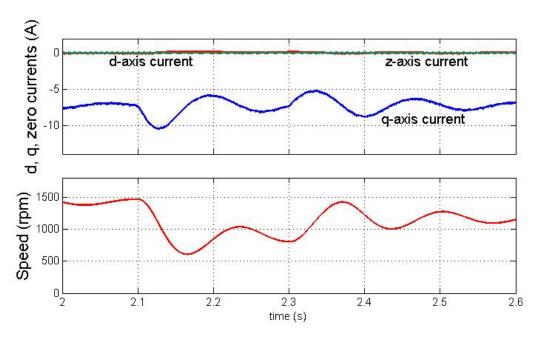

| Fig 4.5: d, q, zero axis current for constant voltage operation of the PMSG                                                                                                                                                                                       | 58 |

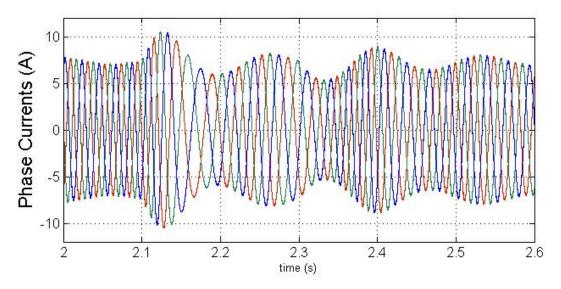

| Fig 4.6: Three phase currents of the PMSG in constant voltage mode of operation                                                                                                                                                                                   | 58 |

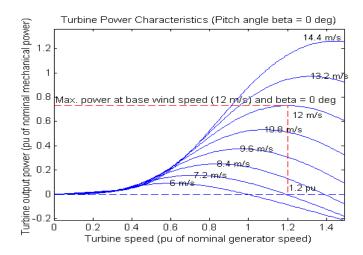

| Fig. 4.7: Power-speed characteristics of wind turbine used for simulation.                                                                                                                                                                                        | 59 |

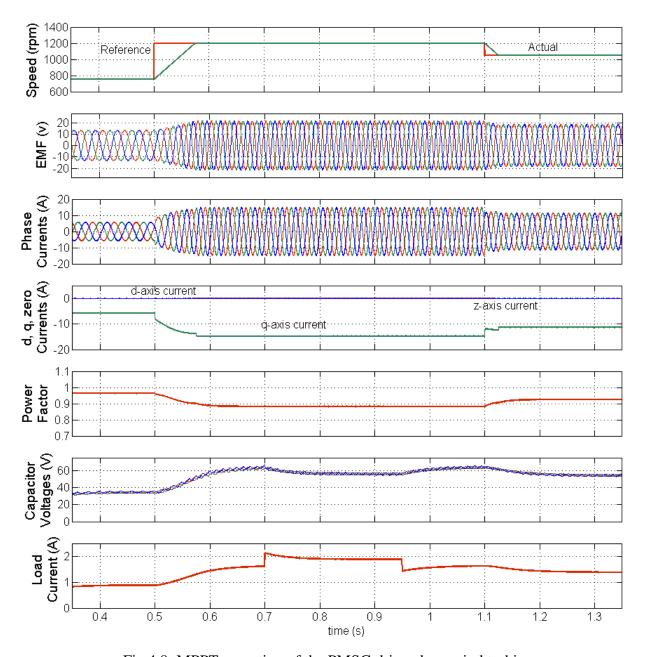

| Fig 4.8: MPPT operation of the PMSG driven by a wind turbine                                                                                                                                                                                                      | 60 |

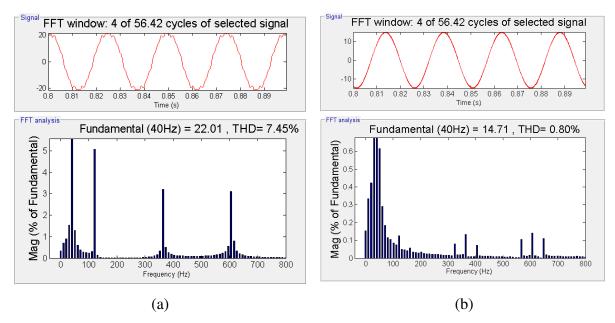

| Fig. 4.9. (a) Induced emf from simulation study and its FFT; (b) Simulated phase current and its FFT                                                                                                                                                              | 61 |

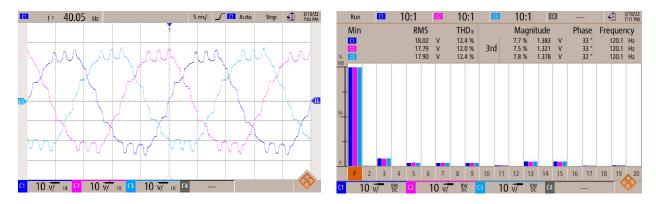

| Fig 4.10: Three phase emfs of the PMSG used for experimentation, FFT of the induced emfs                                                                                                                                                                          | 62 |

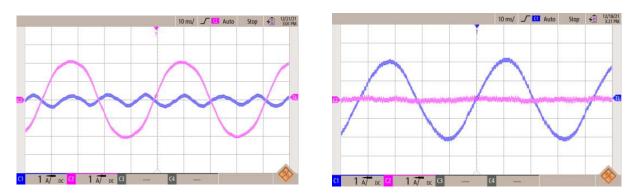

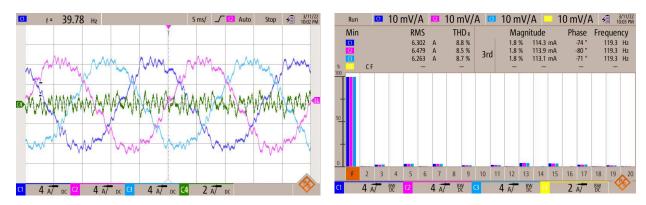

| Fig 4.11: Three phase currents of the PMSG with their FFT                                                                                                                                                                                                         | 62 |

| Fig 4.12: Capacitor voltage and one phase current for constant voltage mode operation                                                                                                                                                                             | 63 |

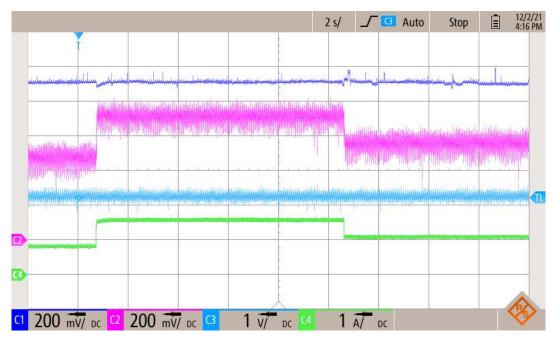

| Fig 4.13: d, q, zero axis currents for a load change in constant voltage mode operation. Channel 1: total DC bus voltage, channel 2: q-axis current, channel 3: d-axis current channel 4: change in load current.                                                 | 64 |

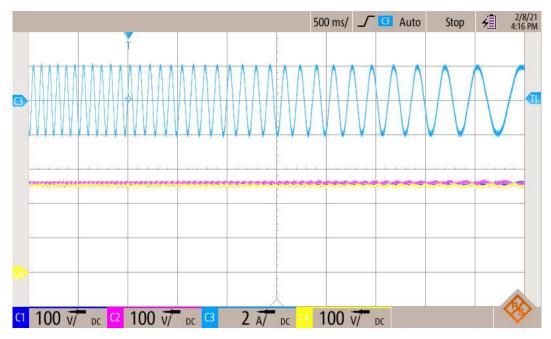

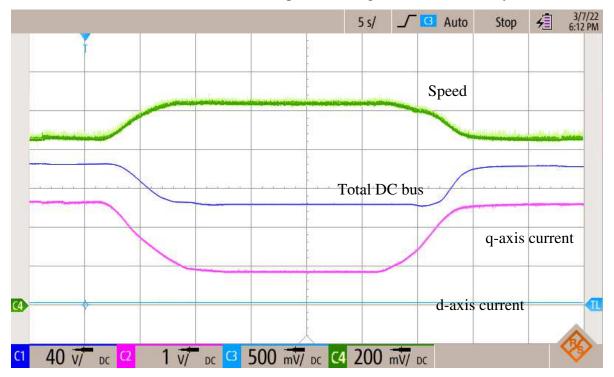

| Fig 4.14: Speed control mode, speed variation from 900 rpm to 1050rpm and back: Ch. 1: Total DC bus voltage (40V/div); Ch. 2: q-axis current from DAC (1V/div); Ch. 3: d-axis current from DAC (0.5V/div); Ch. 4: Speed change from 900 rpm to 1050 rpm and back; | 65 |

| Fig. 4.15. Experimental setup.                                                                                                                                                                                                                                    | 66 |

### List of Tables

|                                                                         | Page no |

|-------------------------------------------------------------------------|---------|

| Table 3.1: Comparison of Proposed Inverter with 3-phase 3-limb Inverter | 33      |

### List of Abbreviations

HVAC High Voltage Alternating Current

HVDC High Voltage Direct Current

SCR Silicon Controlled Rectifier

THD Total Harmonic Distortion

VSI Voltage Source Inverter

VFD Variable Frequency Drive

NPC Neutral Point Clamp

EMI Electromagnetic Interference

IM Induction motor

PMSM Permanent Magnet Synchronous Motor

FOC Field Oriented Control

PWM Pulse Width Modulation

SPWM Sinusoidal Pulse Width Modulation

SVPWM Space Vector PWM

GTO Gate Turn Off Thysristor

OEIM open end winding induction motor

RMS Root Mean Square

OE-PMSG Open end winding Permanent Magnet Synchronous Generator

PMSG Permanent Magnet Synchronous Generator

**MMC** Modular Multilevel Converter **ISOP** input-series-output-parallel **IPOS** input-parallel-output-series **IPOP** Input-parallel-output-parallel **ISOS** input-series-output-series CSI **Current Source Inverters** SST Solid State Transformer DAB **Dual Active Bridge**

ANPC Active NPC

DF Displacement Factor

df distortion factor

DOL Direct On Line

DAC Digital to Analog Converter

# Review of Topologies and Switching Schemes

### 1.1. Introduction

Higher voltage level is popular for the transmission of bulk power [1]. Both High Voltage AC (HVAC) and High Voltage DC (HVDC) transmission systems are used depending upon the requirement, the voltage level of HVDC usually being higher than that of HVAC. Thus, on the generation side a lower voltage is stepped up by using different methods to a suitable higher voltage; on the consumer end the higher voltage is stepped down to a suitable lower voltage level. On the generation end this stepping up has become more important with the availability of lower voltage renewable energy sources. With the availability of high-speed semiconductor devices, the importance has shifted towards more compact, more efficient converters.

The type of AC to DC converter, called rectifier fundamentally consists of diode or Silicon Controlled Rectifier (SCR) bridges for a single phase system [2, 3]. The diode bridge rectifier is an uncontrolled one without any control over the rectified DC output voltage by the converter; while SCR based system has the capability of controlling the output DC voltage by controlling the firing angles of the SCRs. Both diode bridge based rectifier and SCR based rectifier draws non-sinusoidal current from the AC source, causing several detrimental issues on the power supply system as a whole [2, 3].

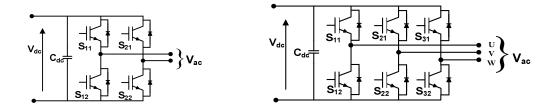

If the diode or SCRs are replaced by force-commutable semiconductor switches and the on-time period of the switches are pulse width modulated at a suitable frequency, current with low Total Harmonic Distortion (THD) can be drawn from the AC source by the converter. The single phase structure consisting of four switches distributed in two legs is as shown in fig. 1.1(a) is also called PWM rectifier. Operated from a single phase AC source this rectifier generates an output voltage greater than the peak of the applied AC voltage. For the operation of this rectifier, an inductor needs to be connected at the AC input. The three phase structure consisting of three

limbs each with two switches is shown in fig. 1.1(b). Here inductors need to be connected in each phase.

Fig. 1.1: (a) A single phase AC↔DC Converter (b) A Three phase AC↔DC Converter

A similar structure can be used for DC to AC conversion or inversion. The DC voltage at the input can be connected to the AC output through suitable switches. With proper switches turned on, the output voltage may be positive or negative. Thus generation of both polarity of the voltage is possible. If the output voltage is to be made free of higher harmonics, a low pass filter may be used. Thus, with a DC source, a suitable switch operation scheme, fig. 1.1(a) becomes a single phase Voltage Source Inverter (VSI) and fig. 1.1(b), a three phase three wire voltage source inverter. For three phase inverter or rectifier the three phase voltage and three phase currents remain 120° displaced from each other.

Two switches connected in series with the emitter of one switch connected to the collector of the other switch, is called a leg/limb of the converter and the common point, that is the connection of the emitter of the top switch and collector of the bottom switch is called the pole. Two legs as combined in fig.1.1(a) is called a full bridge or H-bridge configuration and thus one leg forming half a bridge is called a half-bridge. Three or four legs are there for a three phase converter. A single phase inverter can drive a single-phase AC motor while a three phase inverter can drive a three phase motor in Variable Frequency Drive (VFD) mode with control in both voltage as well as the fundamental frequency. Thus a smooth speed or precise position control is possible with AC motors also.

When the upper switch of leg-1,  $S_{11}$  and bottom switch of leg-2,  $S_{22}$  is turned on, the voltage across the AC side is  $+V_{dc}$ , when the upper switch of leg-2,  $S_{21}$  and bottom switch of leg-1,  $S_{12}$  are turned on, the voltage across the AC terminals or between the poles is  $-V_{dc}$ . When upper switches of both the limbs or lower switches of both the limbs are turned on voltage across the load is zero. It should be mentioned that once a switch is turned on in a leg, the other switch

must be turned off; otherwise, a short circuit across a voltage source may arise resulting in a catastrophe. Besides, because of the non-zero time required for turning on and off of a switch, some delay must be incorporated between the turn off of a switch of a leg and the turn on of a switch of the same leg. This time difference is called dead-time, when both switched of a leg remain turned off.

When one switch of a leg is tuned on the voltage appearing across the other switch is  $V_{\rm dc}$ . Thus the switch must be capable of withstanding this voltage. If suitable switches cannot be found to withstand the voltage, a suitable number of switches can be connected in series with proper voltage balancing, to withstand the higher voltage.

Thus, the pole voltage can have values of  $+V_{dc}$ , 0 and  $-V_{dc}$ . When applied across a load, this will give rise to a rate of change of the voltage or dv/dt. Even in the absence of a conducting path for the pole voltage, this dv/dt may cause current in the associated equivalent capacitance. The dv/dt can be high if the magnitude of voltage change or the DC bus voltage is high or the switching frequency is high. The latter issue indirectly restricts the operating frequency of the switches. The dv/dt issue can be mitigated by using a multilevel converter as the most popular solution.

### 1.2. Converter structures for high voltage operation

High voltage withstand capability can be incorporated into the 2-level converter structures, those shown in fig. 1.1, by series connection of the switches. The series-connected switches require voltage balancing schemes. Besides, the dissimilar turn-on and turn-off time of the switches is to be taken care of. With a multilevel converter structure, these issues could be mitigated. Moreover, the multilevel schemes provide advantages in number of voltage levels generated on the AC side, thus reducing the harmonics in the AC voltage/current and in the size of the low pass AC filter required, along with other significant advantages.

The first multilevel inverter structure was proposed in a 1975 patent utilizing several cascaded H-bridges with their own DC sources, to generate a multi-stepped AC output voltage waveform [4]. Nabae et al proposed the first three level inverter structure, now called Neutral Point Clamped (NPC) multilevel inverter [5]. Diodes were used for connecting to the artificially formed DC bus midpoint, thus it is also called diode clamped multilevel inverter. Here two capacitor banks of similar values are used to form the mid-point of the DC source. Thus the

voltage across each capacitor bank is  $V_{dc}/2$ . Using diodes this midpoint is connected to suitable terminals of a four-switch leg as shown in fig 1.2(a). Normally the switches here are operated in a complementary manner, such that when  $S_{11}$  is on,  $S_{13}$  is held turned off and when  $S_{12}$  is on  $S_{14}$  is kept turned off and vice versa. Thus, by turning on  $S_{11}$  and  $S_{12}$  both, the pole voltage becomes  $V_{dc}/2$ , with  $S_{12}$  turned on pole voltage is 0, and with  $S_{11}$  and  $S_{12}$  both turned off pole voltage is -  $V_{dc}/2$ . Thus, the voltage change in achievable in each level is  $V_{dc}/2$ , which for the same dt gives rise to half dv/dt compared to a full bridge system. Even for the same output current, this reduces the switching loss also.

The blocking voltage requirement of the switches in this case is  $V_{dc}/2$ , half compared to a full bridge converter. Thus, switches with lower voltage ratings can be used for a DC bus with higher voltage. This also results in lower THD in the output voltage when a suitable high switching frequency is used. Besides, due to less dv/dt Electromagnetic Interference (EMI) problem reduces.

Depending on the requirement of total DC bus voltage and availability of switching devices the number of levels can be increased, using further division of the total DC bus voltage. Several converter structures emerged for proposing further development, say, to minimize the number of switches, to increase DC bus utilization, simplify the voltage balancing mechanism, so on.

Another popular modification of the NPC inverter structure shown in fig 1.2(b) is called the flying capacitor multilevel inverter [6] [7]. Several floating capacitors are connected as shown here. Compared to the NPC inverter this topology does not require the clamping diodes, thereby the loss in the diode can be reduced. Further, the redundant switching states can be used to maintain voltages across the flying capacitors  $C_A$ ,  $C_B$ ,  $C_C$ . In this structure shown, the flying capacitors remain charged at half the DC bus voltage and the capacitor voltage can be added or subtracted from the DC bus voltage creating a number of levels in the output AC voltage.

Fig. 1.2: (a) Neutral Point Clamped AC↔DC Converter (b) Flying Capacitor AC↔DC Converter

Fig. 1.3: H-bridge AC↔DC Converter

H-bridge multilevel inverter structure shown in fig. 1.3 uses cascaded H-bridge inverters to form a resultant multilevel inverter. Here each H-bridge has its own DC source, requiring several isolated DC sources [8]. Although the structure requires several switches and isolated DC sources, the structure is simple and does not require complex switching for capacitor voltage balancing as in the case of flying capacitor inverter or extra diodes as in NPC inverter.

The converter structures are popularly used for interfacing AC/DC machines. When used as an inverter to drive suitable AC machines, they are popularly used as VFD, resulting in speed control performance similar to DC motors. This drive scheme is used to drive three-phase Induction motor (IM) and Permanent Magnet Synchronous Motor (PMSM) to name a few, in Field Oriented Control (FOC) mode emulating the non-interfering control of the flux and armature current of a DC motor. Similarly, when used as a rectifier these converters can convert

AC voltage to suitable DC. The rectifier can be used to rectify as when as provide voltage gain when connected to the output of an AC generator.

#### 1.3. Pulse Width Modulation (PWM) Schemes

The switches in any inverter structure are to be controlled in such a way, as to generate the required AC waveform out of the DC source. As the well known bulk power AC motors are mostly driven by sinusoidal AC waveforms for current or voltage, the inverters are usually used to generate sinusoidal AC waveforms. The PWM scheme used for modulating the turn-on time of any switch in a leg of the inverter is required to produce a fundamental AC waveform of a particular amplitude and frequency. With the advent of high speed power semiconductor switches and digital signal processors, the PWM can be performed at a much faster rate. In general, a PWM scheme for an inverter needs to fulfill non-exhaustive requirements such as, a good range of linear modulation, low harmonic content or THD, reduced lower harmonics, the minimum number of pole voltage transitions and simple implementation, etc [2, 3, 9].

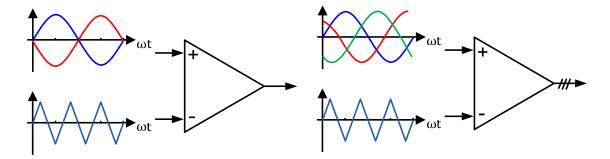

For a single phase 2-level inverter, the most popular PWM scheme is called the Sinusoidal Pulse Width Modulation (SPWM) scheme. This is based on the comparison of a sine wave of required phase, frequency and amplitude with a triangular wave determining the switching frequency as shown in fig. 1.4. Here, one sinewave (say the blue one) is used for generating the switching pulses, the diagonal switches of a single phase H-bridge inverter are turned on and off simultaneously. This operation is called bipolar switching as the output voltage has both positive and negative voltage values in a switching cycle. When two sinewaves, one, the reference sinewave (say the blue one) and another, a of 180 deg phase shifted version (the red one) of the reference sinewave are used for PWM, the operation will be called unipolar SPWM as the inverter output voltage for a half cycle of a reference sinewave remain in the same polarity. The triangular pulse used for comparison is called the carrier waveform, which dictates the switching frequency. For unipolar SPWM the switching frequency harmonics has frequency double that of bipolar SPWM.

Fig. 1.4: (a) Carrier based Sinusoidal Pulse Width Modulation scheme for 1-phase converter (b)

Carrier based Sinusoidal Pulse Width Modulation scheme for 3-phase converter

For a three phase inverter as the three legs of the inverter need to generate 120° phase shifted waveforms, three sinewave references of 120° phase apart are compared with the same carrier waveform to generate the SPWM switching pattern.

The modulation index for SPWM switching is defined as the ratio of the amplitude of the sinewave to the amplitude of the carrier wave, i.e.

$$m = \frac{V_{\sin e}}{V_{triangle}} \tag{1.1}$$

The amplitude of the output voltage for a two level inverter is given by

$$V_{out ac} = m \times V_{dc} \tag{1.2}$$

Thus, the modulation index determines the output amplitude.

Linear modulation range is for  $0 \le m \le 1$ ; for m > 1 the operation is called overmodulation. Usually, overmodulation is avoided except in special cases as it results into the generation of lower harmonics, although the output voltage is higher. For multilevel inverters shifted carriers are used for SPWM or carrier based switching.

For three phase inverter Space Vector PWM (SVPWM) is more popular as it generates less THD with minimum switch transition in a switching cycle. The space vector is the extended idea of the rotating flux vector of a balanced three phase machine. When a three phase machine with its three windings placed 120° apart in space is supplied by currents 120° apart in time, a rotating magnetic field is created. Thus, a fictitious voltage vector can be imagined to have been

created when three such voltages are combined with 120° phase angle difference. A voltage space vector is defined as [9, 10, 11]:

$$\overrightarrow{v_s}(t) = v_a(t)e^{j0} + v_b(t)e^{j2\pi/3} + v_c(t)e^{j4\pi/3}$$

(1.3)

where,  $v_a$ ,  $v_b$ ,  $v_c$  are the instantaneous voltages applied to a, b, c phase windings. The windings should be mechanically apart in space by  $120^{\circ}$  electrical angle.

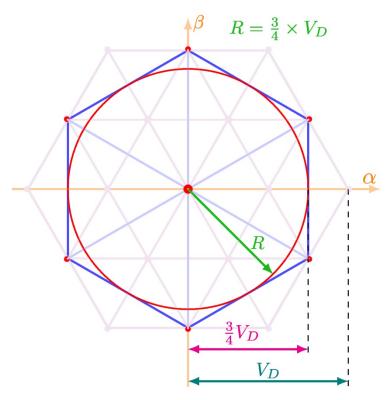

Fig. 1.5 (a) Space Vector PWM (SVPWM) for a two level 3-phase converter (b) Duty Ratio Calculation for SVPWM

As there is a limited number of switches in an inverter, namely six for a three phase inverter, the average voltage in a switching cycle is considered the output of the inverter. Thus, considering all possible switching combinations, i.e.  $2^3 = 8$  possible combination for six switches, eight possible voltage vectors can be generated when switches are fully on for a full cycle. The voltage vectors so generated, when put together with their magnitude and direction form a hexagon shown in fig. 1.5(a) with each vertex representing the of the vector in  $\alpha$ - $\beta$  voltage plane. Here, the part in the third bracket shows the switching states of the upper switches in each limb in order of UVW phases, with '1' representing an on switch while '0' representing an off switch. It should be mentioned that if the upper switch in a leg is on, the bottom switch of the same leg must remain off. The active vectors producing a non-zero voltage, represented by ABCDEF in the fig. 1.5(a) divides the hexagon into six smaller triangular regions, called sectors. The sectors are represented by sector numbers I to VI. The vector with switch states [000] and

[111] i.e. all bottom switches on or all top switches on do not produce any resultant voltage at the output. They are called null vectors and are thus shown at the origin of the space vector diagram. This figure also shows the limit of traversal of the voltage vector. In the linear modulation range, the tip of the voltage vector forms a uniform circle shown in fig 1.5(a). Thus any vector less than this value can be generated by the PWM of the switches where the modulation index is  $\leq 1$ .

The on-time of a switch for SVPWM can be calculated using the voltage averaging principle as shown in fig. 1.5(b). Thus, a reference vector  $V^*$  being applied for the whole switching duration is equivalent to  $V_1$  and  $V_2$  vectors being applied for  $T_1$  and  $T_2$  duration respectively. Thus, it can be written for  $\alpha$ - $\beta$  axis:

$$T_s V^* \cos \phi = T_1 V_1 \cos \left(\theta_1\right) + T_2 V_2 \cos \left(\theta_2\right)$$

$$T_s V^* \sin \phi = T_1 V_1 \sin \left(\theta_1\right) + T_2 V_2 \sin \left(\theta_2\right)$$

(1.4)

Where,  $|V_1| = |V_2| = V_{DC}$ ,  $\theta_1$  and  $\theta_2$  are the angle of  $V_1$  and  $V_2$  with  $\alpha$ -axis respectively. In the case sector I,  $\theta_1 = 0^{\circ}$ ,  $\theta_2 = 60^{\circ}$ . Thus, for sector-I:

$$\frac{T_1}{T_s} = \frac{V_{\alpha}}{V_{DC}} - \frac{1}{\sqrt{3}} \frac{V_{\beta}}{V_{DC}}; \frac{T_2}{T_s} = \frac{2}{\sqrt{3}} \frac{V_{\beta}}{V_{DC}}$$

(1.5)

where,  $V_{\alpha} = V^* \cos \varphi$  and  $V_{\beta} = V^* \sin \varphi$ . In case the reference vector resides within the hexagon,  $T_1 + T_2 \le T_s$ .

Thus, for the rest of the duration i.e.  $T_s - (T_1 + T_2)$ , null or zero vectors will be applied with [000] and [111] being applied evenly such that there are a minimum number if switching in one switching cycle.

The switching pattern is arranged to apply the vectors in sequence,  $V_z \rightarrow V_1 \rightarrow V_2 \rightarrow V_z \rightarrow V_2 \rightarrow V_z \rightarrow V_z \rightarrow V_z$  or reverse, according to the required direction of rotation with time  $T_z/4 \rightarrow T_1/2 \rightarrow T_2/2 \rightarrow T_z/2 \rightarrow T_1/2 \rightarrow T_z/4$  respectively. The dwell time for other sectors can be calculated accordingly. Works have been done to relate carrier base PWM and SVPWM and thus, SVPWM can be generated even without going into the sector determination issues.

The per phase Root Mean Square (RMS) voltage generated by SVPWM switching is given by:

$$V_{rms-phase} = \frac{2}{3}R = \frac{2}{3}\frac{\sqrt{3}}{2\sqrt{2}}V_D = \frac{V_D}{\sqrt{6}} \approx 0.408V_D$$

(1.6)

Here, R is the radius of the circle shown in fig 1.5(a), denoting the boundary of the linear modulation range.

In SPWM, the per-phase voltage that can be generated is given by:

$$V_{rms-phase} = \frac{1}{\sqrt{2}} \frac{V_D}{2} \approx 0.3535 V_D$$

(1.7)

Thus, for the same DC bus, the AC voltage generated can be around 15.5% higher.

For multilevel inverter as the number of switches increase, the number of vectors that can be generated by full on/off of the switches increases. For a three-level NPC inverter, as each leg can have three switching states, the total voltage vector that can be generated are  $3^3 = 27$ . Out of this total 18 are non-null vectors, rest are null vectors, as shown in fig 1.6. In the case of multilevel inverters, null vectors can be utilized for capacitor voltage balancing.

Fig. 1.6: Space Vector PWM (SVPWM) for a three-level 3-phase converter

### 1.4. Developments in Open-End Winding Machine

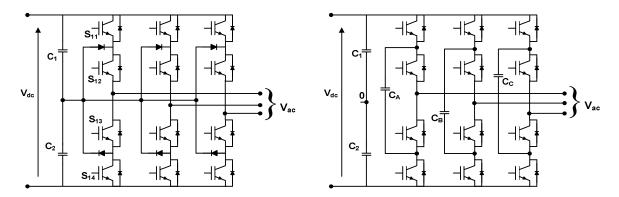

The idea that, an induction motor winding be opened and two sides of each winding be fed from separate inverters was shown to have various advantages. Stemmler et al. first proposed

the open-end winding motor drive configuration for enhancing the maximum power and speed of the Gate Turn Off Thysristor (GTO) based inverter system [12]. Both isolated and non-isolated DC bus systems were discussed. The non-isolated DC bus system employed zero sequence chokes to limit zero sequence current. Another early study on the performance characterization of open-end winding induction motor (OEIM) drive system was published by Corzine et al. [13]. The authors modified the DC bus voltages of the two inverters, to find that the structure can work as two, three, four-level inverters. The open-end inverter for an-open end winding AC machine is easier to construct using three phase inverter modules, compared to NPC inverters, which require clamping diode connections. The capacitor voltage balancing issue of the NPC or flying capacitor inverter was not present here.

Fig. 1.7 shows one such structure with two two-level inverters feeding an open-end winding AC machine from both sides. Although two-level inverters are used on both sides, the resultant voltage across the machine winding becomes equivalent to that supplied by a three-level inverter. Besides, for the same RMS voltage across the AC machine winding, the DC bus voltage required for the two inverter becomes half that of a single three level inverter. Another major advantage is the absence of neutral point fluctuation of the AC machine. Multilevel inverter structures as discussed earlier can be used in place of the two-level inverter, increasing the voltage levels across the AC machine windings.

If the two-level inverters feeding the open-end winding machine are fed by two isolated DC sources, as shown in fig. 1.7, the zero sequence current becomes zero inherently. The zero sequence current is defined as:

$$i_{z}(t) = \left[i_{a}(t) + i_{b}(t) + i_{c}(t)\right] \div 3 \tag{1.8}$$

Where,  $i_a$ ,  $i_b$ ,  $i_c$  are the three phase currents.

Fig. 1.7: Open end winding machine with AC↔DC Converter fed by two level converters with isolated DC buses

Fig. 1.8: Open end winding machine with AC↔DC Converter fed by two level converters with same DC bus

In the absence of the two isolated DC voltage sources, the DC bus of the two-level inverters can be connected, thereby both inverters being fed from the same DC source. All advantages of the open-end winding scheme would be present in this case, except the zero sequence current. In the case of the inverters fed from the same source, there exists a path for the zero sequence current [9-10]. As the zero current causes a stationary flux, the back emf or the induced voltage due to this flux is zero. Thus, in the presence of a zero sequence voltage, the zero sequence current is limited only by the zero sequence impedance of the AC machine. The zero sequence impedance of a machine is usually low, thus there is a chance of high zero sequence current due to a low zero sequence voltage. Besides this causes power loss and torque pulsation, hampering the life of the AC machine. Thus suitable switching scheme should be employed to restrict the zero sequence current in this scheme.

All these inverter topologies when looked at from the output to the input side become rectifiers due to the presence of bidirectional switches. Thus, the rectifiers would be able to generate and withstand higher DC bus voltage. Although, the topologies are similar and similar switch control methods can be employed, interesting developments on this topic happened in the name of multi-level converters [14].

For the structure shown in fig. 1.7, with open-end winding configuration and interfaced by two number two level converters with isolated DC buses, the SVPWM switching states are similar to a three level converter. This is because the structure in fig 1.7 also results in a three-level converter, although the constituent converters are two-level. Besides, the voltage magnitude of each bus for equivalent voltage on the AC side is half that in the three-level structure.

Fig. 1.9: Space Vector PWM (SVPWM) for a three-level 3-phase converter without any zero sequence voltage generating states

If the isolated voltage buses are connected, as in fig 1.8, the zero-sequence voltage generating states are to be removed from the applicable voltage space vectors to nullify zero sequence current. Thus, the space vector diagram results in the one shown in fig. 1.9. As shown in this diagram, the resultant voltage magnitude reduces, along with a number of achievable states. The red circle shows the boundary of linear modulation in this case.

In this case the per phase rms voltage is:

$$V_{rms-phase} = \frac{2}{3}R = \frac{2}{3}\frac{3}{4\sqrt{2}}V_D = \frac{V_D}{2\sqrt{2}} \approx 0.3535V_D$$

(1.9)

which is the same as the voltage generated by SPWM switching scheme. Thus, for the structure shown in fig 1.8, SPWM switching can be performed to have similar voltage modulation, although SVPWM provides definitive minimum switching in a cycle.

Baranwal et al. proposed carrier based SVPWM switching scheme for zero common mode voltage [15]. The maximum voltage for a given DC bus voltage is that given by eq (1.9).

Carrier based SVPWM implementation does not require sector identification, thereby, reducing the processing time.

Open end winding Permanent Magnet Synchronous Generators (OE-PMSG) are studied for generating higher voltage. Each OE-PMSG feeds a diode bridge rectifier. The voltage of each such rectified winding voltage is boosted by boost converters the output of such boost converter is further converted to AC by single phase inverter. The outputs of the single phase inverters are connected in series to generate higher AC voltage [16]. This scheme thus connected multiple Permanent Magnet Synchronous Generators (PMSG) in series to generate higher AC voltage. Yuan et al. proposed a similar scheme, however using multiple segments of each winding [17]. The winding segments are isolated from each other. Thus authors proposed putting the boost output in series to step up the voltage further. Johnson et al. studied the issues when multiple generators are connected in series through rectifier circuits [18]. This study shows that the series connection this way may lead to a violation of operating limits both on the mechanical and electrical side.

Kshirsagar et al proposed operating and open end winding IM from a nine-level inverter [19]. The inverter structure consists of cascaded half bridge limbs as a leg of one side of the three phase inverter. The other side of the winding is fed by a similar inverter producing nine levels at the output voltage. The two sides are fed by four isolated DC sources, which is little difficult to achieve. However, there is no clamping diode as in the NPC inverter of capacitor as required in the flying capacitor inverter.

Different converter combinations can be used for feeding open-end winding machines from the two ends. PMSG system with two-level rectifier on one side and a diode rectifier on the other side has been proposed [20]. Modular Multilevel Converter (MMC) is also used for interfacing open end winding PMSG for wind energy conversion systems [21]. The modularity of MMC is a big advantage besides its suitability in high voltage application.

Kawabata et al. discuss inverter schemes for feeding open end windings machines including transformers for VAr compensators [22]. The authors studied various methods for generating the DC bus voltages for these inverters. As discussed earlier, common mode voltage and current become serious issues when open-end winding machine is fed by converters having linked DC bus. Somani et al. investigated the reasons behind the circulating current in open end

winding machine drive systems with common DC bus [23]. The circulating current is due to the common mode voltage generated in this structure. As the authors suggested, the common mode voltage even when nullified by switching strategy may come from non-linearity such as dead time, device on-time voltage drops, etc, which are inherent to the operation of the converters. The suggested methods to reduce this current are the use of common mode chokes, dead time compensation, etc. Vattuone et al. discuss the background reason for the common mode issues like shaft voltage, ground currents, and bearing currents and suggest the design procedure of a passive common mode filter to mitigate the issues [24].

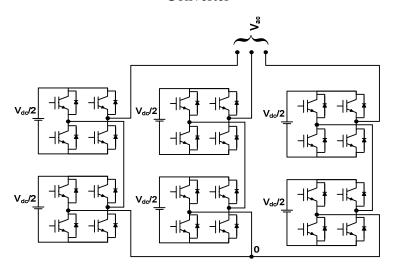

Che et al investigated the operation of a six-phase induction motor from two three-phase inverters to feed the three sets of three-phase windings [25]. The DC buses of the two three-phase inverters are connected in series. The individual DC buses of the two three phase inverters are generated by using a capacitor voltage divider. The two three phase set of currents are converted to four decoupled AC components namely,  $\alpha$ ,  $\beta$ , x, y. The balance of the capacitor voltages is maintained by modifying the x, y components of the current.

One open-end winding PMSG is employed to feed two DC loads from its two ends through two three-phase converter structures. One end of the system drives a three-phase diode rectifier to feed a DC load, whereas on the other end, there is three-phase PWM rectifier charging or discharging a battery [26].

Sensorless control has been extended for open-end winding PMSG driven by a wind turbine. The fragile position sensors required for FOC of the PMSG can be done away with. The sensorless drive scheme for a three phase converter needs to be modified to apply in open end winding scheme [27].

Single-phase AC load can be fed from a three-phase open-end winding PMSG interfaced with three-phase converter structure. The converter involves no low-pass filter. The zero sequence current control and ripple on the output single-phase AC voltage are controlled in  $\alpha$ - $\beta$ -0 coordinate [28].

Thus, open-end winding schemes for interfacing AC machines are popular and relevant for the researchers due their advantages despite having higher number of switches compared to conventional converter structures.

### 1.5. Review of Series Parallel DC-DC Converters

The problem of interfacing high-voltage bus using lower voltage switches can be handled by multilevel inverters or series connection of suitable number of switches to withstand the bus voltage.

A parallel development went on to divide the bus voltage into several smaller voltage buses for smaller converters. The converter inputs are connected in series. Thus the total bus voltage is the sum of the voltages of the converter input buses. The voltage sharing of the converters needs to be taken care of. The initial development happened in terms of input-series-output-parallel (ISOP) DC-DC converters [29]. Capacitors are used to divide the total bus voltage into several sections. The capacitor voltages are measured and using suitable controller input current is regulated such that voltage balance can be ensured. ISOP inverter system has been reported with several h-bridges with their input bus connected in series, the AC side of the h-bridges feeding grid [30]. Thus, input currents of the h-bridges are controlled individually to maintain the input voltage sharing.

While an ISOP divides input DC bus into several smaller buses, input-parallel-output-series (IPOS) combines several smaller DC output in series to provide higher voltage DC [31]. Output-series converters are well-known in the field of DC-DC conversion. They have the advantage of controlling the input current individually to control the output voltage. Work on IPOS inverter control has been reported [32].

Input-parallel-output-parallel (IPOP) and input-series-output-series (ISOS) converter topologies are also studied. All these are static converters being DC-DC or AC-DC or vice-versa systems. However, no study has been reported involving electric machines, i.e. for electric drives. For electrical machines works have been reported with multiple segments of phase winding each with its converter. These converters are connected for higher voltage or current according to the requirements. Although these converters are utilized for DC-DC or DC-AC conversion systems, they are rarely used for AC motor interfacing. In the case of ISOP converters interfacing an AC machine input voltage balance has to be ensured along with output current sharing. Similarly, for IPOS converters interfacing with an AC machine, input current sharing has to be ensured simultaneously with output voltage balancing. In both cases, the

second balancing requirement limits the performance of the first sharing requirement. Thus, there is some scope for investigation.

# 1.6. Other Developments related to AC machines interfaced to higher voltage

AC motors driven by Current Source Inverters (CSI) are popular due to their inherent controlled current capability, eliminating the chance of over-current, which is a risk in a VSI [33-34]. When an AC motor is driven by CSI, the driving inverters can be made 1-phase, connected in series on the DC side, such that the total voltage applied is divided across the component inverter [31-32]. The constant current drawn from the DC bus by each 1-phase CSI can be either bypassed or permitted through the respective stator phase windings of the 3-phase motor to control the motor. This utilized the reliability of a CSI in terms of inherent short circuit/over-current protection while adding the scope of independent switching of the inverter devices with reduced voltage ratings of the semiconductor switches.

Ruseler et al. proposed several h-bridge inverters connected in series on the DC bus side [35]. The AC output of the inverters drives winding segments of a three-phase transformer winding. Thus the AC voltage outputs can be connected in series or parallel depending on the requirement. The secondary of the transformer is driving a three-phase RLC load simulating an induction motor. As the windings can be segmented to have equal impedance and as the current through the segments are same, the voltage balance of the DC bus capacitors is ensured. AC machine interfaced to higher DC bus voltage is thus, still an area of development. New devices are coming up to cope with this requirement. Some solutions with the existing technology may be considered for further research.

# 1.7. Research related to the generation of higher DC voltage from AC generator

The generation of higher DC voltage has been an area of interest for a long time. This has important audiences in wind generation systems along with many other fields.

In the case of bulk wind energy conversion system, offshore wind generation system is more popular due to the availability of offshore wind resources with higher and steadier wind speed and reduced environmental issues [36, 37]. As space required for offshore wind power systems on the land is negligible, it is beneficial in terms of space savings for human settlement, or other land utilization. Due to the requirement that large power be transmitted over a long distance to the onshore substations, the natural choice is to increase the voltage level of transmission to make the system efficient and economical. The available literature related to this purpose can be broadly classified into HVAC and HVDC transmission with the latter being more popular. In both cases, either the high voltage can be produced by each individual source themselves and then the sources may be connected in parallel for increased power or the sources can be connected in series to produce further higher voltage level [38-39].

Power frequency transformers or autotransformers may be used to provide the required voltage boost, but they are not the preferred choice in off-shore applications due to higher cost, weight and floor space requirement [39]. Solid State Transformer (SST) operating at high frequency with high voltage SiC devices or different multilevel converters reduces the overall size [21, 40].

For smaller generators with lower voltage ratings, mainly the PMSG, the higher DC voltage suitable for transmission can be generated by rectifying the AC voltage and then using a DC-DC voltage boost stage [11, 39, 41] that processes the full power produced by the generators. For achieving higher DC voltage, the outputs of several such DC-DC voltage boost converters powered by individual PMSG can be connected in series [37]. This scheme is well established in the literature as this does not require a DC substation onshore although a voltage balancing scheme is necessary between the DC sources to maintain the DC bus voltage for transmission. However, the rectifier input power factor can be very poor due to the non-sinusoidal input current, preventing extraction of the maximum active power from the generator. To improve the power factor, a front-end PWM converter can be employed, also making the output DC voltage to be higher than the highest peak voltage, helping to increase the DC bus voltage. A significant boost through the PWM converter increases the blocking voltage requirement of the converter switches, often making it difficult for economical commercial implementation. To reduce the blocking voltage of switches, various multilevel DC-DC converter sub-modules may be used [36, 37, 38, 42]. This may be series connected Dual Active Bridge (DAB) converters, which

reduces the voltage rating of each DAB converter [40]. Cascaded H-bridge (CHB) or MMC are also employed due to modular design and lower filter size requirement [21, 43]. Other multilevel voltage source converters namely NPC, Active NPC (ANPC), T-type converters, etc., are also used with multiple segments of generator windings to create high-voltage DC buses using lower voltage devices [36, 21, 42, 43, 44, 45].

Various schemes for the design of wind parks have been suggested by Holtsmark et al. [46]. One option is to rectify the AC outputs of the generators and connect the DC buses of the generator to have a HVDC voltage suitable for transmission to the on-shore substation, where it will connect to the AC grid through the inverter. AC parallel windfarm design is suggested utilizing a transformer for interconnecting several wind generators. The stepped-up AC voltage at the secondary of the transformer is rectified to transmit to the on-shore substation.

The AC outputs of the wind generators can be converted to high DC voltage suitable for transmission using various schemes discussed by Meyer et al [47]. Gjerde et al. proposed converting the AC voltage of several stator winding segments to higher DC voltage and then connecting them in series for higher DC voltage generation [48].

Doubly-fed induction generator is popular in wind generation applications. Soares et al. suggested connecting them directly to form a DC microgrid [49]. Both stator side and rotor side converters are connected to the same DC bus of the microgrid. Besides for higher power operation a diode-bridge rectifier for the stator windings is also suggested.

Beik et al. suggest a new generator configuration with a rotor having both wound-field and permanent magnet [50]. The designed 9-phase generator has an exciter on the rotor also. The output voltage is the phasor summation of the voltage generated by the wound field and permanent magnet.

Zeng et al. proposed the utilization of three-phase PWM rectifiers on the two ends of the open end winding PMSG [51]. The DC bus of the two rectifier systems is further boosted by a DC-DC converter with high-frequency isolation. The outputs of the isolated DC-DC converters are connected in series to generate high voltage. Compared to earlier systems of line frequency transformers to combine the AC voltages for HVAC, this system can produce HVDC voltage directly both by boosting, stepping up and series connection of the voltage sources.

A complete scheme for connecting an open end winding PMSG to the power grid through NPC inverters fed by an HVDC link has been proposed by Vattuone et al [52]. The PMSG voltage is rectified by three-phase diode rectifier on both ends, which is then stepped up by individual conventional boost converters. The outputs of the boost converters are connected in parallel. Simulation results are presented to substantiate the proposal.

Guo et al. suggested using the MMC for converting the AC power of the wind energy system to DC and then several such DC sources can be connected in series to generate HVDC suitable for transmission using submarine DC cable to the onshore substation [42].

Thus, research on the direct connection of offshore wind generators to the power system is still an active subject of interest. Both HVAC and HVDC are popular for power delivery by long-distance cable from offshore generators to onshore substations, with HVDC gaining an edge in recent times.

### 1.8. <u>Scope and Organization of the thesis</u>

This thesis investigates suitable converter topology, control, and the related issues for interfacing an AC machine of lower voltage rating to a higher voltage DC bus. The study as a whole is based on the idea of dividing the higher voltage DC bus into smaller ratings and then individually interfacing the AC machine windings in open-end configuration through suitable converters.

Chapter 2 deals with the mathematical modeling of AC machines in this thesis namely induction machines and permanent magnet synchronous machines. The mathematical models usually considering a star-connected stator, are well discussed in the available literature. However, when the stator windings are opened for open-end winding connection, there is a path for zero sequence current, which is to be considered by the mathematical model.

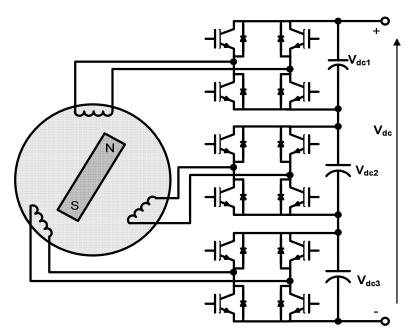

Chapter 3 proposes an inverter structure suitable for interfacing a lower voltage three-phase induction motor to a higher voltage DC bus. The total DC bus is subdivided into smaller DC buses by capacitive voltage dividers, each feeding a single-phase inverter module. The single-phase inverters feed the stator windings of the induction motor. It is shown that the capacitor voltages remain balanced inherently.

Motoring operation also calls for a regenerative mode of operation. This has been dealt with in chapter 4. Instead of limiting to the regenerative operation only, this chapter deals with the issues in operating a lower voltage AC generator to generate a much higher voltage DC bus. Due to the presence of a low impedance path of zero sequence current without a back-emf, suitable generators for this operation are those, which generate sinusoidal voltage. Thus, PMSG is a good choice for this discussion. The PMSG stator winding is connected in an open-end winding configuration, each feeding a single-phase PWM rectifier, generating much higher DC bus voltage from a lower stator winding voltage rating. The operation, control, and voltage balancing issues have been discussed in this chapter.

Finally, chapter 5 considers the scope for future work, to improve upon the configurations discussed in earlier chapters.

Overall, the thesis attempts to study the proposition of dividing a higher voltage DC bus into smaller DC buses, those interfacing phases of an open-end winding AC machine through an AC $\leftrightarrow$ DC converter. The proposed configurations including the AC machines are simulated using MATLAB SIMULINK. These are also verified experimentally. The machine parameters used for simulation and experimental studies are provided at the end of chapters 3 and 4.

Page intentionally left blank.

# Machine modeling for Simulation Study

#### 2.1. Introduction

The mathematical models of the electrical machines under study are to be developed for software simulation of these machines with the interfacing converters. 3-ph open winding Induction motor and an open winding PMSG are used for two studies in this work. Their mathematical models are discussed in this chapter. Here the standard two-axis models are augmented by the zero sequence network of these machines.

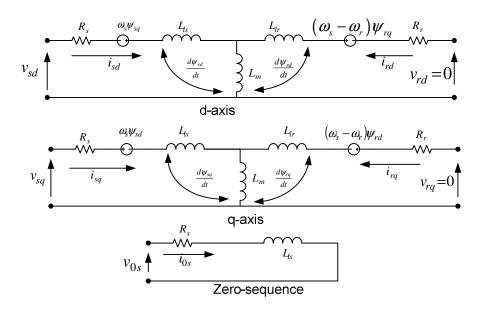

#### 2.2. Induction Machine model

The 3-phase voltage applied across the induction motor stator winding is first converted from dependent three-axis quantity to independent 2-axis namely  $\alpha$ ,  $\beta$  and zero sequence quantity by Clarke Transformation given by:

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \\ v_{0} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -1/2 & -1/2 \\ 0 & \sqrt{3}/2 & \sqrt{3}/2 \\ 1/2 & 1/2 & 1/2 \end{bmatrix} \begin{bmatrix} v_{a} \\ v_{b} \\ v_{c} \end{bmatrix}$$

(2.1)

Here,  $v_a$ ,  $v_b$ ,  $v_c$  are the voltage across the three windings of the IM. The transformed voltage on  $\alpha$ ,  $\beta$  are orthogonal to each other, but they are sinusoidally varying similar to  $v_a$ ,  $v_b$ ,  $v_c$ .

These sinusoidally varying quantities are again transformed into steady d-q, zero axis by Prak's Transformation using:

$$\begin{bmatrix} v_{sd} \\ v_{sq} \\ v_{0s} \end{bmatrix} = \begin{bmatrix} \cos \theta & \sin \theta & 0 \\ -\sin \theta & \cos \theta & 0 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} v_{\alpha} \\ v_{\beta} \\ v_{0} \end{bmatrix}$$

(2.2)

Here,  $\theta = \omega_s t$  is the angle of the flux vector with respect to axis of the A-phase winding. The calculation of  $\theta$  is different for depending on the selection of the flux vector. In case of IM, there are three flux vectors to work with. Depending upon the requirement any one of them can be selected. Rotor flux axis is the most popular reference frame. Thus, for a rotor flux oriented model the rotor flux vector is considered to be along the angle  $\theta$  and no component of the rotor flux exits in other directions.  $\omega_s$  is the speed of rotation of the selected flux vector, i.e. rotor flux in this case. This is also the synchronous speed of the IM. The generalized d, q, zero equivalent circuit of the induction machine can be represented as in fig 2.1.

Fig. 2.1: equivalent circuit of the induction machine in d, q, zero axis

The rotor flux oriented mathematical model can be derived from the generalized equivalent circuit of the IM with  $\psi_r = \psi_{rd}$  and  $\psi_{rq} = 0$ . The induction motor is modeled using the following equations in the rotor-field oriented reference frame in this study [9, 10, 11].

$$v_{sd} = R_s i_{sd} + \frac{L_m^2 R_r}{L_r^2} i_{sd} + \sigma L_s \frac{di_{sd}}{dt} - \frac{L_m R_r}{L_r^2} \psi_{rd} - \sigma L_s \omega_s i_{sq}$$

(2.3)

$$v_{sq} = R_s i_{sq} + \sigma L_s \frac{di_{sq}}{dt} + \omega_s \frac{L_m}{L_s} \psi_{rd} + \sigma L_s \omega_s i_{sd}$$

(2.4)

$$\psi_{rd} = L_m i_{mr} \text{ and } \frac{L_r}{R_u} \frac{di_{mr}}{dt} + i_{mr} = i_{sd}$$

(2.5)

Here,  $R_s$  = stator winding resistance per phase,  $L_s$  = stator self inductance per phase,  $L_m$  = magnetizing inductance per phase,  $L_r$  = rotor self inductance,  $R_r$  = rotor resistance per phase,  $v_{sd}$  = stator voltage in d-axis,  $v_{sq}$  = stator voltage in q-axis,  $i_{sd}$  = stator current in d-axis,  $i_{sq}$  = stator current in q-axis,  $i_{mr}$  = rotor magnetizing current.  $\Psi_{rd}$  = rotor flux linkage in d-axis and  $\sigma = 1 - \frac{L_m^2}{L_s L_r}$ .

The rotor flux being considered to be aligned along the d-axis of the rotor, rotor flux linkage in the q-axis becomes zero and total flux linkage is along the d-axis of the rotor.

It is well established that for a symmetrical rotor structure, zero sequence current does not produce any back emf or resultant torque. However, this produces a torque pulsation, which is detrimental for the life of shaft. For a given zero sequence voltage the zero sequence current generated can be calculated using the following equation:

$$v_{os} = R_s i_{os} + L_0 \frac{d}{dt} (i_{os})$$

$$\tag{2.6}$$

The developed electromagnetic torque in the rotor filed oriented scheme can be calculated as:

$$T_{e} = \frac{2}{3} \frac{P}{2} \frac{L_{m}}{L_{c}} \psi_{rd} i_{sq} \tag{2.7}$$

Where, P = number of poles of the induction motor

The mechanical speed of the rotor can be calculated as

$$J\frac{d\omega_r}{dt} = T_e - T_l - B\omega_r \tag{2.8}$$

Where, J = moment of inertia of the motor drive system,  $T_l =$  load torque, B = coefficient of friction.

The stator phase currents can be calculated from d-q currents using Inverse Park's Transformation first and then Inverse Clarke's Transformation as given below.

$$\begin{bmatrix} i_{\alpha} \\ i_{\beta} \\ i_{0} \end{bmatrix} = \begin{bmatrix} \cos \theta & -\sin \theta & 0 \\ \sin \theta & \cos \theta & 0 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} i_{sd} \\ i_{sq} \\ i_{0s} \end{bmatrix}$$

(2.9)

and

$$\begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & 0 & 1 \\ -1/2 & \sqrt{3}/2 & 1 \\ -1/2 & -\sqrt{3}/2 & 1 \end{bmatrix} \begin{bmatrix} i_\alpha \\ i_\beta \\ i_0 \end{bmatrix}$$

(2.10)

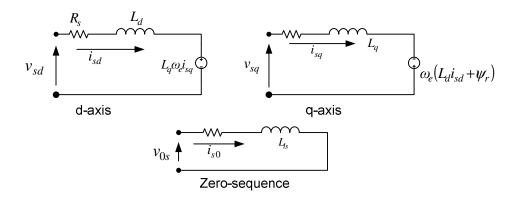

#### 2.3. Permanent Magnet Synchronous Generator model

The PMSG is usually modeled in the synchronously rotating reference frame which is also the rotor field oriented reference frame in case of a PMSG [9, 10, 11, 53].

$$v_{sd} = R_s i_{sd} + L_d \frac{d}{dt} (i_{sd}) - \omega_e L_q i_{sq}$$

(2.11)

$$v_{sq} = r_s i_{sq} + L_q \frac{d}{dt} (i_{sq}) + \omega_e (L_d i_{sd} + \lambda_{1r})$$

(2.12)

$$v_{os} = r_s i_{os} + L_0 \frac{d}{dt} (i_{os}) + 3\omega_e \lambda_{3r} \sin(3\theta_r)$$

(2.13)

where,  $v_{sdb}$   $v_{sqp}$   $v_{os}$  are the d-axis, q-axis and zero axis voltage components respectively. They are obtained from the voltages applied across the stator winding by Clarke and Park's Transformations as in equations (3.1) and (3.2). In case of PMSG the angle for Park's Transformation and  $\theta_r = \omega_e t$  is the electrical angle subtended by the rotor with respect to stator A-phase wingding axis. Thus information about the position of the rotor axis is essential. The corresponding components of currents are  $i_{ds}$ ,  $i_{qs}$ ,  $i_{0s}$  respectively.  $R_s$  is the stator winding resistance and  $L_0$  is the zero sequence inductance while  $L_d$ ,  $L_q$  are d and q-axis self inductance.  $\omega_e$  is the electrical synchronous speed and  $\lambda_{1r}$ ,  $\lambda_{3r}$  are the fundamental and 3rd harmonic component of the rotor flux linkage. There can be other harmonic flux linkages also, depending on the construction of the machine. This generally happens for the Interior PMSGs (IPMSG). The equivalent circuit of the PMSG is shown in fig 2.2.

Fig. 2.2: Mathematical equivalent circuit of the PMSG in d, q, zero axis

The electromagnetic torque produced, can be calculated as:

$$T_{e} = \frac{2}{3} \frac{P}{2} \left[ \psi_{1r} i_{sq} + \left( L_{d} - L_{q} \right) i_{sd} i_{sq} \right]$$

(2.14)

The mechanical speed of the rotor can be calculated as using equation (2.8).

The stator phase current can be found using inverse Park and Clarke Transform in order using equation (2.9) and (2.10).

Page intentionally left blank.

# Operation of a Lower Voltage Induction Motor from Higher Voltage DC Bus

#### 3.1. Introduction

Electric drive technology advanced in diverse applications due to the progress of low-cost digital controller technology with high-speed processing capability [9, 11, 54-56]. According to the consumption of bulk electrical power, the most popular AC drive topologies consist of squirrel cage induction motors driven from PWM VSI, fed from a suitable voltage source DC bus.

Induction motor drive usually requires a matching DC bus voltage. The DC bus voltage must be greater than a minimum value, that can be calculated using eq. (1.9), and theoretically, there is no limit to the maximum DC bus voltage. The inverter uses proper the modulation index to achieve the required AC voltage across the motor windings. In practice, however, if the DC bus voltage becomes much higher, the range of modulation index becomes very low. Thus as the speed control requires a change in modulation index along with the change in frequency, the resolution of the speed control reduces. Thus a crudely matching DC bus voltage is required for the induction motor drive system.

Further, for higher DC buses, the high magnitude voltage pulses, when switched at a high switching frequency, create high dv/dt, rapidly deteriorating the insulation of the motor [57]. The inverter semiconductor devices also have to withstand the high DC bus voltages, resulting in higher costs and higher losses. To mitigate this issue, multilevel inverters can be used which divides the high voltage into multiple voltage levels. However, the restricted range of the modulation index still remains a problem.

#### © 2023 IEEE.

Part of the contents of this chapter has been published in the paper entitled "Three-Phase Open-End Induction Motor Drive Interfaced to Higher Voltage DC Bus," by D. Maiti and S. K. Biswas, in IEEE Transactions on Industrial Electronics, vol. 71, no. 2, pp. 1277-1285, Feb. 2024, doi: 10.1109/TIE.2023.3262874.

The use of an intermediate stage of DC-DC conversion is another solution to match the voltage. Such a DC-DC converter will have a somewhat higher power rating than that of the inverter considering the efficiency involved, and have higher voltage & higher current-rated semiconductor devices, all increasing the cost, size, and weight of the entire system while reducing the efficiency[58].

If the input is derived from an AC voltage source it is possible to use a transformer to implement voltage matching. This also has the disadvantages of higher cost, more space and weight with lower efficiency. As discussed, earlier, a front-end PWM rectifier can be employed instead of a thyristor-controlled rectifier to achieve better Displacement Factor (DF) and distortion factor (df). However, the output DC voltage in this case has to be higher than the highest peak voltage. Such a situation may just aggravate the problem by increasing the DC bus voltage further.

The work presented here proposes to drive each phase of the 3-phase Open-End (Winding) Induction Motor (OEIM) by one 1-phase PWM VSI with the input DC bus of these three inverters connected in series across the available DC bus voltage. Thus, the total available DC bus voltage is split into three equal smaller voltage levels with individual lower voltage-rated single-phase PWM inverters driving each isolated winding. Thus, an IM of a lower voltage rating can be connected to the available higher DC voltage bus through a modification of the inverter topology and the use of open-end winding, without the need for transformers or DC-DC converters. It is shown that the individual DC bus voltage levels remain reasonably balanced in the normal operation of the machine.

### 3.2. <u>Proposed Scheme</u>