# A NEW NON-ISOLATED DC-DC CONVERTER FOR HIGH VOLTAGE BOOST RATIO

Thesis submitted by

## **KOUSTUV SARKAR**

**Doctor of Philosophy (Engineering)**

Department of Electrical Engineering

Faculty Council of Engineering & Technology

Jadavpur University

Kolkata, India

2023

#### **Index No. 08/16/E**

Title of the Thesis: A New Non-Isolated DC-DC

Converter for High Voltage Boost

Ratio

Name, Designation & Institution of the Supervisor:

Name: Prof. (Dr.) Sujit K. Biswas

Designation: Former Professor

Department: Electrical Engineering Institution: Jadavpur University,

Kolkata, West Bengal, India,

Pin 700032

List of Publications:

- 1. **K. Sarkar**, A. Chakrabarti, P. Kasari, B. Das and S. K. Biswas, "Performance Improved Multi-Level OEIM Drive with Voltage Boost through Unequal Levels", *IEEE Transactions on Industry Applications*, Early Access, DOI: 10.1109/TIA.2023.3290574

- 2. A. Chakrabarti, **K. Sarkar**, P. Kasari, B. Das and S. K. Biswas, "A CB-PWM Technique for Eliminating CMV in Multilevel Multiphase VSI", *IEEE Transactions on Industrial Electronics*, Vol. 70, Iss. 9, September 2023, DOI: 10.1109/TIE.2022.3198256

List of Patents:

**NIL**

List of Presentations in National/ International/Conferences/Workshops:

- 1. **K. Sarkar**, A. Chakrabarti, and S. K. Biswas, "A Five-Level Boost NPC Inverter for Electric Vehicle," IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), MNIT Jaipur, India, Dec. 2020, DOI: 10.1109/PEDES49360.2020.9379599

- 2. A. Chakrabarti, **K. Sarkar**, and S. K. Biswas, "Generalized Carrier Based Technique for Eliminating CMV in 3-Phase n-level NPC Inverter," IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), MNIT Jaipur, India, Dec. 2020, DOI: 10.1109/PEDES49360.2020.9379889

# FACULTY OF ENGINEERING & TECHNOLOGY JADAVPUR UNIVERSITY

## "Statement of Originality"

I, <u>Sri Koustuv Sarkar</u> registered on <u>19<sup>th</sup> September</u>, <u>2016</u> do hereby declare that this thesis entitled "<u>A New Non-Isolated DC-DC Converter for High Voltage Boost Ratio</u>" contains literature survey and original research work done by the undersigned candidate as part of Doctoral studies.

All information in this thesis have been obtained and presented in accordance with existing academic rules and ethical conduct. I declare that, as required by these rules and conduct, I have fully cited and referred all materials and results that are not original to this work.

I also declare that I have checked this thesis as per the "Policy on Anti Plagiarism, Jadavpur University, 2019", and the level of similarity as checked by iThenticate software is 1 %.

Signature of the Candidate: Koustv Lukan

Date: 14-09-2023

Certified by Supervisor: (Signature with date & seal)

Dr. Sujit K. Biswas

Former Professor & Head

Department of Electrical Engineering

Jadavpur University, Kolkata-700032

# FACULTY OF ENGINEERING & TECHNOLOGY JADAVPUR UNIVERSITY

#### **CERTIFICATE FROM THE SUPERVISOR**

This is to certify that the thesis entitled "A New Non-Isolated DC-DC Converter for High Voltage Boost Ratio" submitted by Sri Koustuv Sarkar, who got his name registered on 19th September, 2016 for the award of Ph.D. (Engineering) degree of Jadavpur University is absolutely based upon his own work under the supervision of Prof. Sujit K. Biswas, Former Professor, Electrical Engineering Department, Jadavpur University and that neither his thesis nor any part of the thesis has been submitted for any degree/diploma or any other academic award anywhere before.

Al 19/2023

**Prof. Sujit K. Biswas** (Signature of the Supervisor with date & Office Seal)

Dr. Sujit K. Biswas Former Professor & Head Department of Electrical Engineering Jadavpur University, Kolkata-700032 Dedicated to Maa Bhabatarini

&

my Mother

#### **ABSTRACT**

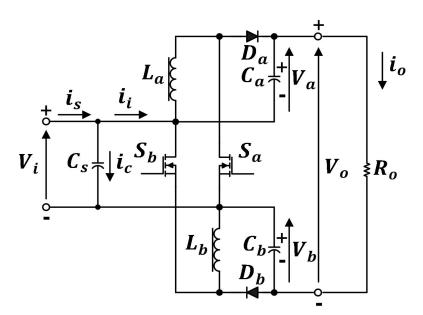

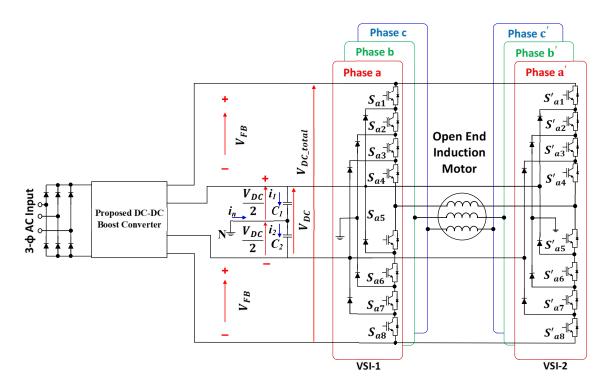

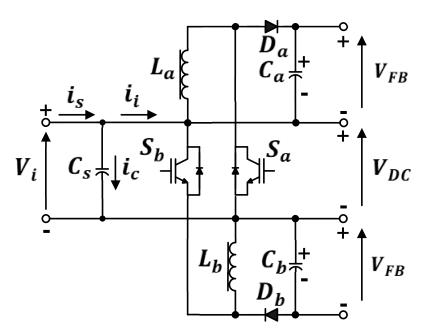

The topology of a floating output, voltage boost, non-isolated interleaved buck-boost DC-DC converter is proposed. Without utilization of transformers or coupled inductors, voltages are added symmetrically on both sides of the input DC bus in series, through two 180° phase shifted buck-boost sub-converters operating from each side of the input DC rails. This results in reduction of input current and output voltage ripples. Therefore, semiconductor and passive component ratings are also reduced compared to classical DC-DC boost converters. There is no subtraction of the total input voltage from the output voltages of the sub-converters. Since fraction of the load power flows in directly from the input, each sub-converter does not process the entire output power. This results in minimizing the current & voltage ratings of the semiconductor devices resulting in improving the overall system efficiency. Due to the symmetrical addition of voltages on both sides of the incoming DC bus, the converter that has been proposed can be used to create multiple DC voltage levels for multilevel inverters.

In the linear modulation range, the maximum fundamental voltage that can be generated across the motor terminal is less than the input AC voltage fed to the diode bridge rectifier. Further, supply voltage can dip by about 10%, either momentary or long term, which is common. Thus, it is essential to boost the DC bus voltage to maintain the rated AC voltage at the motor terminal despite the mentioned practical limitations.

A modified topology for efficiently boosting the DC bus voltage in a transformer-less 5-level Neutral Point Clamped (NPC), Voltage Source Inverter (VSI) based Open End Induction Motor (OEIM) drive is shown as the application of the proposed DC-DC boost converter. Out of the four separate voltage levels, the two middle levels are obtained by dividing the input DC voltage using a capacitor voltage divider. The top and bottom voltage levels are obtained from the sub-converters of the proposed DC-DC converter whose generated voltages are kept just sufficient to cater to the boost need, resulting in low additional power loss in the process of boosting the voltage.

#### ACKNOWLEDGEMENT

The research work and the current thesis are outcomes of constant technical inputs from several persons I have met at various stages of my research period. I would like to convey my most sincere recognition to each one for their respective assistance.

At the onset, I would like to convey my heartfelt gratitude and deepest regards to my thesis supervisor, Prof. Sujit K. Biswas for his valuable guidance, advice, encouragement and motivation at every step of my doctoral program. In spite of his busy & hectic schedule and even at odd hours of the day, he was always there to discuss my thesis problem and ready to advise me for achieving the necessary solution. I do consider myself very blessed for working under such a positive and approachable human being.

I am grateful to the HoD of Electrical Engineering Department, **Prof. Biswanath Roy** and Doctoral Committee members of Electrical Engineering Department, Jadavpur University, for their kind support and concern regarding my academic requirements.

I would like to thank **Dr. Abanishwar Chakrabarti**, Assistant Professor, Electrical Engineering Department, NIT Agartala for his enormous help and technical support for completing my research paper and thesis work.

I would also like to thank Mr. Dipten Maiti, Assistant Professor, Electrical Engineering Department, Jadavpur University for his accurate technical inputs for the completion of my research work, especially during building the experimental prototype in the laboratory.

I am thankful to Mr. Pravat Chandra for his constant assistance during building my experimental prototype and being patient during the trial period of the experiment work.

Last but not the least, the love, blessings and the moral support of my Mother, was a great source of motivation for me to keep on moving forward even on rough days for the completion of my doctoral degree.

September 2023

Jadavpur University

Kolkata- 700032

**Koustuv Sarkar**

Kowny lankou

# **Contents**

| Abstract     |                                                                           | vii  |

|--------------|---------------------------------------------------------------------------|------|

| Acknowled    | gement                                                                    | viii |

| List of Figu | ıres                                                                      | xiii |

| List of Tabl | les                                                                       | xix  |

| List of Abb  | previation                                                                | xxi  |

| Chapter 1    |                                                                           | 1    |

| 1. Intro     | oduction and Literature Survey                                            | 1    |

| 1.1          | Brief Background and Present Statistics of Renewable Energy Sources (RES) | 1    |

| 1.2          | Stand alone system Based on Solar PV for Rural Deployment.                | 2    |

| 1.3          | Vital Issues Regarding Designing a Stand Alone Scheme Based               |      |

|              | on Solar Photovoltaic                                                     | 3    |

|              | 1.3.1 Requirement of DC-DC converter                                      | 4    |

| 1.4          | Stand Alone Configuration Engaging DC-DC Converter for High               |      |

|              | Gain                                                                      | 5    |

| 1.5          | High Gain DC-DC Converter                                                 | 7    |

|              | 1.5.1 Classical Boost Converter (CBC)                                     | 7    |

|              | A. Operating Principle                                                    | 8    |

|              | 1.5.2 Tapped Inductor Boost Converter (TIBC)                              | 10   |

|              | A. Operating Principle                                                    | 11   |

|              | 1.5.3 Quadratic Boost Converter (QBC)                                     | 13   |

|              | A. Operating Principle                                                    | 14   |

|              | 1.5.4 Voltage Lift Techniques                                             | 15   |

|              | A. Operating Principle                                                    | 16   |

|              | 1.5.5 Interleaved Boost DC-DC Converter                                   | 19   |

| 1.6          | Objective of the Thesis Formulation                                       | 21   |

| 1.7          | Organization of the Remainder Thesis                                      | 22   |

| Chapt | er 2  |                                                           | 2          |

|-------|-------|-----------------------------------------------------------|------------|

| 2.    | A Nev | w Interleaved Boost DC-DC Converter                       | 2          |

|       | 2.1   | Introduction                                              | 2          |

|       | 2.2   | Proposed Converter                                        | 2          |

|       | 2.3   | Conduction States of the Proposed Converter               | 3          |

|       |       | 2.3.1 Continuous Conduction Mode (CCM)                    | 3          |

|       |       | 2.3.2 Discontinuous Conduction Mode (DCM)                 | 3          |

|       | 2.4   | Control Design of the Proposed Converter                  | 4          |

|       |       | 2.4.1 Introduction                                        | 4          |

|       |       | 2.4.2 PWM Control Methods for Voltage-Fed DC-DC Converter | 4          |

|       | 2.5   | PWM Control Using PWM IC UC3525A                          | 4          |

|       | 2.6   | PWM Control of the Proposed Converter                     | 4          |

|       |       | 2.6.1 UC3525A Synchronization through Sync Pin            | 4          |

|       | 2.7   | Control Loop for Voltage                                  | 4          |

|       | 2.8   | Hardware Design of the Entire Control Circuit             | 4          |

|       | 2.9   | Conclusion                                                | 5          |

|       |       |                                                           |            |

| Chapt | er 3  |                                                           | 5          |

| 3.    | State | Space Modeling and Results from Hardware Prototype        | 5          |

|       | 3.1   | State Space Model                                         | 5          |

|       |       | 3.1.1 Introduction                                        | 5          |

|       | 3.2   | State Space Modeling for the Proposed Converter           | 5          |

|       | 3.3   | Inductor Design                                           | 6          |

|       |       | 3.3.1 Introduction                                        | 6          |

|       |       | 3.3.2 Inductor Value Determination                        | 6          |

|       |       | 3.3.3 Design Process of the Inductor                      | 6          |

|       |       | 3.3.4 Calculation of Air Gap of the Inductor              | 6          |

|       | 3.4   | Semiconductor Device Selection                            | 6          |

|       |       | 3.4.1 MOSFET Selection                                    | 6          |

|       |       | 3.4.2 Diode Selection                                     | 6          |

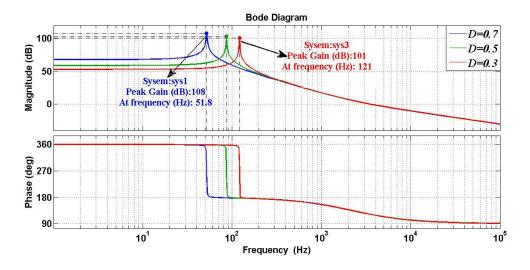

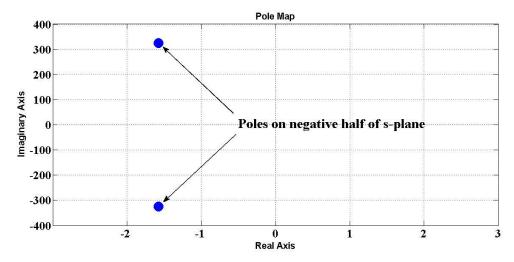

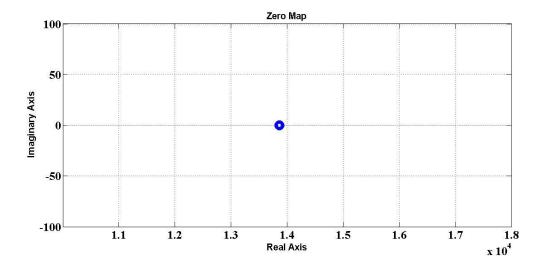

|       | 3.5   | Bode Plot for the Proposed DC-DC Converter                | $\epsilon$ |

|       |       | 3.5.1 Introduction                                        | 6          |

|       |       | 3.5.2 Bode Diagram for the Proposed Converter             | 6          |

|       | 3.6   | Simulation Results                                        | 7          |

|       |                | 3.6.1 Introduction                                           | 71          |

|-------|----------------|--------------------------------------------------------------|-------------|

|       |                | 3.6.2 Waveforms of the Converter                             | 72          |

|       | 3.7            | Experimental Validation                                      | 79          |

|       | 3.8            | Conclusion.                                                  | 86          |

| Chapt | er 4           |                                                              | 87          |

| 4.    | Comp           | parison with Other Boost Converters and Cascaded Representat | ion         |

|       | of the         | Proposed Converter                                           | 87          |

|       | 4.1            | Introduction                                                 | 87          |

|       | 4.2            | Comparison with Classical Boost DC-DC Converter              | 87          |

|       | 4.3            | Comparison with Quasi-SEPIC and Interleaved Boost            |             |

|       |                | DC-DC Converter                                              | 94          |

|       | 4.4            | Efficiency Plot.                                             | 101         |

|       | 4.5            | Cascaded Multi-Stage Extension                               | 103         |

|       |                | 4.5.1 Voltage Gain Equation of the Internally                |             |

|       |                | Cascaded Converter                                           | 104         |

|       | 4.6            | Simulation Results for Two-stage Cascaded Configuration      | 107         |

|       | 4.7            | Conclusion.                                                  | 110         |

| Chapt | er 5           |                                                              | 112         |

| 5.    | Propo<br>Drive | osed Converter Application in a 5-Level Open-End Induction M | otor<br>112 |

|       | 5.1            | Introduction                                                 | 112         |

|       | 5.2            | Proposed Scheme                                              | 114         |

|       | 5.3            | Voltage Boost Generation using DC-DC Converter               | 116         |

|       | 5.4            | CMV Elimination in Drive with Unequal Voltage Step           | 118         |

|       | 5.5            | Reference Signal Generation                                  | 120         |

|       | 5.6            | Capacitor Voltage Balancing                                  | 122         |

|       | 5.7            | Implementation of the Proposed Scheme                        | 124         |

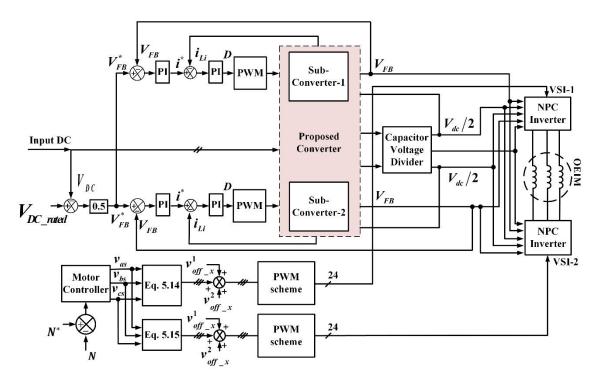

|       | 5.8            | Complete Closed Loop System of the Proposed Scheme           | 126         |

|       | 5.9            | Performance Analysis                                         | 127         |

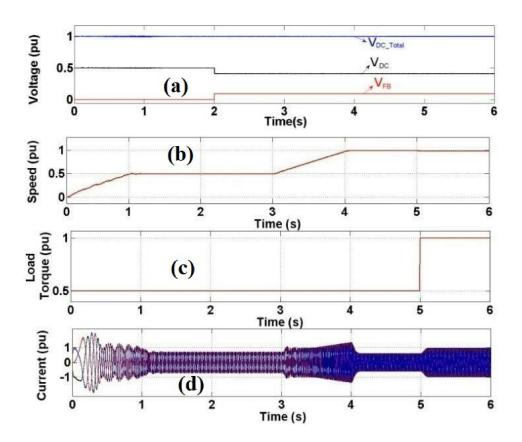

|       |                | 5.9.1 Simulation Results                                     | 127         |

|       |                | 5.9.2 Experimental Results                                   | 131         |

|       | 5.10           | Efficiency Calculation                                       | 135         |

|       | 5.11           | Comparative Study                                            | 136         |

|       | 5.12  | Conclusion                                                 | 137 |

|-------|-------|------------------------------------------------------------|-----|

| Chapt | er 6  |                                                            | 139 |

| 6.    | Conc  | lusion and Future Scope                                    | 139 |

|       | 6.1   | Conclusion                                                 | 139 |

|       | 6.2   | Future Scope                                               | 140 |

| REFE  | RENC! | ES                                                         | 141 |

| PUBL  | ICATI | ONS                                                        | 152 |

| APPE  | NDIX- | A                                                          | 153 |

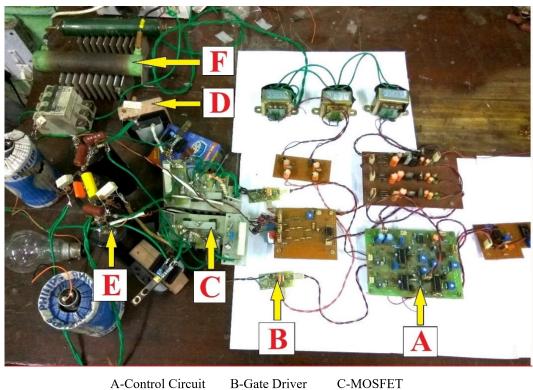

|       | A.1   | Control Circuit Hardware                                   | 153 |

|       | A.2   | MOSFET selection & parameters                              | 154 |

|       | A.3   | Diode selection & parameters                               | 154 |

|       | A.4   | View of the Laboratory experimental setup                  |     |

|       |       | (Proposed DC-DC Converter)                                 | 155 |

| APPE  | NDIX- | В                                                          | 156 |

|       | B.1   | MATLAB Code for Bode Plot                                  | 156 |

|       | B.2   | MATLAB Code for Pole Zero Map                              | 157 |

| APPE  | NDIX- | C                                                          | 158 |

|       | C.1   | Parameters for Simulation & Experimental Study             | 158 |

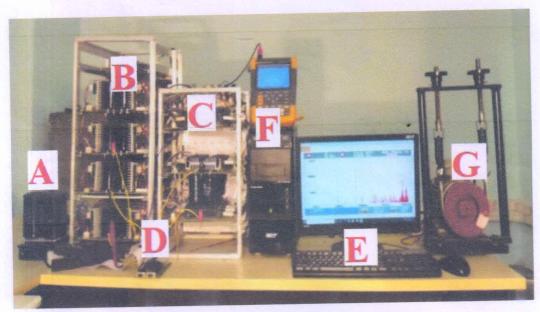

|       | C.2   | Photograph of the experimental setup (Proposed 5-level NPC |     |

|       |       | VSI base OEIM drive)                                       | 159 |

# List of Figures

| Figure 1.1  | Schematic for a basic stand alone system                                                                                                                                                             | 3         |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Figure 1.2  | Rudimentary four stage framework                                                                                                                                                                     | 6         |

| Figure 1.3  | Three stage framework with battery bank incorporated in cascade                                                                                                                                      | 6         |

| Figure 1.4  | Schematic of a Classical Boost Converter                                                                                                                                                             | 7         |

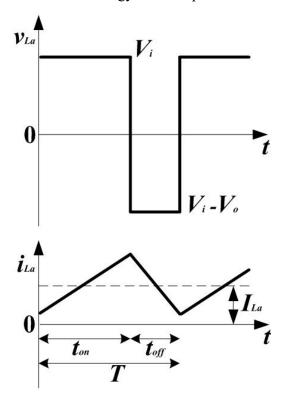

| Figure 1.5  | Inductor voltage and current waveform during Continuous Conduction Mode for CBC.                                                                                                                     | 8         |

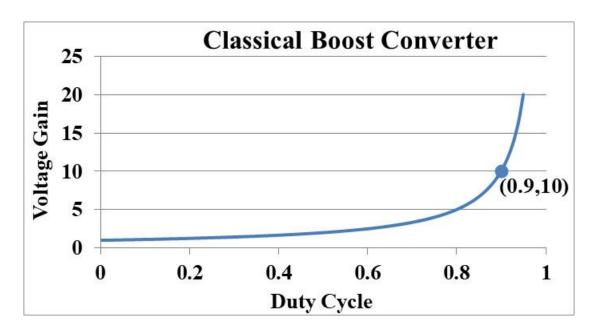

| Figure 1.6  | Voltage gain versus Duty cycle of a CBC                                                                                                                                                              | 10        |

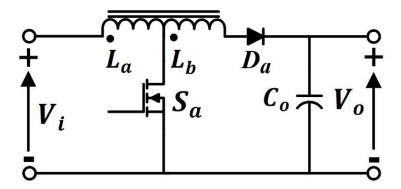

| Figure 1.7  | Schematic of a Tapped Inductor Boost converter                                                                                                                                                       | 11        |

| Figure 1.8  | Schematic of a Quadratic Boost Converter                                                                                                                                                             | 13        |

| Figure 1.9  | Elementary circuit of a positive output Luo converter                                                                                                                                                | 16        |

| Figure 1.10 | Schematic of Interleaved Boost DC-DC converter                                                                                                                                                       | 20        |

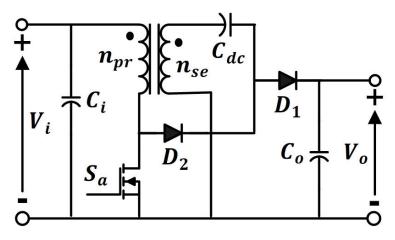

| Figure 1.11 | Modified diagram of IDDB converter                                                                                                                                                                   | 21        |

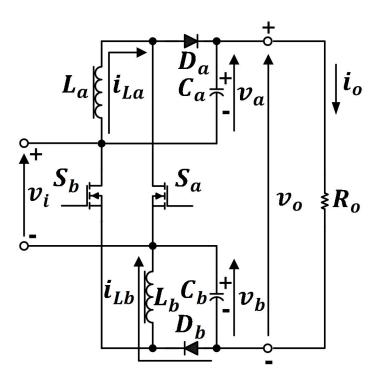

| Figure 2.1  | Proposed boost DC-DC converter                                                                                                                                                                       | 25        |

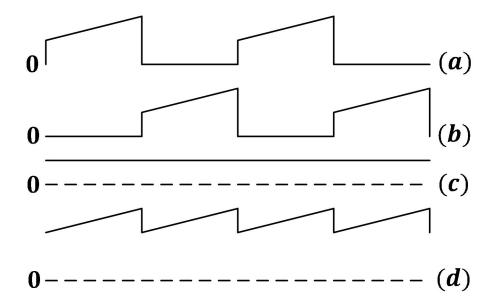

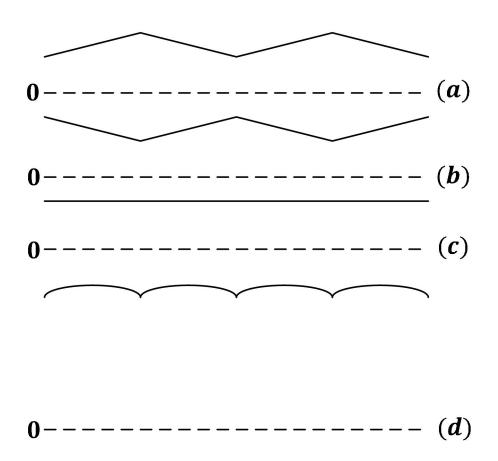

| Figure 2.2  | Components of instantaneous input current of proposed boost DC-DC converter (a) input current of converter 'a' (b) input current of converter 'b' (c) load current component (d) total input current | 27        |

| Figure 2.3  | Components of instantaneous output voltage of proposed boost DC-DC converter (a) output voltage of converter 'a' (b) output voltage of conver 'b' (c) input voltage (d) total output voltage         | ter<br>27 |

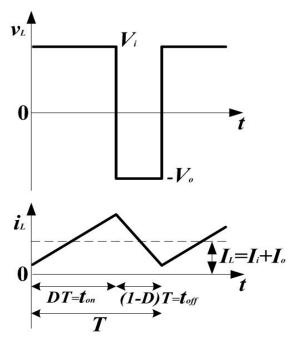

| Figure 2.4  | Inductor voltage and current waveform during CCM for individual converter (proposed converter)                                                                                                       | 28        |

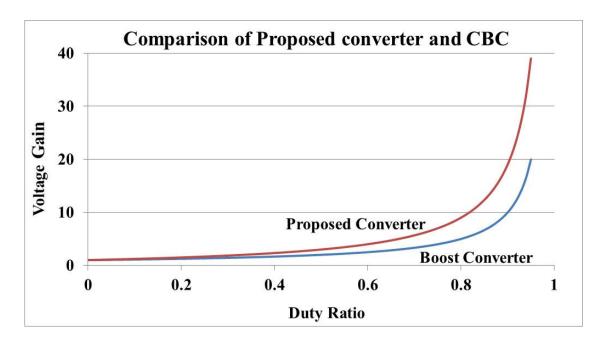

| Figure 2.5  | Voltage gain of the proposed converter and CBC versus duty ratio                                                                                                                                     | 29        |

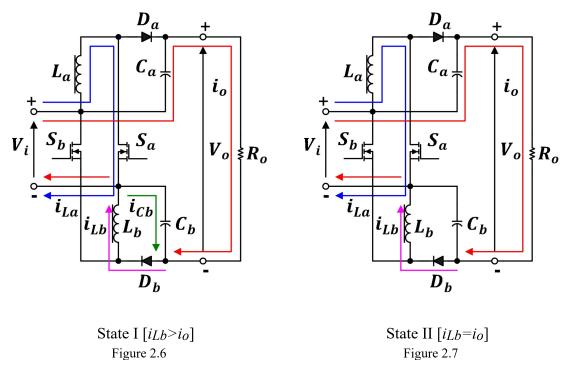

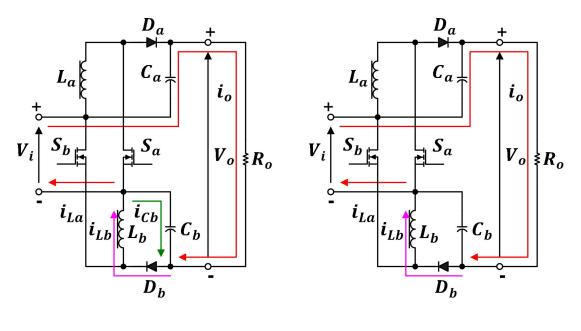

| Figure 2.6  | Conduction State (CCM) State I [ $iLb > i_0$ ]                                                                                                                                                       | 32        |

| Figure 2.7  | Conduction State (CCM) State II [ $iLb=i_O$ ]                                                                                                                                                        | 32        |

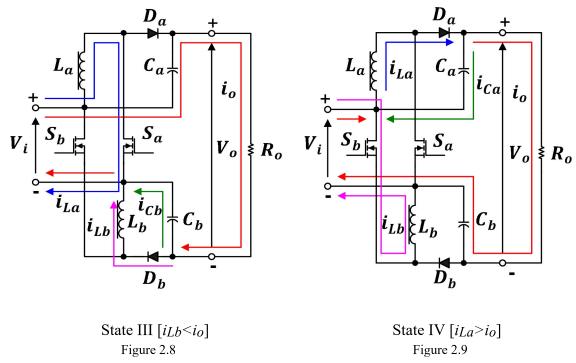

| Figure 2.8  | Conduction State (CCM) State III [ $iLb < i_0$ ]                                                                                                                                                     | 33        |

| Figure 2.9  | Conduction State (CCM) State IV [ <i>iLa</i> > <i>io</i> ]                                                                                                                                           | 33        |

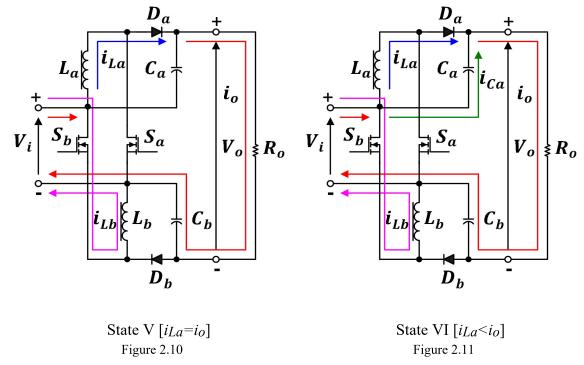

| Figure 2.10 | Conduction State (CCM) State V [ <i>iLa=io</i> ]                                                                                                                                                     | 34        |

| Figure 2.11 | Conduction State (CCM) State VI [ <i>iLa</i> < <i>io</i> ]                                                                                                                                           | 34        |

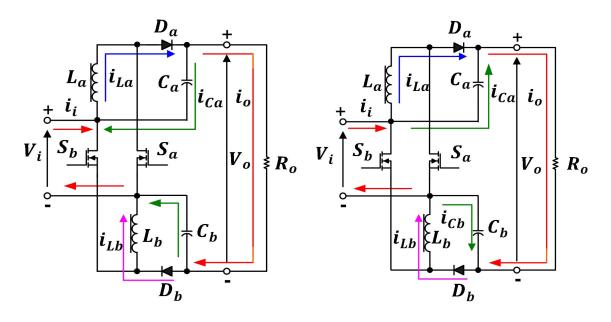

| Figure 2.12 | Conduction State (CCM) State VII $[iLa > i_0][iLb < i_0]$                                                                                                                                            | 35        |

| Figure 2.13 | Conduction State (CCM) State VIII [ $iLa < i_0$ ][ $iLb > i_0$ ]                                                                                                                                     | 35        |

| Figure 2.14 | Conduction State (CCM) State IX                                                                                                                                                                      | 35        |

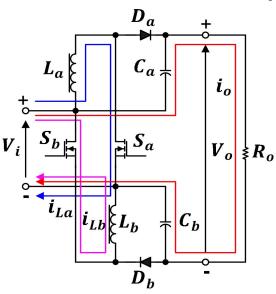

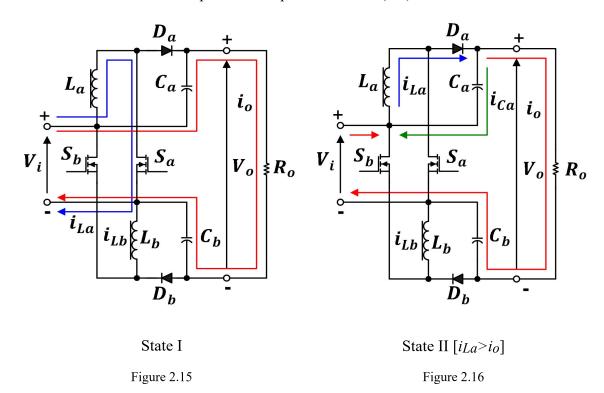

| Figure 2.15 | Conduction State (DCM) State I                                                                                                                                                                       | 36        |

| Figure 2.16 | Conduction State (DCM) State II [ $iLa > i_0$ ]                                                | 36   |

|-------------|------------------------------------------------------------------------------------------------|------|

| Figure 2.17 | Conduction State (DCM) State III [ $iLa=i_0$ ]                                                 | 37   |

| Figure 2.18 | Conduction State (DCM) State IV $[iLa < io]$                                                   | 37   |

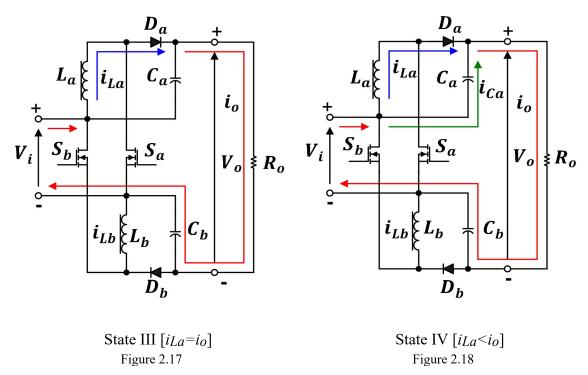

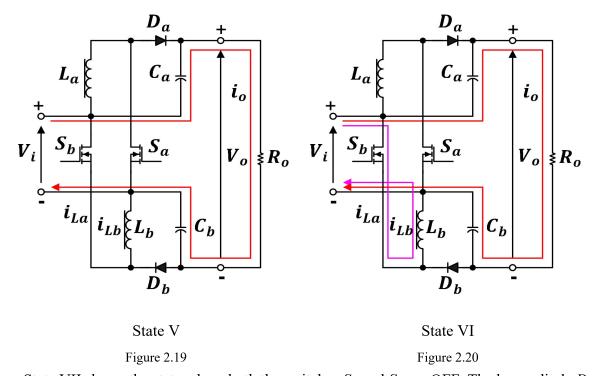

| Figure 2.19 | Conduction State (DCM) State V                                                                 | 38   |

| Figure 2.20 | Conduction State (DCM) State VI                                                                | 38   |

| Figure 2.21 | Conduction State (DCM) State VII [ <i>i</i> L <i>b</i> > <i>i</i> <sub>0</sub> ]               | 39   |

| Figure 2.22 | Conduction State (DCM) State VIII $[iLb=i_0]$                                                  | 39   |

| Figure 2.23 | Conduction State (DCM) State IX [ <i>i</i> L <i>b</i> < <i>i</i> <sub>0</sub> ]                | 39   |

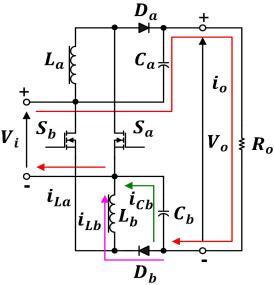

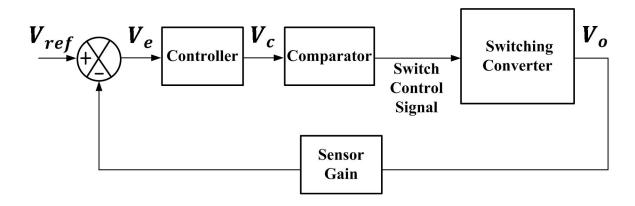

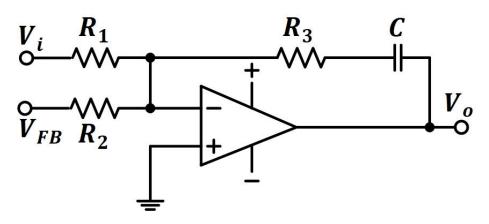

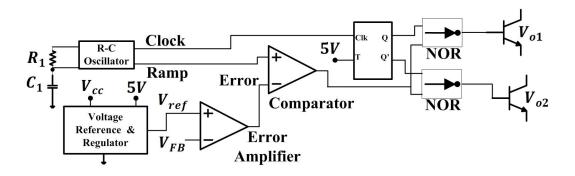

| Figure 2.24 | Block diagram of a feedback system generally used in PWM operation                             | . 40 |

| Figure 2.25 | Standard PI controller                                                                         | 41   |

| Figure 2.26 | Schematic for PWM controller having two switches on the same leg                               | 42   |

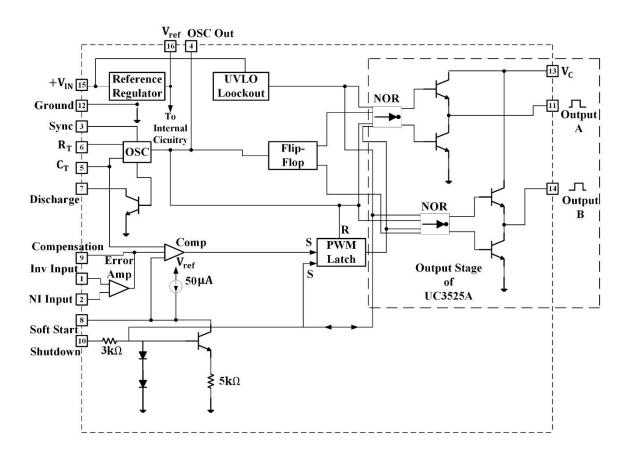

| Figure 2.27 | Block diagram of PWM IC UC3525A                                                                | 44   |

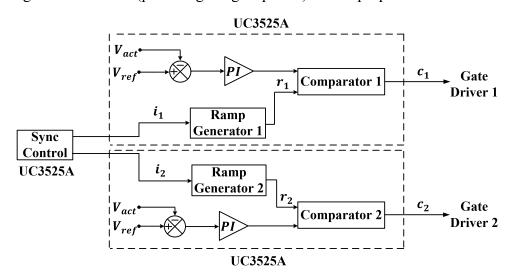

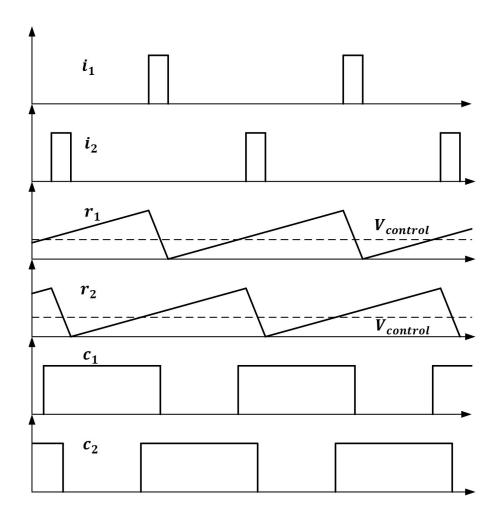

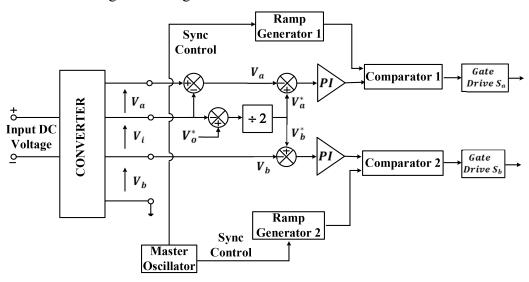

| Figure 2.28 | Basic block diagram of PWM control of the proposed converter                                   | 45   |

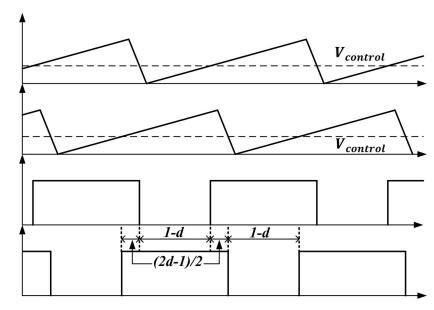

| Figure 2.29 | Waveforms at various designated points in Fig. 2.28                                            | 46   |

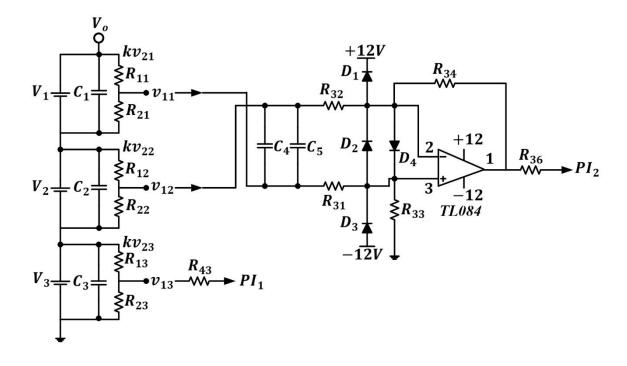

| Figure 2.30 | Schematic of the hardware voltage control loop                                                 | 49   |

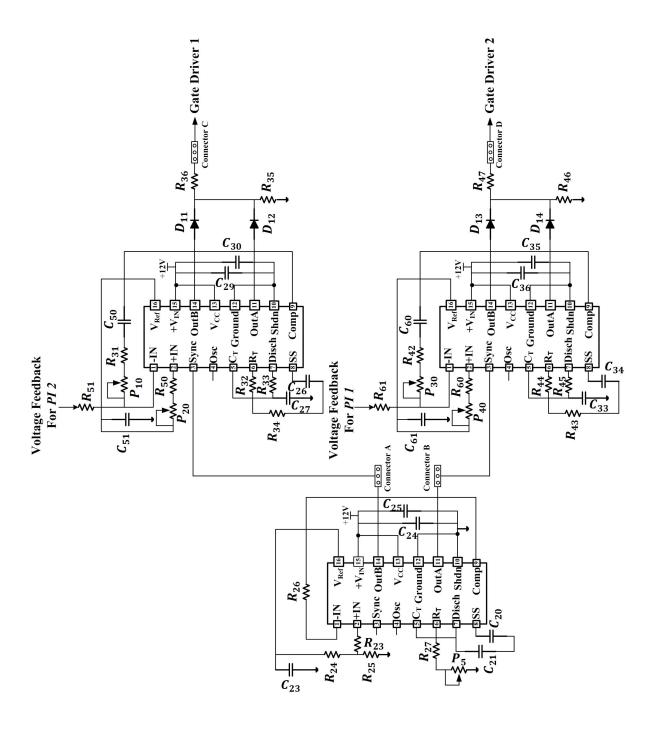

| Figure 2.31 | Schematic diagram of the total control circuit                                                 | 50   |

| Figure 2.32 | Block diagram of the control scheme                                                            | 51   |

| Figure 3.1  | Schematic for state space modeling                                                             | 53   |

| Figure 3.2  | Conduction states of the switches over a switching period                                      | 55   |

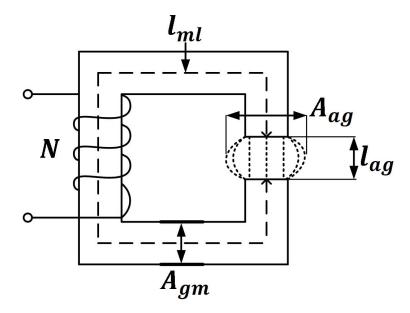

| Figure 3.3  | Diagram for inductor magnetic circuit                                                          | 61   |

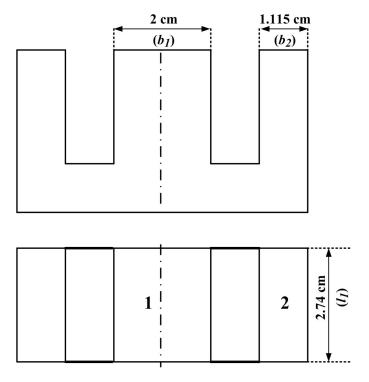

| Figure 3.4  | Dimension of the EE-65-27 ferrite core                                                         | 65   |

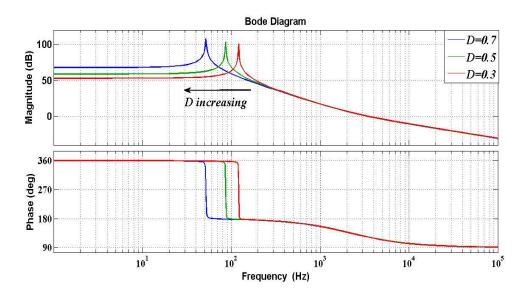

| Figure 3.5  | Bode diagram for the proposed converter                                                        | 69   |

| Figure 3.6  | Bode diagram with gain peaking frequency                                                       | 70   |

| Figure 3.7  | Pole mapping for the system transfer function                                                  | 70   |

| Figure 3.8  | Zero mapping for the system transfer function                                                  | 71   |

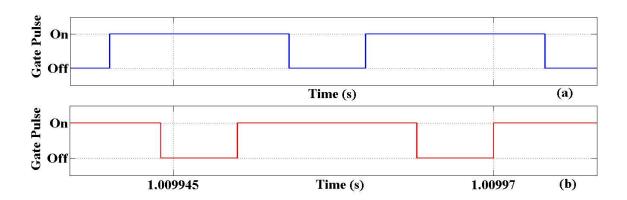

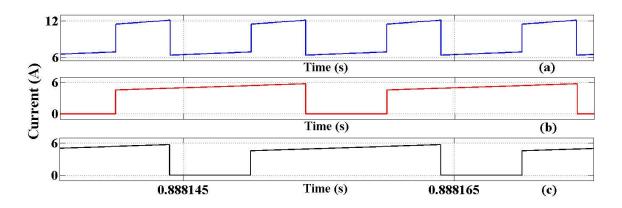

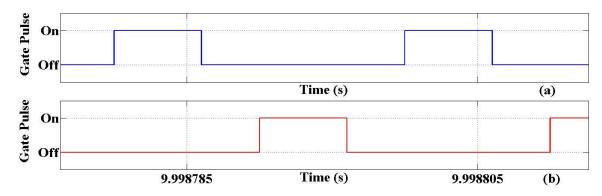

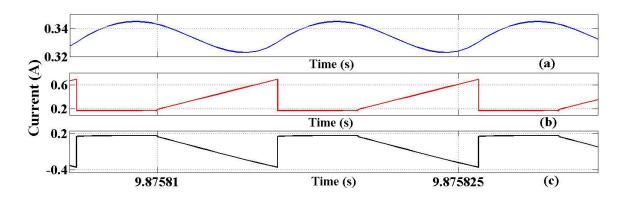

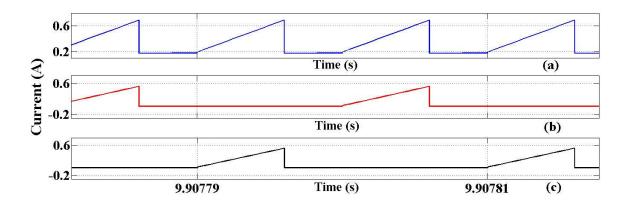

| Figure 3.9  | ( $D$ =0.7) (a) Gate pulse for switch $S_a$ (b) Gate pulse for switch $S_b$                    | 72   |

| Figure 3.10 | (D=0.7) (a) Source current (b) Converter input current (c) Current through the input capacitor | _    |

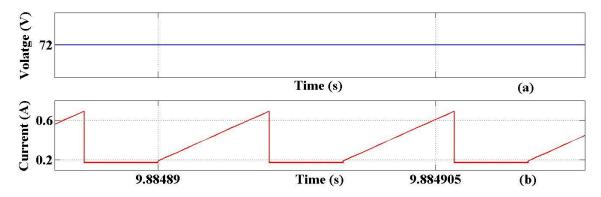

| Figure 3.11 | (D=0.7) (a) Input voltage (b) Converter input current                                          | 73   |

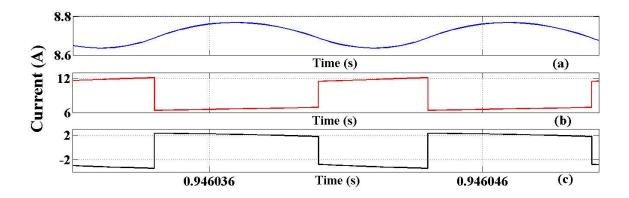

| Figure 3.12 | (D=0.7) (a) Source current (b) Load current (c) Input voltage (d) Total output voltage         | 73   |

| Figure 3.13 | $(D=0.7)$ (a) Converter input current (b) Inductor current for $L_a$ (c) Inductor              | tor  |

|             | current for <i>Lb</i>                                                                          | 73   |

| Figure 3.14 | ( $D$ =0.7) (a) Converter input current (b) Switch current for $S_a$ (c) Switch                                                                 |          |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|             | current for Sb                                                                                                                                  | 74       |

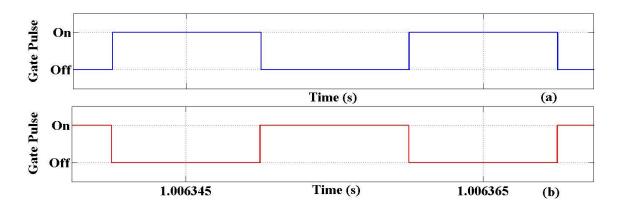

| Figure 3.15 | ( $D$ =0.5) (a) Gate pulse for switch $S_a$ (b) Gate pulse for switch $S_b$                                                                     | 75       |

| Figure 3.16 | (D=0.5) (a) Source current (b) Converter input current (c) Current through the input capacitor                                                  | h<br>75  |

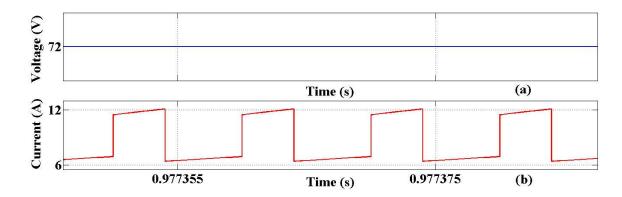

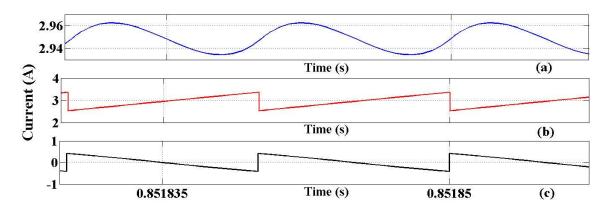

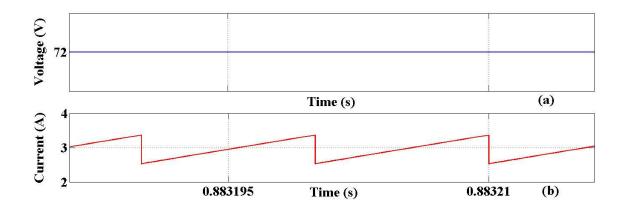

| Figure 3.17 | (D=0.5) (a) Input voltage (b) Converter input current                                                                                           | 75       |

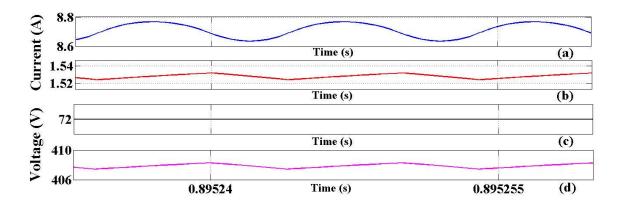

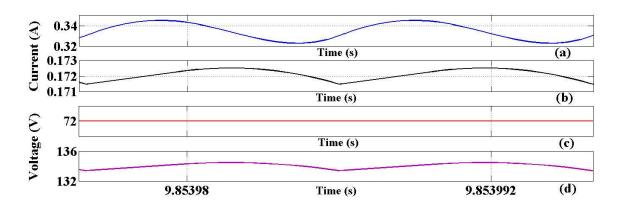

| Figure 3.18 | (D=0.5) (a) Source current (b) Load current (c) Input voltage (d) Total output voltage                                                          | 76       |

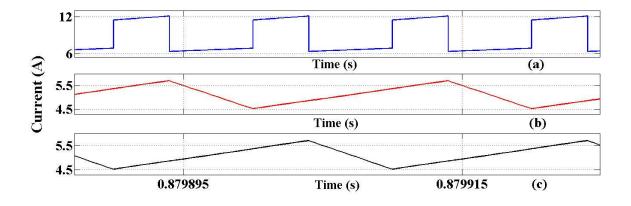

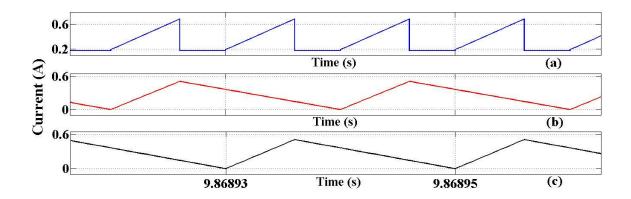

| Figure 3.19 | $(D=0.5)$ (a) Converter input current (b) Inductor current for $L_a$ (c) Inductor current for $L_b$                                             |          |

| Figure 3.20 | ( $D$ =0.5) (a) Converter input current (b) Switch current for $S_a$ (c) Switch current for $S_b$                                               | 76       |

| Figure 3.21 | ( $D$ =0.3) (a) Gate pulse for switch $S_a$ (b) Gate pulse for switch $S_b$                                                                     | 78       |

| Figure 3.22 | (D=0.3) (a) Source current (b) Converter input current (c) Current through the input capacitor                                                  | h<br>78  |

| Figure 3.23 | (D=0.3) (a) Input voltage (b) Converter input current                                                                                           | 78       |

| Figure 3.24 | (D=0.3) (a) Source current (b) Load current (c) Input voltage (d) Total output voltage                                                          | 79       |

| Figure 3.25 | ( $D$ =0.3) (a) Converter input current (b) Inductor current for $L_a$ (c) Inductor current for $L_b$                                           | or<br>79 |

| Figure 3.26 | ( $D$ =0.3) (a) Converter input current (b) Switch current for $S_a$ (c) Switch current for $S_b$                                               | 79       |

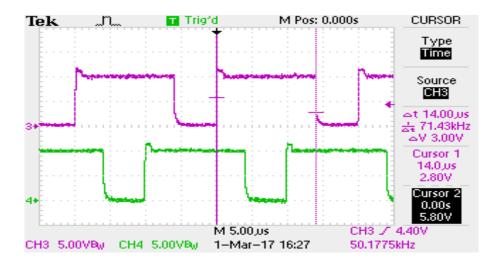

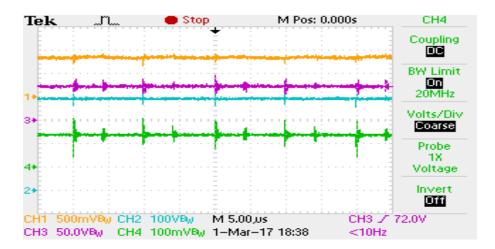

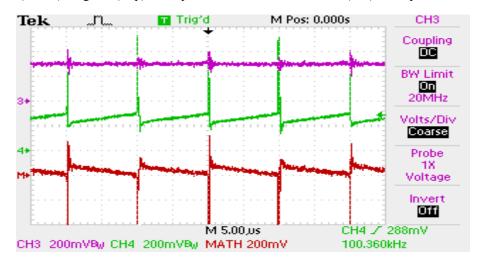

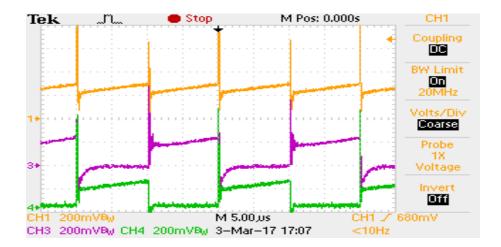

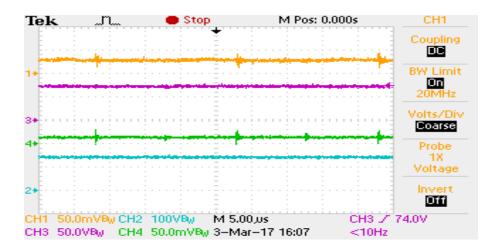

| Figure 3.27 | ( $D$ =0.7) Magenta (Top): Gate pulse for switch $S_a$ , Green (Bot): Gate pulse for switch $S_b$                                               | e<br>80  |

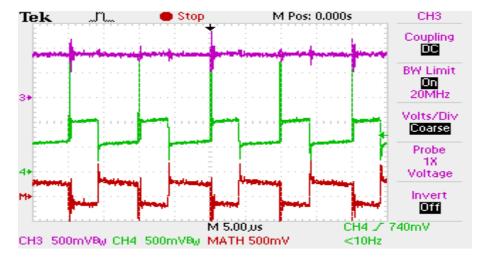

| Figure 3.28 | (D=0.7) Magenta (Top): Source current, Green (Mid): Converter input current, Red (Bot): Current through the capacitor                           | 80       |

| Figure 3.29 | (D=0.7) Magenta (Top): Input voltage, Green (Bot): Converter input current                                                                      | 81       |

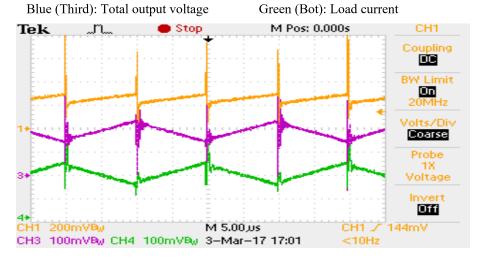

| Figure 3.30 | ( <i>D</i> =0.7) Yellow (First): Source current, Magenta (Second): Input voltage, Blue (Third): Total output voltage, Green (Bot): Load current |          |

| Figure 3.31 | ( $D$ =0.7) Yellow (Top): Converter input current, Magenta (Mid): Inductor current for $L_a$ , Green (Bot): Inductor current for $L_b$          |          |

| Figure 3.32 | ( $D$ =0.7) Yellow (Top): Converter input current, Magenta (Mid): Switch current for $S_a$ , Green (Bot): Switch current for $S_b$              | 82       |

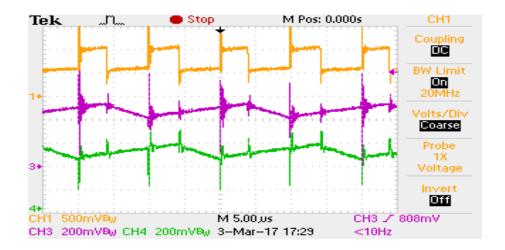

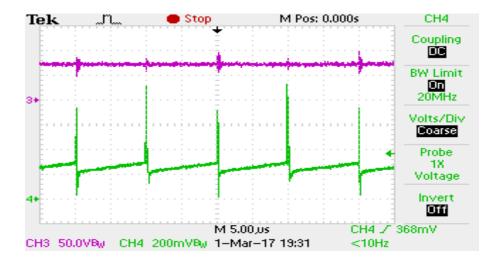

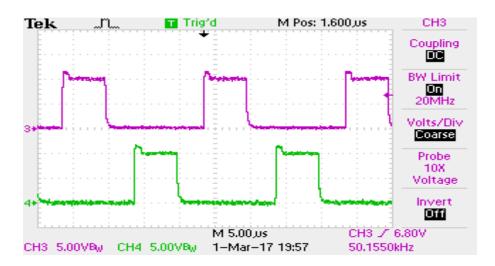

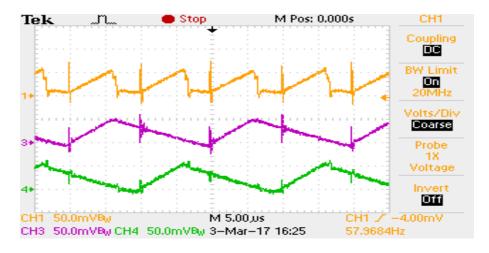

| Figure 3.33 | ( $D$ =0.5) Magenta (Top): Gate pulse for switch $S_a$ , Green (Bot): Gate pulse for switch $S_b$                                               |          |

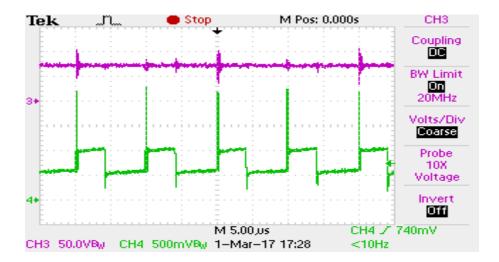

| Figure 3.34 | (D=0.5) Magenta (Top): Source current, Green (Mid): Converter input current, Red (Bot): Current through the capacitor                           |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.35 | (D=0.5) Magenta (Top): Input voltage, Green (Bot): Converter input current                                                                      |

| Figure 3.36 | (D=0.5) Yellow (First): Source current, Magenta (Second): Input voltage, Blue (Third): Total output voltage, Green (Bot): Load current          |

| Figure 3.37 | ( $D$ =0.5) Yellow (Top): Converter input current, Magenta (Mid): Inductor current for $L_a$ , Green (Bot): Inductor current for $L_b$          |

| Figure 3.38 | ( $D$ =0.5) Yellow (Top): Converter input current, Magenta (Mid): Switch current for $S_a$ , Green (Bot): Switch current for $S_b$              |

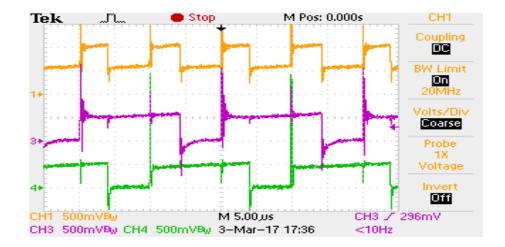

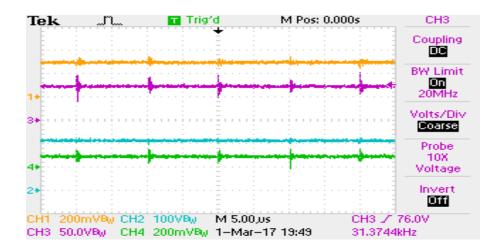

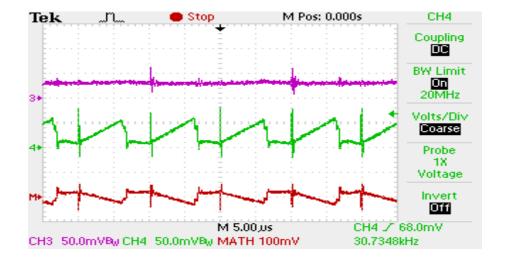

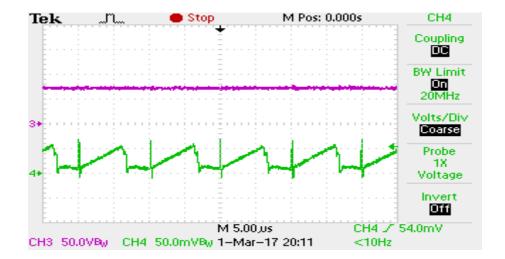

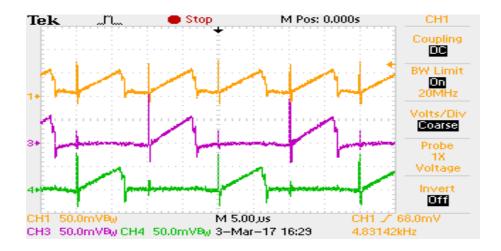

| Figure 3.39 | ( $D$ =0.3) Magenta (Top): Gate pulse for switch $S_a$ , Green (Bot): Gate pulse for switch $S_b$                                               |

| Figure 3.40 | (D=0.3) Magenta (Top): Source current, Green (Mid): Converter input current, Red (Bot): Current through the capacitor                           |

| Figure 3.41 | (D=0.3) Magenta (Top): Input voltage, Green (Bot): Converter input current                                                                      |

| Figure 3.42 | ( <i>D</i> =0.3) Yellow (First): Source current, Magenta (Second): Input voltage, Green (Third): Load current, Blue (Bot): Total output voltage |

| Figure 3.43 | ( $D$ =0.3) Yellow (Top): Converter input current, Magenta (Mid): Inductor current for $L_a$ , Green (Bot): Inductor current for $L_b$          |

| Figure 3.44 | Yellow (Top): Converter input current, Magenta (Mid): Switch current for $S_a$ , Green (Bot): Switch current for $S_b$                          |

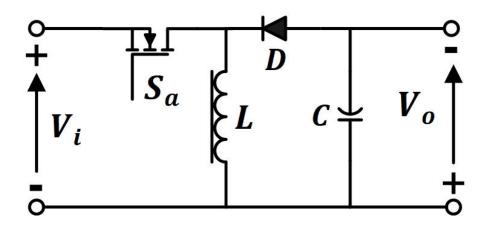

| Figure 4.1  | Schematic Diagram of a Buck-Boost Converter                                                                                                     |

| Figure 4.2  | Schematic Diagram of a Quasi-SEPIC Converter                                                                                                    |

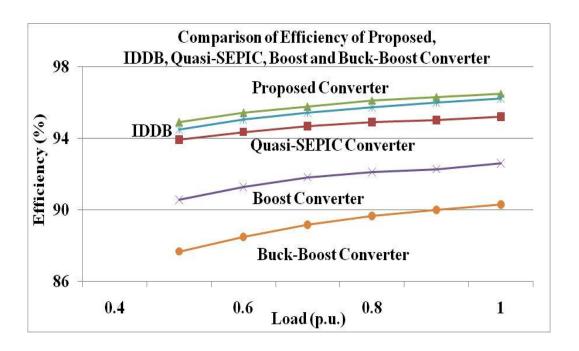

| Figure 4.3  | Efficiency Plot of the Proposed Converter along with Boost                                                                                      |

|             | Buck-Boost, Quasi-SEPIC and Interleaved Boost DC-DC Converter 102                                                                               |

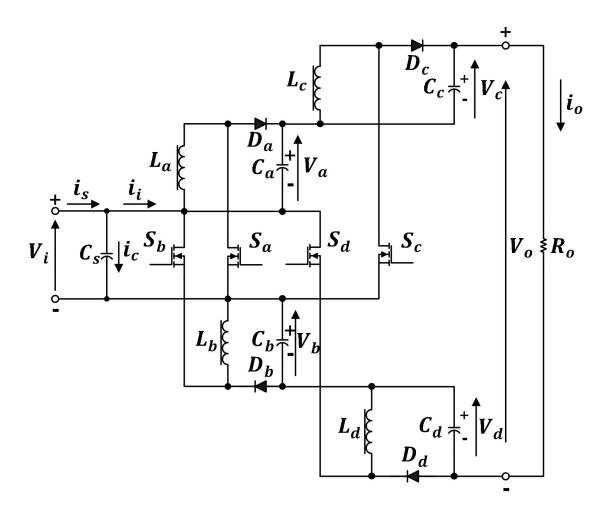

| Figure 4.4  | Schematic Diagram of Internally Cascaded Multi-Stage Extension of                                                                               |

|             | Proposed Boost Converter with Two Stages                                                                                                        |

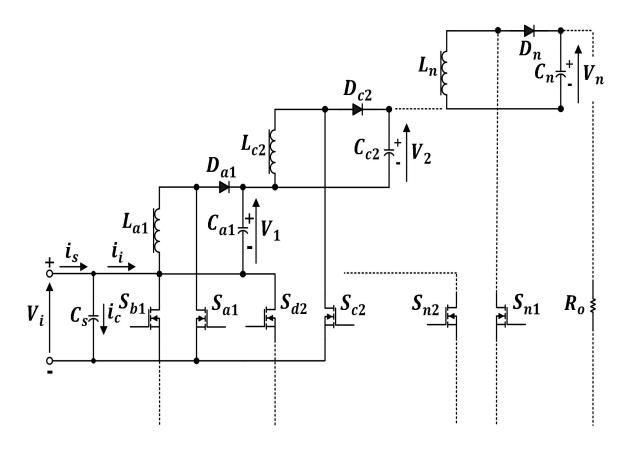

| Figure 4.5  | Schematic Diagram of Internally Cascaded Multi-Stage Extension of                                                                               |

|             | Proposed Boost Converter for <i>n</i> <sup>th</sup> stages                                                                                      |

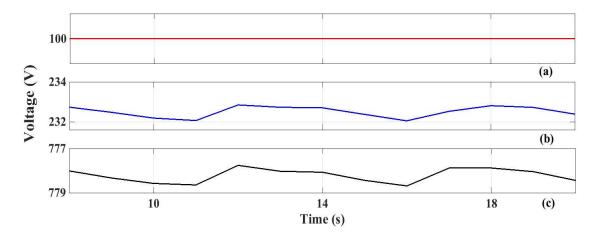

| Figure 4.6  | (D=0.7) (a) Input voltage (b) Singe-stage sub-converter output                                                                                  |

| C           | voltage (c) Two-stage sub-converter output voltage                                                                                              |

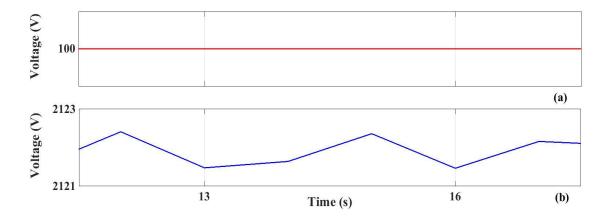

| Figure 4.7  | (D=0.7) (a) Input voltage (b) Total output voltage                                                                                              |

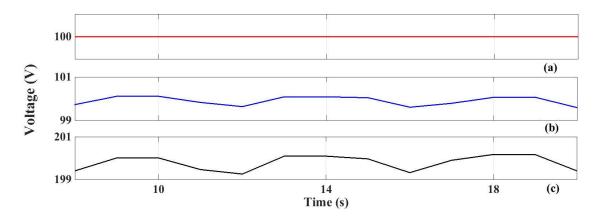

| Figure 4.8  | (D=0.5) (a) Input voltage (b) Singe-stage sub-converter output                                                                                  |

| ~           | voltage (c) Two-stage sub-converter output voltage                                                                                              |

| Figure 4.9  | ( <i>D</i> =0.5) (a) Input voltage (b) Total output voltage                                                                                     |

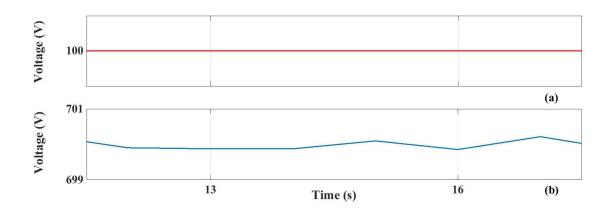

| Figure 4.10 | (D=0.3) (a) Input voltage (b) Singe-stage sub-converter output                                                                                  |

|               | voltage (c) Two-stage sub-converter output voltage                                             | 110      |

|---------------|------------------------------------------------------------------------------------------------|----------|

| Figure 4.11   | (D=0.3) (a) Input voltage (b) Total output voltage                                             | 110      |

| Figure 5.1    | Proposed 5-level open end induction motor drive with unequal level an voltage boost capability | d<br>115 |

| Figure 5.2    | Proposed converter as source of multiple DC voltage level                                      | 116      |

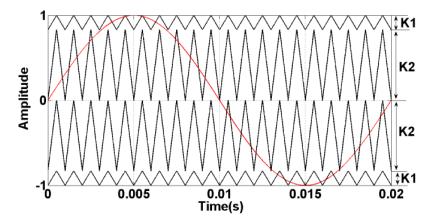

| Figure 5.3    | Possible Multicarrier PWM scheme                                                               | 125      |

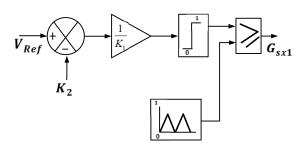

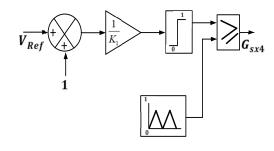

| Figure 5.4(a) | Gate Pulse Generation for $S_{x1}$                                                             | 125      |

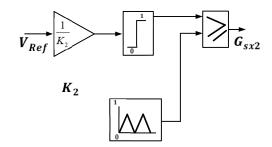

| Figure 5.4(b) | Gate Pulse Generation for $S_{x2}$                                                             | 125      |

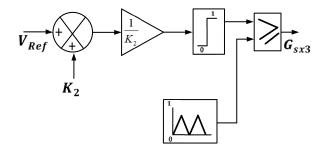

| Figure 5.4(c) | Gate Pulse Generation for $S_{x3}$                                                             | 125      |

| Figure 5.4(d) | Gate Pulse Generation for $S_{x4}$                                                             | 125      |

| Figure 5.5    | Complete Closed Loop Control System of the Proposed Scheme                                     | 127      |

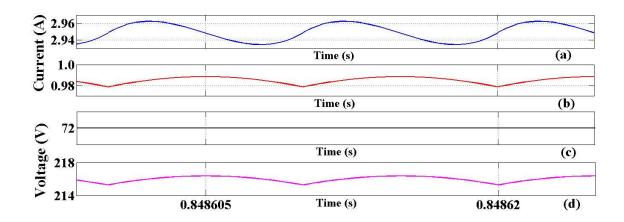

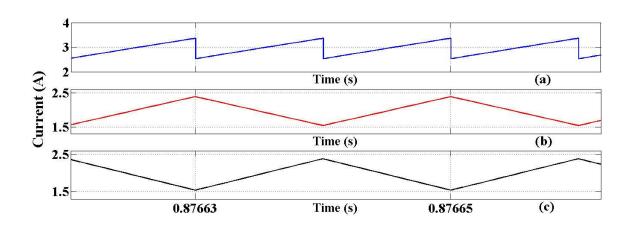

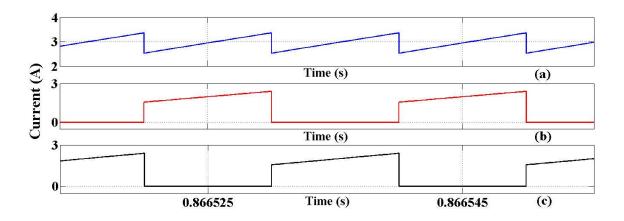

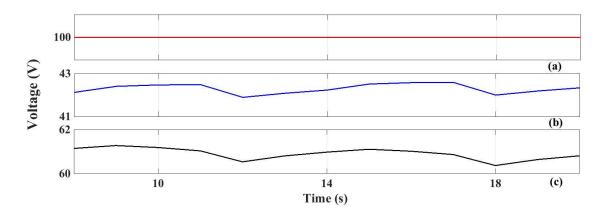

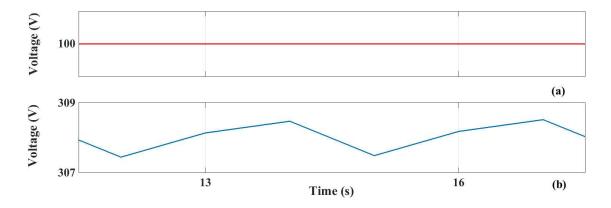

| Figure 5.6    | Simulation results under dynamic condition (a) Total DC link voltage,                          |          |

|               | supply voltage and DC-DC Converter voltage (b) Operating speed of the                          | ie       |

|               | open end induction motor (c) Load torque of the motor (d) Motor windi                          | ing      |

|               | current                                                                                        | 128      |

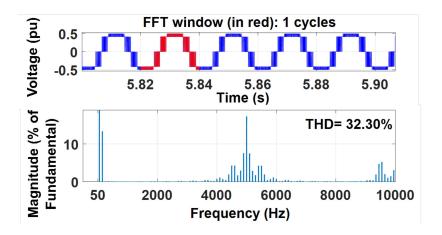

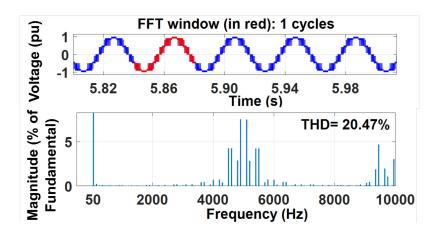

| Figure 5.7    | Pole Voltage in p.u. with rated DC bus voltage as base and its                                 |          |

|               | spectrum                                                                                       | 129      |

| Figure 5.8    | Voltage across motor winding in p.u. with rated DC bus voltage as base                         | in       |

|               | open-end mode and its spectrum                                                                 | 130      |

| Figure 5.9    | Winding current in p.u. with rated motor current as base and in                                |          |

|               | open-end configuration and its spectrum                                                        | 130      |

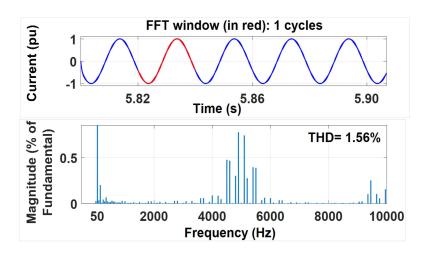

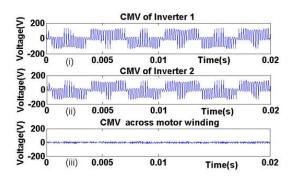

| Figure 5.10   | a) CMV generated by VSI-1 (b) CMV generated by VSI-2 (c) CMV                                   |          |

|               | across motor winding (d) Common mode current through the motor                                 |          |

|               | winding                                                                                        | 131      |

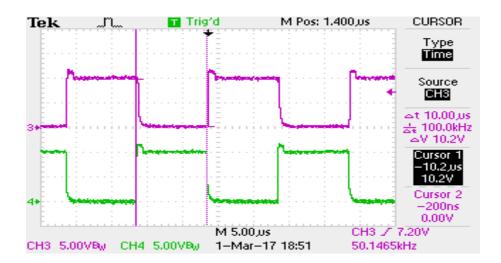

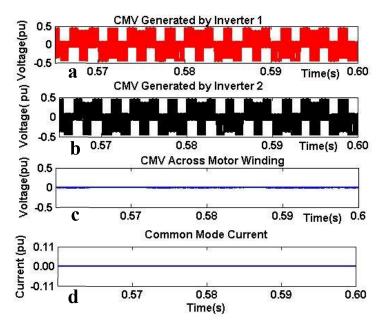

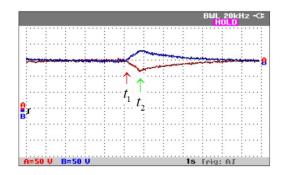

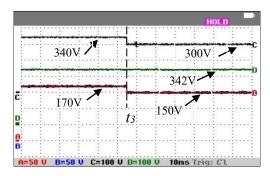

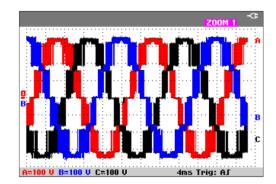

| Figure 5.11   | Capacitor Voltage Balancing with and without Balancing Loop                                    | 132      |

| Figure 5.12   | Experimental result of capacitor voltage balancing during sudden                               |          |

|               | change in input voltage; Capacitor Voltage C1 & C2                                             |          |

|               | (Trace A in Red and Trace B in Blue), input voltage                                            |          |

|               | (Trace C in Black) & Total DC voltage (Trace D in Green)                                       | 132      |

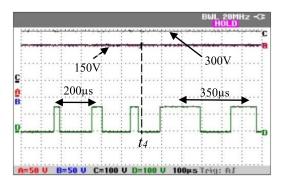

| Figure 5.13   | Experimental result of capacitor voltage balancing during change in                            |          |

|               | switching frequency; Capacitor Voltage C1 & C2 (Trace A in Red                                 |          |

|               | and Trace B in Blue), Total input voltage (Trace C in Black) & Output                          |          |

|               | voltage (Trace D in Green)                                                                     | 132      |

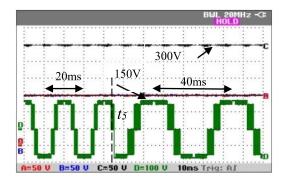

| Figure 5 14   | Experimental result of capacitor voltage balancing during sudden                               |          |

|             | change in operating frequency; Capacitor Voltage (Trace A in Red  |     |

|-------------|-------------------------------------------------------------------|-----|

|             | and Trace B in Blue), Total input voltage (Trace C in Black),     |     |

|             | Pole voltage of Five level VSI (Trace D in Green)                 | 132 |

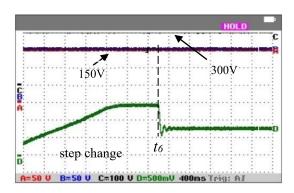

| Figure 5.15 | Experimental result of capacitor voltage balancing during dynamic |     |

|             | speed change; Capacitor Voltage C1 & C2 (Trace A in Red and       |     |

|             | Trace B in Blue), Total input voltage (Trace C in Black) &        |     |

|             | Dynamic change in speed (Trace D in Green)                        | 133 |

| Figure 5.16 | Voltage across the motor windings                                 | 133 |

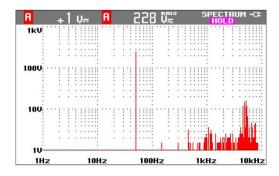

| Figure 5.17 | Spectrum of Voltage across the motor winding                      | 134 |

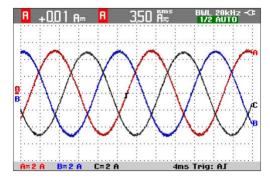

| Figure 5.18 | Motor Current at rated load                                       | 134 |

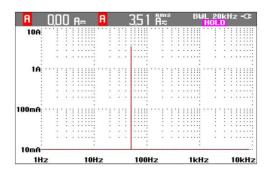

| Figure 5.19 | Motor current spectrum upto twice the switching frequency         | 135 |

| Figure 5.20 | Experimental results of (i) CMV of VSI-1 (ii) CMV of VSI-2        |     |

|             | (iii) CMV across motor winding                                    | 135 |

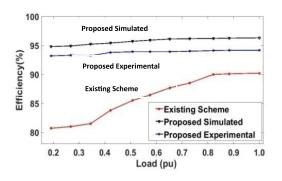

| Figure 5.21 | Comparative study of efficiency of the proposed scheme and        |     |

|             | existing similar boost inverter topology                          | 136 |

| Figure 5.22 | Power loss distribution between DC-DC converter and inverter for  |     |

|             | different values of voltage boost                                 | 136 |

# List of Tables

| Table 4.1  | Table showing the comparison of proposed converter with boost and      |     |

|------------|------------------------------------------------------------------------|-----|

|            | buck-boost converter for operating conditions with $V_i=100\text{V}$ , |     |

|            | $V_o = 566.7 \text{V}, P_o = 1000 \text{W}.$                           | 89  |

| Table 4.2  | Table showing the ripple value comparison for the specified operating  |     |

|            | condition specified in Table 4.1                                       | 90  |

| Table 4.3  | Table showing the comparison of proposed converter with boost and      |     |

|            | buck-boost converter for operating conditions with $V_i$ =100V,        |     |

|            | $V_o=300V, P_o=1000W$                                                  | 90  |

| Table 4.4  | Table showing the ripple value comparison for the specified operating  |     |

|            | condition specified in Table 4.3                                       | 91  |

| Table 4.5  | Table showing the comparison of proposed converter with boost and      |     |

|            | buck-boost converter for operating conditions with $V_i=100\text{V}$ , |     |

|            | $V_o=185.7V, P_o=1000W$                                                | 92  |

| Table 4.6  | Table showing the ripple value comparison for the specified operating  |     |

|            | condition specified in Table 4.5                                       | 93  |

| Table 4.7  | Table showing the comparison of proposed converter with Quasi-SEPIG    | С   |

|            | and Interleaved boost DC-DC converter for operating conditions with    |     |

|            | $V_i=100V, V_o=566.7V, P_o=1000W$                                      | 96  |

| Table 4.8  | Table showing the ripple value comparison for the specified operating  |     |

|            | condition specified in Table 4.7                                       | 97  |

| Table 4.9  | Table showing the comparison of proposed converter with Quasi-SEPIG    | С   |

|            | and Interleaved boost DC-DC converter for operating conditions with    |     |

|            | $V_i=100V, V_o=300V, P_o=1000W$                                        | 98  |

| Table 4.10 | Table showing the ripple value comparison for the specified operating  |     |

|            | condition specified in Table 4.9                                       | 99  |

| Table 4.11 | Table showing the comparison of proposed converter with Quasi-SEPIG    | С   |

|            | and Interleaved boost DC-DC converter for operating conditions with    |     |

|            | $V_i=100V, V_o=185.7V, P_o=1000W$                                      | 99  |

| Table 4.12 | Table showing the ripple value comparison for the specified operating  |     |

|            | condition specified in Table 4.11                                      | 100 |

| Table 5.1 | Table showing the comparison of proposed converter with Existing |     |

|-----------|------------------------------------------------------------------|-----|

|           | topologies                                                       | 137 |

| Table C.1 | Parameters for Simulation & Experimental Study                   | 158 |

# List of Abbreviation

Renewable Energy Source **RES** Government of India GoI Photovoltaic PV Ministry of New and Renewable Energy **MNRE** Maximum Power Point Tracking **MPPT** Maximum Power Point **MPP** Metal Oxide Semiconductor Field Effect Transistor **MOSFET Tapped Inductor Boost Converter TIBC** Electromagnetic Interference **EMI CBC** Classical/Conventional Boost Converter Quadratic Boost Converter **QBC** Quadratic Following Boost Converter **OFBC Buck-Boost Flyback Integrated Converter BBFIC** Floating Interleaved Boost DC-DC Converter **FIBC** Interleaved Double Dual Boost converter **IDDB** Insulated Gate Bipolar Transistor **IGBT** Continuous Conduction Mode **CCM** Discontinuous Conduction Mode **DCM** Pulse Width Modulation **PWM Proportional Integral** PΙ Printed Circuit Board **PCB** Multi-Input Multi-Output **MIMO** Safety Factor SF **VSF** Voltage Safety Factor **PIV** Peak Inverse Voltage Ultra Fast Recovery **UFR** Electric Vehicle EV Neutral Point Clamped **NPC** Voltage Source Inverter **VSI Induction Motor** IM **HEV** Hybrid Electric Vehicle **Total Harmonic Distortion** THD Phase Disposition-Pulse Width Modulation PD-PWM Medium Voltage MV Cascade H-Bridge **CHB** Flying Capacitor FC Medium Voltage High Power **MVHP VSD** Variable Speed Drive Open End Induction Motor **OEIM SV-PWM** Space Vector Pulse Width Modulation

## Introduction and Literature Survey

## 1.1 Brief Background and Present Statistics of Renewable Energy Sources (RES)

Electricity is the most acknowledged and the most crucial requirement for human being to survive. The evolution and the enlargement of the country in every sphere is largely dependent on the overall consumption of electrical energy. From the recent statistics it has been reported that India has become the third largest producer of electricity in the world. The consumption of electricity in India is also placed third in the global spectrum. The national electric grid in India has an installed capacity of 416 GW reported till 31st March 2023 [1]. The World Bank research claims that during the period 2010 and 2016 India has come up with electricity to power the houses of 30 million people each year. Although it will be a challenge to extend it to 15% of 1.25 billion of the Indian population which is still under poor infrastructure and has no proper access to electricity. However, India has done extremely well in extending access to electricity to 85% of its huge population and it has set an all-inclusive target for access to electricity for all at the end of 2030 [2][3]. India has a surfeit power generation capability but has a disadvantage that it does not have requisite infrastructure to distribute it. To deal with this issue, the Government of India (GoI) has floated a program named "Power for All" in 2016. The electricity sector in India is hugely governed by fossil fuels, particularly coal. In the fiscal year 2021-22 coal massproduced about three-quarters of the country's electricity [1]. Although in due course of time the fossil fuel reserve will get drained out and as a result the price is growing at an exponential rate. Due to the above mentioned issues it is extremely important to shift focus to Renewable Energy Sources (RES).

RES often introduced as a clean form of energy. It usually descends from natural sources or processes that are constantly refilled. There are several kinds of RES [4]:

- Solar Energy

- Wind Energy

- Hydroelectric Power

- Biomass Energy

- Geothermal Energy

#### Tidal & Wave Energy

In 2015, the government made its objective clear by aiming at a target which comprise of 175 GW energy from renewable by 2022. The intent is to process cheaper and a wider form of energy alternative. The renewable energy industry made a positive impression by belligerently spiking up the magnitude by an annual increment rate of 17.5% during the period 2014 and 2019 and strengthening the allocation of renewables in India's total energy mix from 6% to 10%. Present day scenario states that the installed capacity of the RES is of the order of 83 GW. There is a further program where 31 GW is under process and an additional 35 GW which is placed under tender. India has emerged as one of the top contenders for clean energy manufacturers in the global map. In due course of time looking at the advancement, the revised aim is installing 225 GW energy purely from renewable sources by 2022 and to reach a target of 40% clean energy by 2030. [5]

From all these energy sources Solar Photovoltaic (PV) has emerged as one of the most distinguished non-conventional energy sources. It is thriving in the recent era due to the reasons which follow as (a) it is accessible in abundance (b) inexhaustibility (c) cleaner and quieter operation (d) there is trimming in the price of the solar PV modules (e) research initiatives have been carried out due to the reduction in cost and increased efficiency of the power electronic converters required for the expulsion of the solar power and (f) government is encouraging and has been granting money to help the sector grow [6-8].

The annual report on National Solar Mission (2022-23) published by Ministry of New and Renewable Energy (MNRE) GoI states that as on 31.12.2022 a 63.3 GW of solar energy has been installed which includes installation in ground-mounted, rooftop and from off-grid systems. Additionally, a capacity of around 51.13 GW is in the stage of implementation and 31.4 GW is under tendering stage. It is expected that the solar power projects of capacity around 15 GW will be commissioned during the Financial Year (FY) 2022-23 [9].

# 1.2 Stand Alone System Based on Solar PV for Rural Deployment

There is still a large gap in infrastructure in rural areas in the sector of electricity as extension of grid is not economically feasible. This leads to a hindrance in the overall growth of the country. So, to deal with this issue the main target is the formation of RES based stand alone /off-grid systems in the rural areas. Solar PV system has been considered as the most favourable component for the following reasons (a) it is perfect for small-scale and isolated

applications, (b) placing of PV panels is not at all an issue in the rural areas, (c) India receives high level of solar insolation and (d) PV panels does not require constant maintenance. The load for such stand alone systems is single phase household appliances in the range of 250-500VA.

## 1.3 Vital Issues Regarding Designing a Stand Alone Scheme Based on Solar Photovoltaic

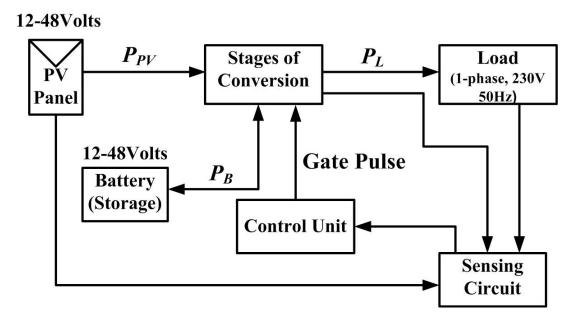

The basic block diagram of a typical solar PV based stand alone system along with the voltage levels are shown in the Fig.1.1. In the figure  $P_{PV}$  is the power from PV source,  $P_B$  denotes the battery power and  $P_L$  is the demand load power. The power output of a solar PV is sporadic in nature so it is necessary for a storage element which will balance the power between the PV modules and the demand from the load side [6]-[8]. The above mentioned storage element is mainly a battery bank. There is also requirement of a power electronic converter in a stand alone scheme to interface amongst PV panel, battery and the AC side load. It generally interfaces one DC-AC converter and two or more DC-DC converters. Here the DC-AC converter is of prime importance as the solar PV and the storage elements are in DC form whereas the load requires AC power.

Figure 1.1: Schematic for a basic stand alone system

The function of DC-DC converter is to draw maximum power from the PV panel and to protect the battery from getting overcharged or discharged. There is another purpose of DC-

DC converter which is to realize high boosting capability.

#### 1.3.1 Requirement of DC-DC converter

The standard voltage level for the AC appliances used in household services is 230V. This results in maintaining the voltage at the input of the DC-AC inverter around 360-400V, if a conventional full bridge inverter is taken into consideration for DC-AC conversion. Here the high boost voltage can be achieved by selecting PV panel and battery of higher voltages. Stepping up the PV panel voltage and that of the battery makes the design and installation complicated. There is also an issue regarding the personnel and equipment safety [10]. Taking into point that ramping up the PV voltage requires a sizeable amount of PV modules to be connected in series. This condition will lead to depletion in power because different modules connected in series will experience varying operating conditions. The voltage level of the battery can also be incremented by connecting several batteries in series. However, the employment of large number of battery bank will increase the cost as well as the size of the system. So, to keep the reliability of the system on the higher side the PV panel and the battery bank are kept in the range of 12-48V. This leads to high voltage requirement which can be fulfilled by intermediate power electronic converters. High gain can also be accomplished by the help of low frequency step-up transformer at the AC side of the inverter. But this will lead to increase in weight, cost and volume of the system. In order to reach high voltage or achieve high gain (in the order of 8-15) intermediate high gain DC-DC converters are essential which interface between the PV panel, the battery and the DC link of the inverter.

Integrating the above mentioned issues and concluding that the major opposition in designing and implementing a PV based stand alone system and operating it with a battery as a storage element are as follows:

- 1. Maximum amount of power that can be extricated from the PV panel at variable operating conditions (insolation level, temperature and loading conditions)

- 2. Allocation of bidirectional power flow for the battery.

- 3. Conversion of DC-AC.

- 4. Supplying with requisite amount of voltage gain as the voltage level(s) of PV panel and the batteries are usually clamped to a certain low value for domestic applications.

- 5. A competent control strategy which steers it through different operating modes which a typical stand alone system encounters.

Hence from the above points it can be identified that ramping up the voltage gain is

essential. The incremented gain can accomplish a voltage level suitable to be fed to the DC link of the standard inverter circuit. The voltage level should also be stable. While inverters are specifically utilised to convert DC to AC, inverter will be unable to produce the required boost. Hence, either power frequency transformer is prerequisite at the AC side of the inverter or a non-isolated DC-DC converter at the DC input of the inverter. The scheme employing transformer has advantages in providing electrical isolation, averting DC current flowing into the grid, resulting in increased safety. However, the incorporation of a low frequency transformer increases the overall weight and volume of the system and decreases the reliability of the overall system. Therefore, non-isolated DC-DC converter topologies are favored in spiking up the voltage levels.

# 1.4 Stand Alone Configuration Engaging DC-DC Converter for High Gain

Several stand alone schemes have been reported in the literature where a non-isolated DC-DC converter has provided the prerequisite boost voltage that is necessary.

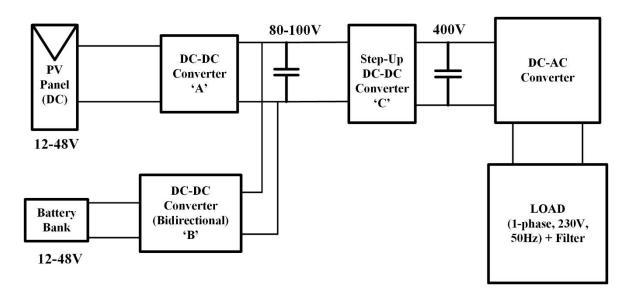

One of the schemes is a four stage configuration shown in Fig. 1.2. The diagram shows a four stage configuration where three DC-DC converters are used. Out of the three converters one of them i.e. DC-DC converter 'A' is employed in Maximum Power Point Tracking (MPPT), second bidirectional converter depicted as DC-DC converter 'B' is used in charging and discharging of battery and the final one step-up DC-DC converter 'C' is used solely for voltage boosting purpose [11]. When a PV panel collects solar radiation it produces power. The current versus voltage can be obtained by plotting it graphically (I-V curve) and the point is identified in the graph where it produces maximum power. This particular point is isolated as the maximum power output of the PV panel.

It is important to set a tracking system because it will increase the power output of the solar panel and will lead to maximize its efficiency [12],[13]. MPPT engages a DC-DC converter which interfaces the PV module and transfers the maximum power to load. Several established algorithm already reported in literature is used to vary the duty cycle of the DC-DC converter to change the load impedance and emulate it with the Maximum Power Point (MPP) of the source to transfer maximum power [14],[15].

Figure 1.2: Rudimentary four-stage framework

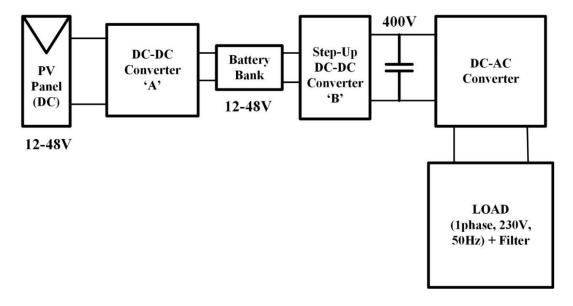

Although the configuration shown is suitable for a stand alone system, but there are some shortcomings of the scheme. The greater number of conversion stages will invariably diminish the reliability and efficiency of the overall system as the number of component count increases. There is depletion in battery charging efficiency as there are two converters present in the battery charging path. The DC-DC converter 'A' used for MPPT control remains inactive when the PV power is low. So, keeping a check on the above mentioned issues a three stage configuration is shown in Fig. 1.3 where a single DC-DC converter is present between the PV panel and the battery charging path as a result increasing the battery efficiency [16].

Figure 1.3: Three stage framework with battery bank incorporated in cascade

Here the DC-DC converter has to be designed carefully as the converter single handedly is responsible for the voltage gain, if the battery bank voltage is not high. So, from the above schematic it can be decided that intermediate converter with high step-up characteristics is very essential in the stand alone structure. Therefore, in the thesis the high step-up DC-DC converter will be taken up as the main form of study and analysis. Starting from analysis, literature survey, limitations of some of the boost converters will be discussed in the following sections.

### 1.5 High Gain DC-DC converter

So initially starting with different types of DC-DC converters given below, the preliminary study is formed.

Some of the basic non-isolated DC-DC converters are as follows:

- > Step-down (buck) converter

- Step-up (boost) converter

- Step-down/step-up converter (buck-boost)

- > Cu'k converter

Out of these four non-isolated converters the main objective is to ramp up the voltage. So, step-up converter or Classical Boost Converter (CBC) is the most fundamental and essential topology in the family of boosts converters (non-isolated).

### 1.5.1 Classical Boost Converter (CBC)

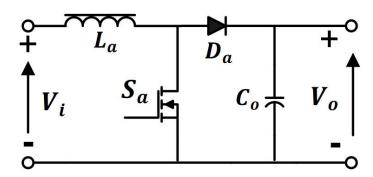

Fig. 1.4 shows the topology of a step-up converter/CBC. The main property of the converter as the name suggests is to obtain a higher voltage level than what is fed to the input of the converter. There are several applications to this converter but few of the highlights are that it is used in regulated DC supplies and DC motor regenerative braking [17].

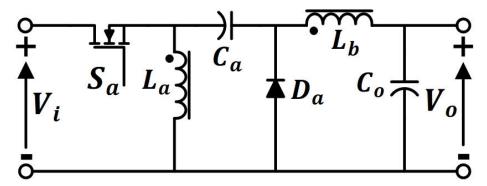

Figure 1.4: Schematic of a Classical Boost Converter

## A. Operating Principle

When Switch Sa turned ON

At this instant the diode  $D_a$  becomes reverse biased. The load current is supplied by the output capacitor  $C_o$ . The input  $V_i$  feeds energy to the inductor  $L_a$ . The inductor stores energy and the current through the inductor increases.

When Switch turned Sa OFF

During this interval the polarity of the voltage across the inductor  $L_a$  reverses. This condition along with the input voltage forward biases the diode  $D_a$ . The current along the inductor diminishes and transfers the energy to the capacitor  $C_o$  and the output load.

Figure 1.5: Inductor voltage and current waveform during Continuous Conduction Mode for CBC

From the Fig. 1.5, during steady state the time integral taken for the inductor voltage over one time period will be zero.

Therefore

$$V_i t_{on} + (V_i - V_o) t_{off} = 0$$

(1.1)

From equation number (1.1)

The voltage gain of CBC is given as:

$$\frac{V_o}{V_i} = \frac{1}{1 - D}$$

(1.2)

Where,  $V_0$  is the total output voltage.

$V_i$  is the input voltage fed to the converter.

D is the duty ratio of the converter.

*ILa* is the average inductor current

Duty Ratio=

$$D = \frac{V_o}{V_i} = \frac{t_{on}}{t_{on} + t_{off}}$$

(1.3)

Here, *ton* is the time during which the switch remains ON.

toff is the time during which the switch remains OFF.

And

$$T = t_{on} + t_{off}$$

(1.4)

T is the total time period.

The boost converter can achieve the target voltage level but it has several limitations. The drawbacks are:

- 1. High duty cycle is mandatory for high voltage applications.

- 2. Instability of closed loop control at high Duty Ratio due to sharp rise in voltage gain.

- 3. Reduced Efficiency.

- 4. Reverse recovery problem of the diode used in the boost circuit.

- 5. Voltage stress across the switch is high. So switches with higher RDS(on) is required.

- 6. Higher level of conduction losses due to high *RDS(on)* of the switch.

The RDS(on) described in point 5 and 6 indicates the drain to source on resistance. It is the drain to source resistance of the Metal Oxide Semiconductor Field Effect Transistor (MOSFET) switch (considering MOSFET is used in Boost hardware topology). RDS(on) is directly proportional to the square of the voltage blocking capability. As discussed in point number 5 rise in RDS(on) increases the conduction losses (I<sup>2</sup>R loss) which implies the decrease in overall efficiency of the converter[18],[19].

To illustrate the point 1 in the above mentioned drawback section. A curve is plotted with Voltage Gain versus Duty Cycle for CBC. The Fig. 1.6 shows the plot, where it has been vividly seen that with increase in the boost voltage there is a significant jump in the duty ratio. A point is marked on the plot which signifies the claim that for a gain of 10 the duty

ratio has risen sharply to 0.9 which is very close to unity. Extreme duty cycle operation for obtaining the voltage gain is the originator of several difficulties. It brings into the picture the parasitic element associated with the passive components which can degrade the gain value at high duty cycle. The current and the voltage stress across the semiconductor elements also rises to significant level leading to diminishing the overall efficiency of the converter [20],[21]. Taking an example to understand the role of parasitic element better, if the internal resistance of the coil is considered it is observed that with duty ratio approaching towards unity the gain value degrades significantly. Although the parasitic element does not play a significant role when the duty ratio is at around 0.5, this proves as the duty cycle reaches a high value the parasitic elements of the passive components pose a threat to the efficiency of the converter [24].

Figure 1.6: Voltage versus Duty Cycle of a CBC

There are several boost topologies apart from CBC which is very well articulated in various research studies. From several boost topologies one of the most highly researched boost topology is the Tapped Inductor Boost topology. Here in the next section the circuit will be studied and explained with various literature references.

### **1.5.2** Tapped Inductor Boost Converter (TIBC)

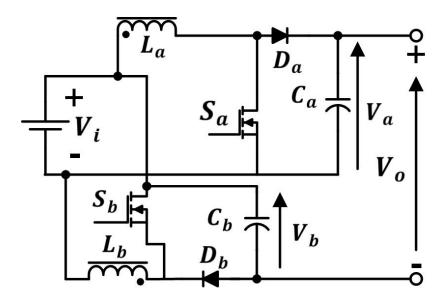

The Fig. 1.7 shows the topology of TIBC. It is very favorable topology where the inductor of the boost converter is tapped like an autotransformer either at the switch or at the diode.

Tapping the inductor has the convenience that the converter duty cycle at the operating

point can be rearranged to achieve a distinctive value at which the device utilization will get enhanced. The tapped versions are categorized mainly into two types [22]:

- Switch tapped- Here the switch is linked to the point where the inductor is tapped and not to one of the extreme points of the inductor.

- Diode tapped- Similarly here the diode is linked to the tapped point of the inductor and not to any of its end.

Figure 1.7: Schematic of a Tapped Inductor Boost converter

Through TIBC a boost capability can be obtained without extreme duty cycle requirement and lower amount of stress on the semiconductor devices. The boosting in this topology is of a higher level as the inductance involved during discharging has an inflated value because it is considered as equivalent. It can be observed in the converter working principle. The operating principle of the TIBC is explained below [23].

### A. Operating Principle

When Switch Sa turned ON

In the duration of conduction of switch  $S_a$ , the diode  $D_a$  becomes reverse biased due to the reverse polarity of voltage across the inductor  $L_b$ . The input feeds the inductor  $L_a$  and the energy is stored in it and there is an increase of current through the inductor.

When Switch Sa turned OFF

At the instant of turn OFF of the switch, the diode  $D_a$  starts to conduct and the energy which was stored in the inductor  $L_a$  now starts to discharge through both the inductors  $L_a$  and  $L_b$ .

The voltage gain of TIBC is given as:

$$\frac{V_o}{V_i} = \frac{1 + \left(\frac{N_2}{N_1}\right)D}{1 - D} = \frac{1 + ND}{1 - D}$$

(1.5)

Where,  $N_2$  is the number of turns in the inductor  $L_2$ .

$N_I$  is the number of turns in the inductor  $L_I$ .

D is the duty ratio of the converter.

TIBC can achieve the high boost but it has some limitations which are discussed below:

- Leakage inductance will be present as in practical inductors there will considerable amount non-ideal coupling. This non-ideal flux coupling between the two coils gives rise to high voltage spikes across the semiconductor devices leading to considerable amount of losses.

- 2. The peak to peak ripple for the input current is higher compared to a conventional boost converter.

Extensive research has been conducted in this domain to deal with the shortcomings of TIBC. Various techniques have been employed to combat this above mentioned issues and it is very distinctively articulated in various research papers.

In [24] a single switch topology is proposed where two taped inductors are employed along with diodes and capacitor to attain the boosting capability. The topology is rearranged further in such a way such that it retains the same boosting capacity but the stress across the semiconductor devices is reduced. The high voltage spike due to non-ideal flux coupling also gets diminished to lower level. At around 0.5 duty cycle it is able to deliver high gain and in addition the current stress across the switch reduces which enables it to improve its efficiency.

The steady state performance of TIBC is analyzed. Comparison has been done between a TIBC and CBC on same output parameters such as output voltage and output current [25]. It has been noted theoretically that taking into account the parasitic parameters generated from the various components in the circuit, TIBC has a higher gain value than CBC when operating under same duty ratio. Thus, the efficiency of TIBC tends to be higher than CBC operating under similar parameters. Experimental results also confirmed the theoretical claim that TIBC offers better voltage gain and efficiency under equivalent parameter selection.

Here a topology is proposed that cascades a traditional boost converter and connects a TIBC in series for maximum voltage boosting capability. In order to increment the boost

voltage, the duty ratio and the turns ratio is simultaneously used. This increases the boost capability to manifold compared to a traditional converter [26].

A boost converter along with a tapped inductor has been introduced to negate the input current ripple. A capacitor and inductor aids in reducing the input current ripple in the circuit, without increasing the Electromagnetic Interference (EMI) and degrading the reverse recovery problem of the diode. The tapped inductor can be easily registered by attaching an extra tap in the main inductor of the Classical/Conventional Boost Converter (CBC) [27]. The weight and volume of the converter remains lower compared to the CBC with an input LC filter, as the inductor and the capacitor does not handle the total power. A soft switched tapped boost converter is proposed [28]. Here the soft switching has a wide operating range and function under a wide duty ratio and varied load conditions. The voltage stress across the active switch is below the load voltage and the current stress is also below permissible limit. The topology can be utilised in power factor correction circuits due its wide operating range.

As TIBC is one of the many boost topologies, there are several other non-isolated converter topologies that produce the boost voltage which is required without much complication. Another boost topology which can provide a considerable amount of gain without much duty cycle requirement is the Quadratic Boost Converter (QBC) which is discussed in the following section with its benefits and voltage gain.

#### 1.5.3 Quadratic Boost Converter (QBC)

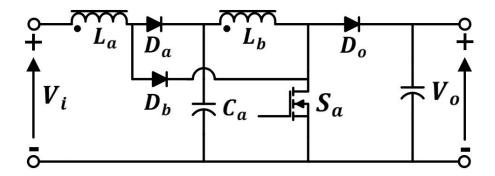

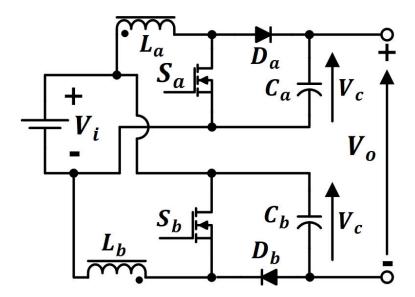

Figure.1.8: Schematic of a Quadratic Boost Converter

Fig. 1.8 shows the QBC topology. In QBC the voltage conversion ratio is related to the duty ratio in a quadratic way. This leads to a very high voltage conversion ratio which is desirable. QBC is arranged in such a way such that two CBC converters are connected in

cascade providing the high gain which amounts to high conversion ratio and efficiency. The QBC is basically a single switch topology which provides an advantage compared to cascading two boost converters. Here as QBC is a single switch topology as the other switch is replaced by a diode the driver circuit requirement also vanishes which in turn enhances the efficiency and diminishes the complexity of the total system [29],[30].

### A. Operating Principle

When Switch Sa turned ON

The diode  $D_a$  gets reverse biased due to the opposite polarity of the inductor  $L_a$ . The input  $V_i$  provides energy to the inductor  $L_a$ . As the diode  $D_b$  is forward biased the inductor current flows through the diode  $D_b$  to the switch. The capacitor  $C_a$  discharges to the inductor  $L_b$  so the energy is stored in  $L_b$ . The capacitor  $C_o$  discharges to the load and the diode  $D_o$  is reverse biased.

When Switch Sa turned OFF

The diode  $D_0$  is forward biased due the polarity change in the inductor  $L_b$ . The energy which was stored in  $L_b$  discharges to the output. Diode  $D_b$  gets reverse biased and the inductor current ramps down and flows through the capacitor  $C_a$  and  $L_b$ . The inductor current of the inductor  $L_b$  flows to the output via the forward biased diode  $D_0$ .

The voltage gain of QBC is given as:

$$\frac{V_o}{V_i} = \frac{1}{(1-D)^2}$$

(1.6)

Here *D* is the duty ratio of the converter.

The equation number (1.6) shows that the voltage ratio is dependent on the square of the duty cycle. This leads to a very high step-up gain for the converter. However, the major hindrance in QBC is that the voltage and the current stress across the switching device are quite high.

In [31] a topology is proposed which is built on the idea of QBC. Here the conversion ratio is ramped up by integrating coupled inductor and switched capacitor technique. A clamped capacitor is inserted in the switch path to clip the voltage across it. The efficiency of the converter increases as the leakage energy of the coupled inductor could be revitalized.

High voltage can also be acquired by integrating a voltage multiplier with the standard

QBC [32]. The major limitation of QBC is the voltage stress is very high across the switching devices. The stress across the semiconductor device can be restricted to a permissible level by employing this topology.

QBC has the ability to ramp up the voltage gain but the conversion ratio becomes sensitive at high duty ratio. This brings forward controlling factors which deteriorate at higher duty ratio range. So, a Quadratic Following Boost Converter (QFBC) is proposed [33]. The circuit comprises of three capacitors and diodes, two switches and two inductors. A duty ratio increase will give rise to the voltage gain, maintaining a balance in the high duty ratio range but with less sensitivity. The voltage gain of the converter is given as:

$$\frac{V_o}{V_i} = \frac{1 - D + D^2}{(1 - D)^2} \tag{1.7}$$

Here *D* is the duty ratio of the converter.

The gain equation number (1.7) for QFBC differs with gain equation number (1.6) for QBC in the numerator part which brings in the extra gain for the converter.

A quadratic boost converter is proposed with a voltage gain that is quite high and possesses reduced voltage stress at the semiconductor devices [34]. Here an additional coupled inductor is integrated to the circuit to increase the gain. Clamp circuit has been included to nullify the effect of leakage inductance as there is presence of coupled inductors. Similarly, a quadratic converter in combination with coupled inductor topology is discussed [35]. Higher voltage gain can be obtained along with reduction in the voltage stress. Quadratic buck-boost converters are proposed with wide range of conversion ratios [36]-[38]. The converter topology [36] possesses low input current and quadratic gain characteristics. The gain of the converter can be further expanded with the help of diode capacitor multiplier cell circuitry. The inductor size also diminishes with the reduction in input current ripple, which serves as a merit to this topology. In [37] the topology can operate as a quadratic boost as well as quadratic buck converter. The wide range of conversion ratio allows the converter to have a broader application range (battery charging, UPS etc). Wide conversion spectrum can be achieved without operating the converter at extreme high or low duty cycle. If the converter had to operate under extreme duty cycle then there would be various issues which are specifically discussed in section 1.5.1.

Voltage lifting technique can also be applied to step-up the output voltage. There are various research works on the voltage lifting technique. This topology has been broadly discussed in the next section.

#### 1.5.4 Voltage Lift Techniques