# NATURAL MITIGATION OF VOLTAGE HARMONICS IN INVERTERS WITH HIGH DC BUS UTILIZATION

## Thesis submitted by

## SUKANYA DASGUPTA

**Doctor of Philosophy (Engineering)**

Department of Electrical Engineering

Faculty Council of Engineering & Technology

Jadavpur University

Kolkata, India

2023

## Index No.- 29/16/E

Title of the Thesis: Natural Mitigation of Voltage

Harmonics in Inverters with High DC

**Bus Utilization**

Name, Designation & Institution of

the Supervisor:

Name: Prof. Sujit K. Biswas

Designation: Former Professor

Department: Electrical Engineering Institution: Jadavpur University,

Kolkata, West Bengal, India, Pin-700032 List of Publications:

- 1. **S. Dasgupta**, D. Maiti, S. K. Biswas, "Single Phase Sine-Wave Inverter with High DC Bus Utilization using Natural Compensation," Accepted for the Jordan Journal of Electrical Engineering [Scopus].

- 2. **S. Dasgupta,** S. K. Biswas, "Three-phase Sine Wave Inverter using Natural Harmonic Compensation," IEEE Calcutta Conference (CALCON), 2020, 521–525. doi:10.1109/CALCON49167.2020.9106544

List of Patents:

Nil

List of Presentations In National/ International/ Conferences/ Workshops: 1. **S. Dasgupta**, S. K. Biswas, "Three-phase Sine Wave Inverter using Natural Harmonic Compensation," *IEEE Calcutta Conference* (*CALCON*), 2020, 521–525. doi:10.1109/CALCON49167.2020.9106544

# FACULTY OF ENGINEERING & TECHNOLOGY JADAVPUR UNIVERSITY

# "Statement of Originality"

I, Mrs. Sukanya Dasgupta registered on 4<sup>th</sup> October, 2016 do hereby declare that this thesis entitled "Natural Mitigation of Voltage Harmonics in Inverters with High DC Bus Utilization" contains literature survey and original research work done by the undersigned candidate as part of Doctoral studies.

All information in this thesis have been obtained and presented in accordance with existing academic rules and ethical conduct. I declare that, as required by these rules and conduct, I have fully cited and referred all materials and results that are not original to this work.

I also declare that I have checked this thesis as per the "Policy on Anti Plagiarism, Jadavpur University, 2019", and the level of similarity as checked by iThenticate software is 9%.

Signature of the Candidate:

Date:

Certified by Supervisor: (Signature with date & seal)

Dr. Sujit K. Biswas Former Professor & Head Department of Electrical Engineering Jadavpur University, Kolkata-700032

iv

# FACULTY OF ENGINEERING & TECHNOLOGY JADAVPUR UNIVERSITY

## CERTIFICATE FROM THE SUPERVISOR

This is to certify that the thesis entitled "Natural Mitigation of Voltage Harmonics in Inverters with High DC Bus Utilization" submitted by Mrs. Sukanya Dasgupta who got his name registered on 4th October, 2016 for the award of Ph.D. (Engineering) degree of Jadavpur University, is absolutely based upon his own work under the supervision of Prof. Sujit K. Biswas, Former Professor, Electrical Engineering Department, Jadavpur University and that neither his thesis nor any part of the thesis has been submitted for any degree/diploma or any other academic award anywhere before.

July 12023

**Prof. Sujit K. Biswas** (Signature of the Supervisor with date & Office Seal)

Dr. Sujit K. Biswas Former Professor & Head Department of Electrical Engineering Jadavpur University, Kolkata-700032

# **Dedicated**

To My Husband

## **ABSTRACT**

Switching inverters are used to supply loads which normally require a sinusoidal voltage waveform. Any harmonic present in the supply from the inverter causes the flow of harmonic currents through the load, resulting in undesired behaviour from the load and additional kVA loading of the inverter. However, high efficiency power electronic inverters produce only flat-topped waveforms with sharp voltage rise and fall due to the switching mode of operation of the power semiconductor switches. Thus, additional low-pass filters are required at the inverter output to filter out the harmonic content in the generated voltage and deliver only the fundamental waveform to the load. However, filters only attenuate the harmonics and hence a large size of filter is often needed to bring down the Total Harmonic Distortion (THD) of the inverter voltage waveform to acceptable limits. Alternatively, special Pulse Width Modulation (PWM) schemes are used, that generate reduced voltage harmonics at the cost of reduced fundamental voltage output (reduced DC bus utilization).

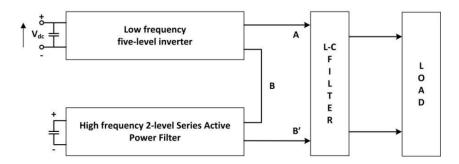

Some researchers have demonstrated that instead of using a bulky filter, an additional power converter circuit can be connected in series with the inverter output to reduce its harmonic content. This additional circuit can be designated as a harmonic compensator, which generates exactly the same amount of harmonics present in the inverter output, but in phase opposition. Thus, the resulting final output to the load is free of harmonics. However, the additional converter requires an isolated power supply, being another switching power stage. As a result, several research work has been directed towards development of a power stage that does not require an additional power supply and the concept of Natural Compensation of harmonic voltages is an attractive issue.

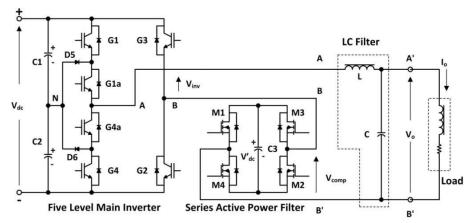

The work envisaged in this thesis is directed towards investigating the techniques of Natural Mitigation of harmonics along with achieving higher fundamental voltage compared to the conventional schemes using Sinusoidal Pulse Width Modulation (SPWM). A new fixed frequency single phase sine wave inverter topology is investigated, having high DC bus utilization. The main inverter uses six IGBT switches operating at low frequency in over-modulation mode to create a five stepped voltage waveform, thus having low switching losses with high DC bus utilization. A series connected active compensator using power MOSFETs helps to remove the major harmonic voltages. No isolated DC power supply is required across the compensator as it is based on the principle of natural compensation. The DC bus voltage needed for the compensator is about half of the inverter, thus the compensator has low switching loss even at the designated switching frequency.

A three phase inverter system is investigated which produces a near sinusoidal three phase voltage output at fixed fundamental frequency with low switching loss. Since the inverter system comprises of fixed waveform, it is not possible to control the output voltage other than by adjusting the DC bus voltage of main inverter. However, introduction of low frequency Pulse Width Modulation permits output voltage adjustment within the inverter. Thus a new three phase inverter system at over-modulation with SPWM control scheme along with compensator is investigated to get high dc bus utilization and low THD. The switching frequency components of the compensator remains in the output as they are not compensated, necessitating the use of a small filter at the output to attenuate them. Thus the use of higher switching frequency in the compensator permits the use of a small filter at the output to attenuate the switching frequency components.

## **ACKNOWLEDGEMENT**

I would like to express my gratitude to the supervisor Prof. (Dr.) Sujit Kumar Biswas, Department of Electrical Engineering, Jadavpur University, for allowing me do this research work where I got to know the functioning of every component involved and also helped me to formulate a systematic approach to a problem guided by empirical formulae and practical guidelines. It would not have been possible without his kind support and constant inputs to complete this PhD research work. I am highly indebted to Mr. Dipten Maiti, Assistant Professor, Department of Electrical Engineering, Jadavpur University for his guidance as well as for providing necessary information regarding the research work. I would also like to express my sincere thanks to the Head of the Department, Professor Biswanath Ray, Department of Electrical Engineering, Jadavpur University, for his encouragement and constant support. Last but not the least my thanks and appreciations also go to my family and parents in developing the project who have willingly helped me out with their abilities and encouragement.

September 2023

Jadavpur University

Kolkata-700032

Sukanya Dasgupta

Suhampa Dasqueh

# **Contents**

| Abstract    |                                                | vii   |

|-------------|------------------------------------------------|-------|

| Acknowled   | dgement                                        | ix    |

| List of Fig | ures                                           | xiii  |

| List of Tal | bles                                           | xviii |

| List of Abl | breviation                                     | xix   |

|             |                                                |       |

| Chapter 1   |                                                |       |

| Int         | roduction                                      |       |

| 1.1         | Power Electronics Inverter System              | 1     |

| 1.2         | Classification of Inverters                    | 2     |

|             | 1.2.1 Single Phase Inverter                    | 2     |

|             | 1.2.2 Three Phase Inverter                     | 6     |

| 1.3         | DC Bus Utilization of Inverter                 | 10    |

|             | 1.3.1 Square Wave Operation                    | 10    |

|             | 1.3.2 PWM Operation                            | 11    |

| 1.4         | Voltage Control in Inverters                   | 16    |

|             | 1.4.1 Single Pulse Width Modulation Technique  | 16    |

|             | 1.4.2 Multiple Pulse Width Modulation          | 18    |

|             | 1.4.3 Sinusoidal Pulse Width Modulation (SPWM) | 19    |

|             | 1.4.4 Space Vector Modulation (SVM)            | 20    |

| 1.5         | Harmonics in Inverters                         | 22    |

|             | 1.5.1 Source of Harmonics in Inverters         | 23    |

|             | 1.5.2 Problems Caused by Inverter Harmonics    | 23    |

|             | 1.5.3 Techniques of Harmonic Elimination       | 24    |

| 1.6         | Closed Loop Operations of Inverter             | 30    |

| 1 7         | Outline of the Thesis                          | 31    |

| Chapte | er 2 |                                                                                                  |

|--------|------|--------------------------------------------------------------------------------------------------|

|        |      | ew of Techniques for Mitigation of Voltage Harmonics and Improved DC<br>Utilization in Inverters |

|        | 2.1  | Introduction                                                                                     |

|        | 2.2  | Different Configuration of Inverters                                                             |

|        | 2.3  | Techniques for Improved DC Bus Utilization                                                       |

|        | 2.4  | Techniques for Mitigation of Voltage Harmonics37                                                 |

|        | 2.5  | Natural Compensation of Harmonics41                                                              |

|        | 2.6  | Conclusion42                                                                                     |

| Chapte | Sine | Wave Inverter with High DC Bus Utilization Using Natural Harmonic                                |

|        | 3.1  | Introduction                                                                                     |

|        | 3.2  | Proposed Scheme44                                                                                |

|        | 3.3  | The Operation of Proposed Inverter47                                                             |

|        |      | 3.3.1 Principle of Operation of Main Inverter47                                                  |

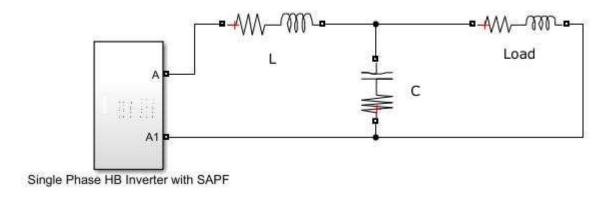

|        |      | 3.3.2 Principle of Operation of SAPF                                                             |

|        |      | 3.3.3 Maintenance of Charge across Capacitor of SAPF49                                           |

|        |      | 3.3.4 Principle of operation of low pass L-C filter                                              |

|        | 3.4  | Control Pulse Generation Scheme                                                                  |

|        | 3.5  | Simulation Results51                                                                             |

|        | 3.6  | Experimental Validation                                                                          |

|        | 3.7  | Efficiency Calculation                                                                           |

|        | 3.8  | Comparison of Performance                                                                        |

|        | 3.9  | Applications61                                                                                   |

|        | 3.10 | Conclusion61                                                                                     |

| Chapte | er 4 |                                                                                                  |

|        |      | e Phase PWM Inverter with High DC Bus Utilization using Natural pensation                        |

|        | 4.1  | Introduction63                                                                                   |

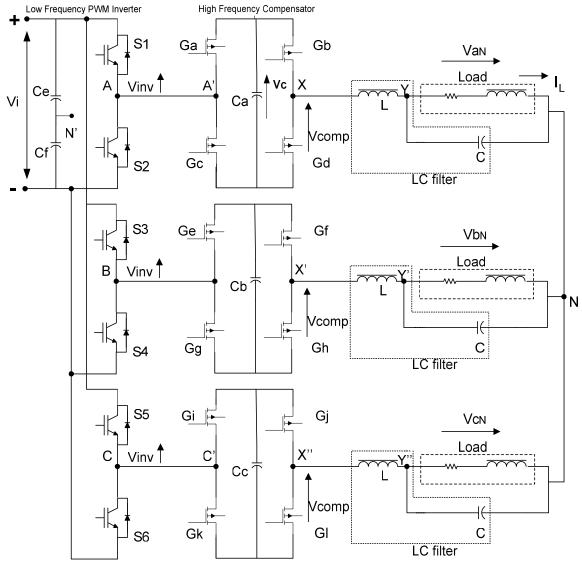

|        | 4.2  | The Proposed Three Phase Inverter70                                                              |

| 4.3       | The Operating Principle of Proposed Inverter71                  |       |  |  |

|-----------|-----------------------------------------------------------------|-------|--|--|

| 4.4       | Control Pulse Generation Scheme                                 |       |  |  |

| 4.5       | Performance Analysis                                            |       |  |  |

|           | 4.5.1 Simulation Results                                        | 75    |  |  |

|           | 4.5.2 Experimental Results                                      | 78    |  |  |

| 4.6       | Efficiency Calculation                                          | 80    |  |  |

| 4.7       | THD Analysis8                                                   |       |  |  |

| 4.8       | Comparative Study                                               | 82    |  |  |

| 4.9       | Proposed Topology for Open End Winding Transformer Coupled Load | 84    |  |  |

| 4.10      | Conclusion                                                      | 89    |  |  |

|           |                                                                 | ••••• |  |  |

| Thi       | ree Phase Sine PWM Inverter using Natural Harmonic Compensation |       |  |  |

| 5.1       | Introduction                                                    | 91    |  |  |

| 5.2       | The Proposed Inverter                                           | 92    |  |  |

| 5.3       | The Operating Principle of Proposed Inverter                    | 94    |  |  |

| 5.4       | Control Pulse Generation Scheme.                                | 96    |  |  |

| 5.5       | Simulation Results                                              | 97    |  |  |

| 5.6       | THD Analysis                                                    | 104   |  |  |

| 5.7       | Conclusion.                                                     | 106   |  |  |

| Chapter 6 |                                                                 | ••••• |  |  |

| Coi       | nclusion and Future Scope                                       |       |  |  |

| 6.1       | Conclusion                                                      | 107   |  |  |

| 6.2       | Future Scope                                                    | 108   |  |  |

| REFEREN   | CES                                                             | 109   |  |  |

| PUBLICA'  | ΓΙΟΝS                                                           | 114   |  |  |

| APPENDI   | X                                                               | 115   |  |  |

# **List of Figures**

- Fig. 1.1(a) Single-phase half bridge VSI, (b) Single-phase full bridge VSI

- Fig. 1.2a) Output of Half Bridge Inverter, b) Output of Full Bridge Inverter

- Fig. 1.3 Square waveform approximation with a limited number of harmonics

- Fig. 1.4 Waveforms for ideal half-bridge voltage source inverter using square-wave modulating technique: (a) ac output voltage and (b) FFT spectrum of the output voltage

- Fig. 1.5 A 3-phase Voltage Source Inverter (VSI) feeding a balanced load

- Fig. 1.6 (a) Timing diagrams of the switches in three phase inverter;(b)Phase voltage waveforms of a 3-phase square wave VSI; (c) Line voltage waveforms of a 3-phase square wave VSI

- Fig. 1.7(a) Equivalent load circuit during conduction of Sw5, Sw6 and Sw1

- Fig. 1.7(b): Equivalent load circuit during conduction of Sw6, Sw1 and Sw2

- Fig. 1.8 Voltage control by varying ma

- Fig. 1.9 Pulse width modulation scheme

- Fig. 1.10 PWM in three phase inverter

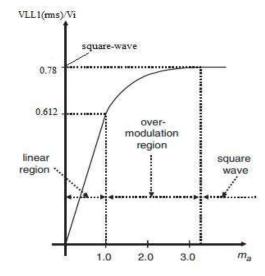

- Fig. 1.11 V<sub>LL</sub> vs m<sub>a</sub> curve of three phase inverter

- Fig. 1.12 Single phase inverter with sinusoidal PWM scheme; (a) Full bridge inverter, (b) Bipolar PWM scheme

- Fig. 1.13 Single phase full bridge inverter with uni-polar sinusoidal PWM scheme

- Fig. 1.14 Single pulse width modulation

- Fig. 1.15 Harmonic profile of single pulse width modulation

- Fig. 1.16 Multiple pulse width modulation

- Fig. 1.17 Harmonic profile of multiple pulse width modulation

- Fig. 1.18 Sinusoidal pulse width modulation

- Fig. 1.19 Harmonic profile of sinusoidal pulse width modulation

- Fig.1.20 The space-vector representation

- Fig. 1.21 Harmonics in Power System

- Fig. 1.22 Stepped wave inverters

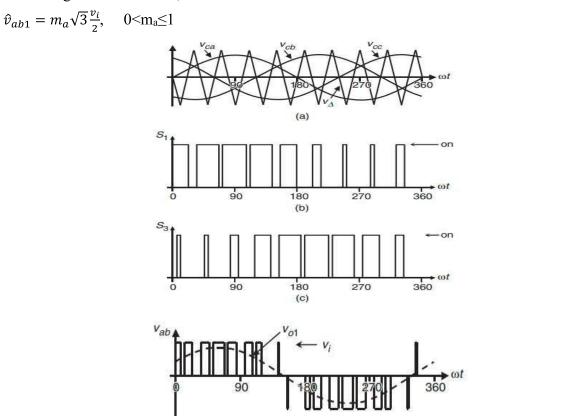

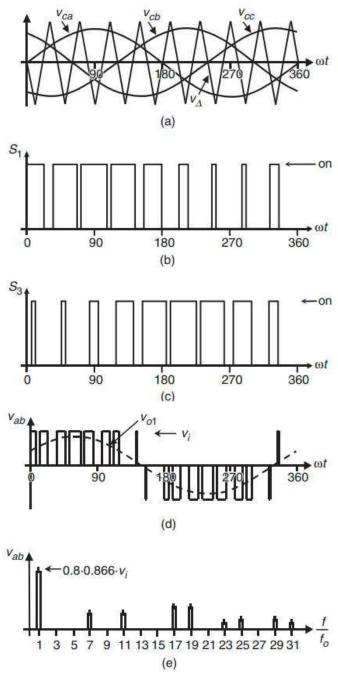

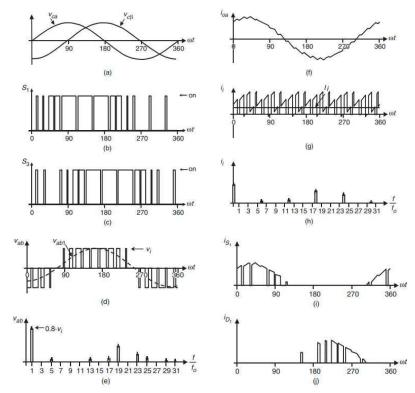

- Fig. 1.23 Ideal waveforms for three phase SPWM- VSI: (a) modulating and carrier waveforms; (b) state of switch  $S_1$  state; (c) state of switch  $S_3$  state; (d) line-line output voltage; (e) spectrum of output voltage

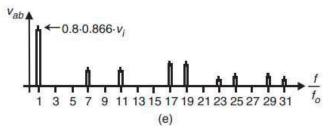

- Fig. 1.24 a) Single-phase structure of a multilevel cascaded H-bridge inverter, b) Output ac phase voltage of a 11-level cascaded inverter with isolated dc sources

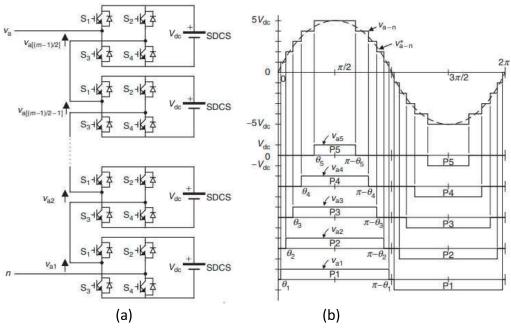

- Fig. 1.25 Waveforms for ideal three-phase VSI with SHE modulation: (a) phase voltage  $v_{aN}$  for  $5^{th}$  &  $7^{th}$  harmonic elimination; (b) phase voltage spectrum; (c) line voltage  $v_{ab}$  for  $5^{th}$  &  $7^{th}$  harmonic elimination; (d) line voltage spectrum.

- Fig. 1.26 Equivalent circuit of one limb of the inverter in series with a auxiliary inverter

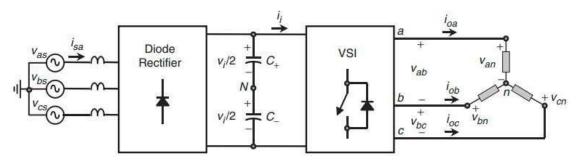

- Fig. 1.27 Three-phase VSI topology with a diode-based front-end rectifier

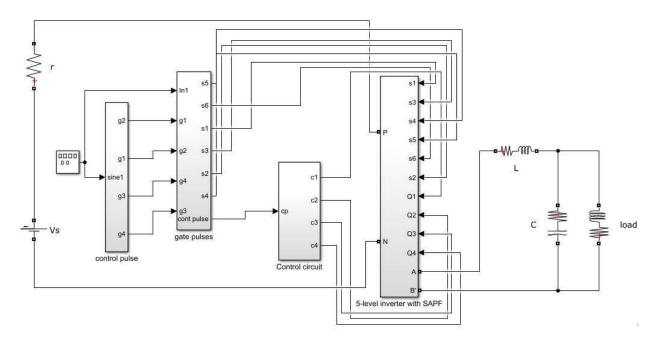

- Fig. 3.1 Proposed scheme of sine-wave inverter using a multi-level inverter with a series active power filter

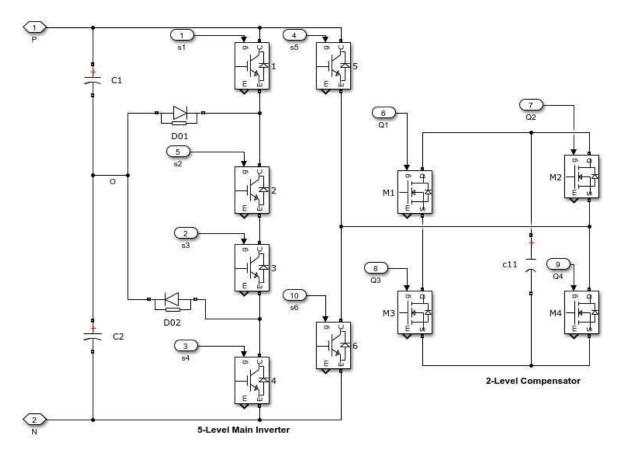

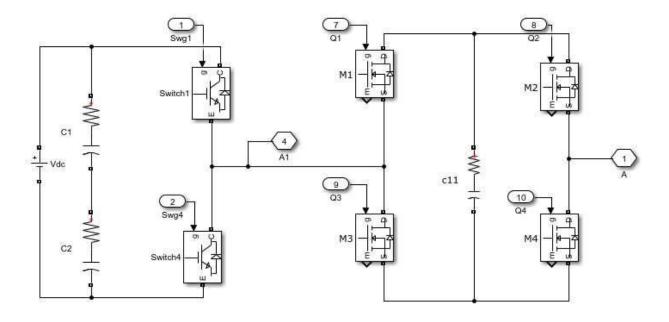

- Fig. 3.2 The proposed 1-phase sine-wave inverter power circuit

- Fig. 3.3 Schematic of stepped wave voltage generation in proposed inverter

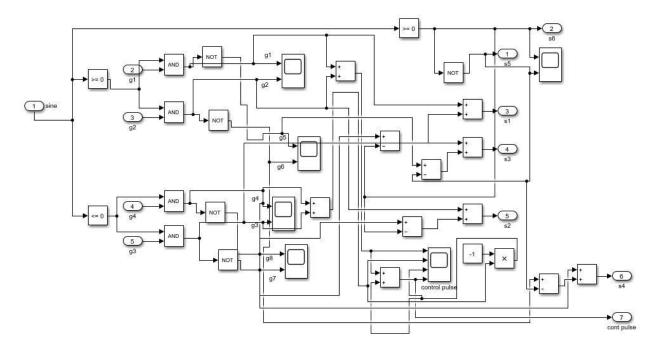

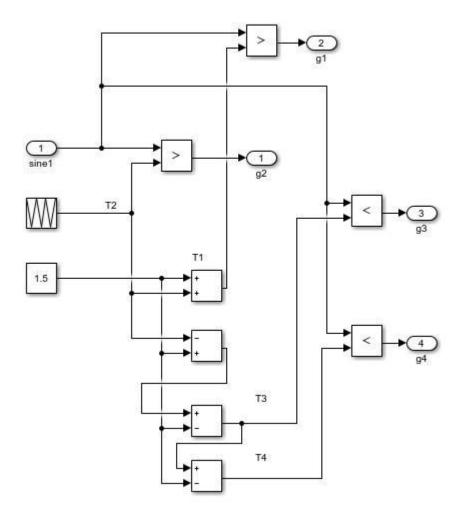

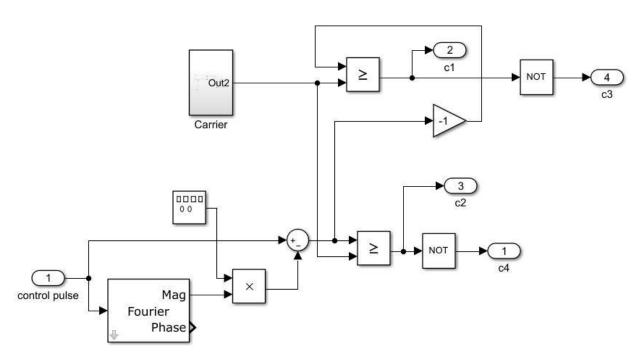

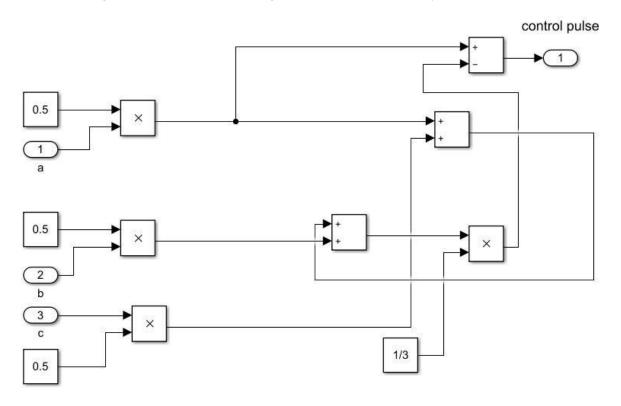

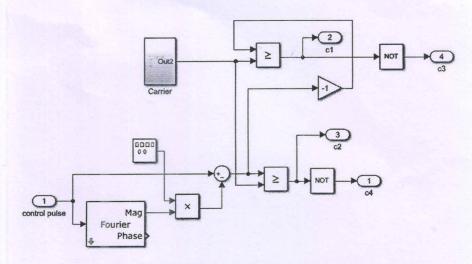

- Fig. 3.4 Block diagram of the scheme for gate pulse generation scheme

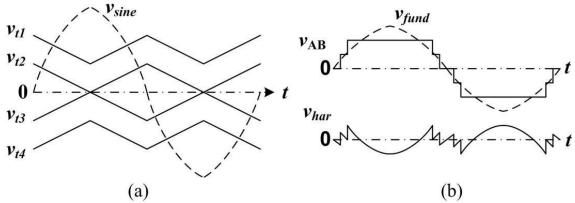

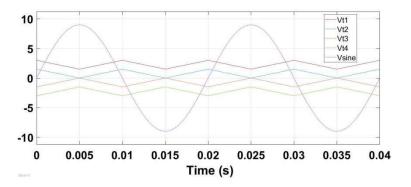

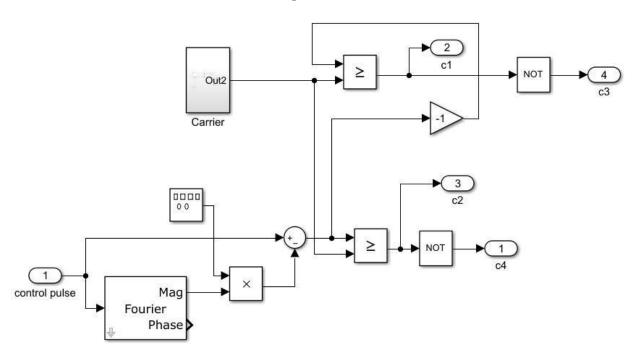

- Fig. 3.5 (a) Principle of over-modulated SPWM pulse generation for the main inverter control; (b) Principle of reference generation for SAPF (or compensator)

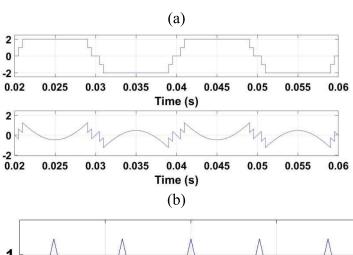

- Fig. 3.6 Simulated waveforms: (a) modulating and carrier signal for pwm in main inverter; (b) top: reference signal for pwm in SAPF; bot: modulating signal for pwm in SAPF; (c) carrier signal for SAPF; (d) different gate signals of the six IGBTs in main inverter; (e) different gate signals of the four MOSFETs in auxiliary inverter

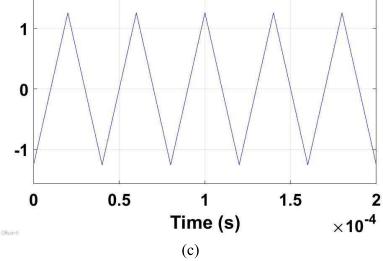

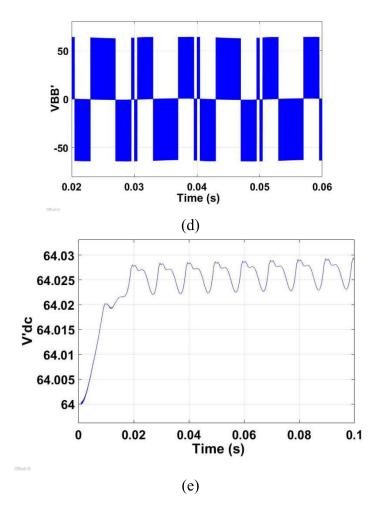

- Fig. 3.7 Simulated waveforms: (a) top: voltage across terminals A & N; mid: voltage across terminals B & N; bot: voltage across terminals A & B; (b) voltage across terminals A & B'; (c) top: load current; bot: output voltage across load; (d) voltage across terminals B & B'; (e) output voltage across C3

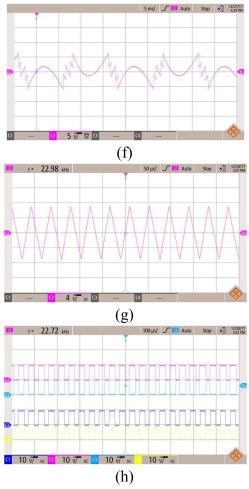

- Fig. 3.8 Experimental waveforms: (a) Modulating Signal and Triangular Signal ( $v_{t2}$ ,  $v_{t3}$ );(b) Modulating Signal and Triangular Signal ( $v_{t1}$ ,  $v_{t4}$ );(c) Gate signals for G4, G1a in Main Inverter;(d) Gate signals for G3, G2 Main Inverter;(e) Reference Signal for SAPF(f) Modulating signal for PWM in SAPF;(g) Carrier Signal for PWM in SAPF;(h) Gate signals for the MOSFETs in SAPF

- Fig. 3.9 Experimental waveforms: (a) top: voltage across terminals A & N; mid: voltage across terminals B & N; bot: voltage across terminals A & B; (b) top: voltage across terminals A & B'; bot: output voltage across load

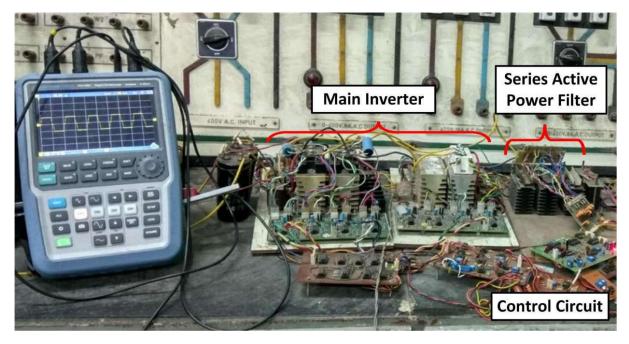

- Fig. 3.10 Experimental setup

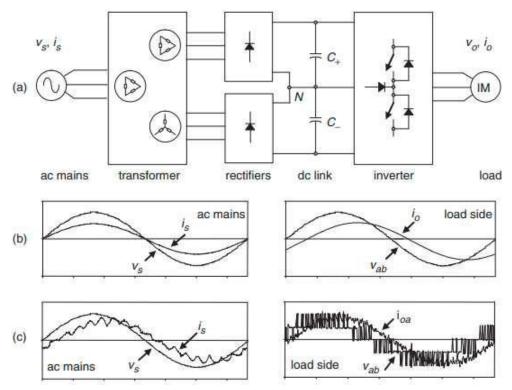

- Fig. 4.1 Waveforms of an adjustable speed drive system: (a) block diagram of electrical power conversion; (b) the ideal input and output waveforms; and (c) the actual input and output waveforms

- Fig. 4.2 Ideal waveforms for the SPWM in 3-phase VSI. ( $m_a = 0.8$ ): (a) modulating and carrier signals; (b) state of switch  $S_1$ ; (c) state of switch  $S_3$ ; (d) output ac voltage; (e) spectrum of line voltage

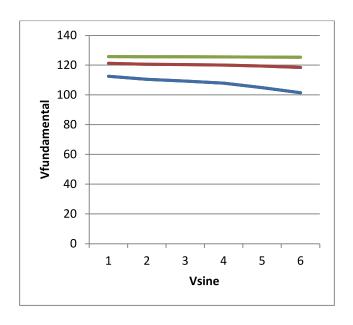

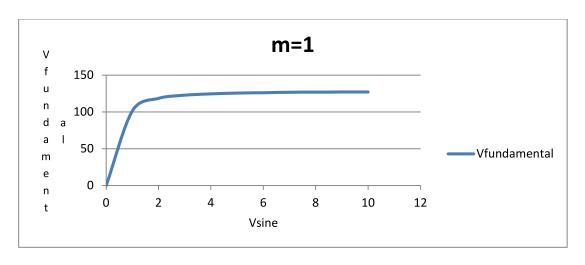

- Fig. 4.3 V<sub>LL1</sub>(rms)/V<sub>i</sub> as a function of ma in three phase inverter

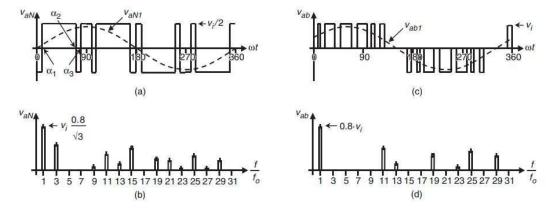

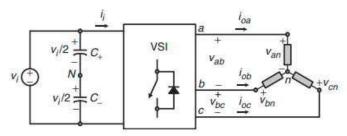

- Fig. 4.4 Ideal waveforms with SVPWM in 3-phase VSI: (a) modulating waveforms; (b) state of switch  $S_1$ ; (c) state of switch  $S_3$ ; (d) output ac voltage; (e) voltage spectrum of output ac; (f) output ac current; (g) input dc current; (h) spectrum of dc current; (i) current through switch  $S_1$ ; and (j) current through diode  $D_1$

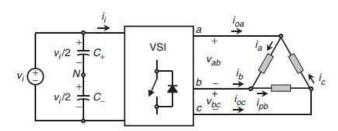

- Fig. 4.5 A VSI with load conneced in delta

- Fig. 4.6 A VSI in a star connected load

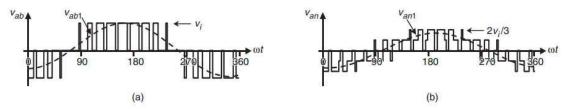

- Fig. 4.7 Line- and phase voltages of the three-phase VSI: (a) line voltage  $v_{ab}$ ; (b) phase voltage  $v_{an}$

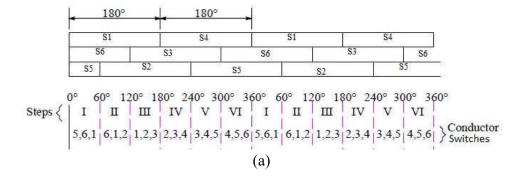

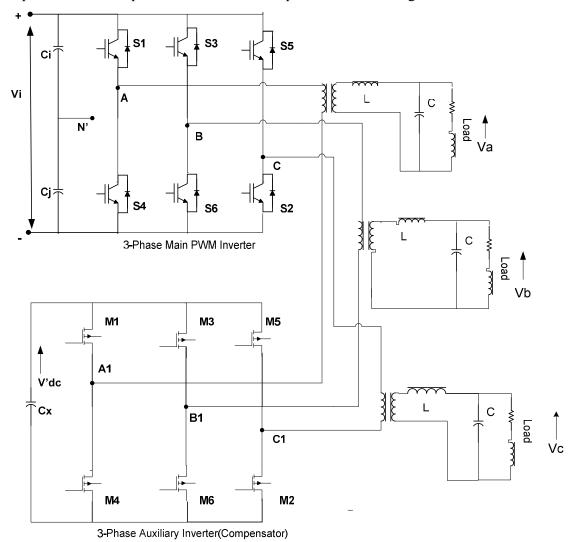

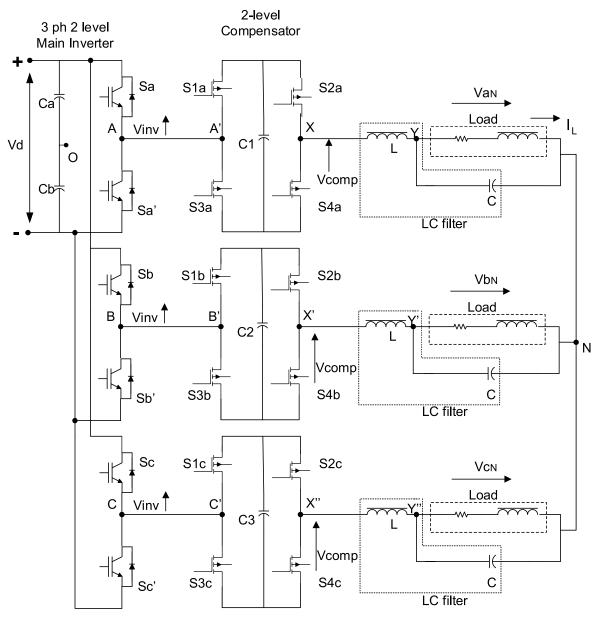

- Figure 4.8 Power circuit diagram of proposed three phase PWM inverter

- Figure 4.9 Single line diagram of proposed inverter system

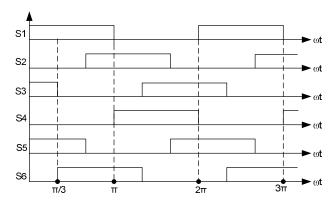

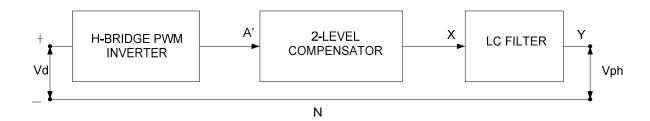

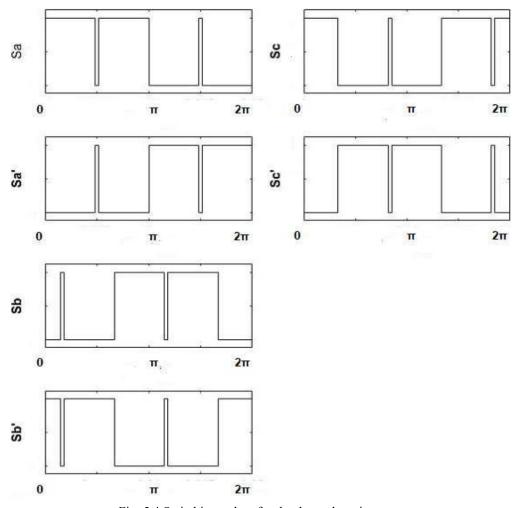

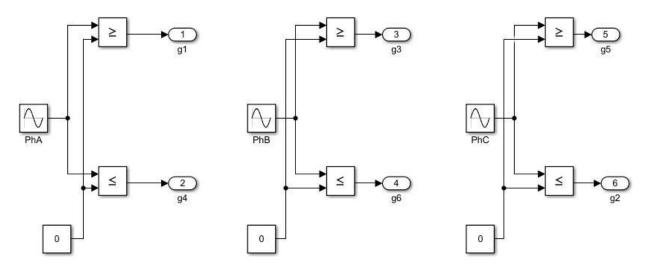

- Figure 4.10 Switching pulses for the three phase inverter

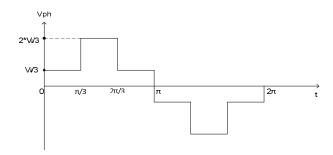

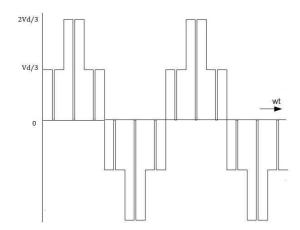

- Figure 4.11 Stepped voltage waveform across terminals A' & N

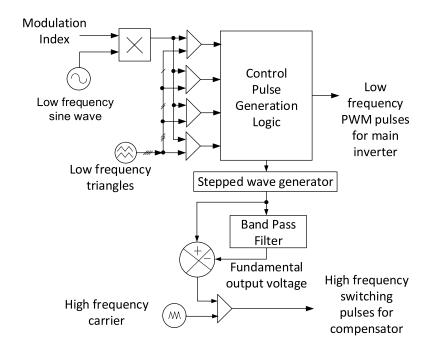

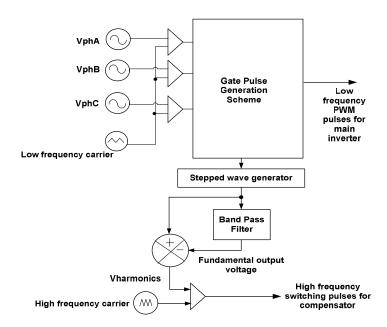

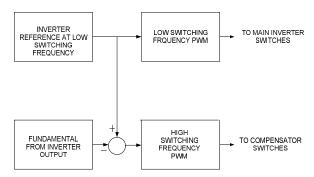

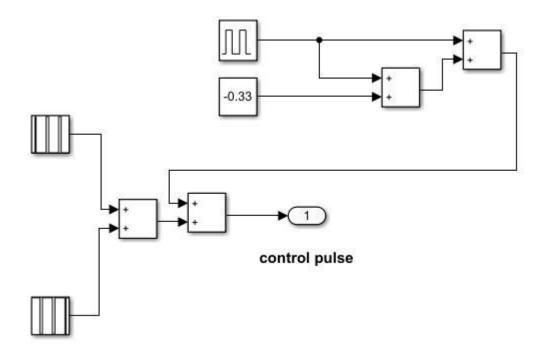

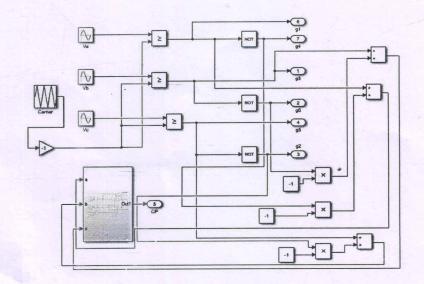

- Figure 4.12 Block diagram of control scheme for generation of gate pulses for main inverter and compensator

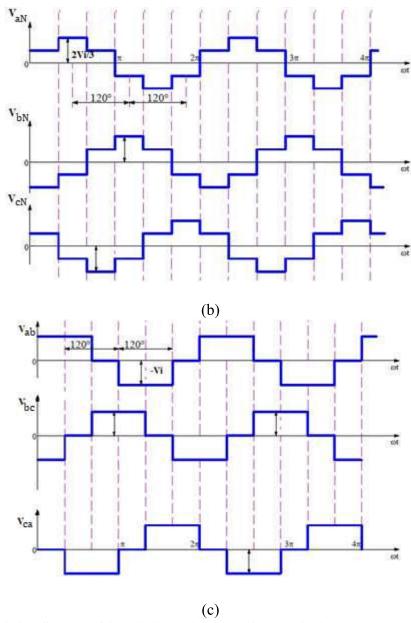

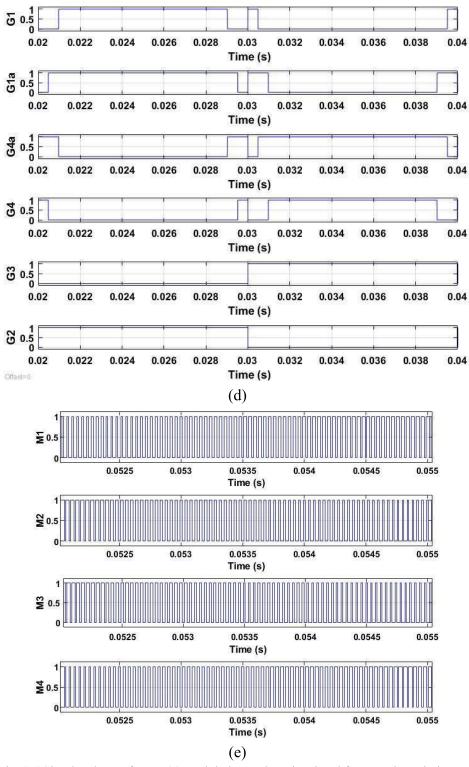

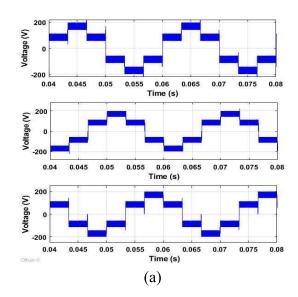

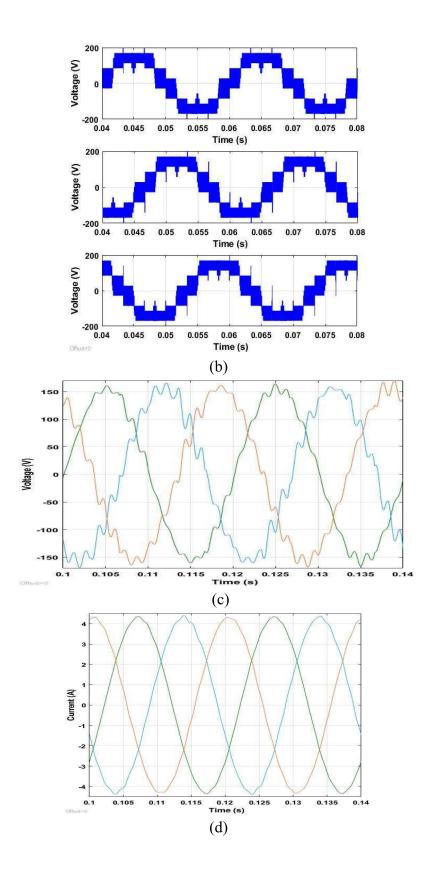

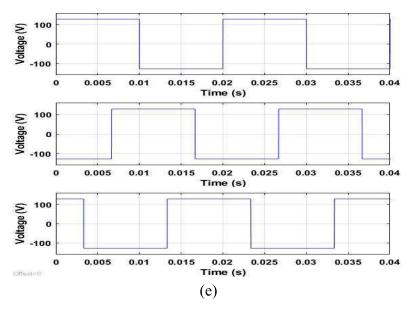

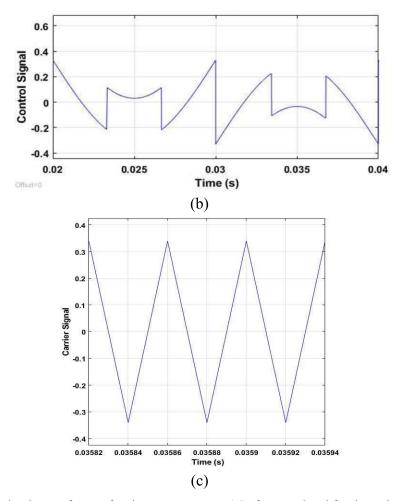

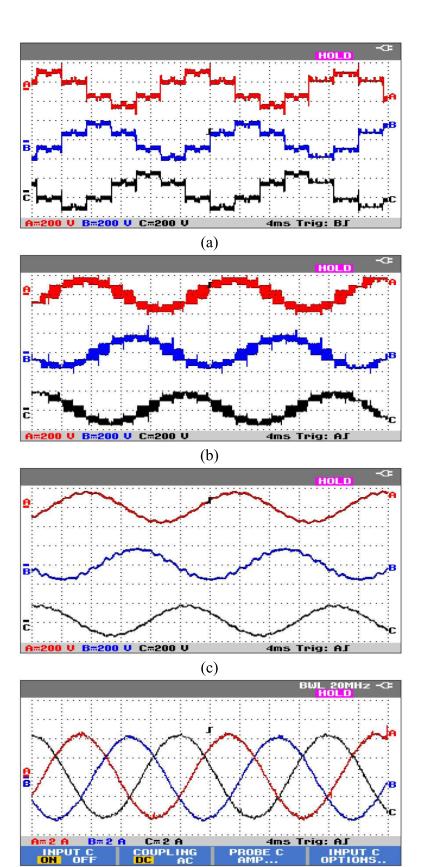

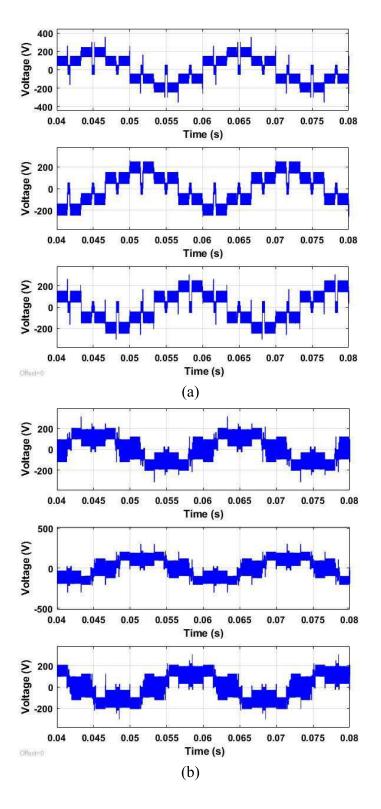

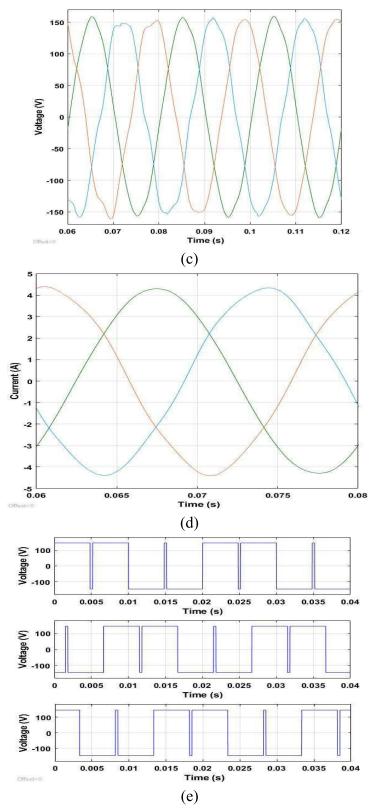

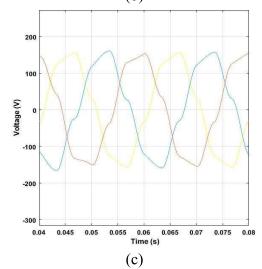

- Figure 4.13 Waveforms at different points of the power circuit of the proposed inverter: a) Line to Neutral voltage of the main inverter; b) Line to Neutral voltage after the compensator; c) Three phase Line to Neutral voltage after LC filter (across R-L load); d) Three phase Line current through R-L load; e) Voltage across dc bus midpoint and inverter output

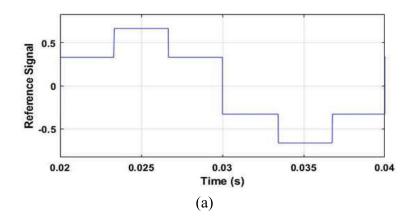

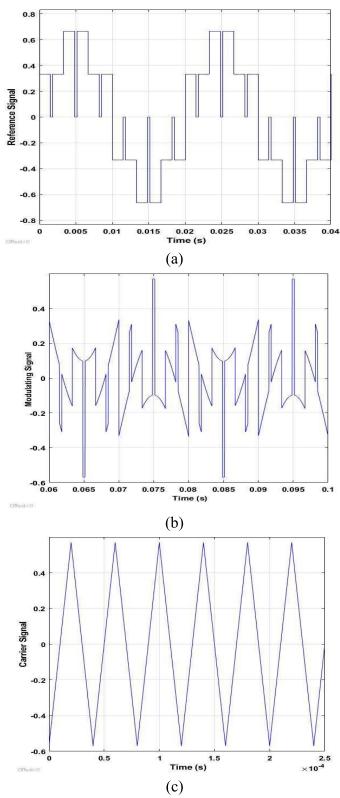

- Fig. 4.14 Control circuit waveforms of active compensator: a) Reference signal for the active compensator; b) Modulating waveform for the high frequency PWM; c) Carrier signal for the high frequency PWM

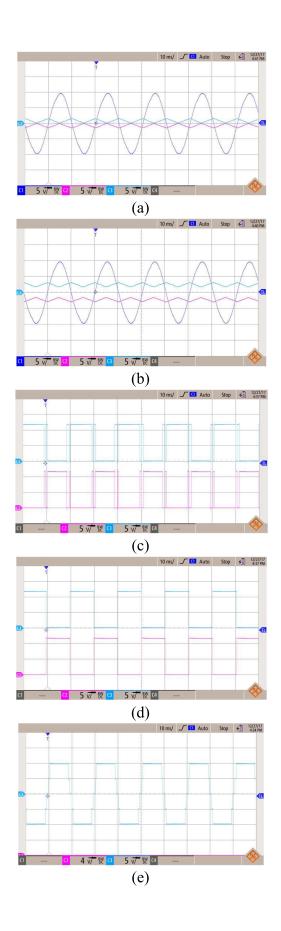

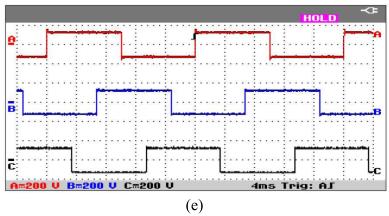

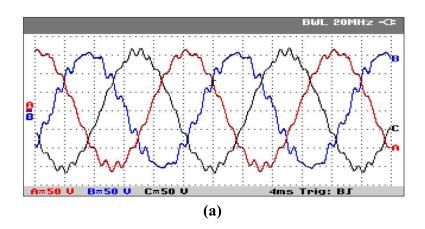

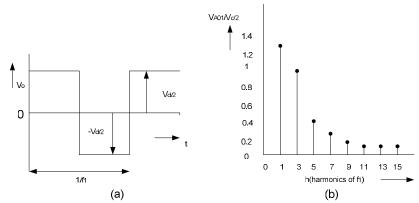

- Fig. 4.15 Experimental waveforms: (a) voltage across inverter output and load neutral; (b) voltage across load without the filter; (c) voltage across load; (d) load current; (e) voltage across terminals inverter output and dc bus midpoint

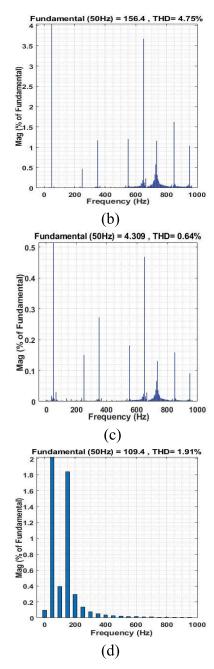

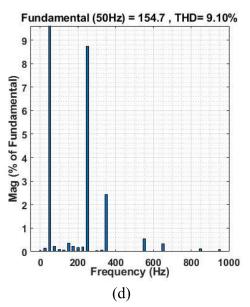

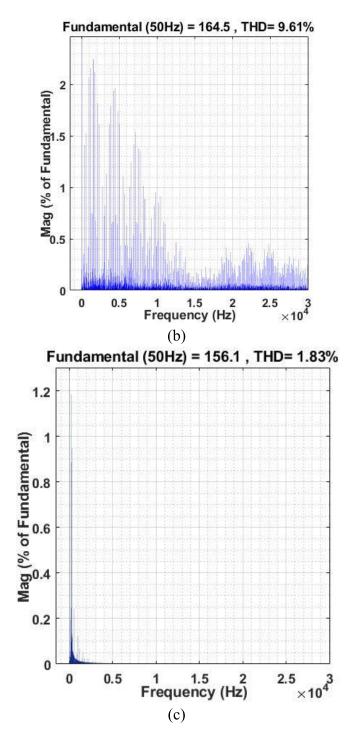

- Fig. 4.16 Harmonic spectrum at different points of the power circuit of the proposed inverter: a) Harmonic spectrum of L-N voltage of main inverter; b) Harmonic spectrum of L-N voltage after LC filter (across load); c) Harmonic spectrum of line current through R-L load; (d) Harmonic spectrum of L-N voltage after LC filter (across load) of three phase SPWM inverter

- Fig. 4.17 Proposed topology for open end winding transformer coupled load

- Fig. 4.18 Open End Winding Transformer in Proposed Converter: (a) Load voltage (after filter); (b) THD spectrum of load voltage (after filter); (c) Load voltage (before filter); (d)

- Load current; (e) THD spectrum of load current; f) Voltage across inverter and dc bus midpoint

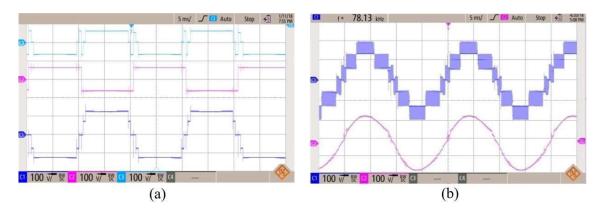

- Fig. 4.19 Open End Winding Transformer in Proposed Converter: (a) Load voltage (after filter); (b) Load voltage (before filter); (c) Load current; (d) Voltage across dc bus midpoint and inverter output

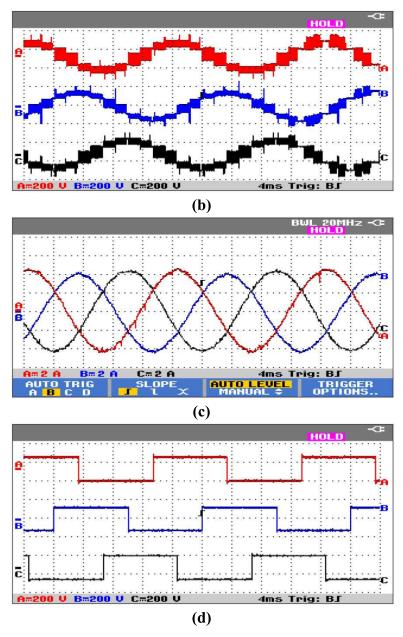

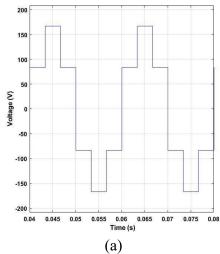

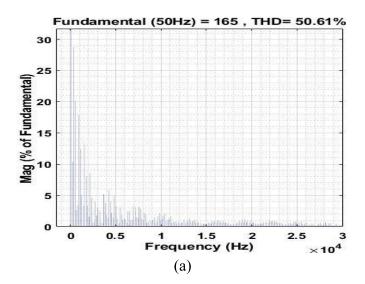

- Fig 5.1 Square wave switching: (a) Fundamental output signal of the inverter; (b) harmonic spectrum

- Fig. 5.2 Circuit connection of proposed SPWM three phase inverter

- Fig. 5.3 Block schematic of one phase of proposed inverter

- Fig. 5.4 Switching pulses for the three phase inverter

- Fig. 5.5 PWM Stepped voltage waveform across terminals A' & N

- Fig. 5.6 Block diagram of control scheme for generation of gate pulse

- Fig. 5.7 Control circuit waveforms of active compensator: (a) Reference signal for the active compensator, (b) Modulating waveform for the high frequency PWM; (c) Carrier signal for the high frequency PWM

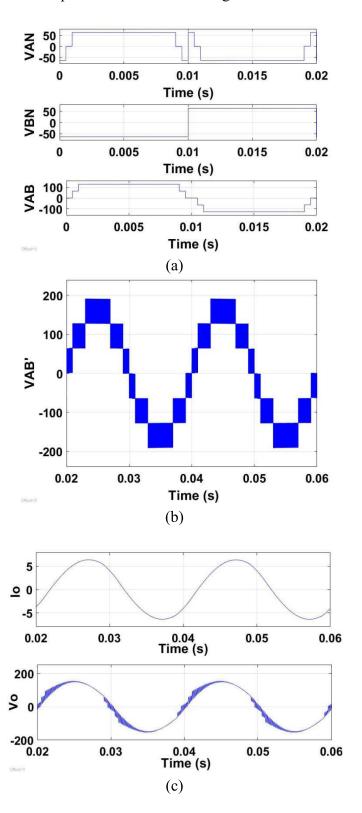

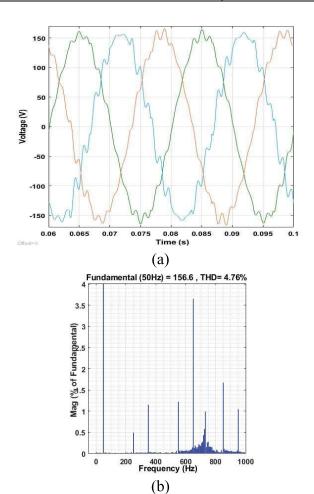

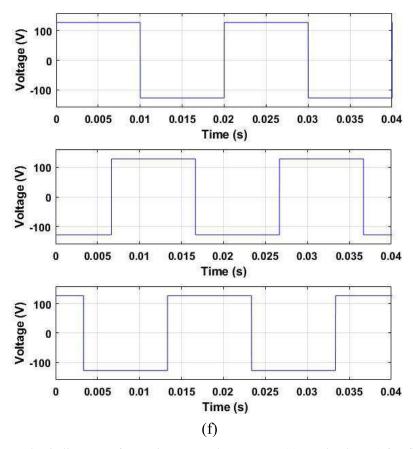

- Fig. 5.8 Waveforms at different points of the power circuit of the proposed inverter: (a) three phase main inverter voltages; (b) three phase voltages after the compensator; (c) three phase voltages after LC filter (across R-L load); (d) three phase load current; (e) three phase main inverter voltages w.r.t. dc bus midpoint O

- Fig. 5.9 (a)  $V_{LN}$  of one phase of the conventional three-phase inverter without filter; (b) harmonic spectrum of the inverter output without filter; (c) conventional three-phase inverter with filter; (b) harmonic spectrum of the inverter output with filter

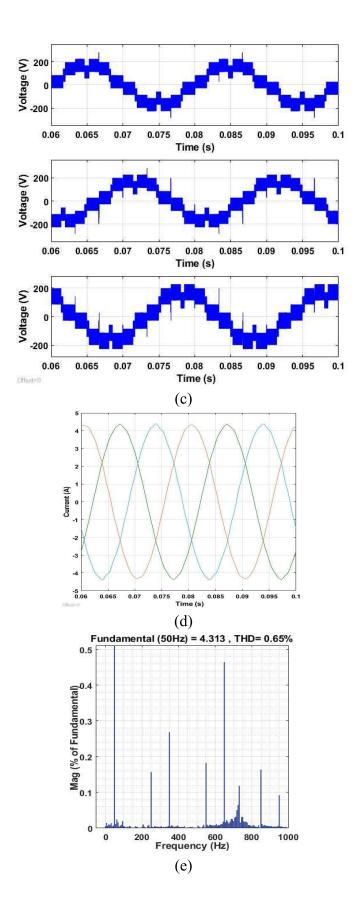

- Fig. 5.10 Harmonic spectrum at different points of the power circuit of the proposed inverter: a) Harmonic spectrum of L-N voltage of main inverter; b) Harmonic spectrum of L-N voltage after the compensator; c) Harmonic spectrum of L-N voltage after LC filter (across load)

## **List of Tables**

- Table 1.1 Switch states for a HB single-phase VSI

- Table 1.2 Switch states for a full-bridge single-phase VSI

- Table 1.3 Switch states for a three-phase VSI

- Table 1.4 Comparative study on DC bus utilization of a single phase FB inverter

- Table 3.1 Values of Parameters and Component Ratings of System Studied

- Table 3.2 Comparison between Simulation and Experimental results

- Table 3.3 Comparison with Conventional SPWM Inverter

- Table 4.1 Values of Parameters and Component Ratings of System Studied

- Table 4.2 Summary of simulation results

- Table 4.3 Comparison with Conventional Three-Phase Inverter

- Table 4.4 Values of Parameters and Component Ratings of System Studied

- Table 4.5 Summary of simulation results

- Table 5.1 Values of Parameters and Component Ratings of System Studied

- Table 5.2 Summary of simulation results

- Table 5.3 Comparison with Conventional Three-Phase Inverter

# **List of Abbreviation**

VSI Voltage Source Inverter

CSI Current Source Inverter

FFT Fast Fourier Transform

AC Alternating Current

DC Direct Current

ASD Adjustable Speed Drive

UPS Uninterruptible Power Supply

RMS Root Mean Square

IGBT Insulated Gate Bipolar Transistor

EMF Electro Motive Force

PWM Pulse Width Modulation

HB Half Bridge

FB Full Bridge

EMI Electro Magnetic Interference

SVM Space Vector Modulation

SPWM Sine Pulse Width Modulation

SCR Silicon Controlled Rectifier

VFD Variable Frequency Drive

EMC Electro Magnetic Compatibility

CM Common Mode

SHE Selective Harmonic Elimination

THD Total Harmonic Distortion

IM Induction Motor

FC Floating Capacitor

DVR Dynamic Voltage Restorer

OEW Open End Winding

MV Medium Voltage

DG Distributed Generation

NPC Neutral Point Clamped

ANPC Active Neutral Point Clamped

PV Photo Voltaic

MLI Multilevel Inverter

LSPWM Level Shifted Pulse Width Modulation

SiC Silicon Carbide

TPWM Trapezoidal Pulse Width Modulation

RC-qTPWM Reconstructed Carrier Quasi Trapezoidal Pulse Width Modulation

CPS PWM Carrier Phase Shifted Pulse Width Modulation

CHB Cascaded H Bridge

TI Transformer less Inverter

SC Switched Capacitor

ASHCM-PWM Asymmetric Selective Harmonic Current Mitigation PWM

MCPWM Multicarrier Modulation

DPWM Discontinuous Pulse Width Modulation

PSPWM Phase Shifted Pulse Width Modulation

PSO Particle Swarm Optimization

PCC Point of Common Coupling

HE Harmonic Elimination

NLM Nearest Level Modulation

MMC Modular Multilevel Converter

APF Active Power Filter

NHC Natural Harmonic Compensator

SAPF Series Active Power Filter

MOSFET Metal Oxide Field Effect Junction Transistor

VAR Volt Ampere Reactive

FACTs Flexible AC Transmission System

VSD Variable Speed Dive

## Introduction

## 1.1 Power Electronics Inverter System

Power Electronics involves power and electronics to convert electrical power from one form to another in a proficient, clean, regulated, and economical manner for the further consumption by end user. Inverter is the heart of power electronics which defines a type of power conversion circuit that is fed from a dc voltage source or alternatively a dc current source to either ac voltage or ac current. Even though input to an inverter circuit is a dc source, it is a very common practice to derive this dc from an available ac source like utility grid. For instance, the major source of input power can be the utility grid supply which is transferred to dc by a rectifier and then 'inverted' back to ac using an inverter. Here, the frequency and magnitude of the ac output may be different than the input ac of the utility supply. The 'inverter' operation can also be used by a rectifier circuit provided the direction of flow of power is from load to source side. Though, in this chapter, irrespective of direction of flow of power, 'inverter' is defined as a power converter which is fed from a stiff dc voltage source and transforms it into ac output voltage source. When the dc input is a voltage source, the corresponding inverter is known as voltage source inverter (VSI). If the input is a current source, the inverter is called as current source inverter (CSI). The VSI is capable of control the output voltage directly while the output current is directly controlled by the CSI.

The voltage waveform of the output of an ideal VSI should not depend on connected load at its output. A common example of dc voltage source applicable to a VSI may be a battery containing multiple cells in series-parallel mode. Solar photovoltaic arrays may be a type of dc voltage source. DC voltage derived from an ac voltage supply, through rectification is also an effective voltage source. A stiff voltage source implies that the magnitude of the source voltage is independent of load connected to it.

Few practical examples of voltage source inverters include uninterruptible power supply (UPS) modules, variable ac motor drives (VSD), frequency changer system etc. The commercially available models of inverter for use in our homes and work places to provide power to critical ac loads in case the unavailability of the utility grid. In these inverters, the input dc source is created by battery and the inverter circuit changes the dc into ac voltage at designated frequency. The ac voltage magnitude is controlled by the amplitude of dc input voltage. If the input dc voltage is lower than that required to meet the load voltage demand, then a step up transformer is used to meet the load demand.

#### 1.2 Classification of Inverters

Inverters can be classified in a several ways. It can be a single-phase inverter or a three-phase inverter depending on whether the output is single-phase or 3-phase ac. As per the method of commutation it is classified as line commutated inverter and forced commutated inverter. A line commutated inverter operates with an ac system. The ac line voltage is used for commutation. As the ac voltage goes to zero crossings and reverses the polarity of voltage the thyristor is turned off. The force commutated inverters used mainly with dc system utilizes extra commutation circuit to turn off the devices. Another Classification of Inverters is as per the connections of thyristors and commutating elements such as series inverter, parallel inverter and bridge inverter. Another Classification of Inverters is voltage source inverters and current source inverters. A voltage source inverter is supplied by a constant dc voltage source while a current source inverter is excited by a constant current source.

#### 1.2.1 Single phase Inverter

A single-phase square wave VSI generates square wave output voltage using a 1-phase load. Those inverters use simple control strategy and the power electronics devices to switch at a low switching frequency compared to some other types of inverters. The early generation inverters based on thyristors as switches, were mostly square wave inverters as thyristors had restricted switching frequency at a few hundred's of frequency. Alternately, the present day semiconductor switches like MOSFETs, IGBTs are having faster switching speed and used at switching frequencies up to few megahertz. Single-phase inverters are generally categorized as half bridge or full bridge configurations. Power circuits of these configurations are depicted in Fig. 1.1(a) and (b) for further discussions.

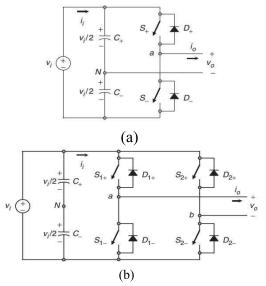

Fig. 1.1(a) Single-phase half bridge VSI, (b) Single-phase full bridge VSI

In this chapter, both the aforementioned configurations of inverters are illustrated assuming ideal source of voltage and ideal switches. In accordance, it is also assumed that the input dc voltage (V<sub>i</sub>) has steady magnitude and the semiconductor switches are free of loss. In half bridge configuration the dc voltage input is divided in two equal halves across an ideal and loss-free capacitive voltage divider. The half bridge configuration contains one limb of switches whereas the full bridge topology has two such limbs. The mid-point of the semiconductor switches in each limb of the inverter acts as an output terminal for the load connection. In half bridge configuration the 1-phase load is connected across the mid-point of the input dc bus voltage and the mid-point of the two semiconductor switches as shown in Fig. 1.1(a). Such points are demarcated as 'a' and 'N' respectively. For simplicity, the semiconductor switches S+ and S- can be assumed to be adjusted as mechanical switches that will open and close in response to the switching signal. Now, if the switches S+ and S- are turned on alternately with duty ratio of 50%, the voltage across the load (V<sub>aN</sub>) will become a square wave with a peak-to-peak amplitude equal to the voltage V<sub>i</sub> of input dc bus voltage. Table 1.1 shows the switching states of 1-phase half bridge inverter.

Fig. 1.2 also shows the output voltage waveform of single phase half bridge and full bridge inverter. Fig. 1.2(a) depicts a typical waveform of load voltage supplied by a half bridge inverter.  $V_{aN}$  achieves an amplitude of  $+0.5V_i$  when  $S_+$  is on and the amplitude is  $-0.5V_i$  when  $S_-$  is turned on. The two switches of the inverter limb are turned on alternatively. For a general purpose load, the switches should not be turned on turned off at the same time. Simultaneous turn-on of both the switches will make the input dc bus short circuited causing the switch currents to rise enormously. For an inductive load, one of the switches should be turned on to maintain continuous load current. For an inductive load, even though the switching frequency is very high as current cannot change instantly through an inductor. Hence, the switches must have bidirectional current carrying ability. Also Table 1.2 shows the switching states of single-phase full bridge (FB) inverter.

Table 1.1 Switching states for a HB single-phase VSI

| Output Voltage V <sub>0</sub> | Switching State                                | Components Conducting |                      |

|-------------------------------|------------------------------------------------|-----------------------|----------------------|

| V <sub>i</sub> /2             | S <sub>+</sub> is on and S <sub>-</sub> is off | S+                    | If i <sub>o</sub> >0 |

|                               |                                                | $D_{+}$               | If i <sub>o</sub> <0 |

| -V <sub>i</sub> /2            | S <sub>+</sub> is on and S <sub>-</sub> is off | D.                    | If i <sub>o</sub> >0 |

|                               |                                                | S.                    | If i <sub>o</sub> <0 |

| 0                             | S <sub>+</sub> is on and S <sub>-</sub> is off | D.                    | If i <sub>o</sub> >0 |

|                               |                                                | $D_{+}$               | If i₀<0              |

Table 1.2 Switch states for a full-bridge single-phase VSI

| Output<br>Voltage V <sub>0</sub> | Switch State                                                                          | Components                         | Conducting           | VaN                | V <sub>bN</sub>     |

|----------------------------------|---------------------------------------------------------------------------------------|------------------------------------|----------------------|--------------------|---------------------|

| Vi                               | S <sub>1+</sub> & S <sub>2-</sub> are on & S <sub>1-</sub> & S <sub>2+</sub> are      | S <sub>1+</sub> & S <sub>2-</sub>  | If i <sub>o</sub> >0 | V <sub>i</sub> /2  | - V <sub>i</sub> /2 |

|                                  | off                                                                                   | $D_{1+} \& D_{2-}$                 | If i <sub>o</sub> <0 |                    |                     |

| -V <sub>i</sub>                  | S <sub>1-</sub> & S <sub>2+</sub> are on<br>& S <sub>1+</sub> & S <sub>2-</sub> are   | D <sub>1-</sub> & D <sub>2+</sub>  | If i <sub>o</sub> >0 | -V <sub>i</sub> /2 | V <sub>i</sub> /2   |

|                                  | off                                                                                   | $S_{1-} \& S_{2+}$                 | If io<0              |                    |                     |

| 0                                | S <sub>1+</sub> & S <sub>2+</sub> are on<br>& S <sub>1-</sub> and S <sub>2-</sub> are | S <sub>1+</sub> & D <sub>2+</sub>  | If i <sub>o</sub> >0 | V <sub>i</sub> /2  | V <sub>i</sub> /2   |

|                                  | off                                                                                   | $D_{1+} \& S_{2+}$                 | If io<0              |                    |                     |

| 0                                | S <sub>1-</sub> & S <sub>2-</sub> are on<br>& S <sub>1+</sub> & S <sub>2+</sub> are   | D <sub>1-</sub> & S <sub>2-</sub>  | If i <sub>o</sub> >0 | -V <sub>i</sub> /2 | - V <sub>i</sub> /2 |

|                                  | off                                                                                   | S <sub>1-</sub> & D <sub>2-</sub>  | If i <sub>o</sub> <0 |                    |                     |

| $V_{i}$                          | S <sub>1-</sub> , S <sub>2-</sub> , S <sub>1+</sub> , & S <sub>2+</sub> are all off   | D <sub>1</sub> - & D <sub>2+</sub> | If i <sub>o</sub> >0 | -V <sub>i</sub> /2 | V <sub>i</sub> /2   |

| -V <sub>i</sub>                  |                                                                                       | D <sub>1+</sub> & D <sub>2-</sub>  | If i <sub>o</sub> <0 | $V_i/2$            | - V <sub>i</sub> /2 |

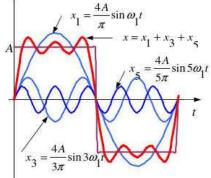

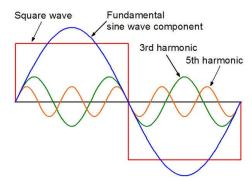

## **Harmonic Analysis of Load Voltage Waveforms**

A square wave is the combination of several sine waves with odd multiple of the fundamental harmonics frequency. To know about the various elements of a complex waveform it is necessary to perform a spectrum (frequency) analysis. Analyzing signals may be carried out in a digital, analog or combined of both ways. Analog signal processing can be done with spectrum analyzers. It could be a group of filters having a variety of pass frequencies as well as narrow band filters that are tunable.

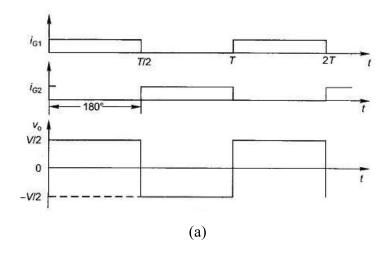

Fig. 1.2(a) Output of Half Bridge Inverter, (b) Output of Full Bridge Inverter

In digital signal processing, Fast Fourier Transform (FFT) is the most frequently used technique. A periodic signal is expressed by the form of a Fourier series is the equivalent of breaking down it into component functions which include the constant part  $a_0$  as well as the harmonic components that have two factors:  $\omega_1$ , 2  $\omega_1$ , 3  $\omega_1$ , ..., n  $\omega_1$ , where  $\omega_1$  is the fundamental content and  $n\omega_1$  are the harmonic content, n is a natural number. The fundamental component is determined by the formula.

$$\omega = \frac{2\pi}{T}$$

1.1

Where, T – time period of the function

The equation expressing the periodic waveform x(t) by means of the Fourier series is given by

$$x(t) = a_0 + \sum_{n=1}^{\infty} (a_n \cos n\omega_1 t + b_n \sin n\omega_1 t)$$

1.2

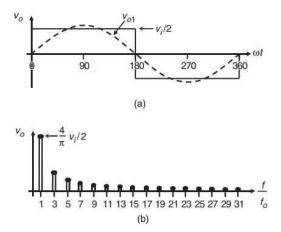

The efficacy of Fourier series  $a_0$ ,  $b_n$  are determined by analyzing the equation of the waveform is demonstrated based on the results of measurements made with the help of a harmonic analyzer. For example, a periodic signal that is in the form of a square waveform can be represented as an infinite trigonometric order that includes odd harmonics (1 3, 5, 7, ...) with decreasing magnitudes. This is a demonstration of the signal in the time domain as shown in fig. 1.3.

$$x(t) = \frac{4A}{\pi} (\sin \omega_1 t + \frac{1}{3} \sin 3\omega_1 t + \frac{1}{5} \sin 5\omega_1 t + \frac{1}{7} \sin 7\omega_1 t + \dots)$$

$$x = \frac{4A}{\pi} \sin \omega_1 t$$

$$x = \frac{4A}{\pi} \sin \omega_1 t$$

Fig. 1.3 Square waveform approximation with a limited number of harmonics

Periodic signals may also be graphically depicted within the defined frequency range. The x-axis is taken as frequency f. The length of the bars is proportional to the magnitude of the harmonics that are present in the signal being studied. The graph is referred to as the amplitude spectrum. Spectrums of the periodic signal components have discrete however (Fig. 1.4), spectrum of aperiodic signal (e.g. impulsive signal) is continuous. From the above amplitude spectrum it can be concluded that for a single phase square wave inverter, the peak amplitude of the fundamental ac output voltage is

$$\frac{4}{\pi} \frac{V_i}{2}$$

where V<sub>i</sub> is the input dc bus voltage to the inverter.

Fig. 1.4 Waveforms for ideal half-bridge voltage source inverter using square-wave modulating technique: (a) ac output voltage and (b) FFT spectrum of the output voltage

#### 1.2.2 Three phase Inverter

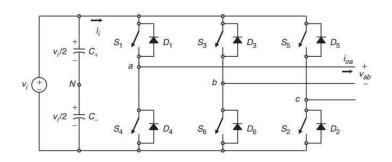

The individual phase voltages w.r.t. the dc bus midpoint of the 3-phase bridge inverter are same with that of the square wave output as obtained by single-phase half bridge or full bridge inverters. Fig. 1.5 shows the power circuit of the three-phase inverter. Here, the three phase voltages are displaced in time by  $120^{\circ}$ . These phase voltages and three line voltages are shown in Fig. 1.6 (b) and (c) respectively. The horizontal axis of the waveforms in Fig. 1.6 is given in the style of ' $\omega$ t', where ' $\omega$ ' is the angular frequency of the fundamental component of the square wave voltage and 't' is the time in second. Referring to Fig. 1.6 (b) & (c) the phase sequence of the phase voltages is taken as  $V_{aN}$ ,  $V_{bN}$  and  $V_{cN}$ . Also Table 1.3 shows the switching states of 3-phase full bridge inverter.

Fig. 1.5 A 3-phase Voltage Source Inverter (VSI) feeding a balanced load

Table 1.3 Switch states for a three-phase VSI

| St                                             | tate                                           | $V_{ab}$         | V <sub>bc</sub>  | V <sub>ca</sub>  |

|------------------------------------------------|------------------------------------------------|------------------|------------------|------------------|

| On State                                       | Off State                                      | Vi               | 0                | - V <sub>i</sub> |

| S <sub>1</sub> ,S <sub>2</sub> ,S <sub>6</sub> | S <sub>4</sub> ,S <sub>5</sub> ,S <sub>3</sub> | 0                | $V_{i}$          | - V <sub>i</sub> |

| S <sub>2</sub> ,S <sub>3</sub> ,S <sub>1</sub> | S <sub>4</sub> ,S <sub>5</sub> ,S <sub>6</sub> | - V <sub>i</sub> | $V_{i}$          | 0                |

| S <sub>3</sub> ,S <sub>4</sub> ,S <sub>2</sub> | S <sub>1</sub> ,S <sub>5</sub> ,S <sub>6</sub> | - V <sub>i</sub> | 0                | $V_{i}$          |

| S <sub>4</sub> ,S <sub>5</sub> ,S <sub>3</sub> | S <sub>1</sub> ,S <sub>2</sub> ,S <sub>6</sub> | 0                | - V <sub>i</sub> | $V_{i}$          |

| S <sub>1</sub> ,S <sub>2</sub> ,S <sub>6</sub> | S <sub>3</sub> ,S <sub>4</sub> ,S <sub>5</sub> | Vi               | - V <sub>i</sub> | 0                |

| S <sub>6</sub> ,S <sub>1</sub> ,S <sub>5</sub> | S <sub>3</sub> ,S <sub>2</sub> ,S <sub>4</sub> | 0                | 0                | 0                |

| S <sub>4</sub> ,S <sub>6</sub> ,S <sub>2</sub> | S <sub>1</sub> ,S <sub>3</sub> ,S <sub>5</sub> | 0                | 0                | 0                |

Fig. 1.6 (a) Timing diagrams of the switches in three phase inverter;(b)Phase voltage waveforms of a 3-phase square wave VSI; (c) Line voltage waveforms of a 3-phase square wave VSI

The switches have been numbered, it is necessary to observe the conduction period of the switches marked in Fig. 1.6 (a). It will be observed that with the chosen numbering the switches turn on in the sequence:-  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$ ,  $S_5$ ,  $S_6$ ,  $S_1$ ,  $S_2$ , ....and so on. Recognizing the fundamental repetition time as  $360^{\circ}$  ( $2\pi$  radians), each switch operates for  $180^{\circ}$  and the turn on of the adjacent switch is displaced by  $60^{\circ}$ . In each limb of the inverter, the upper and lower switches operate in a complementary manner. If the output phase sequence is to be reversed, the switching sequence must be altered. From the symmetry style of the switch conduction, it may be observed that at any time three switches will conduct. The sequence may involve two from the of switches of the top group connected to positive dc input, and one from bottom

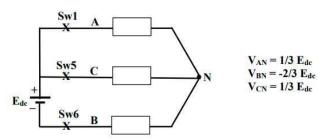

group i.e., two from upper group and one from lower group. As per the conduction pattern depicted in Fig. 1.6 (a) six combinations of conducting switches exists over one complete input cycle. Each of these combinations of switches conducts for 60 degrees as per the above mentioned sequence to create output phase sequence of a, b, c. The phase voltages across load,  $V_{aN}$ ,  $V_{bN}$  and  $V_{cN}$  can be obtained from the sequence of conduction of the switches in the inverter. Concerning to Fig. 1.7, it can be noted that for  $0 \le \omega t \le \pi/3$ , conduction exists for switches Sw5, Sw6 and Sw1. Assuming that the switches are ideal, Fig. 1.7(a) depicts the equivalent model of inverter and load circuit for the interval  $0 \le \omega t \le \pi/3$ . Looking into the equivalent circuit, the non conducting switches are ignored and the conducting switches are represented by a cross (X) sign. The instantaneous phase voltage waveforms for a balanced 3-phase load are given below for the two conditions (i) when a purely resistive load is connected and (ii) when a load, comprising of a resistance in series with an inductance and a back e.m.f. in each phase. In both the cases, Fig. 1.7(a) is the equivalent circuit referred to obtain the expression for load-phase voltage.

Fig. 1.7(a) Equivalent load circuit during conduction of Sw5, Sw6 and Sw1

Fig. 1.7(b): Equivalent load circuit during conduction of Sw6, Sw1 and Sw2

For case (i), with a balance resistive load, it is simple to observe that for  $0 \le \omega t \le \pi/3$ , the instantaneous phase voltages shall be expressed by  $V_{AN} = 1/3$   $E_{dc}$ ,  $V_{BN} = -2/3$   $E_{dc}$ ,  $V_{CN} = 1/3$   $E_{dc}$ . Fig. 1.7(b) depicts the equivalent circuit for case (ii) during  $\pi/3 \le \omega t \le 2\pi/3$ , when the switches Sw6, Sw1 and Sw2 are in conduction. The voltages across load phase instantaneous values can be determined to yield  $V_{AN} = 2/3$   $E_{dc}$ ,  $V_{BN} = V_{CN} = -1/3$   $E_{dc}$ .

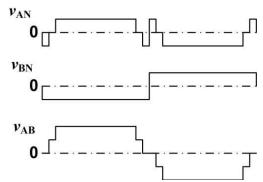

For other switching combinations, the load phase voltage waveforms may be determined in a similar approach. Two phase voltages,  $V_{aN}$  and  $V_{bN}$ , and line voltage  $V_{ab}$  have been shown in Fig. 1.6(c). It will be observed that voltage  $V_{bN}$  is similar to  $V_{aN}$  but lags it by 120°. Further, it may be proved that the voltage across the load phase  $V_{aN}$  also has a similar waveform to the other two voltages across phases but displaced in time by 120°. The waveform of voltage  $V_{cN}$

leads  $V_{aN}$  by 120°. It is clear that the phase voltage waveforms will contain a balanced fundamental components of 3-phase voltage with a phase sequence A, B, C. The output phase sequence can be altered by suitably controlling the switching pattern. The phase voltage waveforms shown in Fig. 1.6 (a) depicts six steps in one output cycle which is also known as the six-stepped waveform.

The 3-phase inverter as explained above may be used to create balanced 3-phase ac voltages at fundamental frequency. On the other hand, the 5<sup>th</sup>, 7<sup>th</sup> and other odd harmonic voltages of fundamental frequency pollute the output voltage. Such distortions in output voltages may not be tolerable in many cases and the use filter circuits to eliminate the harmonic voltages may also not be desirable.

#### 1.3 D.C. Bus Utilization of Inverter

DC Bus utilization is a performance index which measures how efficiently the input dc voltage can be utilized at the output of an inverter.

For an example if input dc is  $V_d=100 \text{ V}$ , then to obtain 100% dc bus utilization, the RMS fundamental ac voltage of the inverter ( $V_{01}$ ) is to be 100 V.

## 1.3.1 Square Wave Operation

In single phase square wave inverter, to control the amplitude of ac output of inverter the input dc has to be varied as the width of the square pulse cannot be adjusted except the frequency of the ac output. During square wave switching mode, each switch of the inverter limb of Fig 1.1(a) is turned on for one half cycle of the desired output frequency, hence a square wave is formed as shown in Fig 1.2. By Fourier-Series analysis, the maximum value of the fundamental component and harmonics in the output waveform of the inverter can be given by:

$$V_{aN} = \frac{4V_i}{2\pi} = 1.273 \frac{V_i}{2} \tag{1.5}$$

$$V_{aNh} = \frac{V_{aN}}{2\pi h} \tag{1.6}$$

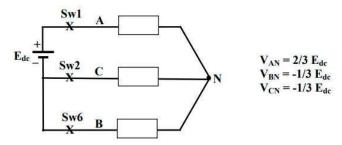

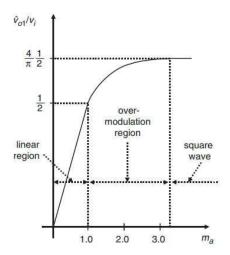

where, the harmonic order h takes on only odd values. It should be obtained that the square wave switching is a particular case of the sinusoidal PWM switching with modulation index unity. The maximum DC bus utilization can be achieved by a square wave. The output voltage is independent of modulation index  $m_a$  in the square wave area of the graph as shown in Fig. 1.8.

Fig. 1.8 Voltage control by varying m<sub>a</sub>

The major advantages of the square-wave switching operation are that each inverter switch alters its state only two times per cycle that is required for a high power applications where the switching speed of the power semiconductor devices are small. The major problem with square wave switching is non availability of output ac voltage magnitude adjustment.

In three phase inverter, with square wave switching output ac voltage magnitude cannot be controlled. Hence control of input dc voltage is the only option for the variable ac output. Using this scheme dc bus utilization can be higher but contains many harmonics. Here each switch conducts for 180° and three switches are turned on at any instant. In three phase inverter operating in square wave mode, the line to line fundamental RMS voltage is

$$V_{LL1} = \frac{\sqrt{3}}{\sqrt{2}} * \frac{4V_i}{2\pi} = 0.78V_i$$

1.7

#### 1.3.2 PWM Operation

The main purpose of pulse width modulation is to control the magnitude of ac output voltage of the inverter and to vary the frequency as well. By controlling the width of the PWM pulses the wave-shape of the output voltage becomes a near sinusoid. To create a pure sinusoidal output voltage at a designated frequency, a modulating control signal at the desired frequency is compared with high frequency carrier signal. The frequency of the carrier signal (e.g. triangular signal) decides the inverter switching frequency at which the inverter switches are switched. A control signal  $v_{control}$  at fundamental frequency  $f_1$  is used to modulate the inverter switches by comparing with the carrier signal at the switching frequency  $f_s$ . Thus a PWM sine wave is produced as shown in Fig. 1.9. The modulation index  $m_a$  is defined as

$$m_a = \frac{V_{control}}{V_{tri}}$$

1.8

where, v<sub>control</sub> is the maximum amplitude of the control signal.

v<sub>tri</sub> is the maximum amplitude of the carrier signal.

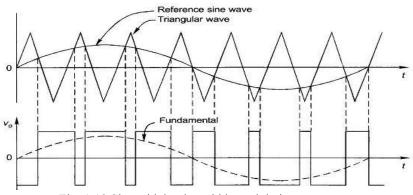

Fig. 1.9 Pulse width modulation scheme

For a single phase inverter at under-modulation, the peak amplitude of the fundamental voltage component as shown in Fig. 1.9 (dotted line) is expressed as

$$V_{o1} = m_a \frac{V_i}{2}$$

, for HB inverter  $V_{o1} = m_a V_i$  , for FB inverter

Which shows that the amplitude of the fundamental output voltage of the inverter varies linearly with  $m_a$ . Thus the linear region of the modulation index lies between 0 and 1. Hence, the RMS value of the fundamental voltage during under-modulation by a half bridge and full bridge inverter is  $0.3535V_i$  and  $0.707V_i$  respectively if the modulation index is unity. Therefore less DC bus utilization can be achieved as compared to square wave switching in which the RMS of fundamental voltage is 90% of the input dc bus voltage as shown in Table 1.4.

Table 1.4 Comparative study on DC bus utilization of a single phase FB inverter

| Type of Switching     | Input dc (V <sub>d</sub> ) | $\begin{array}{ccc} RMS & value & of & fundamental \\ voltage(V_{01}) & \end{array}$ | Observation                                                                                                              |

|-----------------------|----------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Square Wave switching | 100 V                      | $V_{01} = \frac{4V_{dc}}{\pi\sqrt{2}} = 0.9V_d$                                      | Maximum dc bus utilization but contains many harmonics                                                                   |

| SPWM switching        | 100 V                      | With $m \le 1$ , $V_{01} = \frac{m_a}{\sqrt{2}} V_d = 0.7 V_d$                       | Harmonic content is low with reduced dc bus utilization                                                                  |

|                       | 100 V                      | With m>1, $\frac{v_d}{\sqrt{2}} < V_{01} < \frac{^{4Vd}}{\pi\sqrt{2}}$               | Over-modulation increases the amplitude of the fundamental frequency component but low frequency harmonics is increased. |

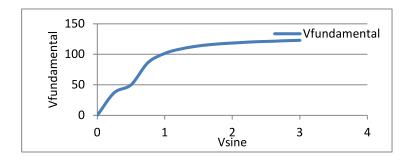

In the previous discussion, it is seen that during under-modulation, in spite of having less harmonic contents, the dc bus utilization is also reduced causing notches at the output waveform. In order to increase the dc bus utilization,  $m_a$  is increased further beyond 1.0

causing the output voltage to contain many harmonics as the fundamental component of output ac voltage of the inverter does not vary linearly beyond m<sub>a</sub>=1as shown in Fig 1.8. Also, the modulation index cannot be increased to large values (say, 3 i.e. the optimum value beyond of which the PWM inverter behaves like a square wave inverter) which decomposes the PWM inverter into a square wave inverter again and thus gives more harmonic contents. Practical inverters are far away from the ideal one as normally constant dc is not obtained at the input to the inverter. Generally this dc is a pulsating as obtained from the rectifiers connected to the grid. Also a large capacitor filter is connected across the dc output of rectifier to remove the ripples in the dc voltage. The capacitor voltage ripple, which is also the voltage ripple across the inverter input, is due to (1) the output of rectifier is not a pure dc, (2) the current drawn by the inverter from the dc source is also not a constant signal, Thus contains second harmonic current along with high switching frequency components. This 2<sup>nd</sup> harmonic causes ripple in the capacitor voltage as the ripple due to high frequency switching component is negligible.

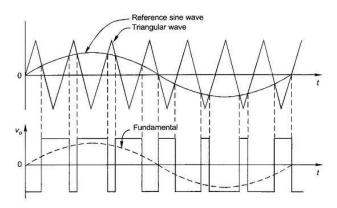

Similarly, in three phase voltage source inverters, pulse width modulation is used to maintain the balanced three phase output voltages in amplitude and frequency. To create the wave shape a pure sinusoid, it is essential to compare a high frequency triangular wave with the three sinusoidal modulating signals which are 120° phase displaced by each other as shown in Fig 1.10.

Fig. 1.10 PWM in three phase inverter

In any three phase inverters, the line to line voltages containing the harmonics are of major concern whereas the harmonics present in the phase voltage concerning the dc bus midpoint is identical to that obtained by single phase inverter. In the linear region where  $m_a$  is less than equal to unity, the fundamental component in the output voltage varies linearly with the amplitude modulation ratio  $m_a$ . The peak value of the fundamental component of phase voltage is given by:

$$V_{an1}=m_a*(V_s/2)$$

1.9

Also, the line to line rms voltage at fundamental frequency can be expressed as

$$V_{LL1} = (\sqrt{3}/\sqrt{2})^* V_{an1}$$

= 0.612m<sub>a</sub>V<sub>s</sub>

In over modulation (m<sub>a</sub>>1), the peak of the modulating signal is higher than the carrier wave. Thus, in this mode of operation the fundamental voltage will not change with the increase of modulation index as shown in Fig. 1.11.

Fig. 1.11 V<sub>LL</sub> vs m<sub>a</sub> curve of three phase inverter

Thus it is found that in three phase inverter, dc bus utilization is maximum (line to line RMS fundamental voltage is 78% of  $V_s$ ) with square wave switching as compared to the PWM switching technique (line to line RMS fundamental voltage is 61.2% of  $V_s$  at undermodulation).

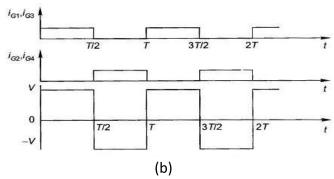

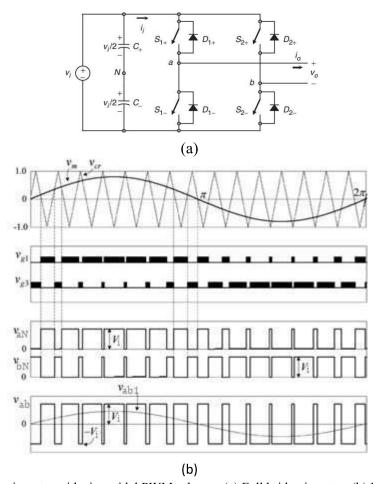

#### • PWM with bipolar voltage switching

In an inverter, the upper and the lower half switches in a limb work in a complementary fashion with alternate switches turned on at a time. Hence only two independent gating signals are required to be provided to the two switches  $S_{1+}$  and  $S_{1-}$  i.e.  $v_{g1}$  and  $v_{g3}$  which are

generated by comparing sinusoidal modulating signal  $v_m$  and triangular carrier signal  $v_{cr}$ . The inverter terminal voltages are obtained denoted by  $V_{aN}$  and  $V_{bN}$  and the inverter output voltage  $V_{ab} = V_{aN} - V_{bN}$ . As the voltage waveform of  $V_{ab}$  alternates between positive and negative dc bus voltage, this technique is called bipolar PWM which is shown in Fig. 1.12.

Fig. 1.12 Single phase inverter with sinusoidal PWM scheme; (a) Full bridge inverter, (b) Bipolar PWM scheme

### PWM with uni-polar voltage switching

The uni-polar modulation basically uses two sinusoidal waveforms  $v_m$  and  $v_m$  as modulating waves which are of same amplitude and frequency but  $180^\circ$  phase opposition. These two modulating signals are compared separately with a common triangular wave (carrier)  $v_{cr}$  to generate two gate signals  $v_{g1}$  and  $v_{g3}$  to be provided to the upper two switches  $S_{1+}$  and  $S_{2+}$ . It must be noted that the upper two switches do not change state simultaneously, which makes it different from the bipolar PWM where all the four switches are switched simultaneously. The output voltage of inverter changes between zero and  $+V_i$  in the positive half cycle or between zero and  $-V_i$  in the negative half cycle of the fundamental frequency. Hence, this modulation logic is called uni-polar modulation as shown in Fig.1.13. The uni-polar switched inverter

supports reduced switching losses and creates less EMI. In terms of efficiency, it seems that the uni-polar switched inverter has an advantage. Over-modulation happens when modulation index m<sub>a</sub> is higher than unity. It results in reducing the number of pulses present in the line to line output voltage waveform causing the presence of lower order harmonics. Further, the notch and pulses near the centre of positive and negative half cycle tend to disappear. To accomplish the switching operations of the switch, minimum notch and pulse widths must be controlled. When minimum width notches and pulses are dropped, there will be some switching transient at the load current.

Fig. 1.13 Single phase full bridge inverter with uni-polar sinusoidal PWM scheme

# 1.4 Voltage Control in Inverters

It is highly essential to control the output voltage of inverters (1) to overcome the variations of dc voltage, (2) for voltage regulation of inverters, (3) for constant volts/frequency control demand. There are different techniques by which the magnitude of output ac voltage of the inverter can be controlled. The widely applicable techniques include:

- i. Single Pulse Width Modulation Technique

- ii. Multiple Pulse Width Modulation Technique

- iii. Sinusoidal Pulse Width Modulation Technique (SPWM)

- iv. Space Vector Modulation Technique (SVM)

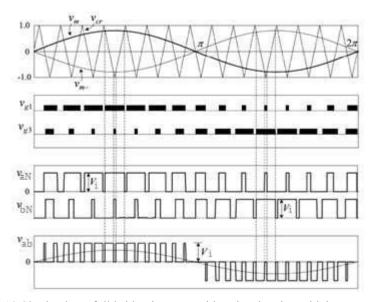

# 1.4.1 Single Pulse Width Modulation Technique

Single pulse width modulation technique involves only one pulse per half cycle and to adjust the inverter output voltage the width of the gate pulse is to be varied. Here the switching signals are created through comparison of a pulsed signal  $E_r$  (reference signal) with a

triangular signal  $E_c$  (carrier). The carrier signal frequency decides the frequency of the fundamental output voltage. The pulse width P can be varied from 0 to  $180^\circ$  by varying  $E_r$  from 0 to  $E_c$  as shown in fig. 1.14. The ratio of  $E_r$  to  $E_c$  is the modulation index and is expressed as

$$m = \frac{E_r}{E_c}$$

1.11

and the RMS output voltage can be given as

$$E_{L} = E_{dc} \sqrt{\frac{P}{\pi}}$$

1.12

Fig. 1.14 Single pulse width modulation

Fig. 1.15 Harmonic profile of single pulse width modulation

Fig. 1.15 shows the harmonic profile of single pulse width modulation. The graph shows that the dominant harmonic content is the third harmonic and the distortion factor increases significantly at a low value of output voltage.

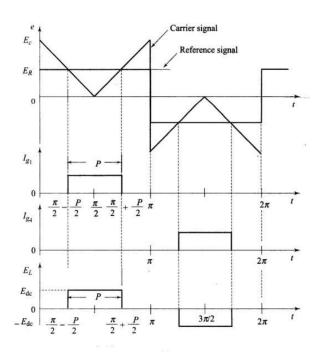

# 1.4.2 Multiple Pulse Width Modulation

This modulation allows the output ac voltage to be controlled by modulation index. The frequency of reference waveform decides the frequency  $f_0$  of the fundamental output and the carrier frequency determines the number of pulses per half cycle (N). The harmonics may be mitigated by using multiple pulses within each half cycle of the output voltage. The firing pulses to turn on and turn off the power electronics switches are shown in fig. 1.16.

Fig. 1.16 Multiple pulse width modulation

The number of pulses per half cycle is expressed as

$$N = \frac{f_c}{2f_0}$$

1.13

The modulation index (m) lies between 0 to 1 which varies the pulse width 0 to  $\pi/N$  and the output voltage from 0 to E<sub>c</sub> The output voltage for a single phase bridge inverters is shown in Fig. 1.16. If P is the width of each pulse, the RMS output voltage is given by

$$E_{c} = E_{dc} \frac{\sqrt{NP}}{\pi}$$

1.14

Fig. 1.17 Harmonic profile of multiple pulse width modulation

Fig. 1.17 depicts the harmonic characteristics with respect to the modulation index to have five pulses in one half cycle. The distortion factor is less in this case concerning to single pulse modulation. But due to the fast switching of the semiconductor devices the switching losses are increased. The amplitudes of lower order harmonics are less with the increase of p. But the magnitude of some higher order harmonics can be present which can be further reduces with the small size passive filter.

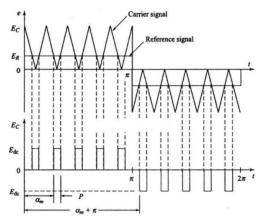

# 1.4.3 Sinusoidal Pulse Width Modulation (SPWM)

This technique is superior as compared to the above two techniques in terms of the distortion factor and lower order harmonics. Here, the size of each pulse is varied in ratio to the magnitude of a sine wave measured at the centre of the same pulse. The control signals as shown in Fig. 1.18 are created by comparing a sinusoidal reference waveform  $(f_r)$  with a high frequency carrier signal  $(f_c)$ . This type of modulation scheme has many industrial applications. The frequency of reference signal defines the fundamental frequency  $f_0$  of the output and its maximum amplitude  $A_r$  decides the modulation index (m) and the RMS output voltage  $V_0$ . The number of cycle per half cycle depends on the carrier frequency.

Fig. 1.18 Sinusoidal pulse width modulation

Fig. 1.19 Harmonic profile of sinusoidal pulse width modulation

The RMS output voltage can be changed from 0 to  $V_s$  by adjusting the modulation index (m) from 0 to 1. Fig. 1.19 depicts the harmonic characteristics with respect to the variation of modulation index for five pulses per half cycle.

# 1.4.4 Space Vector Modulation Control

Presently, in the digital systems the modulation technique to control the switches in any power converter system is most suitable one. The space vector modulation is an effective method to develop PWM signals as the line voltages which are on an average similar to the line voltages across a load. This is accomplished in each interval of sampling by suitably adopting the switching states obtained from the conventional ones of the VSI as shown in Table 1.3. and through calculation of the value of time periods correctly. The selected and calculated time periods are based on the Space Vector transformation.

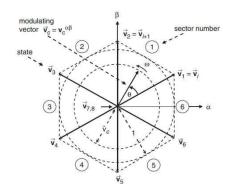

#### A. Space-vector Conversion

A 3-phase set of data which sum up to zero in the abc stationary frame may be expressed in a complex plane using a complex vector which consists of a real ( $\alpha$ ) as well as an imaginary ( $\beta$ ) part. As an example, the 3 phase line-modulating signals  $v_c^{abc} = [v_{ca} v_{cb} v_{cc}]^T$  can be expressed by the complex vector  $\dot{v}_c = v_c^{\alpha\beta} = [v_{ca} v_{c\beta}]^T$  through the following transformation:

$$v_{c\alpha} = \frac{2}{3} [v_{c\alpha} - 0.5(v_{cb} + v_{cc})]$$

1.15

$$v_{c\beta} = \frac{\sqrt{3}}{3} [v_{cb} - v_{cc}]$$

1.16

Assuming the line-modulating signals  $v_c^{abc}$  are balanced three sinusoidal voltage waveforms which attribute a magnitude  $\hat{v}_c$  at an angular frequency  $\omega$ , the ensuing signals used for modulation in the  $\alpha\beta$  stationary frame provides a vector  $\overrightarrow{v_c} = v_c^{\alpha\beta}$  at fixed module  $\hat{v_c}$ , that

rotates with a frequency  $\omega$  (Fig. 1.20). Also, the SV transformation is applicable to the line voltage signals of the eight states of the VSI normalized concerning  $v_i$  as given in Table 1.3, that creates the eight space vectors ( $\overrightarrow{v_i}$ , i = 1, 2, ..., 8) in Fig. 1.20. As accepted,  $\overrightarrow{v_1}$  to  $\overrightarrow{v_6}$  are non-null line-voltage vectors  $\overrightarrow{v_7}$  and  $\overrightarrow{v_8}$  are null line-voltage vectors.

Fig.1.20 Space-Vector representation

The objective of the space vector modulation scheme is to estimated the line-modulating space vector  $\overrightarrow{v_c}$  using the eight space vectors  $(\overrightarrow{v_l}, i = 1, 2, ..., 8)$  presented in VSIs. On the other hand, if the modulating signal  $\overrightarrow{v_c}$  lies between the random vectors  $\overrightarrow{v_l}$  and  $\overrightarrow{v_{l+1}}$ , only the closest two non-zero vectors  $(\overrightarrow{v_l}$  and  $\overrightarrow{v_{l+1}})$  and one zero space vector  $(\overrightarrow{v_z} = \overrightarrow{v_7} \text{ or } \overrightarrow{v_8})$  can be used. Hence the highest load line voltage is increased and the frequency of switching is reduced. To certify that the developed voltage in one time period  $T_s$  of sampling (made up of the voltages produced by the vectors  $\overrightarrow{v_l}$ ,  $\overrightarrow{v_{l+1}}$ , and  $\overrightarrow{v_z}$  used at times  $T_i$ ,  $T_{i+1}$ , and  $T_z$ ) is on an average same as to the vector  $\overrightarrow{v_c}$ , the subsequent equation must hold:

$$\overrightarrow{v_c}.T_s = \overrightarrow{v_i}.T_s + \overrightarrow{v_i} + 1.T_i + 1 + \overrightarrow{v_z}.T_z$$

1.17

For a line-load voltage that features an amplitude restricted to  $0 \le \hat{v}_c \le 1$ , the solution of the real and imaginary parts of Eq. (1.15) gives

$$T_i = T_s.\,\hat{v}_c.\sin(\frac{\pi}{3} - \theta)$$

1.18

$$T_{i+1} = T_s \cdot \hat{v}_c \cdot \sin(\theta)$$

1.19

$$T_z = T_s - T_i - T_{i+1} 1.20$$

The previous equations represent that the magnitude of the highest line-voltage fundamental magnitude is unity for  $0 \le \theta \le \pi/3$ . This is created an improvement over the SPWM method which gains a  $\sqrt{3}/2$  highest value of magnitude of line-voltage fundamental under the linear operating area. While, space vector modulation (SVM) strategy decides on the vectors usable and their turn-on times, it does not decide the sequence at which they are used, the choice of the zero space vector, and the normalized sampled frequency. As an illustration, if the modulating line-voltage vector is in segment 1 (Fig. 1.20), the vectors  $\overrightarrow{v_1}$ ,  $\overrightarrow{v_2}$ , and  $\overrightarrow{v_z}$  is to be taken within a sampling time by time intervals denoted by  $T_1$ ,  $T_2$ , and  $T_z$ , respectively.

However, whether the sequence, or any other sequence should actually be used, remains a question.

(i)

$$\overrightarrow{v_1} - \overrightarrow{v_2} - \overrightarrow{v_z}$$

,

(ii)

$$\overrightarrow{v_z} - \overrightarrow{v_1} - \overrightarrow{v_2} - \overrightarrow{v_z}$$

,

$$(iii)\overrightarrow{v_z} - \overrightarrow{v_1} - \overrightarrow{v_2} - \overrightarrow{v_1} - \overrightarrow{v_2}$$

$$(\mathrm{iv})\overrightarrow{v_z} - \overrightarrow{v_1} - \overrightarrow{v_2} - \overrightarrow{v_2} - \overrightarrow{v_z} - \overrightarrow{v_2} - \overrightarrow{v_1} - \overrightarrow{v_2}$$

However, the method does not clarify if  $\overrightarrow{v_z}$  should be  $\overrightarrow{v_7}$ ,  $\overrightarrow{v_8}$ , or a combination of both.

# B. Space-vector patterns and Zero Space-vector optimization

The sequence followed for the line-voltages of load which characterize quarter-wave symmetry for minimizing undesired harmonics (even harmonics). In addition, the zero SV optimization must be carried out to reduce the switching frequency. Even though there is no systematic process to develop sequence for SV, a graphical presentation depicts that the sequence  $\vec{v}_i$ ,  $\vec{v}_{i+1}$ ,  $\vec{v}_z$  (where  $\vec{v}_z$  is alternately chosen from  $\vec{v}_1$  and  $\vec{v}_2$ ) can provide improved performance in terms of reducing undesired harmonics and minimizing the switching frequency.

# C. The Normalized Sampling Frequency

In three-phase carrier based PWM schemes, the normalized carrier frequency  $m_f$  is opted to be an odd multiple of 3 ( $m_f = 3*n$ , where, n = 1, 3, 5, ...). Hence, it is possible to remove non-intrinsic harmonics from the PWM waveforms. For the SVM technique, a similar process may be used to reduce uncharacteristic harmonics. Thus, it is obtained that the normalized frequency of sampling  $f_{sn}$  must be an integer multiple of 6. Such a case arises because to provide symmetrical line voltages, all the sectors (total of 6) must be equally used in one time period.

#### 1.5 Harmonics in Inverters

In today's world, with the growing utilisation of power electronics switches, the quality of electrical power, towards the energy efficiency, has become a major challenge. The main issues of power quality are the harmonic distortion, voltage unbalance, voltage sag/swell which represents the deviation between the ideal sinusoidal signal of the network voltage or the load current should have, and what really it is as depicted in Fig. 1.23. The word harmonics can be defined in the following three ways.

I. "Harmonics are voltages and/or currents present in an electrical network at some multiple of the fundamental frequency."

- II. "Harmonics are any frequency that exists in the system except the fundamental frequency".

- III. "In other words, harmonics appear as the distortion in the desirable sinusoidal waveform in power line".

Fig. 1.21 Harmonics in Power System

#### 1.5.1 Source of Harmonics in Inverters

Power electronic inverters produce flat-topped wave-shapes with sharp voltage rise and fall due to switching operation of the semiconductor switches, injecting substantial harmonics into the load that lead to its undesired behaviour.

Also, non-linear load which creates a current waveform differed from the applied voltage wave causes Harmonics in the power converter. The non-linear load involves power semiconductor switches such as diodes, thyristors, SCRs, or transistors etc.

A non-linear load changes its impedance value with the change of instantaneous applied voltage, causing a non-sinusoidal current to be drawn. Alternately, this type of load does not have a constant relation between current and voltage along the alternating time period. The simplest circuit to express a non-linear load is a diode-rectifier, with its different topologies (half-wave diode rectifier, full-wave diode rectifier). Few more examples of non-linear loads, capable of injecting harmonics are as follows: industrial equipments (welding, arc furnace), variable frequency drives (VFD), line-switched rectifiers, switch-mode power supplies, lighting ballasts and also modern electronic equipments, at low load levels, even they could be designed to optimize efficiency around it's rated working value. All these circuits contain semiconductor power switches such as diodes, thyristors (SCR's), transistors etc.

# 1.5.2 Problems Caused by Inverter Harmonics

Harmonic currents aggravate the RMS current in electrical network and degrade the supply voltage quality. They offer stress to the electrical network and indirectly damage the connected appliances. This may also hamper the normal operation of the devices and enhance operating costs. Also, power factor degrades as the input current wave shape changes from

sinusoidal to some distorted signal causing large amount of harmonics. Thus the overall system efficiency and voltage regulation are reduced significantly.

# 1.5.3 Techniques of Harmonic Elimination

Few major techniques of harmonic mitigations are explained below:

#### • Passive Filters:

Now days at the receiving end those who consume electrical power is transmitted to various electronic modules say AC- DC conversion device, adjustable motor drive unit, various switch mode power supply unit. All the above mentioned systems are operated on power semiconductor switches which provide the nonlinear characteristics & because of this non linear attributes, the receiver will inject large amount of harmonics in the distribution system & will also influence the other consumers by this contamination of harmonic in system. Generally, harmonic filter is reasonably vital for the enhancement of power quality of the system. Harmonic deformation in the system is very cosmic problem for the entire power electronic researcher & they continuously worked upon the improvement of harmonic component in the system to construct an efficient & clean consumer based electrical utilities in very determinant, with high voltage regulation & maximum efficiency. Passive filters are quite useful for lessening of harmonic component & used conventionally. Passive filters are the most traditional process for the improvement of harmonic in the electrical power system over decades & there has been constant development in this regard for the optimal use of filter & modification of their features to achieve the optimal approach of consumption with reduced cost & rating. They can be used in six pulse three phase converter for the elimination of harmonic component & also gives the reactive power compensation to improve the power quality. Hence by doing so the cost of the extra needed capacitor for the supply of extra kVAr in the line to balance the reactive power will be reduced and thus power quality issues resolves.

#### Passive series filter-

A passive type series filter has characteristics of both purely inductive type or LC tuned features. The main element used in passive series filter are AC line reactor & DC link filter.

#### Passive shunt filter-

This has been the most usual method for the elimination of harmonic content in distribution system. Such filter is basically designed as either single tuned or band pass filter technique. In accordance with the name, shunt filters are connected in the system shunted with the load. Such passive filter gives a very low impedance in the circuit at the tuned frequency to switch all the related current & at given tuned frequency. The problem is that passive filter always offers some reactive power in the line, hence the design of passive shunt filter serves the two

purposes- one is the filtration purpose & other one is to support reactive power compensation for correcting the power factor in the network in a proper manner. The benefit of passive shunt type filter is that it carries only a fraction of load current, thus the overall power losses are less as compared to series type filter [47].

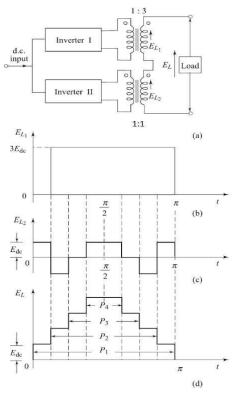

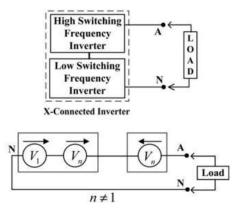

# • Stepped wave Inverters: