## ANALYSIS OF THREE LEVEL BI-DIRECTIONAL DC –DC CONVERTER AND ITS APPLICATION IN ELECTRIC VEHICLE

This thesis is submitted in the partial fulfilment of the requirements of the degree

# MASTER OF ELECTRICAL ENGINEERING (CONTROL SYSTEM)

Submitted by

#### Rahul Kumar

Examination Roll Number: M4ELE22012B

Registration Number: 154006 of 2020- 2021

Under the Guidance of

Dr. Sayantan Chakraborty

Department of Electrical Engineering

Faculty of Engineering and Technology

JADAVPUR UNIVERSITY

KOLKATA-700032

November, 2022

# Faculty of Engineering and Technology JADAVPUR UNIVERSITY

#### **Kolkata-700032**

#### **Certificate of Recommendation**

This is to certify that Mr. Rahul Kumar (002010802012) has completed his dissertation entitled, "Analysis of Three Level Bi-directional DC— DC Converter and its Application in Electric Vehicle", under the direct supervision and guidance of Dr. Sayantan Chakraborty, Department of Electrical Engineering, Jadavpur University. We are satisfied with his work, which is being presented for the partial fulfilment of the degree of Master of Electrical Engineering(Control System) of Jadavpur University, Kolkata-700032.

| Dr. Sayantan Chakraborty               | Prof. Saswati Mazumdar              |  |  |

|----------------------------------------|-------------------------------------|--|--|

| Assistant Professor,                   | Head of the Department,             |  |  |

| Electrical Engineering Department      | Electrical Engineering Department,  |  |  |

| Jadavpur University, Kolkata-700032    | Jadavpur University, Kolkata-700032 |  |  |

| ······································ |                                     |  |  |

| Dr. Bhaskar Gupta                      |                                     |  |  |

| Dean                                   |                                     |  |  |

Faculty of Engineering & Technology

Jadavpur University, Kolkata 700032

# Faculty of Engineering and Technology JADAVPUR UNIVERSITY

#### Kolkata-700032

#### **Certificate of Approval**

The foregoing thesis entitled "Analysis of Three Level Bi-directional DC – DC Converter and its Application in Electric Vehicle" is hereby approved as a creditable study of an Engineering subject carried out and presented in a manner satisfactory to warrant its acceptance as a pre-requisite to the degree of Master of Electrical Engineering(Control System) for which it has been submitted. It is understood that, by this approval the undersigned does not necessarily endorse or approve any statement made, opinion expressed, or conclusion therein but approve this thesis only for the purpose for which it is submitted.

# Signature of the Examiners

**Final Examination for Evaluation of the Thesis**

**Declaration of Originality**

I hereby declare that this thesis contains a literature survey and original research

work by the undersigned candidate, as part of his Master of Electrical

Engineering(Control System) curriculum. All information in this document

has been obtained and presented in accordance with academic rules and

ethical conduct. I also declare that, as required by these rules and conduct, I

have fully cited and referenced all material and results that are not original to

this work.

Name: Rahul Kumar

Examination Roll No.: M4ELE22012B

Thesis Title: Analysis of Three Level Bi-directional DC -

**DC** Converter and its Application in Electric Vehicle

Signature with Date:

iv

#### **ACKNOWLEDGEMENT**

I sincerely thank my supervisor, Dr. Sayantan Chakraborty, Department of Electrical Engineering, Jadavpur University, Kolkata, for his invaluable guidance, suggestions, encouragement, and constant support throughout my thesis work, which helped me in successfully completing it. It was a great honour for me to pursue my research under his supervision.

I would also like to thank all my classmate Ritam Halder, Soumik Dey for his continuous help and support without which this would not have been possible.

I would like to express my gratitude towards all the staffs of control systems laboratory for providing constant encouragement throughout my thesis work.

Last but not the least, I extend my words of gratitude to my parents, Mr. Surya Narayan Mahto and Mrs. Uma Devi, for their endless love support to guide me through every thick and thin of life.

Rahul Kumar

Jadavpur University,

Kolkata - 700032

#### **ABSTRACT**

Ultra-capacitors, are widely employed in power conversion systems such as controlled electric drives, active filters, power conditioners, and uninterruptible power supplies. The ultracapacitor is used as a form of energy storage since it has a short charge/discharge time. The ultracapacitor is connected to the power conversion system via an interface dc-dc power converter to improve flexibility and efficiency. The dc-dc power converter employs a variety of topologies, including isolated soft-switched dc-dc converters and non isolated two-level single-phase or multiphase interleaved converters.

The significant challenges faced by the engineers in the design and implementation of advanced electric drives are the recovery of the braking energy and the drive system's ability to ride over obstacles. In some applications, such as traction and lift drives, an approach based on the standard diode front-end-drive converter fitted with an energy-storage component is utilized in addition to the conventional alternatives, such as back-to-back and matrix converters. With the rapid development of electrochemical double layer capacitors, often known as ultra-capacitors, this strategy has recently gained attention.

The drive is connected to the ultracapacitor through a dc-dc converter to increase system flexibility and efficiency. The converter is managed in a fashion that satisfies the three control goals of peak-power filtering, ultracapacitor state of charge management, and dc-bus voltage management. Using an ultracapacitor as an energy storage and backup power source, we have covered the modelling and control components of the regenerative controlled electric motor in this study.

#### **Contents**

| ABSTRACT                                                        | V  |

|-----------------------------------------------------------------|----|

| List of Abbreviationsi                                          | X  |

| List of Figures                                                 | X  |

| List of Tablesxii                                               | ii |

| Chapter 1 : Introduction & Literature Survey                    | 1  |

| 1. Introduction                                                 | 1  |

| 1.1 Conversion of Unidirectional to Bi-Directional DC-DC        |    |

| Converter                                                       | 1  |

| 1.2 Types of Bidirectional DC DC Converter                      | 2  |

| 1.3 Non Isolated bidirectional DC DC Converter topologies       | 3  |

| 1.3.1Construction of Impedance Networks                         | 3  |

| 1.3.1.1 Inductor + Inductor type                                | 3  |

| 1.3.1.2 Capacitor + Capacitor type                              | 4  |

| 1.3.1.2 Inductor + Capacitor type                               | 5  |

| 1.3.1.2 Hybrid/Cascaded                                         | 6  |

| 1.3.2 Current Status of Non Isolated                            |    |

| Bi-Directional DC- DC Converter topologies Research             | 6  |

| 1.3.3 Comparison and Evaluation of Typical Non Isolated         |    |

| Bi-Directional DC- DC Converter topologies Research             | 8  |

| 1.4 Isolated Bidirectional DC-DC Converter topologies           | 9  |

| 1.4.1Voltage fed Bi-Directional DC- DC Converter                | 9  |

| 1.4.1.1 Basic Voltage fed Isolated Bi-Directional DC- DC        |    |

| Converter                                                       | 9  |

| 1.4.1.2 Dual Active Bridge Bi-Directional DC- DC                |    |

| Converter1                                                      | 0  |

| 1.4.1.3 Z Source and Quasi Z-Source Bridge Bi-Directional       |    |

| DC- DC Converter1                                               | 1  |

| 1.4.1.4 Interleaved Isolated Bi-Directional DC- DC              |    |

| Converter1                                                      | 3  |

| 1.5 Evaluation and Comparison of Common Isolated Bi-Directional |    |

| DC- DC Converter                                                | 5  |

| 1.6 Limitations and Prospects of Bi-Directional DC-DC                       |      |

|-----------------------------------------------------------------------------|------|

| Converter                                                                   | 16   |

| 1.7 Thesis Outline                                                          | 17   |

| Chapter 2 : Comparative Analysis of 3-level Bi-Directional DC- DC Converter | 18   |

| 2.1 Three level Interface DC-DC Converter                                   | 18   |

| 2.1.1 Working Principle                                                     | 19   |

| 2.2 Comparison of 3-level converter with state of art convert               | er21 |

| 2.2.1 Drive Cycle Characteristics                                           | 22   |

| 2.2.2 Magnetic Component Size                                               | 23   |

| 2.2.3 Semiconductor Selection Guidelines                                    | 24   |

| 2.3 Loss Mechanism and Efficiency Analysis                                  | 25   |

| 2.3.1 Switching Losses                                                      | 25   |

| 2.3.2 Conduction Losses                                                     | 26   |

| 2.3.3 Inductor Losses                                                       | 27   |

| 2.3.4 Efficiency Analysis                                                   | 27   |

| 2.3.5 Control Complexity                                                    | 28   |

| 2.4 Conclusion                                                              | 28   |

| Chapter 3: Ultra Capacitor for Power Conversion application                 | 29   |

| 3.1 The Ultra Capacitor                                                     | 29   |

| 3.1.1 Short History of Ultra Capacitors                                     | 29   |

| 3.1.2 Overview of different technologies                                    | 30   |

| 3.1.3 Electric Double layer Capacitors-EDLC                                 | 30   |

| 3.2 The Ultra-Capacitors Macro(Electric-Circuit) model                      | 31   |

| 3.2.1 Full Theoretical Model                                                | 31   |

| 3.2.2 Simplified Model                                                      | 33   |

| 3.3 The Ultra Capacitor Charge/Discharge Method                             | 35   |

| 3.3.1 Constant Resistive Load                                               | 35   |

| 3.3.2 Constant Current                                                      | 35   |

| 3.3.2.1 Discharging                                                         | 35   |

| 3.3.2.2 Maximum Discharge Power                                             | 36   |

| 3.3.3 Charging                                                            | 36   |

|---------------------------------------------------------------------------|------|

| 3.3.3.1 Maximum Charging Power                                            | 36   |

| 3.3.4 Constant Power                                                      | 37   |

| 3.3.4.1 Discharging                                                       | 37   |

| 3.3.4.2 Maximum Discharge Power                                           | 37   |

| 3.3.4.3 Charging                                                          | 38   |

| 3.3.4.4 Maximum Charging Power                                            | 38   |

| 3.4 Trends in Development of Ultra Capacitors                             | 38   |

| 3.5 Conclusion                                                            | 39   |

| <b>Chapter 4 : Regenerative Electric Drives based on ultra capacitors</b> | 40   |

| 4.1 Introduction                                                          | 40   |

| 4.2 Operational Modes                                                     | 40   |

| 4.2.1 Definition of Reference Voltages                                    | 40   |

| 4.3 Ultra-Capacitor Selection and Design                                  | 44   |

| 4.3.1 Voltage Rating                                                      | 45   |

| 4.3.2 The Capacitance                                                     | 45   |

| 4.3.3 Current Stress and Losses                                           | 45   |

| 4.3.4 Conversion Efficiency                                               | 46   |

| 4.4 Modelling Aspects and Control Scheme                                  | 46   |

| 4.4.1 Modelling Techniques                                                | 46   |

| 4.4.2 The DC-DC Converter Model                                           | 46   |

| 4.4.2.1 Large Signal Model                                                | 47   |

| 4.4.2.2 Linearization and Small Signal                                    | 48   |

| 4.5 Control Scheme                                                        | 49   |

| 4.5.1 The Ultra-Capacitor and the DC Bus Voltage Contr                    | ol49 |

| 4.6 The Controller(s) Synthesis                                           | 50   |

| 4.6.1 The Ultra Capacitor Voltage Controller                              | 50   |

| 4.6.2 The DC Bus Voltage Controller                                       | 54   |

| 4.7 Conclusion                                                            | 57   |

| Chapter 5 : Conclusion                                                    | 59   |

| 5.1 Contribution of the thesis                                            | 59   |

| 5.2 Scope of the Future                                                   | 60   |

| REFERENCES                                                                | 61   |

#### **List of Abbreviations**

BDC : Bidirectional DC- DC Converter

UC : Ultra-capacitor EV : Electric Vehicle

TLC : Three Level Converter

CBC : Conventional Two Level Converter BIC : Bidirectional Interleaved Converter

CCM : Continuous Conduction Mode

SOC : State of Charge

PWM : Pulse Width Modulation

UDDS : Urban Dynamometer Driving Schedule

UPS : Uninterrupted Power Supply

MM : Motoring ModeSTB : Standby Mode

MC : Motoring Energy Recovery Mode

RT : Ride Through Mode

MM-CH: Ultra-capacitor Charging Mode

DAB : Dual Active Bridge

HESS : Hybrid Energy Storage System

HEV : Hybrid Electric Vehicle

IPSPM: Interior Permanent Magnet Synchronous

Motor

## **List of Figures**

| Fig. No.    | Title                                                                                                                          |    |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|----|--|--|

| Fig. 1.1(a) | Unidirectional buck converter                                                                                                  | 2  |  |  |

| Fig. 1.1(b) | Unidirectional boost converter                                                                                                 | 2  |  |  |

| Fig.1.1(c)  | Transformation to bidirectional converter by substituting diodes with a controllable switch[3]                                 | 2  |  |  |

| Fig. 1.2    | Classification of Bidirectional DC-DC converter[4]                                                                             | 3  |  |  |

| Fig. 1.3    | The derivation of inductor + inductor impedance network[5]                                                                     | 4  |  |  |

| Fig. 1.4    | The derivation of capacitor + capacitor impedance network[4]                                                                   | 5  |  |  |

| Fig. 1.5    | The derivation of inductor + capacitor impedance network[4]                                                                    | 6  |  |  |

| Fig. 1.6(a) | Bidirectional flyback converter                                                                                                | 10 |  |  |

| Fig. 1.6(b) | Bidirectional push-pull converter                                                                                              | 10 |  |  |

| Fig. 1.7    | Resonant DAB converter[5]                                                                                                      | 11 |  |  |

| Fig. 1.8    | Z source bidirectional full-bridge DC-DC converter[5]                                                                          | 12 |  |  |

| Fig.1.9     | Quasi-Z source bidirectional full-bridge DC-DC converter[5]                                                                    | 12 |  |  |

| Fig.1.10    | Two phase interleaved bidirectional DC-DC converter                                                                            | 13 |  |  |

| Fig. 1.11   | Three phase $\Delta - \Delta$ interleaved LLC resonant bidirectional DC-DC converter[7]                                        | 14 |  |  |

| Fig. 1.12   | Three phase Y-Y interleaved LLC resonant bidirectional DC-DC converter[7]                                                      | 14 |  |  |

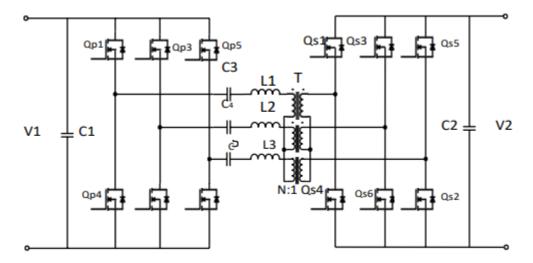

| Fig. 2.1    | Shows the circuit diagram for a three-level bidirectional dc-dc converter interface                                            | 18 |  |  |

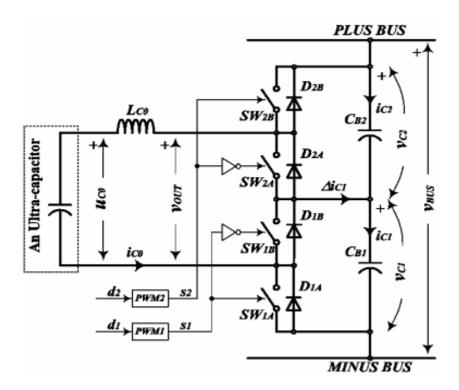

| Fig. 2.2    | Equivalent circuits for steps A, B, C, and D                                                                                   | 19 |  |  |

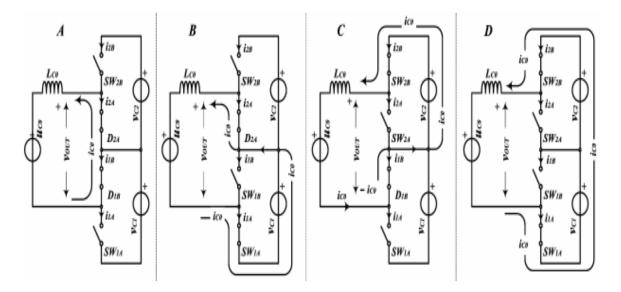

| Fig. 2.3    | Shows the several topological stages of the three-level dc- dc converter. Ideal waveforms for d<1/2 and d>1/2, respectively    | 20 |  |  |

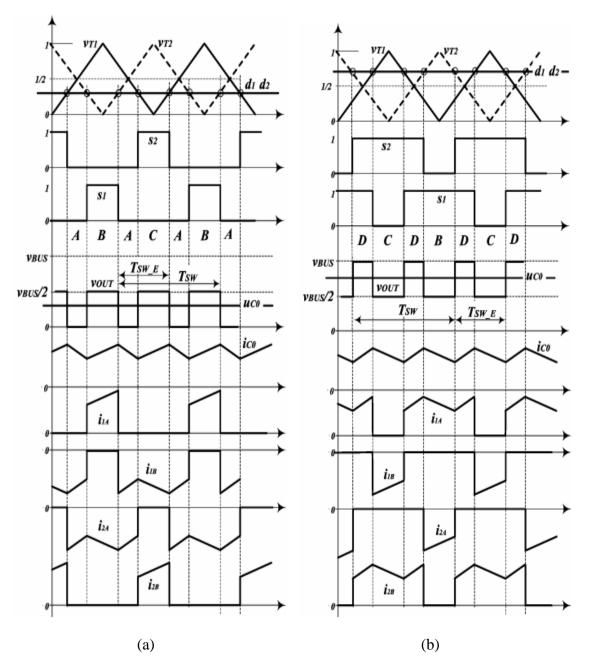

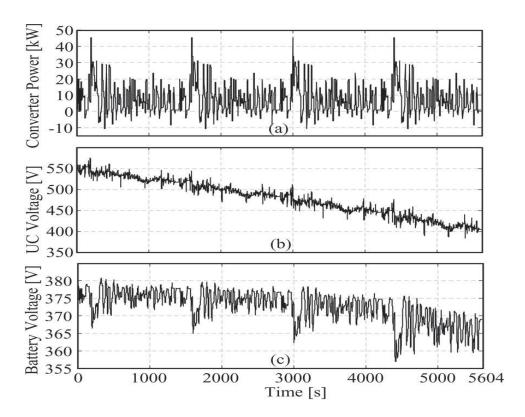

| Fig. 2.4    | Dynamic variations of state variables [27](a) Converter power.(b) UC voltage. (c) Battery voltage                              | 22 |  |  |

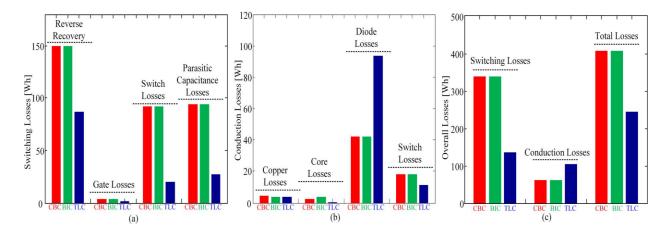

| Fig. 2.5    | Energy losses at the switching frequency of 20 kHz[27] (a) Switching losses. (b) Conduction and core losses. (c) Overall loss  | 26 |  |  |

| Fig.2.6     | Energy losses at the switching frequency of 100 kHz[27] (a) Switching losses. (b) Conduction and core losses. (c) Overall loss | 27 |  |  |

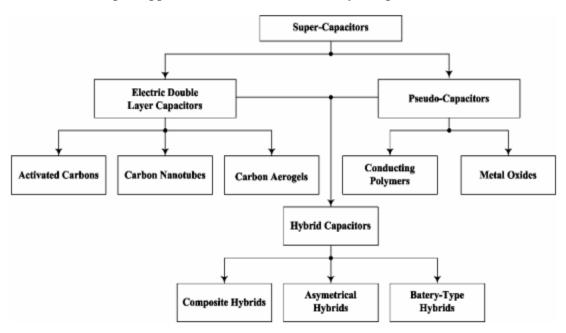

| Fig. 3.1    | Taxonomy of the ultra-capacitors                                                                                               | 30 |  |  |

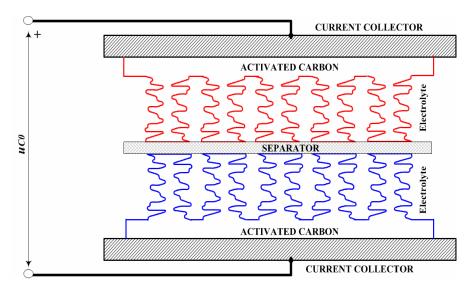

| Fig.3.2     | Construction of an electrochemical double layer capacitor with porous electrodes (activated carbon)                            | 31 |  |  |

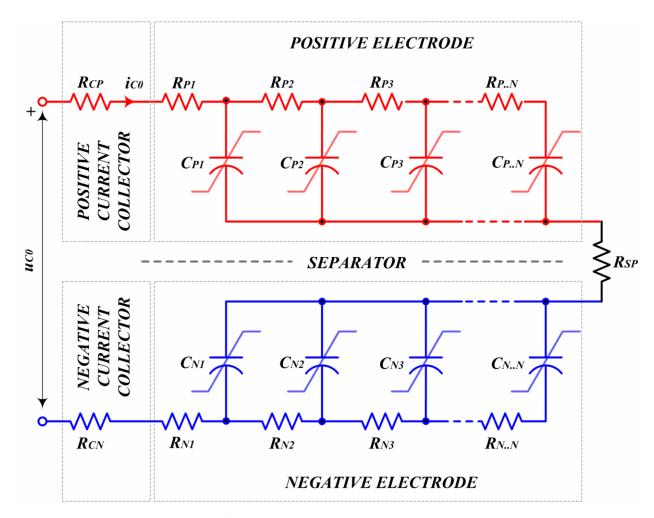

| Fig.3.3     | An approximation of the electrochemical double layer capacitor that takes the electrodes' porosity into consideration          | 32 |  |  |

| Fig. 3.4  | Nth order equivalent model of an electrochemical double                | 22 |

|-----------|------------------------------------------------------------------------|----|

|           | layer capacitor                                                        | 33 |

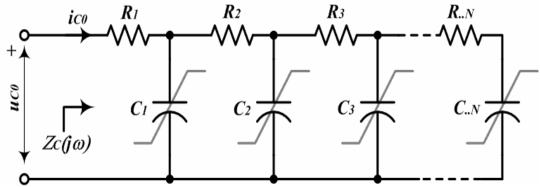

| Fig. 3.5  | Ultra-capacitor simple RC model                                        | 34 |

| Fig. 3.6  | The power conversion using ultra-capacitors                            |    |

|           | and resistors. A charging and a discharging                            | 35 |

|           | process                                                                |    |

| Fig. 3.7  | Using a continuous current source to charge and discharge              |    |

|           | the ultracapacitor                                                     | 35 |

| Fig. 3.8  | Using a constant power supply to charge and discharge                  |    |

|           | an ultracapacitor                                                      | 37 |

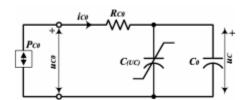

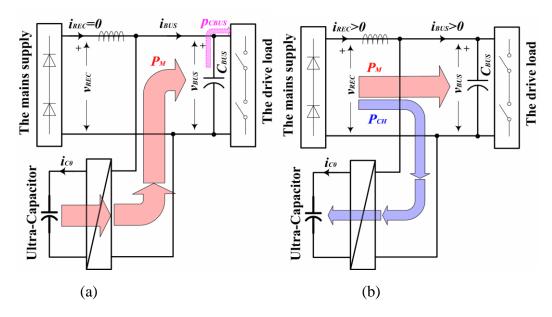

| Fig.4.1   | Using a constant power supply to charge and discharge                  |    |

|           | an ultracapacitor                                                      | 41 |

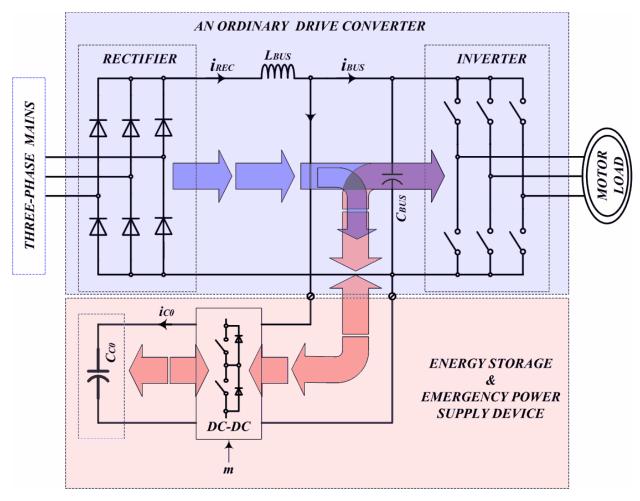

| Fig.4.2   | The power flow for various operation modes are                         |    |

|           | following a) The mains motoring mode (MM) and b) the                   | 42 |

|           | braking mode                                                           |    |

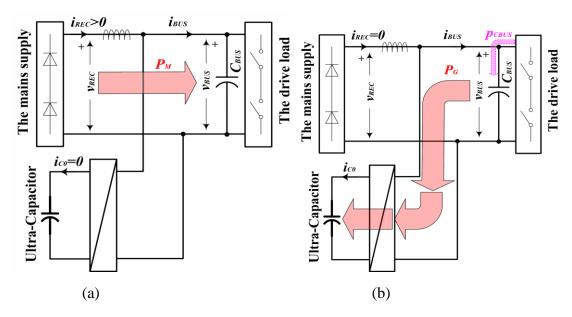

| Fig.4.3   | The power flow for each of the following operating                     |    |

|           | modes: a) energy recovery mode (MC0) and ride-through                  | 43 |

|           | mode (RT); b) the ultra-capacitor charging mode (MM-                   |    |

|           | CH)                                                                    |    |

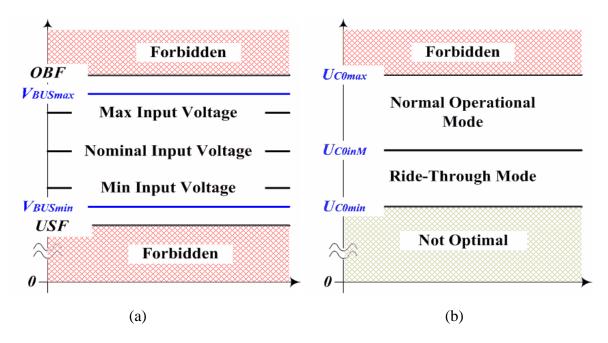

| Fig. 4.4  | The reference voltages are defined in as (a) V <sub>BUSmax</sub> ,     |    |

| 8.        | (b) $V_{BUSmin}$ , and (c) $U_{C0min}$ , $U_{C0inM}$ , and $U_{C0max}$ | 44 |

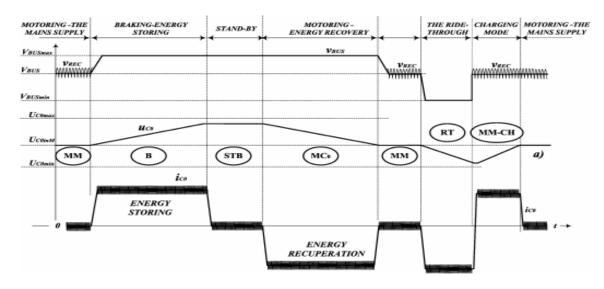

| Fig. 4.5  | The waveforms for the various operating modes                          | 44 |

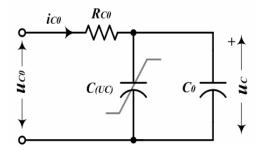

| Fig. 4.6  | Shows the ultra-capacitor's first order RC model                       | 45 |

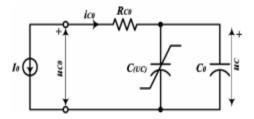

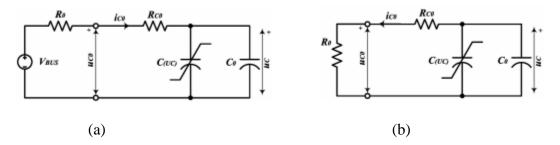

| Fig. 4.7  | Large signal (average) dc-dc converter model                           | 47 |

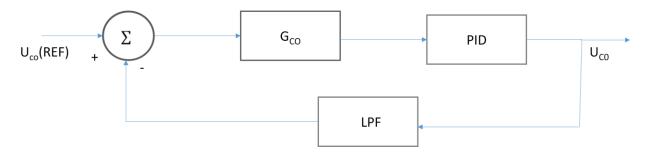

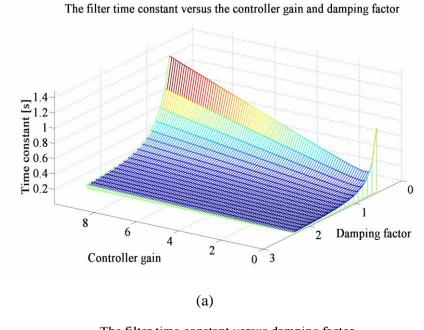

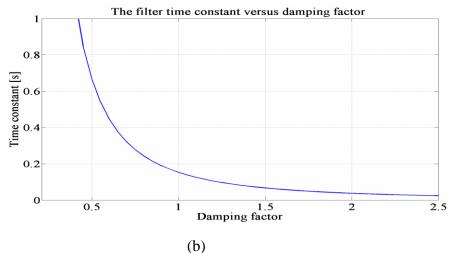

| Fig. 4.8  | The ultra-capacitor voltage closed loop                                | 51 |

| Fig. 4.9  | The filter time constant (TF) vs the controller gain and               |    |

| 118       | damping factor is shown. $R_{C0} = 2$ , $C_{C0} = 3$ , and $k_{C} = 1$ | 53 |

|           | 0.1/700 F/V. (b) TF vs damping factor for a controller                 |    |

|           | with fixed gain, $k_{PC0} = 5$                                         |    |

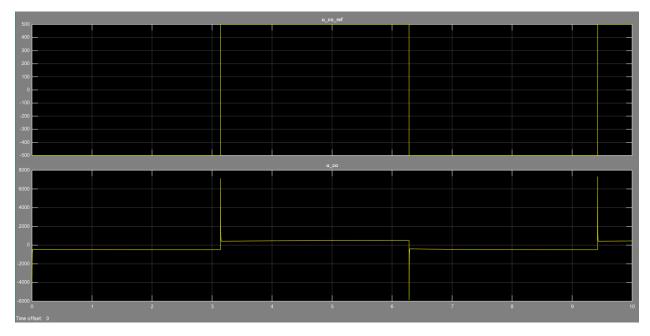

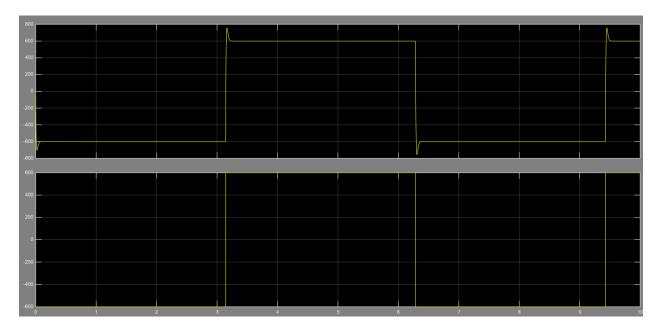

| Fig. 4.10 | Simulated result of ultra-capacitor reference voltage and              |    |

| 115       | ultra-capacitor voltage                                                | 54 |

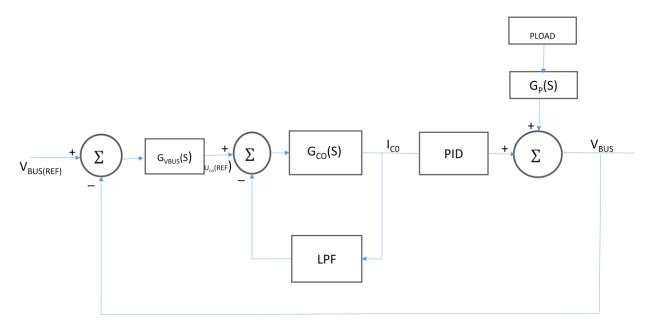

| Fig. 4.11 | Block diagram of DC bus voltage controller                             | 55 |

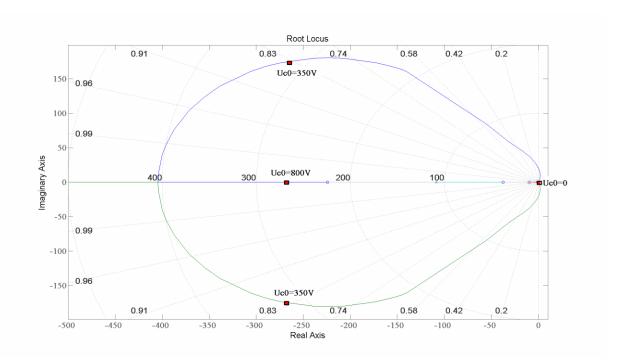

| Fig. 4.12 | The ultra-capacitor voltage $U_{C0}$ in relation to the closed         |    |

| 115. 1.12 | loop root locus of the dc bus voltage. k <sub>PBUS</sub> =0.08,        | 56 |

|           | $k_{IBUS}$ =16, $f_{BUS}$ =25Hz, and $V_{BUS}$ =700V                   | 50 |

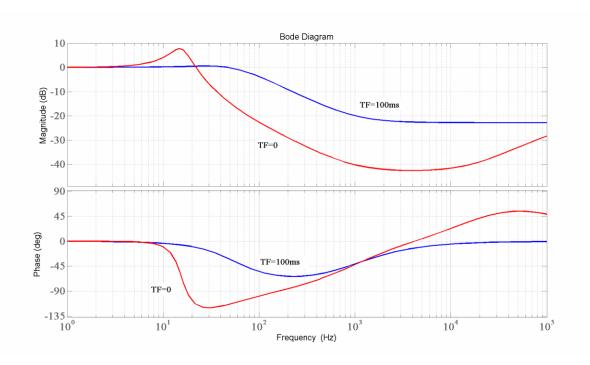

| Fig. 4.13 | Bode diagram of the ultra-capacitor voltage feedback                   |    |

| 118. 7.13 | filter's dc bus voltage transfer function for various time             | 57 |

|           | constants, V <sub>BUS</sub> (s) / V <sub>BUS</sub> (REF)(s)            | 51 |

| Fig. 4.14 |                                                                        |    |

| Fig. 4.14 | Simulated result of DC bus voltage and reference DC bus                | 57 |

|           | voltage                                                                | 31 |

#### **List of Tables**

| Table | Title                                                              |     |  |  |

|-------|--------------------------------------------------------------------|-----|--|--|

| No.   |                                                                    | No. |  |  |

| 1.1   | Advantages and disadvantages of typical non-isolated               |     |  |  |

|       | bidirectional DC-DC impedance networks                             | 8   |  |  |

| 1.2   | Indexes of typical non-isolated bidirectional DC-DC topologies     | 9   |  |  |

| 1.3   | Advantages and disadvantages of isolated bidirectional DC-DC       |     |  |  |

|       | converters                                                         | 15  |  |  |

| 1.4   | Indexes of typical isolated bidirectional DC-DC topologies         | 15  |  |  |

| 2.1   | Converter Currents During Four UDDS (F <sub>S</sub> = 20 KHz) [22] | 24  |  |  |

| 2.2   | Analyzed Converter Specifications [22]                             | 25  |  |  |

| 5.1   | Specification of the Control System                                | 53  |  |  |

#### **CHAPTER 1**

#### BIDIRECTIONAL DC-DC CONVERTER

#### 1. Introduction:

Bi-directional dc-dc converters (BDC) have recently attracted a lot of interest due to the growing demand for systems that can transfer energy bi-directionally between two dc buses. Besides its usual use in dc motor drives, novel BDC applications include energy storage in renewable energy systems, fuel cell energy systems, hybrid electric vehicles (HEV), and uninterruptible power supply (UPS)[1].

The fluctuating nature of most renewable energy supplies, such as wind and sun, makes them unsuitable for use as a sole source of power. To compensate for these oscillations and ensure a smooth and continuous power supply to the load, one typical approach is to deploy an energy storage device in addition to the renewable energy resource. Batteries and supercapacitors are the most widely used and cost-effective energy storage devices in the medium-power range, so a dc-dc converter is always needed to enable energy transfer between storage devices and the rest of the system. A bidirectional power flow converter with flexible control in all working modes is required.

BDCs are used in HEV applications to connect different dc voltage buses and transmit energy between them. A BDC, for example, is used to interchange energy between the main batteries (200-300V) and the drive motor via a 500V direct current link. Some significant requirements for the BDC employed in this application include high efficiency, lightweight, compact size, and high reliability[2].

BDCs are also used in line-interactive UPS systems, which do not employ double conversion technology and hence achieve superior efficiency. During normal mode, energy can be sent back to the inverter's dc bus and used to charge the batteries via a BDC because the line-interactive UPS's output terminals are linked to the grid. In backup mode, the battery supplies the inverter dc bus again via BDC, but in the opposite power flow direction[3].

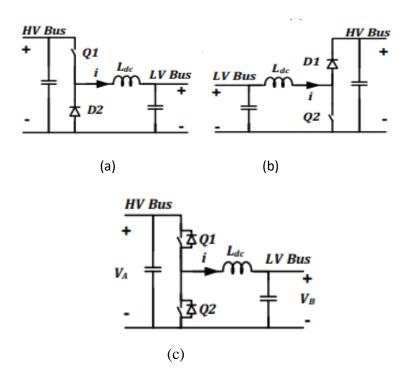

## 1.1 Conversion of Unidirectional DC-DC Converter Bidirectional DC-DC Converter:

Basic dc-dc converters like buck and boost converters are unable to transfer power in both directions. The presence of diodes in their structure prohibits reverse current flow. In general, a unidirectional dc-dc converter can be converted to a bidirectional converter by replacing the diodes with a controllable switch in its structure. An elementary buck and boost converter's structure is depicted in Fig. 1.1, as is the process by which the diodes in the converter can be changed to create a bidirectional converter. It is significant that the converter that is produced has the same structure in both situations.

Fig. 1.1 (a) Unidirectional buck converter, (b) Unidirectional boost converter and (c) transformation to bidirectional converter by substituting diodes with a controllable switch [3]

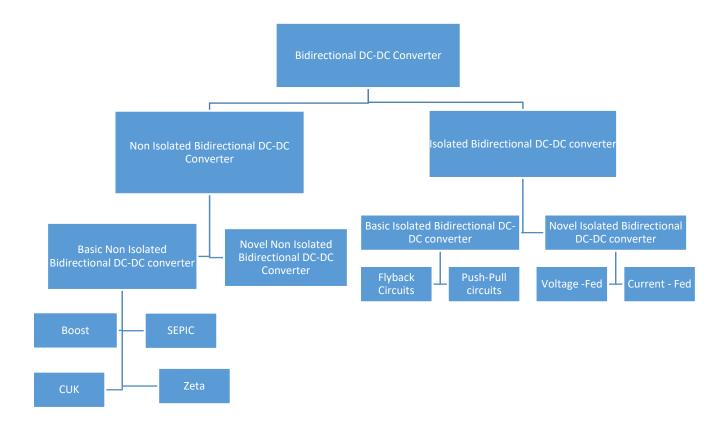

#### 1.2 Types of Bidirectional DC-DC Converter:

The bidirectional dc-dc converter is classified into two types (see in fig.1.2). 1) Non-isolated bidirectional DC-DC converter. 2) Isolated bidirectional DC-DC converter. Non-isolated bidirectional DC-DC converter is an impedance network composed of inductor, capacitor and used to realize direct DC-DC conversion.

#### 1.3. Non-isolated Bidirectional DC-DC Topologies:

# 1.3.1 Construction of Impedance Networks of Novel Non-isolated Bidirectional DC-DC Converters:

The unique non-isolated bidirectional DC-DC converters, which are based on the fundamental bidirectional DC-DC converters, are intended to enhance the functionality of bidirectional DC-DC converters by impedance transformation from the view points of improving the voltage conversion ratio and efficiency, lowering the current ripple on the power source side, lowering the voltage/current stresses of the devices, and enhancing the input and output characteristics. The unique non-isolated DC-DC converter topologies that are now in use are categorized in this research based on various combinations of energy storage components. There are four categories of the unique non-isolated bidirectional DC-DC impedance networks: hybrid/cascaded, inductor + inductor, capacitor + inductor, and inductor + capacitor.

Fig.1.2 Classification of Bidirectional DC-DC Converter [4]

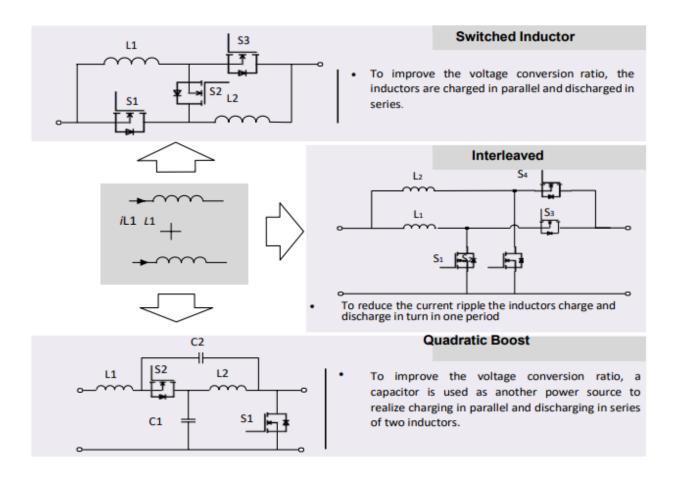

#### **1.3.1.1 Inductor** + **Inductor** type:

Two inductors are charged in parallel and discharged in series to create a switched inductor impedance network, which increases the voltage conversion ratio. An interleaved impedance network is created by turning on each inductor sequentially with the same trigger phase difference in order to eliminate the current ripple on the power source side. In order to achieve parallel charging and series discharging of inductors and obtain the quadratic Boost impedance network, the power source and one capacitor are employed as energy sources, respectively. Fig. 1.3 depicts the approach used to derive inductor + inductor impedance networks.

Fig.1.3 The derivation of inductor + inductor impedance network [5]

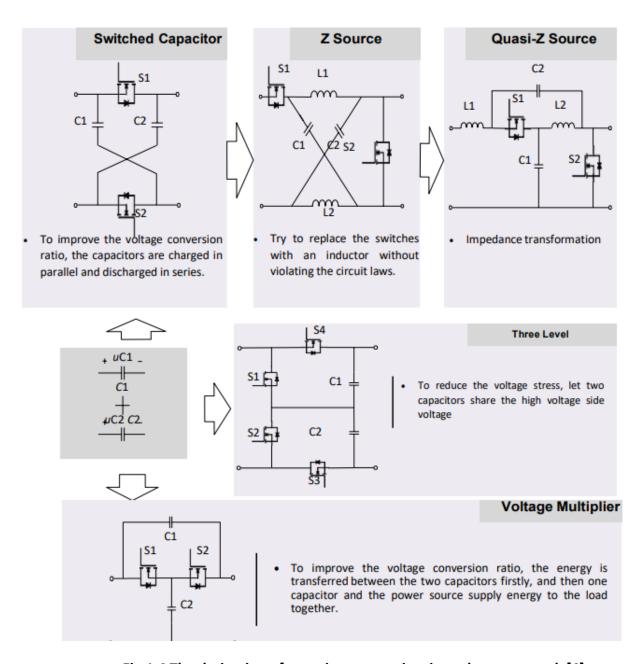

#### **1.3.1.2** Capacitor + Capacitor type:

Two capacitors are charged in parallel and discharged in series to create a switched capacitor impedance network, which increases the voltage conversion ratio. The voltage multiplier (VM) impedance network can be obtained by first transferring energy between the two capacitors, followed by the capacitor and the power source supplying energy to the load at the same time. Inductor and switch only allow current to flow in one direction when the converter is operating steadily. The Z source impedance network can be created by switching the switch in the switched capacitor with an inductor without breaking the circuit rules.

The quasi-Z source impedance network can be created by impedance transforming the Z source in order to fix the defects of discontinuous current at the power source side and non-common ground of the input and output of Z sources. Two capacitors made to tolerate high voltages are combined to create a three level impedance network, which lowers the voltage stress.

Fig.1.4 The derivation of capacitor + capacitor impedance network [4]

#### **1.3.1.3 Inductor** + Capacitor type:

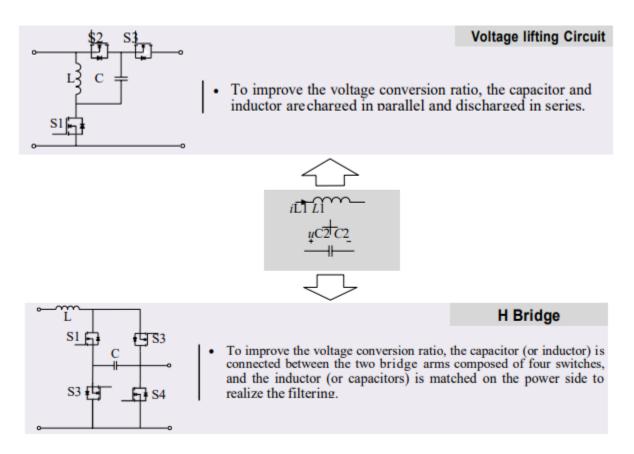

The voltage lifting circuit is created by charging a capacitor and an inductor in parallel and discharging them in series to increase the voltage conversion ratio. Capacitors (or inductors) are connected between the two bridge arms made of four switches to increase the voltage conversion ratio. To achieve filtering, components (such as capacitors) are put on the power source side, generating an H-bridge impedance network. Fig. 1.5 depicts the approach used to derive inductor + capacitor impedance networks.

Fig.1.5 The derivation of inductor + capacitor impedance network [4]

#### 1.3.1.4 Hybrid/Cascaded:

Bidirectional DC-DC converter performance can be improved and new topologies can be created by integrating and cascading the three types of impedance networks mentioned above. The purpose of a cascaded impedance network is to share some devices without breaking the circuit law, connect more than two impedance networks sequentially, and enhance topological performance. In order to achieve topology optimization, functional units of the existing topology can be swapped out for topologies (or impedance networks), yielding a hybrid impedance network. There are numerous publications [3] – [4] on cascaded structure and comparatively few on hybrid structure in the bidirectional DC-DC references that are currently available. The cascaded topologies are the main topic of this work.

#### 1.3.2. Current Status of Non-isolated Bidirectional DC-DC Converter Topologies:

The derivation techniques of the impedance networks of the novel bidirectional DC-DC converters are similar to those of the unidirectional DC-DC converters. When the diode in the unidirectional DC-DC converter is swapped out for the switch, the equivalent bidirectional DC-DC converter architecture is produced.

There are only a few topologies based on switched inductor, switched capacitor, Z source, and voltage raising circuit because Novel Electric Vehicle have high requirements for the input and output common ground, as well as power source side current ripple of bidirectional DC-DC converters. In addition, it is also rare to find references to bidirectional DC-DC converters based on quadratic Boost and hybrid.

There are a number of non-isolated bidirectional DC-DC converter topologies now available, including bidirectional Boost, Cuk, SEPIC topologies, interleaved bidirectional DC-DC topologies, three level bidirectional DC-DC topologies, bidirectional DC-DC topologies based on VM, bidirectional DC-DC topologies based on quasi-Z sources, bidirectional DC-DC topologies based on H bridges, and cascaded.

Table 1.1 Advantages and disadvantages of typical non-isolated bidirectional DC-DC impedance networks

| Classification         | Impedance<br>Network  | Disadvantages                                                                                                                                                |                                                                                                                                                                                                 |

|------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Basic                  | Boost/SEPIC/<br>Cuk   | <ul> <li>Simple Structure</li> <li>Easy to control</li> <li>Easy to generate new topologies</li> <li>Low number of devices</li> </ul>                        | Narrow voltage conversion range                                                                                                                                                                 |

| Inductor +<br>Inductor | Switched<br>Inductor  | <ul> <li>Wide voltage conversion range</li> <li>Easy to control</li> <li>Easy to generate new topologies</li> </ul>                                          | Pulsating current of power sources side                                                                                                                                                         |

|                        | Interleaved           | <ul> <li>Low current ripple of power side</li> <li>Input-Output common ground</li> </ul>                                                                     | <ul> <li>Requiring high control precision</li> <li>Large number of switches</li> </ul>                                                                                                          |

|                        | Quadratic<br>Boost    | <ul> <li>Wide voltage conversion range</li> <li>Continuous power source side current</li> <li>Easy to control</li> <li>Input-Output common ground</li> </ul> | High voltage stress at high voltage side                                                                                                                                                        |

| Capacitor + Capacitor  | Switched<br>Capacitor | Wide voltage conversion range                                                                                                                                | <ul> <li>Input- Output non common ground</li> <li>Pulsating current of power source side</li> </ul>                                                                                             |

|                        | VM                    | <ul><li>Wide voltage conversion range</li><li>Input- Output common ground</li></ul>                                                                          | High voltage stress at<br>high voltage side                                                                                                                                                     |

|                        | Z Source              | High voltage conversion ratio in<br>non extreme duty cycle                                                                                                   | <ul> <li>Discontinuous power source side current</li> <li>Input- Output non common ground</li> <li>Steep slope of voltage conversion ratio</li> <li>Requiring high control precision</li> </ul> |

|            | Quasi-Z Source  | <ul> <li>High voltage conversion ratio in non extreme duty cycle</li> <li>Continuous power source side current</li> <li>Input- Output common ground</li> </ul> | <ul> <li>Requiring high control precision</li> <li>Steep slope of voltage conversion ratio</li> <li>High voltage stress at high voltage side</li> </ul> |

|------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inductor + | Voltage lifting | Easy to generate new topologies                                                                                                                                | No obvious increase in                                                                                                                                  |

| Capacitor  | circuit         | • Input- output common ground                                                                                                                                  | voltage                                                                                                                                                 |

|            |                 |                                                                                                                                                                | Pulsating current of power source side                                                                                                                  |

|            | H bridge        | • Easy to generate new topologies                                                                                                                              | Large no of switches                                                                                                                                    |

|            |                 | • Less number of energy storage devices                                                                                                                        | Requiring high control precision                                                                                                                        |

|            |                 | Input- output common ground                                                                                                                                    |                                                                                                                                                         |

| Hybrid/    | Cascaded        | Wide voltage conversion range                                                                                                                                  | • Large number of devices                                                                                                                               |

| cascaded   |                 | Easy to generate new topologies                                                                                                                                | • Low conversion efficiency                                                                                                                             |

|            |                 |                                                                                                                                                                | Low power density                                                                                                                                       |

|            | Hybrid          | Wide voltage conversion range                                                                                                                                  | • Large number of devices                                                                                                                               |

|            |                 | Easy to generate new topologies                                                                                                                                | • Low conversion efficiency                                                                                                                             |

|            |                 |                                                                                                                                                                | Low power density                                                                                                                                       |

#### 1.3.3 Comparison and Evaluation of Typical Non-isolated Bidirectional DC-DC Converter:

The technology, power source side current, step-up ratio, step-down ratio, duty cycle range, voltage stress of switches, current stress of switches, number of devices, and presence of common ground are the ten comparison criteria used to rank non-isolated bidirectional DC-DC converters in this section. Table 1.2 summarizes the index distribution for nine common non-isolated bidirectional DC-DC topologies.

Table 1.2 Indexes of typical non-isolated bidirectional DC-DC topologies

| Top<br>o<br>Logi<br>es | Technolo<br>gy<br>used           | Power<br>Source<br>Side<br>Current | $\begin{array}{c} \text{Step-up} \\ \text{ratio} \\ U_{\text{high}}/U_{\text{low}} \end{array}$ | Step down ratio $U_{low}/U_{high}$ | Duty-<br>cycle<br>range                                                                                                                                                                                 | Voltage<br>stress of<br>switches | Current<br>stress<br>of switches       | Nun<br>devi | nber<br>ces | of | Com<br>mon<br>groun<br>d |

|------------------------|----------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------|-------------|-------------|----|--------------------------|

| Ref. [8]               | Boost                            | Non<br>Pulsating                   | $\frac{1}{1-d}$                                                                                 | d                                  | 0 <d<1< td=""><td>u<sub>high</sub></td><td><math display="block">\frac{\mathrm{I_{high}}}{1-d}</math></td><td>1</td><td>1</td><td>2</td><td>Yes</td></d<1<>                                             | u <sub>high</sub>                | $\frac{\mathrm{I_{high}}}{1-d}$        | 1           | 1           | 2  | Yes                      |

| Ref. [9]               | Interleave<br>d                  | Low<br>Ripple                      | $\frac{3}{1-d}$                                                                                 | $\frac{d}{3}$                      | 0.67 <d<1< td=""><td><math>\frac{2}{3}</math>u<sub>high</sub></td><td><math display="block">\frac{2I_{\text{high}}}{1-d}</math></td><td>3</td><td>3</td><td>6</td><td>No</td></d<1<>                    | $\frac{2}{3}$ u <sub>high</sub>  | $\frac{2I_{\text{high}}}{1-d}$         | 3           | 3           | 6  | No                       |

| Ref. [10]              | Interleave<br>d + Three<br>level | Low<br>Ripple                      | $\frac{2}{1-d}$                                                                                 | $\frac{d}{2}$                      | 0 <d<0.5<br>0.5<d<1< td=""><td><math>\frac{u_{\text{high}}}{2}</math></td><td><math display="block">\frac{2I_{\text{high}}}{1-d}</math></td><td>2</td><td>4</td><td>5</td><td>No</td></d<1<></d<0.5<br> | $\frac{u_{\text{high}}}{2}$      | $\frac{2I_{\text{high}}}{1-d}$         | 2           | 4           | 5  | No                       |

| Ref. [11]              | Three<br>level                   | Non<br>Pulsating                   | $\frac{2}{1-d}$                                                                                 | $\frac{d}{2}$                      | 0 <d<1< td=""><td><math>\frac{u_{\text{high}}}{2}</math></td><td><math display="block">\frac{2I_{\text{high}}}{1-d}</math></td><td>1</td><td>3</td><td>4</td><td>No</td></d<1<>                         | $\frac{u_{\text{high}}}{2}$      | $\frac{2I_{\text{high}}}{1-d}$         | 1           | 3           | 4  | No                       |

| Ref. [12]              | VM                               | Non<br>Pulsating                   | $\frac{2}{1-d}$                                                                                 | $\frac{d}{2}$                      | 0 <d<1< td=""><td><math>\frac{u_{\text{high}}}{2}</math></td><td><math display="block">\frac{(1+d)I_{\text{high}}}{d(1-d)})</math></td><td>1</td><td>4</td><td>4</td><td>Yes</td></d<1<>                | $\frac{u_{\text{high}}}{2}$      | $\frac{(1+d)I_{\text{high}}}{d(1-d)})$ | 1           | 4           | 4  | Yes                      |

| Ref. [13] | Quasi Z-<br>Quartz | Non<br>Pulsating | $\frac{1+d}{1-d}$         | $\frac{d}{2-d}$       | 0 <d<1< th=""><th><math display="block">\frac{u_{\text{high}}}{1+d}</math></th><th><math display="block">\frac{2I_{\text{high}}}{1-d}</math></th><th>2</th><th>4</th><th>3</th><th>Yes</th></d<1<>                     | $\frac{u_{\text{high}}}{1+d}$     | $\frac{2I_{\text{high}}}{1-d}$                    | 2 | 4 | 3 | Yes |

|-----------|--------------------|------------------|---------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------|---|---|---|-----|

| Ref. [14] | H Bridge           | Non<br>Pulsating | $\frac{1}{1-2d}$          | 2d – 1                | Up:<br>0 <d<0.5<br>Down:<br/>0.5<d<1< td=""><td>u<sub>high</sub></td><td><math display="block">\frac{\mathrm{dI}_{\mathrm{high}}}{(1-d)(1-2d)}</math></td><td>1</td><td>3</td><td>5</td><td>Yes</td></d<1<></d<0.5<br> | u <sub>high</sub>                 | $\frac{\mathrm{dI}_{\mathrm{high}}}{(1-d)(1-2d)}$ | 1 | 3 | 5 | Yes |

| Ref. [15] | Cascaded           | Non<br>Pulsating | $\frac{2+d}{1-d}$         | $\frac{d}{3-d}$       | 0 <d<1< td=""><td><math display="block">\frac{u_{\text{high}}}{2+d}</math></td><td><math display="block">\frac{(1+2d)I_{\text{high}}}{d(1-d)}</math></td><td>2</td><td>6</td><td>5</td><td>No</td></d<1<>              | $\frac{u_{\text{high}}}{2+d}$     | $\frac{(1+2d)I_{\text{high}}}{d(1-d)}$            | 2 | 6 | 5 | No  |

| Ref. [16] | Cascaded           | Pulsating        | $\frac{1+d+d^2}{(1-d)^2}$ | $\frac{d^2}{1+d-d^2}$ | 0 <d<1< td=""><td><math display="block">\frac{u_{\text{high}}}{1+d-d^2}</math></td><td><math display="block">\frac{(1-d)^2 I_{\text{high}}}{1+d-d^2}</math></td><td>2</td><td>4</td><td>5</td><td>No</td></d<1<>       | $\frac{u_{\text{high}}}{1+d-d^2}$ | $\frac{(1-d)^2 I_{\text{high}}}{1+d-d^2}$         | 2 | 4 | 5 | No  |

#### 1.4 Isolated Bidirectional DC-DC topologies:

In comparison to a non-isolated bidirectional DC-DC converter, a high-frequency transformer can ensure galvanic isolation of the input and output in a bidirectional topology for HESS, which can alter the voltage conversion range by varying the turns ratio. Because of their better voltage conversion ratio and ability to accommodate various voltage levels for HESS, isolated bidirectional DC-DC topologies are advantageous. According to various DC power sources, the isolated bidirectional DC-DC converters can be separated into voltage-fed and current-fed types.

Rectifier and inverter units make up the voltage-fed bidirectional DC–DC converter. The current-fed and voltage-fed converters have a similar structural design. The primary distinction is the requirement for an inductor on the DC current source side of current-fed converters and DC source types to reduce current ripple. Considering that current-fed converters are less commonly employed in automotive applications, the current source can be replaced with a voltage source and an inductor.

#### 1.4.1 Voltage-fed Bidirectional DC-DC Converter:

- Basic Isolated Bidirectional DC-DC Converter

- Dual Active Bridge DC-DC Converters

- Z Source and Quasi-Z Source Full-bridge Bidirectional DC-DC Converters

- Interleaved Isolated Bidirectional DC-DC Converter

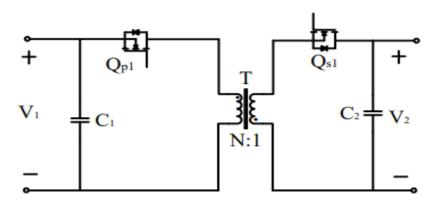

#### 1.4.1.1 Basic Voltage-fed Isolated Bidirectional DC-DC Converter:

Bidirectional flyback and push-pull converters are two common fundamental voltage-fed bidirectional DC-DC converters. Due to their simple designs, small number of components, and quick dynamic response, bidirectional flyback converters are frequently utilized in low-power applications needing galvanic isolation [5]. Because the flyback converter's transformer must accomplish galvanic isolation while also storing energy, the switches must be able to tolerate high voltage and current strains. Both the conversion efficiency and the switching losses are significant. A significant voltage spike will be produced because the high-frequency transformer of push-pull converters has leakage inductance.

Additionally, the converter's reliability is decreased and design complexity is increased by the transformer's Centre tap. With the exception of HESS and Novel Electric Vehicle(NEV), the fundamental voltage-fed isolated converters are acceptable for low-power applications.

(a) Bidirectional flyback converter

(b) Bidirectional push-pull converter

Fig.1.6 Basic bidirectional DC-DC converters [5]

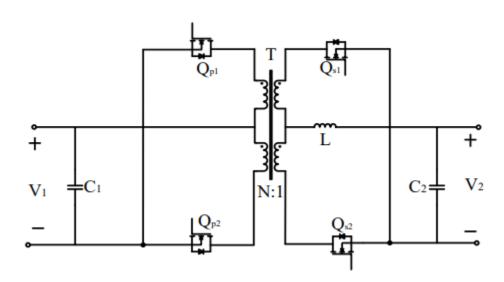

#### 1.4.1.2 DAB Bidirectional DC-DC Topologies:

DAB converters can be divided into resonant and non-resonant variants based on the different arrangements of the primary and secondary sides of the high-frequency transformer. For DAB of

the resonant type, the high-frequency transformer is coupled in series with a soft switching resonant circuit.

Fig.1.7 Resonant DAB converter [5]

The high-frequency transformer for non-resonant DAB converters only has one inductor connected in series. DAB converters, in general, refers to non-resonant DAB converters. Types of the structure include half bridges and full bridges. The advantages of fewer devices and a smaller volume make half bridge structures popular in battery chargers and UPS systems [5]. The dual active full-bridge converter has twice as many switches as a half-bridge converter.

The non-resonant DAB converter's intermediate stage is simply an inductor, which not only allows for bidirectional energy transmission but also offers the advantages of low voltage stress and flexible control. The resonant DAB DC-DC converter can increase the soft switching capabilities and efficiency by inheriting the benefits of the DAB converter. The resonant structure can also be chosen based on the needs of the various applications. However, as the number of resonant parts increases, so does the complexity of the converter and the difficulty of controller design. The bidirectional full-bridge converters are appropriate for HESS of NEV and other high voltage and power situations.

#### 1.4.1.3 Z Source and Quasi-Z Source Full-bridge Bidirectional DC-DC Converters:

Two capacitors and two inductors make up the Z source and quasi-Z source impedance network. Between the power source and the inverter bridge arms of the conventional full-bridge DC-DC converter, the Z source full-bridge DC-DC converter will add a Z source impedance network. Based on this, thyristors are inserted between the power source and the Z source structure to limit the flow of current in one direction [5].

Fig.1.8 Z source bidirectional full-bridge DC-DC converter [5]

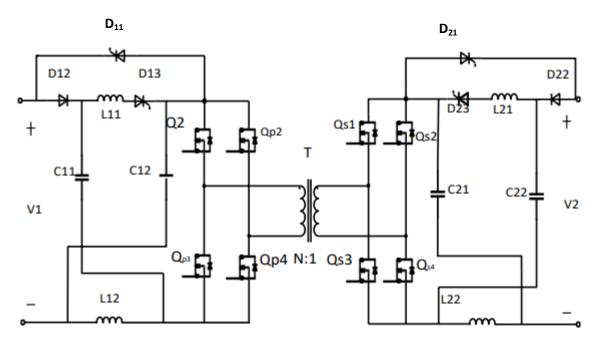

Four thyristor  $D_{11}$ ,  $D_{13}$ ,  $D_{21}$ , and  $D_{23}$  are added to the Z source structure in order to adapt it to the needs of bidirectional energy transfer. In order to provide reverse current, the thyristor  $D_{11}$  is switched on in the reverse power flow and off in the forward power flow. To separate the Z source network into LC filters, the thyristor  $D_{13}$  is turned on in the forward power flow and off in the reverse power flow. Thyristors  $D_{21}$  and  $D_{23}$  perform comparable tasks to those performed by thyristors  $D_{11}$  and  $D_{13}$ . The switching frequency is low because the states of  $D_{11}$ ,  $D_{13}$ ,  $D_{21}$ , and  $D_{23}$  only change when the current flow direction changes, and using thyristors can lower the cost and boost reliability.

Fig.1.9 Quasi-Z source bidirectional full-bridge DC-DC converter [5]

The Z source network is added to the usual DAB structure, thus eliminating the possibility of shoot-through of the same bridge arm and improving conversion efficiency. Since the startup current will decrease system stability and device service life. The starting current and the problem of current discontinuity in the Z-source full bridge structure can both be improved by the quasi-Z source full bridge construction. Therefore mentioned updated converters, however, increase the number of components and the level of design complexity, which lowers system reliability and makes them unsuitable for HESS of NEV.

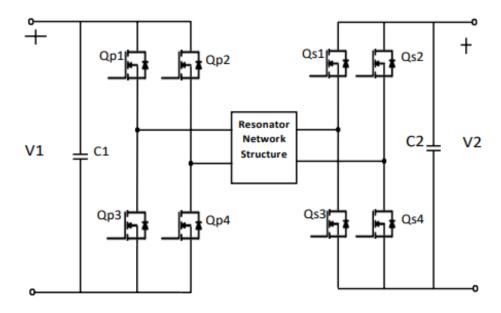

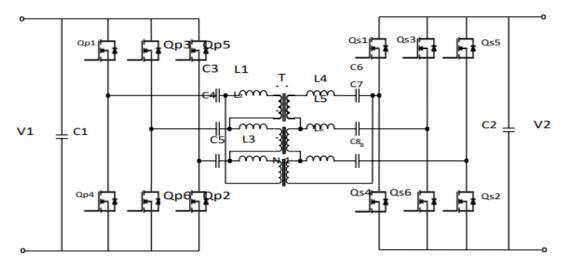

#### 1.4.1.4 Interleaved Isolated Bidirectional DC-DC Converter:

The interleaved construction can increase the voltage conversion ratio and power transmission level while sharing the voltage and current strains and reducing current ripple [6]. The resonator structure of interleaved converters is similar to the DAB resonant structure, and they are classified as Y-Y and  $\Delta - \Delta$  types of interleaved isolated converters.

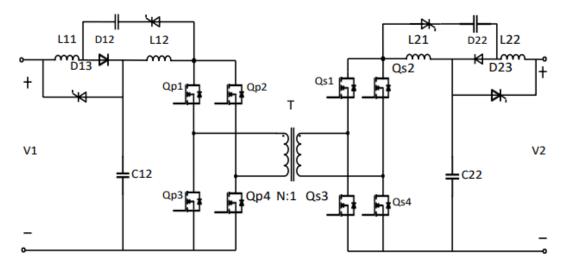

Fig.1.10 Two phase interleaved bidirectional DC-DC converter [6]

Low input and output current ripples are advantages of the two phase dual active full-bridge structure.

Fig.1.11 Three phase  $\Delta$ - $\Delta$  interleaved LLC resonant bidirectional DC-DC converter [7]

Additionally, they can lessen the turn ratio of the transformer as well as the voltage and current stresses placed on the primary and secondary side devices, respectively.

The need for current balance and the issue of a high number of devices, however, make the design more challenging. Current self-balancing and power source side current ripple might both be reduced by the Y-Y type connection topology.

The three phase interleaved LLC resonant full-bridge structure, which is appropriate for applications needing a significant voltage differential between the input and output voltages, can modify the voltage conversion ratio through phase shift and frequency modulation control schemes. Among them, the Y-Y structure is of particular interest because to its exceptional present self-balancing ability.

Fig.1.12 Three phase Y-Y interleaved LLC resonant bidirectional DC-DC converter [7]

#### 1.5 Comparison of Common Isolated Bi-directional DC-DC Converter

Table 1.3 Advantages and disadvantages of isolated bidirectional DC-DC converters

| Classification           | Advantages                                                                                                                                     | Disadvantages                                                                                          |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Basic                    | <ul> <li>Simple structure</li> <li>Easy to control</li> <li>Easy to generate new topologies</li> <li>Low number of devices</li> </ul>          | <ul><li>Large switching loss</li><li>Low conversion efficiency</li><li>Low power application</li></ul> |

| DAB                      | <ul> <li>Wide voltage conversion range</li> <li>Low stress of switches</li> <li>Flexible control method</li> <li>High power density</li> </ul> | <ul> <li>Complex structure</li> <li>Difficult to control</li> <li>Large volume and cost</li> </ul>     |

| Z Source/ Quasi-Z Source | <ul><li>High conversion efficiency</li><li>Small startup current</li></ul>                                                                     | <ul><li>Complex structure</li><li>Large number of devices</li><li>Difficulty to design</li></ul>       |

| Interleaved              | <ul><li>Wide voltage conversion range</li><li>Low current ripple</li><li>High power density</li></ul>                                          | <ul><li>Large number of switches</li><li>Complex structure</li></ul>                                   |

Typical isolated bidirectional DC-DC topologies are compared in this section from six perspectives: power source side current ripple, voltage and current stresses, power density, number of devices, and transformer winding design. Table 1.4 provides an overview of the index distribution for seven common isolated bidirectional DC-DC topologies.

Table 1.4 Indexes of typical isolated bidirectional DC-DC topologies

| Top<br>o<br>logi | Technology<br>Used | Power<br>Source<br>Side | Voltage<br>stress of<br>switches | Transformer<br>design | Current stress of switches | Number of devices |          |          | Commo<br>n<br>ground |

|------------------|--------------------|-------------------------|----------------------------------|-----------------------|----------------------------|-------------------|----------|----------|----------------------|

| es<br>Ref.       | Flyback            | Current<br>Pulsating    | $u_{high}$                       | Difficulty            | $I_{ m high}$              | 1                 | <u>T</u> | <u>C</u> | Yes                  |

| [17]             | ,                  |                         | ingii                            |                       | $\frac{1-d}{1-d}$          | _                 |          |          |                      |

| Ref.             | Resonant DAB       | Pulsating               | $u_{\text{high}}$                | Medium                | $I_{high}$                 | 3                 | 3        | 6        | No                   |

| [18]             |                    |                         | 2                                |                       |                            |                   |          |          |                      |

| Ref.             | Non-resonant       | Non                     | $u_{\text{high}}$                | Easy                  | $I_{high}$                 | 2                 | 4        | 5        | No                   |

| [19]             | DAB                | Pulsating               | 2                                |                       |                            |                   |          |          |                      |

| Ref.             | Z Source Full      | Pulsating               | $u_{high}$                       | Easy                  | $2I_{high}$                | 1                 | 3        | 4        | No                   |

| [20]             | Bridge             |                         |                                  |                       | $\overline{1-2d}$          |                   |          |          |                      |

|                  |                    |                         |                                  |                       |                            |                   |          |          |                      |

| Ref. [21] | Quasi-Z Source<br>Full Bridge | Non<br>Pulsating | $u_{high}$                  | Easy       | $\frac{2I_{high}}{1-2d}$    | 1 | 4 | 4 | Yes |

|-----------|-------------------------------|------------------|-----------------------------|------------|-----------------------------|---|---|---|-----|

| Ref. [22] | Two-Phase<br>Interleaved      | Low Ripple       | u <sub>high</sub> 2         | Medium     | I <sub>high</sub> 4         | 2 | 4 | 3 | Yes |

| Ref. [23] | Three Phase Y-Y Interleaved   | Low Ripple       | $\frac{u_{\text{high}}}{2}$ | Difficulty | $\frac{I_{\text{high}}}{3}$ | 1 | 3 | 5 | Yes |

#### 1.6 Limitations and Prospects of Bidirectional DC-DC Converters

The bidirectional DC-DC demand voltage and power will fluctuate in a wide range because the instantaneous power needed by the NEV will alter in real time with changes in driving conditions. As a result, the bidirectional DC-DC converter reduces the ripple in the current flowing from the power source while producing steady voltage under all operating situations. The topological design, correct modelling, and optimal management of the bidirectional converters for HESS are key concerns that require immediate attention[12]-[14].

An essential element that has a significant impact on the development of the NEV industry is the dependability of a bidirectional DC-DC converter for the vehicle powertrain. An important study area for bidirectional converters for HESS would be to fully integrate the studies of system detection, modelling, control strategy, and fault diagnosis techniques to accomplish the safe and dependable operation of bidirectional DC-DC conversion systems[16]-[18].

A bidirectional DC-DC converter is a highly nonlinear system. There would be several kinds of bifurcation, chaos, and other nonlinear phenomena under certain circumstances. These are reflected in the converter's increased harmonic content, increased harmonic voltage and current ripples, decreased conversion efficiency, noise, oscillations, and even system collapse. Important study areas in relation to bidirectional DC-DC converters include the method for doing nonlinear modelling of DC-DC converters, examining converter stability, and applying chaos control. Given the difficulties encountered during research on bidirectional DC-DC converters for NEV, the following works can be evaluated.

Bidirectional DC-DC converters for HESS can operate efficiently and with a high voltage conversion ratio by taking advantage of wideband gaps' high frequency and low loss characteristics. The optimization calculation approach can be utilised to enhance and optimise existing interleaved, quasi-Z source, cascaded, and other topologies for bidirectional DC-DC converters[20]. To do this, it is possible to reduce switching loss, device stress, and energy storage element volume.

The bidirectional DC-DC converter for HESS has the challenge of stable operation under all operating situations and a low power side current ripple[22]. To address this issue, the converter's dynamic response and anti-interference ability can be artificially enhanced based on existing topology optimization, such as by applying an interleaved parallel technology, in conjunction with research on accurate modelling and the adaptive control method.

In order to address the problem of nonlinear modelling and control of the bidirectional DC-DC converter for HESS, the nonlinear behaviour brought on by changes in the bidirectional DC-DC converter parameter can be revealed by qualitative and quantitative methods based on the study of nonlinear dynamics and combined synthetical modelling techniques, such as state variable equation and discrete mapping[23]. In order to apply chaos control to the converter and get the desired periodicity, this is done.

#### 1.7 THESIS OUTLINE

In this thesis, chapter 1 includes a review of bidirectional dc-dc converters (IBDC). The basic structure of these converters along with the terminology used in the literature was described. The advantages and disadvantages of each configuration were briefly stated.

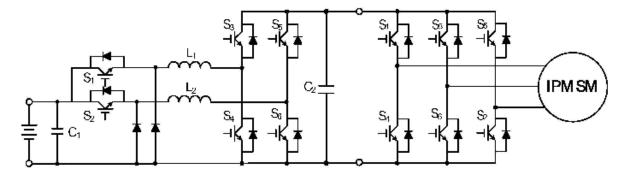

In chapter 2, the three-level converter is reviewed and comprehensively compared with CBC and interleaved bidirectional converter in terms of magnetic component size and efficiency.

Chapter 3 discusses the macro model of ultra-capacitor. Depending on the application, a simplified first order or higher order RC model is proposed. The model can be used to estimate the ultra-capacitor losses and temperature.

Chapter 4 explores the State-of-the-art interface dc-dc converter topologies, and a new three-level dc-dc converter is presented. In addition to providing design principles, the suggested topology is analysed. A control strategy is suggested together with the development of the model of the full conversion system. Controlling the ultra-capacitor current and dc bus midpoint voltage is the aim of the proposed control technique. Depending on the operating mode, the second control goal is to asymptotically regulate the dc bus voltage to the specified reference. The third control objective is to regulate the state of charge (SOC) of ultra-capacitors.

Chapter 5 concludes the contributions of the thesis and points out the scope of future work.

#### **CHAPTER 2**

# COMPARATIVE STUDY OF BIDIRECTIONAL THREE-LEVEL DC-DC CONVERTER FOR AUTOMOTIVE APPLICATIONS

#### 2.1 Three-Level Interface DC-DC Converter:

In applications requiring a high input voltage and high switching frequency, three-level converters are a popular choice. One-half of the total dc bus voltage is used to stress the switches[29].

This enables us to employ switches with lower voltage ratings that perform better in terms of switching and conduction than switches rated for the full dc bus voltage. Therefore, compared to two-level converters, the converter's overall performance, including cost and efficiency, can be noticeably improved, especially when switching frequency is above 20 kHz or MOSFETs are utilized as switches.

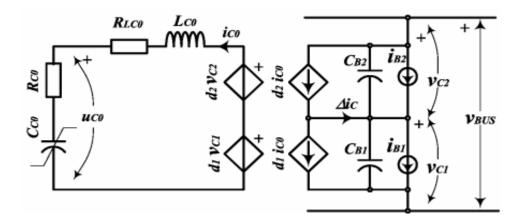

The input filter capacitors work as a capacitive voltage divider to divide the dc bus voltage  $V_{BUS}$  into two equal voltages,  $V_{C1}$  and  $V_{C2}$ . They are connected in series. The switching cell midpoint is connected to the midpoint of the capacitor.

#### 2.1.1. Working Principle:

Switching function  $S_1$  and the complimentary function determine the states of the switches  $SW_{1A}$  and  $SW_{1B}$ , whereas switching function  $S_2$  and the complementary function determine the states of the switches  $SW_{2A}$  and  $SW_{2B}$ . The  $S_1$  and  $S_2$  switching operations are produced by the  $PWM_1$  and  $PWM_2$  pulse width modulators. The  $S_1$  and  $S_2$  switching operations are

Fig. 2.1. Circuit diagram for a three-level bidirectional dc-dc converter interface [24].

$$S_{1}(t) = \begin{cases} 1, KT_{SW} < t \le T_{SW} \left( K + 1 - \frac{d_{1}}{2} \right) & AND \ T_{SW} \left( K + 1 - \frac{d_{1}}{2} \right) < t \le (K+1)T_{SW} \\ 0, T_{SW} \left( K + \frac{d_{1}}{2} \right) < t \le T_{SW} \left( K + 1 - \frac{d_{1}}{2} \right) \end{cases}$$

(2.1)

$$S_{2}(t) = \begin{cases} 1, KT_{SW} < t - \frac{T_{SW}}{2} \le T_{SW} \left( K + \frac{d_{2}}{2} \right) AND \ T_{SW} \left( K + 1 - \frac{d_{2}}{2} \right) < t - \frac{T_{SW}}{2} \le (K+1)T_{SW} \\ 0, T_{SW} \left( K + \frac{d_{2}}{2} \right) < t - \frac{T_{SW}}{2} \le T_{SW} \left( K + 1 - \frac{d_{1}}{2} \right) \end{cases}$$

$$(2.2)$$

where  $T_{SW}$  is the switching period and k is an integer between 0 and 1. The signals of modulation Duty cycles  $d_1$  and  $d_2$  are produced by the control circuit. The control circuit balances the voltages  $V_{C1}$  and  $V_{C2}$  and regulates the ultra-capacitor current  $i_{C0}$ . They are the modulation carriers. Triangle signals  $V_{T1}$  and  $V_{T2}$  running at the same frequency  $f_{SW}$  but with a shift of radians. When  $d_1 = d_2 < 1/2$ , the converter waveforms are shown in Fig. 2.3 (a), while Fig (b) when  $d_1 = d_2 > 1/2$ , displays the waveforms. The switches' states determine four different there are four topological stages that can be identified: A, B, C, and D. Diagrams of equivalent circuits Fig. 2.2 provides an illustration of these steps (c). Idealized models of the input filter capacitors are used.  $V_{C1}$  and  $V_{C2}$  are voltage sources.

Fig.2.2. equivalent circuits for steps A, B, C, and D [24].

Stage A): The converter can only be at this stage if the duty cycle is less than 1/2.  $SW_{1B}$  and  $SW_{2A}$  switches are closed, whereas  $SW_{1B}$  and  $SW_{2B}$  switches are open. Because the current  $i_{C0}$  is believed to be positive in the circuit design, the currents  $i_{1B}$  and  $i_{2A}$  is negative. The freewheeling diodes  $D_{1B}$  and  $D_{2A}$  are conducting. Input voltage is Since  $V_{OUT} = 0$ , the current  $i_{C0}$  declines.

$$\frac{di_{c0}}{dt} = \left(-\frac{u_{c0}}{L_{c0}}\right) < 0 \tag{2.3}$$

Stage B): The switches  $SW_{1A}$  and  $SW_{2A}$  are closed, whereas the switches  $SW_{1B}$  and  $SW_{2B}$  are open. The freewheeling diode  $D_{2A}$  is conducting, and the currents  $i_{1A}$  and  $i_{2A}$  are both positive. The current  $i_{1A}$  discharges the filter capacitor  $C_{B1}$ . The voltage at the output is  $V_{OUT} = V_{C1}$ . There is a change in the current  $i_{C0}$  depending on the voltage of the ultra-capacitors (duty cycle consequently).

$$\frac{di_{c0}}{dt} = \frac{1}{L_{c0}} (V_{c1} - u_{c0}) \begin{cases} > 0, u_{c0} < V_{c1} \\ < 0, u_{c0} > V_{c1} \end{cases}$$

(2.4)

In stage C), the switches  $SW_{1A}$  and  $SW_{1B}$  are open while  $SW_{1B}$  and  $SW_{2B}$  are both closed. The freewheeling diode  $D_{1B}$  is conducting, and the currents  $i_{2B}$  and  $i_{1B}$  are both positive. The current  $i_{2B}$  discharges the filter capacitor  $C_{B2}$ . The voltage at the output is  $V_{OUT} = V_{C2}$ . The duty cycle determines whether the current  $i_{C0}$  grows or drops.

$$\frac{di_{c0}}{dt} = \frac{1}{L_{c0}} (V_{c2} - u_{c0}) \begin{cases} > 0, u_{c0} < V_{c2} \\ < 0, u_{c0} > V_{c2} \end{cases}$$

(2.5)

Figure 2.3 (a) and (b) shows the several topological stages of the three-level dc-dc converter. Ideal waveforms for d < 1/2 and d > 1/2, respectively [24]

Stage D): Only if the duty cycles are more than 1/2 can the converter be at this stage. When compared to the switches  $SW_{1B}$  and  $SW_{2A}$ ,  $SW_{1A}$  and  $SW_{2B}$  are closed. Positive currents flow through the switches,  $i_{1A}$  and  $i_{2B}$ . Because the output voltage is  $V_{OUT} = V_{BUS}$ , the current  $i_{CO}$  rises.

$$\frac{di_{c0}}{dt} = \frac{1}{L_{c0}} (V_{BUS} - u_{c0}) > 0 {(2.6)}$$

The expression for instantaneous output voltage  $V_{OUT}$  is :

$$V_{OUT}(t) = V_{BUS}S_1(t) + V_{C1}(S_1(t) - S_2(t))$$

(2.7)

where the switching functions are  $S_1(t)$  and  $S_2(t)$  (2.1) and (2.2).

Assuming that  $d_1 = d_2 = d$  and  $V_{C1} = V_{C2} = V_{BUS}/2$  (as in a well-designed and controlled converter), it follows from (4.9)-(4.14)

$$V_{OUT}\left(t + \frac{T_{SW}}{2}\right) = V_{OUT}(t) \tag{2.8}$$

$$u_{C0} = \frac{1}{T_{SW}} \int_0^{T_{SW}} V_{OUT}(t) dt = V_{BUS} d$$

(2.9)

The output voltage is a periodic function with a period of  $T_{SW}/2$ , as shown by (2.8) and (2.9). As a result, the output current iC0 and its effective fundamental frequency,  $f_{SW-E}=2f_{SW}$ , are twice that of the switching frequency.

# **2.2** Comparison of Three-Level Converter with the state-of-the-art Converters:

In comparison to the most advanced two-level bidirectional dc-dc converter and interleaved bidirectional buck/boost converters, three level dc-dc converter offers a number of benefits. The voltage put across the switch plays a significant role in switching losses. In particular, when the switches are exposed to half the output voltage compared to CBC, the switching loss of the parasitic capacitance can be greatly decreased even without soft switching.

As low-voltage switches are employed, parasitic capacitance losses are anticipated to be even lower. Due to the fact that the reverse voltage is only half as high as the output voltage and low-voltage diodes often recover more quickly, the diode reverse recovery losses are smaller for passive components. This section compares the topologies of bidirectional buck/boost dc-dc converters shown in terms of the size and efficiency of magnetic components over the entire drive cycle range, taking into account the dynamic variations of the battery and UC voltages as well as the power processed by the converter.

#### 2.2.1. Drive Cycle Characteristic:

The load power and dynamic voltage changes of the energy sources have a significant impact on the efficiency of the bidirectional converter.

In this theis, we discuss the three-level wavelet decomposition battery and UC reference power results [27]. Fig. 2.4 displays the converter power and battery voltage fluctuations for four successive UDDS cycles. In this particular instance, it is assumed that the battery has an initial state of charge (SOC) of 80% and that the UC has a SOC of 91.6%. During the driving cycle, the converter power fluctuates between 10.78 and 45.32 kW, the battery voltage varies between 381 and 357 V, the UC voltage varies between 575 and 384 V, and the battery voltage varies between 381 and 357 V.

Fig.2.4. Dynamic variations of state variables [27](a) Converter power.(b) UC voltage. (c) Battery voltage.

#### 2.2.2. Magnetic Component Size:

Peak flux density and peak current flowing through the core are both correlated with the size of the magnetic component. The battery's current ripple can be represented in CBC as

$$\Delta i_{batt-boost}(d) = \frac{v_0}{Lf_s} d(1-d)$$

(2.10)

The battery current ripple for TLC is

$$\Delta i_{batt-TL}(d) = \frac{v_0}{2Lf_s} d_{eff} (1 - d_{eff})$$

(2.11)

Two inductor currents are added to create the BIC converter's input current. The input current ripple increases when the switches' duty cycles are lower than 50% the current ripple as

$$\Delta i_{batt-Interleaved} (d) = \frac{2v_{in}-v_0}{Lf_s} (1 - \frac{v_{in}}{v_0})$$

(2.12)

The core geometry approach is used to determine the approximate size of the magnetic component. Many factors, including peak current ( $I_{peak}$ ), rms current ( $I_{rms}$ ), maximum flux density ( $B_{max}$ ), regulation ( $\alpha$ ), maximum output power ( $P_{omax}$ ), necessary inductance ( $I_{max}$ ), and window utilisation factor ( $I_{max}$ ), should be evaluated in order to estimate the core size.

Table 2.1: Converter Currents During Four UDDs ( $F_S = 20 \text{ kHz}$ ) [26]

|                        | CBC(200μH) | TLC(100µH) | BIC(200μH) |

|------------------------|------------|------------|------------|

| Max bat. Current[A]    | 138.64     | 130        | 123.2      |

| Ripple current[A]      | 30.86      | 4.28       | 15.43      |

| Max. Inductor cur[A]   | 138.64     | 130        | 77.03      |

| Ind. Ripple cur[A]     | 30.86      | 4.28       | 30.86      |

| Max bat. Ripple cur[A] | 32.94      | 11.5       | 15.8       |

| Max ind. Ripple cur[A] | 32.94      | 11.5       | 31.6       |

| Max ind. RMS cur[A]    | 126.89     | 126.86     | 63.49      |

The necessary inductance and peak inductor current must be calculated in order to estimate the magnetic core size. In this regard, the drive cycle has been assessed using an intermediate buck/boost converter with a switching frequency of 20 kHz, where the effective frequency of the input current ripple is 40 kHz in BIC and TLC. The maximum discharge rate limits the battery current ripple to 20% of the discharging current, which translates to a 40% inductor current ripple for BIC. The inductances for CBC, BIC, and TLC are computed as  $400\mu$ H,  $200\mu$ H(×2), and  $100\mu$ H, respectively, based on the expected ripple current, switching frequency, and operational maximum voltage across the inductor with corresponding duty cycle.

### 2.2.3. Semiconductor Selection Guidelines:

The voltage and current stress on the switches should be examined before choosing any power switches. The switches in CBC and BIC are exposed to the output voltage, but the switches in TLC are exposed to half the output voltage.

**TABLE 2.2: Analyzed Converter Specifications [26]**

|                         | CBC       | TLC      | BIC       |

|-------------------------|-----------|----------|-----------|

|                         |           |          |           |

|                         | 357-381   | 357-381  | 357-381   |

| Input voltage[V]        |           |          |           |

| Output voltage[V]       | 384-575   | 384-575  | 384-575   |

| Peak prop. Power[KW]    | 45.32     | 45.32    | 45.32     |

| Power switch            | 1XFB30    | 1XFX80   | 1XFB30    |

|                         | N120P     | N60P3    | N120P     |

| Switch rating           | 1200V/30A | 600V/80A | 1200V/30A |

| No. of switches         | 12        | 8        | 12        |