# B.E. ELECTRONICS AND TELE-COMMUNICATION ENGINEERING 2<sup>ND</sup> YEAR 1<sup>ST</sup> SEMESTER EXAM, 2019

ANALOG CIRCUITS- I

Time: Three hours

Full Marks: 100

+20 V

Use a separate Answer-Script for each Part

#### PART-I (50 MARKS)

Answer **0.1**, any **one** from **2** and **3** and any **one** from **4** and **5**

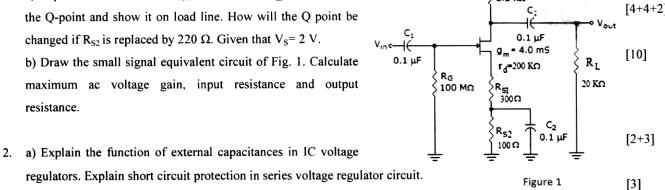

1. a) Explain the function of  $R_{G_1}R_{S_1}$  and  $R_{S_2}$  in Fig. 1. Determine the Q-point and show it on load line. How will the Q point be

- regulators. Explain short circuit protection in series voltage regulator circuit.

- b) Why negative feedback is important in wide range of OP-AMP applications.

- c) Define input offset voltage and slew rate and explain their origin.

- d) For a step input the output of op-amp appears after 1 µs. calculate its slew rate. Vin=

[5]

- 3. a) Design a voltage regulator using LM317 to obtain regulated voltage of 10 V. [5+5]

- b) Explain difference mode and common mode operation of differential amplifier using BJT. Find the expression for voltage gain, input resistance and output resistance for both cases.

- 4. a) Explain the effect of noise in comparator circuits.

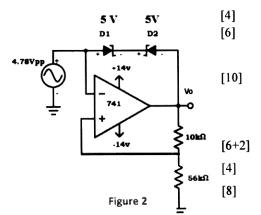

- b) Calculate output voltage in Fig. 2.

- c) Explain the temperature measurement using instrumentation amplifier

- 5. a) Explain the function of all pass filter with circuit diagram and mention its use.

- b) Design a all pass filter to obtain a phase shift of 90°

- c) Draw and explain frequency response of practical integrator circuit.

Ref. No.: Ex/ET/T/215/2019

## **PART-II**

#### **Section A: Answer any TWO**

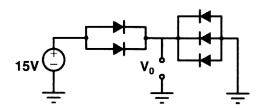

1. **Explain** the working principle of a Full Wave Voltage Multiplier with proper circuit diagram. **Plot** the initial voltage across both the capacitors and the overall output voltage for a sinusoidal input (assume ideal diode and capacitors are uncharged initially).

[Marks: 4+6=10]

2. A full wave transformer coupled rectifier with  $R_L = 20k\Omega$  is implemented using ideal diodes. Find the value of  $\mathbf{V}_{dc}$ ,  $\mathbf{V}_{rms}$  and  $\mathbf{V}_{rrms}$  (ripple rms). **Design** one capacitive filter (find the value of the capacitor) to reduce the peak to peak ripple voltage across load within 1% of DC output.

[Marks: 6+4=10]

3. Find the output voltage **V**<sub>0</sub> of the diode circuit shown in Figure 1 and **plot** the output voltage for a temperature range 0 to 100°C. [All diodes are real and identical]

[Marks: 6+4=10]

# **Section B: Compulsory**

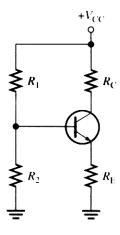

4. **Determine** the expression of stability factor **S(Ico)** for a BJT in Emitter Bias configuration. **Calculate** the value of **S(Ico)** of the voltage divider circuit shown in Figure 2. [ $\beta$ = 100,  $R_1$  = 60 $k\Omega$ ,  $R_2$  = 30 $k\Omega$ ,  $R_E$  = 3 $k\Omega$ ,  $R_C$  = 1 $k\Omega$ , and  $V_{CC}$  = 12V] [Marks: 5+5=10]

Ref. No.: Ex/ET/T/215/2019

## **Section C: Answer any TWO**

- 5. **Explain** the working principle of a current mirror circuit. **Design** one current mirror with  $1\mu A$  current in primary branch and  $2\mu A$  and  $2.5\mu A$  in two different secondary branches. (Available transistors are identical with  $\beta$ =1000 and  $V_{BE}$  =0.7V. Supply voltage 3V) [Marks: 4+6=10]

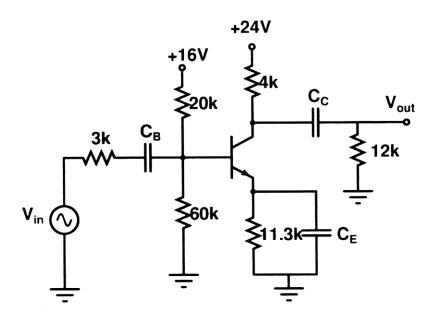

- 6. A CE amplifier with proper biasing arrangement is shown in Figure 3. [ $\beta$ = 100,  $C_E$  =  $C_C$  =  $C_B$  = 1  $\mu$ F and neglect  $r_o$ ]

- A) Draw the small signal model of the entire amplifier and calculate the midband gain.

- B) **Find** all the low frequency poles, zeros and lower cut-off frequency due to coupling capacitors.

- C) **Plot** the gain response with respect to frequency for very low to mid frequency range.

[Marks: 5+3+2-1]

[Marks: 5+3+2=10]

7. Using the high frequency model of BJT find the expression of  $\beta(s)$ ,  $\omega_{\beta}$  and  $\omega_{T}$ .

Calculate the value of  $\omega_{\beta}$  and  $\omega_{T}$  for the BJT shown in figure 3. [use  $\beta$ = 100,  $C_{\pi}$  = 12pF,  $C_{C}$  = 2pF]

[Marks: 6+4=10]