## SUBTHRESHOLD ANALYSIS OF NEGATIVE CAPACITANCE FIELD EFFECT TRANSISTORS FOR DIFFERENT FERROELECTRIC MATERIALS

Thesis Submitted to the Department of Electronics and Telecommunication Engineering in partial fulfilment of the requirements for the degree of

#### MASTER OF ENGINEERING ELECTRONICS AND TELE-COMMUNICATION ENGINEERING

Submitted By **NEHA KAPOOR**

Exam Roll No: **M4ETC19012** Registration No: **140696** of **2017-2018**

Under the Guidance of **Dr. Chandrima Mondal**

Department of Electronics and Telecommunication Engineering Faculty Council of Engineering and Technology

JADAVPURUNIVERSITY KOLKATA- 700032 May, 2019

#### **Department of Electronics and Telecommunication Engineering**

#### JADAVPUR UNIVERSITY KOLKATA- 700032

#### Certificate of Recommendation

This is to certify that Neha Kapoor (Exam Roll No M4ETC19012, Registration No 140696 of 2017-2018) has satisfactorily completed the thesis entitled "SUBTHRESHOLD ANALYSIS OF NEGATIVE CAPACITANCE FIELD EFFECT TRANSISTORS FOR DIFFERENT FERROELECTRIC MATERIALS", under the guidance of Dr. Chandrima Mondal, Department of Electronics and Telecommunication Engineering, Jadavpur University. We recommend that her dissertation is fully adequate in scope and quality for the partial fulfilment of the requirement for the degree of MASTER OF ENGINEERING ELECTRONICS AND TELE-COMMUNICATION ENGINEERING in the Department of Electronics and Telecommunication Engineering, Jadavpur University, Kolkata-700032.

Dr. Chandrima Mondal

Project Supervisor

Assistant Professor, Department of Electronics

and Telecommunication Engineering,

Jadavpur University, Kolkata – 700032

Prof. Sheli Sinha Chaudhuri

Head of the Department, Department of Electronics and Telecommunication Engineering, Jadavpur University, Kolkata-700032 Prof. Chiranjib Bhattacharjee

Dean, Faculty Council of Engineering and Technology, Jadavpur University, Kolkata-700032

#### **Faculty Council of Engineering and Technology**

#### JADAVPUR UNIVERSITY KOLKATA- 700032

#### Certificate of Approval \*

The foregoing thesis titled "SUBTHRESHOLD **ANALYSIS OF NEGATIVE TRANSISTORS CAPACITANCE FIELD EFFECT** DIFFERENT **FOR** FERROELECTRIC MATERIALS" is hereby approved as a creditable study of MASTER OF ENGINEERING ELECTRONICS AND TELE-COMMUNICATION ENGINEERING in Department of Electronics and Telecommunication Engineering and presented in a manner satisfactory to warrant its acceptance as a prerequisite to the degree for which it has been submitted. It is understood that by this approval the undersigned do not necessarily endorse or approve any statement made, opinion expressed or conclusion therein but approve this thesis only for the purpose for which it is submitted.

| Final Examination for Evaluation of the Thesis |

|------------------------------------------------|

|                                                |

| <br>Signature of Examiners                     |

<sup>\*</sup> Only in case the thesis is approved

#### **Declaration of Originality and Compliance of Academic Ethics**

I hereby declare that this thesis contains literature survey and original research work by myself as a part of my MASTER OF ENGINEERING ELECTRONICS AND TELE-COMMUNICATION ENGINEERING in Department of Electronics and Telecommunication Engineering.

All information in this document has been obtained and presented in accordance with academic rules and ethical conduct.

I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name (Block Letters): **NEHA KAPOOR** Exam Roll Number: **M4ETC19012**

Thesis Title: SUB-THRESHOLD ANALYSIS OF NEGATIVE CAPACITANCE FIELD EFFECT

TRANSISTORS FOR DIFFERENT FERROELECTRIC MATERIALS

Signature with Date:

## ACKNOWLEDGEMENT

It is a pleasant task to express my gratitude to all those who have accompanied and helped me in my project work.

First and foremost, I really take this opportunity to express my deep sense of gratitude to my guide, **Dr. Chandrima Mondal**, Department of Electronics and Telecommunication Engineering, Jadavpur University, Kolkata, for her invaluable guidance, suggestions and encouragement throughout the project, which helped me a lot to improve this project work. It has been very nice to be under her guidance. Her appreciation during the good times has been boosting my morals and confidence.

I am also indebted to *Prof. Sheli Sinha Chaudhuri*, the Head, Department of Electronics and Telecommunication Engineering, Jadavpur University, for her kind help during this project work.

My heart-felt thanks also goes to all my family members for their love and encouragement, without which, the work would not have been possible.

Last, but not the least, I would like to thank my batch-mates who have directly or indirectly helped me in this work.

## **ABSTRACT**

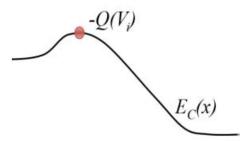

MOSFET current voltage characteristics is dependent on the potential barrier present between source and the channel. This barrier is controlled by the voltage applied at the gate. The number of carriers (governed by the Boltzmann statistics) that cross the barrier specifies that to rise the I by a decade, 60 mV of rise in voltage is minimum requirement. This has put an important block in downscaling of voltage. Hence, we are not able to optimize the power requirement.

S. Salahuddin and S. Dutta of *Purdue University* came out with the concept of adding a ferroelectric material in MOSFET. The material shall be added at the gate stack and this will help in amplification of the voltage applied at the gate. This allows us to operate at lower voltage and hence less power consumption as well. Moreover, the subthreshold swing is also found to improve.

In this thesis, a simple mathematical model-based study of NCFET devices has been made. Study is carried out to know how the device react to the changes in the ferroelectric material. At first, a compact mathematical model-based method to study device features is taken. In the results we will see that the developed model of NCFET, the subthreshold swing of such devices improves. Further properties like drain induced barrier rising are observed to improve as well.

Using the compact model developed, the NCFET has been analysed for two different ferroelectric materials and with its varying thickness.

Scaling has been performed to see the performance of NC devices in future technologies. This analysis demonstrations that NC devices are more advantageous in overpowering short channel effects like DIBL and thus helps in scaling down of devices.

## **CONTENTS**

| CERTIFICATE OF RECOMMENDATION                          | i     |

|--------------------------------------------------------|-------|

| CERTIFICATE OF APPROVAL                                | ii    |

| DECLARATION                                            | iii   |

| ACKNOWLEDGEMENT                                        | iv    |

| ABSTRACT                                               | V     |

| CHAPTER 1                                              |       |

| INTRODUCTION                                           |       |

| 1.1 MOSFET                                             | 1     |

| 1.2 THE HAPPY DAYS OF SCALING                          | 1     |

| 1.3 MOTIVATION FOR NCFET                               | 1-2   |

| 1.4 NEGATIVE CAPACITANCE IN MOSFET                     | 3-5   |

| 1.5 SCOPE OF WORK                                      | 5-6   |

| CHAPTER 2                                              |       |

| LITERATURE SURVEY                                      |       |

| 2.1 DEVELOPMENT AND PROSPECTS OF NCFETS                | 7-9   |

| 2.2 EXPERIMENTAL EVIDENCE OF NCFETS                    | 9-10  |

| 2.3 MODELING NCFETS                                    | 10-11 |

| 2.4 GETTING SS LOWER THAN 60                           | 11    |

| 2.5 LOW POWER NCFETS FOR QW BODY TECHNOLOGY            | 11-12 |

| 2.6 A COMPACT SUB-THRESHOLD MODEL FOR SHORT-CHANNEL    |       |

| MONOLAYER TRANSITION METAL DICHALCOGENIDE FIELD-EFFECT | -     |

| TRANSISTORS                                            | 12-13 |

| CHAPTER 3                                              |       |

| DEVICE STRUCTURE AND MODEL                             | 14-19 |

| CHAPTER 4                                              |       |

| RESULTS AND DISCUSSION                                 | 20-40 |

| CHAPTER 5                                              |       |

| CONCLUSION AND FUTURE WORK                             | 41    |

| REFERENCES                                             | 42-44 |

## CHAPTER 1

## **INTRODUCTION**

Before introducing negative capacitance Field Effect Transistor (NCFET), let us known a little about conventional Metal Oxide Semiconductor Field effect transistor, MOSFET and its limitation.

### **1.1. MOSFET**

In 1926, a patent was filed by Julius Edgar Lilienfeld[1], "Method and Apparatus for Controlling Electric Currents," in which he anticipated a 3-electrode assemblyby means of copper-sulphide semiconductor material. Now this is well known as field-effect transistor, and also later he proposed the idea of the depletion-mode MOSFET [2]. The idea of the inversion-mode MOSFET was proposed, seven years later, by Reil [3]. In 1960 first MOSFET was fabricated by Kahng and Atalla [4]. We observe that there was a huge time gap between the emergence of the idea and the fabrication. This was due to the absence of a stable oxide and the lack of information on semiconductors. For example, the idea of a "hole," developed by Wilson in 1931 [5], was used in 1941 by Ohl [6]. Brattain [8] developed a good field effect device and first talked about transistor effect. Shockley defined in [9] discovery of transistor. They used Silicon instead of Ge. The reason for this was that Atalla had shown that a high-quality Si/SiO<sub>2</sub> interface could be obtained using his oxidation process. This high-quality Si/SiO<sub>2</sub> interface was extremely important, since it constitutes the heart of the MOSFET. In contrast, the oxide of germanium is soluble in water and its interface with germanium often contains plenty of defects. Due to the availability of stable oxide, Silicon became the leading semiconductor.

### **1.2.** THE HAPPY DAYS OF SCALING (1960–2000)

In 1965, it was observed by Moore that the number of transistors increases by two times in every two year. This empirical law has indeed been the driving force behind the semiconductor industry for many decades. Throughout this period, the architecture and working principle of the MOSFET have essentially not been changed. The continuous scaling of its physical dimensions has delivered improved performance and lower cost at every single technology generation.

Until 2000, this evolution has driven the growing computing power of the PC and ever-increasing functionalities (more data storage, performing games, internet access, etc.).

### 1.3. MOTIVATION FOR NCFET

FETs at Room Temperature require the potential at the g to change by minimum of 60 mV to get the current at the drain to increase by ten times. This minimum sub-threshold slope forces anessential lower boundary on the allowable voltage and also on the dissipation in the switching action using FET.

Due to the difficulty in removing this heat dissipated in the switching process, the scaling down of FET will be limited [15-18]. Thus, to enjoy the advantages of scaling, it is needed to come up with new ideas on the ways to reduce power dissipation.

As the power dissipation is proportional to the square of voltage, hence reduction in the voltage helps in reduction in the power dissipation. A limit to the operating voltage is posed by the sub-threshold swing S, which is given by the reverse of the change of current that we can get for a unit change in gate voltage, Vg:

$$S = \frac{\partial Vg}{\partial (\log_{10} I)} = \frac{\partial Vg}{\partial \psi s} \frac{\partial \psi s}{\partial (\log_{10} I)} \dots (1)$$

The variation in drain current to the variation in the surface potential  $\psi_s$  in the channel can be a minimum of 60mV at room temperature. In FET, gate voltage Vg and surface potential  $\psi$ scan be related by a capacitive voltage divider, thus the 1<sup>st</sup> term in eq(1) can be given as

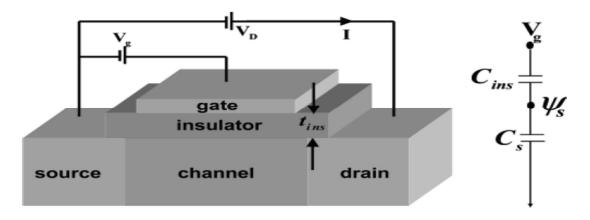

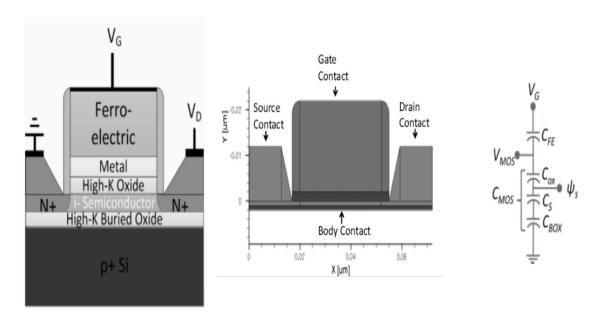

Figure 1: a simple n channel MOSFET and its capacitive model

$$\frac{\partial Vg}{\partial \psi s} = 1 + \frac{Cs}{Cins} \dots (2)$$

This is called body factor(m).

From the equation it is clear that m should begreater than one. This puts a limit of 60mV/decade(m=1 condition) on the S given in (1). This is true even for high k(dielectric constant) materials [19]. Even large values of  $C_{ins}$  can only be used to make the body factor 1 but not lower than that.

#### 1.4. <u>NEGATIVE CAPACITANCE IN MOSFET</u>

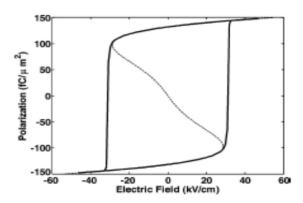

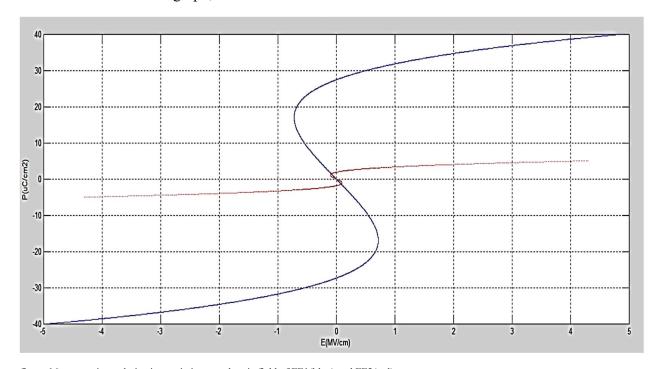

It has been studied that if we add a ferroelectric material in the gate stack of FET, we can obtain an amplification. Thus,  $\frac{\partial Vg}{\partial \psi s} < 1$  can be obtained and value of subthreshold swing lower than 60 mV/decade can be obtained. This unique feature is obtained due to the unique P vs E characteristics of FE, that shows a negative slope at the origin.

Figure 2: polarization vs electric field of any ferroelectric material

This FET is termed as Negative Capacitance FET. Due to the ability of internal voltage gain (Av) and getting a steep slope, it has gained substantial interest for ultra-low power applications. Very thin body structure is suggested for getting more internal amplification and steeper slope in the subthreshold region. 2D semiconductor TMD (transition-metal-dichalcogenides) is a suitable channel material. This is due to their atomically thin thickness, untouched surface, and acceptable bandgap. Thus, TMD materials like MoS<sub>2</sub> is a suitable channel material for NCFET.Sub-2.3 kT/q swing in a TMD NCFET has recently been experimentally demonstrated.

Experiments exhibiting hysteresis jumps in polarization are not stable at the negative capacitance region of the FE material. This unstable capacitance can be stabilized by introduction of a series positive capacitance. This further helps ingetting the channel potential  $\Psi$ s to change more than the voltage Vg applied at the gate terminal. It thus provides a voltage amplifier or to be specific a step-up voltage transformer. The concept of negative capacitance arises from the positive feedback. This is shown in FE material. Similar features can be obtained also through other microscopic mechanism.

Positive feedback can be used to explain NCFET [20]as follows. Let us assume, we have a (positive) capacitor  $C_0$  (per unit area) with a terminal voltage equal to the applied voltage V plus a feedback voltage  $\alpha_f$ Qthat is proportional to charge Q (per unit area) on the capacitor,

This yields Q=CinsV where

$$Cins = \frac{co}{1 - \alpha f}.$$

(4)

Certainly, with  $\alpha_f$  Co >1 we have a negative capacitance that in general is unstablethus leading toincrease in charge tillcontrolled by the non-linear terms that had been avoided so far. If we stabilize the negative capacitor by putting an ordinary capacitor Cs (semiconductor capacitor) in series such that the overall capacitance  $[C_s^{-1} + C_{ins}^{-1}]^{-1}$  is positive, then it follows from equations that the body factor canbe made small showing that the NC can be applied as a step-up voltage transformer. This transformer canamplify the applied potential Vg to channel/ surface potential of  $\Psi s$ . As long as,  $Ceq^{-1} = Cs^{-1} + Cins^{-1}$  remains positive, the composite ferroelectric- semiconductor system will behave like a normal positive capacitor and Ceq (equivalent capacitance) will be larger than both Cs and Cins(insulator capacitance). Thus, the dissipated energy in switching event for the equivalent capacitor will be much less than the individual capacitors.

Thus the linear capacitor can be replaced by capacitor  $Q=C_0(V + \alpha_f Q)$  with a nonlinear capacitance function  $Q=F(V + \alpha_f Q)$ , so that

$$V = F^{-1}(Q) - \alpha_f Q$$

.....(5)

The function  $F^{-1}$  is odd, expanding it to the fifth power to write

$$V = \alpha_0 Q + \beta_0 Q^3 + \gamma_0 Q^5 + \rho_0 \frac{dQ}{dt}....(6)$$

The first term being the inverse linear capacitance 1/Co.

A resistive drop is added which is proportional to the  $\frac{dQ}{dt}$ . Further the parameter  $\alpha_0$  equals  $(1/C_0)$  -  $\alpha_f$  and is negative provided we are operating in the negative capacitance region where  $\alpha_f C_0 > 1$ .

We illustrated the positive feedback approach of the NCFET. But same equations can also be derived from the dynamics of ferroelectric capacitors given by the Landau- Khalatnikov(LK) equations[21-23]

$$\rho \frac{dP}{dt} + \nabla_p U = 0.$$

(7)

Where,

$$U = \alpha P^2 + \beta P^3 + \gamma Q P^5 - E_{ext} P.$$

(8)

U is the Gibb's free energy which is given by the addition of the anisotropy energy and the external field energy  $E_{\text{ext}}$ , and the polarization charge per unit area is represented by P. From equations

$$E_{ext} = 2\alpha P + 4\beta P^3 + 6\gamma P^5 + \rho \frac{dP}{dt}$$

...(9)

If Q=P and V= $E_{ext}$ \* $T_{ins}$  where  $T_{ins}$  is the thickness of the insulator, we get  $\alpha_0$ = $2\alpha T_{ins}$  and  $\beta_0$ = $4\beta T_{ins}$  and  $\gamma_0$ = $6\gamma T_{ins}$  and  $p_0$ = $pT_{ins}$  in our equations.

Now replacing the insulator with a FE one. The gate circuit can now be represented as a series combination of the FE capacitor and semiconductor capacitor Cs, channel-to-source and channel-to-drain capacitors. A voltage  $\Psi s$  (surface potential) appears across semiconductor capacitor, while Vg -  $\Psi s$  appears across the FE capacitor. As both capacitors are in series so they have same charge. Thus, we can write

$$\psi_{\mathcal{S}} = \frac{\varrho}{c_{\mathcal{S}}}....(10)$$

$$Vg - \psi_s \approx \alpha_0 Q + \beta_0 Q^3 + \gamma_0 Q^5 + \rho_0 \frac{dQ}{dt}$$

....(11)

Thus, we get

$$\tau \frac{d\psi_s}{dt} + (1 + a_1)\psi_s + a_2\psi_s^3 + a_3\psi_s^5 = V_g....(12)$$

Where

$$\tau = \rho C_s t_{ins}, \quad a_1 = 2\alpha C_s t_{ins}, \qquad a_2 = 4\beta C_s^3 t_{ins}, \qquad a_3 = 6\gamma C_s^5 t_{ins}$$

By setting  $d\Psi s/dt = 0$  we can obtain the steady state  $\Psi s$  versus Vg. This relation depends on the material. If a 1 is more than both a 2 and a 3 than  $\Psi s$  and Vg is essentially linear.

$$\frac{\partial V_g}{\partial \psi_s} \approx 1 + a_1....(13)$$

This mimics the earlier obtained results. Even, when a2 and a3 are significant, (1 + a1) represents the slope close to the origin  $\Psi s = 0$ , Vg = 0. This slope must be greater than 0 if origin is to be made a stable operating point. Thus, it puts a limit to the thickness of the insulator.

$$t_{ins} \le \frac{1}{2\alpha C_s} \equiv t_c...$$

(14)

Tc is the critical thickness.

### 1.5. SCOPE OF WORK

In this thesis, a simple mathematical model-based study of NCFET devices has been made. Study is carried out to know how the device react to the changes in the ferroelectric material. At first, a compact mathematical model-based method to study device features is taken. In the results we will see that the developed model of NCFET, the subthreshold swing of such devices improves. Further properties like drain induced barrier rising are observed to improve as well.

Using the compact model developed, the NCFET has been analysed for two different ferroelectric materials and with its varying thickness.

Scaling has been performed to see the performance of NC devices in future technologies. This analysis demonstrations that NC devices are more advantageous in overpowering short channel effects like DIBL and thus helps in scaling down of devices.

Next in chapter 2 literature survey is presented. In Chapter 3 the device structure and the model has been described. Chapter 4 involves the results and discussion of the simulation done in MATLAB for the described model. In Chapter 5, Conclusion and future work is presented. Finally, references are provided.

## CHAPTER 2

## LITERATURE SURVEY

In this chapter, the latest findings of negative capacitance FETs is presented. We begin with a review of development of the idea of the NCFETs, and their future prospects in a theoretical perspective. Then we look at various experimental realizations of negative capacitance MOSFETs. Finally, we discuss the latest developments made in modeling of NCFETs.

#### 2.1. DEVELOPMENT AND PROSPECTS OF NCFETS

Datta and Salahuddin [24] proposed the idea of negative capacitance MOSFETs to achieve SS < 60 mV/dec, wherein a ferroelectric insulator is used as gate oxide and provides step up voltage transformation.

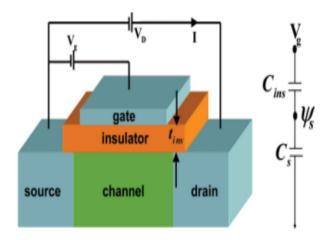

figure 3: a cross section area of a metal oxide semiconductor field effect transistor (MOSFET)

Further they argued that for the system to stable in its totality the capacitance of the system should be positive. This poses a fundamental limit on the maximum thickness of the ferroelectric for hysteresis free operation given by

$$t_{FE} = \frac{1}{2\alpha C_s}....(15)$$

where  $\alpha$  is the material property of the ferroelectric and  $C_S$  is the semiconductor capacitance.

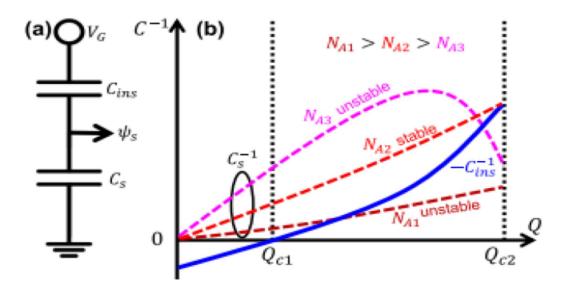

In [25] design guidelines for designing NCFETs are given. They showed that for stableoperation, the total capacitance of the system should be positive, and hence

$$C_S^{-1}(Q) > C_{ins}^{-1}(Q)$$

(16)

throughout the region of operation of the device. Further for minimum coupling factor m, C<sub>S</sub> and ferroelectric capacitance -Cins should be as close as possible.

For ferroelectric FET operating in stable region, they showed that the minimum subthreshold swing is given by

$$SS_{min} = \frac{2.3k_BT}{q} \left( 1 + \frac{M}{y_0} \right) \tag{17}$$

where

$$M = (2\phi_t(\alpha Q_{C1} + \beta Q_{C1}^3 + \gamma Q_{C1}^5)/(2\alpha^2 Q_{C1}^2),$$

$$y_0 = \sqrt{\frac{4\phi_f \phi_t}{\alpha^2 Q_{C1}^2}}$$

and QC1 is the solution of the equation

$$5\gamma Q_C^4 + 3\beta Q_C^2 + \alpha = 0.$$

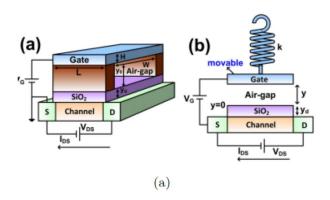

Figure 4(a) capacitive model of fet (b) stability analysis of fet for different doping concentration

Other implementations of NCFETs have been discussed in [26,27]. In particular the nano electromechanical switch (NEMS) with suspended gate can also provide the negative capacitance effect. As the suspended gate is charged, it is attracted towards the MOSFET and consequently the voltageacross it decreases. The NEMS

switch can be then used in series with the ferroelectric capacitor to provide an ideal logic switch with SS=0 mV/dec

figure 5: suspended gate and ideal logic switch (a) a suspended gate nomos with a nano mechanical spring (b) sg technology can be used in series with ferroelectric insulator to provide an ideal logic switch by providing a dual energy landscape [26,27]

#### 2.2. EXPERIMENTAL EVIDENCE OF NCFETS

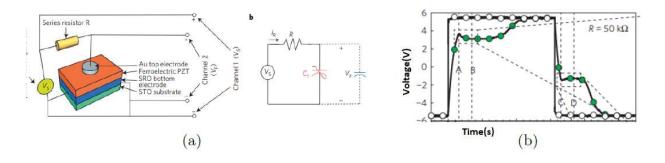

Experimental evidence of NC mechanism has been first provided by A.I.Khan and Salahuddin [28].In this experiment they connected a ferroelectric capacitor in series with a high resistor. The flow ofscreening charges from battery is then hindered by the resistance and a transient negative capacitance observed, where in the charge across the ferroelectric decreases even though the voltage across itincreases.

figure 6: experimental evidence of NCFETs (a) experimental setup (b) output obtained while switching

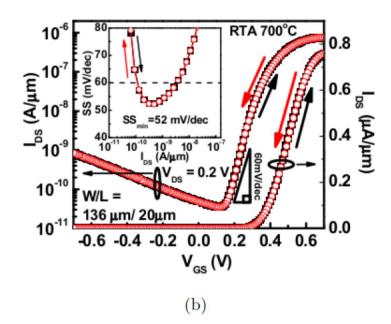

Experimental evidence of FE-FinFETs have been discussed in [29]. In particular in 1.5 nmthickness HZO (HalfniumZincronium Oxide) was used to achieve a subthreshold swing of about 52mV/dec.

Figure 7: experimental evidence of fe-FinFET (a) structure of the device (b) current voltage characteristics

#### 2.3. MODELING NCFETS

The basic methodology to model the performance of NCFETs has been including an additional insulating layer governed by Landau Khaltnikov equation,

$$V_{FE} = 2\alpha Q + 4\beta Q^3 + 6\gamma Q^5$$

.....(18)

and then solve the MOS equation

$$V_G = V_{FE} + \psi_s + \psi_{ox} + V_{FB} \tag{19}$$

self consistently. If the ferroelectric is connected through a metal, Eq. 19 is homogeneous throughout the length of the ferroelectric and can be solved easily. However, if the ferroelectric is connected directly to the dielectric insulator, Eq. 19 has to be solved at each point along the length of the ferroelectric self consistently as is done in [30].

A compact model compatible with BSIM-CMG model has been proposed in [31]. In this workthe core BSIM-CMG model is extended by an additional term. This model can also be used without lumped metal by solving the equation selfconsistently at n points along the channel.

The non-ideal phenomena of leakage through the ferroelectric has been studied in [32]. Theleakage is modeled as resistor parallel to ferroelectric capacitor. The resistor provides an additional path to provide screening charges to ferroelectric degrading its performance. A solution is alsoprovided by changing the metal work functions

appropriately. With appropriate work functionselection, the point where ferroelectrics go into negative capacitance regime is decreased. This also reduces the leakage, as leakage has been modeled as a resistance (I = V/R).

Multidomain nature of ferroelectrics is taken into account in [33] where NEGF formalism hasbeen used to get the device characteristics. An additional term of

$$\kappa \left(\frac{dP_z}{dx}\right)^2$$

.....(20)

has to be added to Eq. to account for variation in polarization in ferroelectric. This gives us an equation of state

$$E_Z = \alpha P + \beta P^3 + \gamma P^5 - k \frac{\partial^2 P_Z}{\partial \gamma^2}.$$

(21)

The k factor is shown to provide a coupling between the polarization in different regions of ferroelectric. Higher values of k are shown to make the ferroelectric polarization more uniform and even the MFIS structure tends to become MFMIS structure.

#### 2.4. GETTING SS LOWER THAN 60 [40]

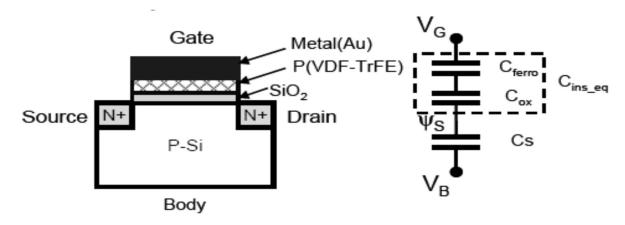

In this work, it has been experimentally demonstrated that integrating a thin FE layer into the gate stack of a standard MOS transistor, we can get a SS lower than 60 mV/decade. It was obtained as low as 13mV/decade in Fe-FETs with 40nm P(VDFTrFE)/ SiO2 gate stack.

Figure 8: 40nm p(vdftrfe)/ sio2 gate stack with the capacitive representation

### 2.5. Low Power NCFETs for QW Body Technology [41]

A new transistor concept is projected that synergistically syndicates two vital trends of future transistors: ultra-thin body to defeat the short-channel properties and sub-60mV/decade operation to radically reduce power dissipation.

NCFET do not change the carrier transport physics and thus benefited from all the permanent and future materials research meant for refining the MOSFET channel transport. On the other hand, NCFET 'amplify' the gate voltage electro-statically to obtain sub-60mV/decade sub-threshold swing (SS). The problem is hysteresis which is seen in the I-V characteristics and is not good for devices.

The structure of the device is shown in Fig.

Figure 9: low power NCFETs for qw body technology (a) structure (b) dimension of the device (c) capacitive model

# 2.6. A COMPACT SUB-THRESHOLD MODEL FOR SHORT-CHANNEL MONOLAYER TRANSITION METAL DICHALCOGENIDE FIELD-EFFECT TRANSISTORS [42]

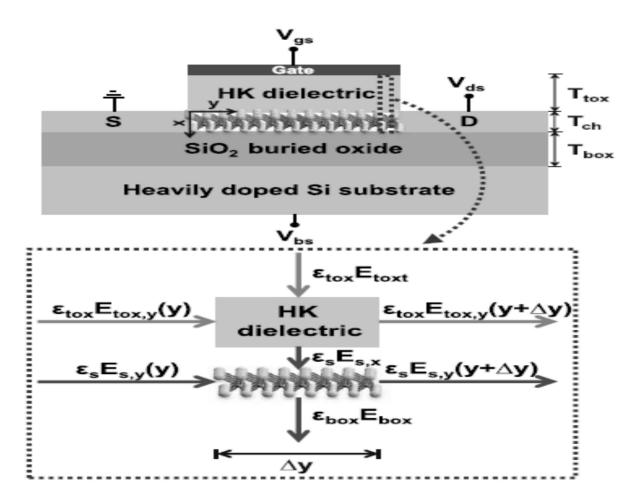

Here fringe field effect of high k insulators is presented. Subthreshold analysis is done for NCFET after considering this effect.

Figure 10: Compact sub-threshold model of box  $SiO_2$

## CHAPTER 3

## **DEVICE STRUCTURE AND MODEL**

#### **DEVICE STRUCTURE**

A simple model for Negative Capacitance FET presented. Discussion on the ballistic to diffusive transport and the electrostatic effects is also made. Lowering of Drain-induced barrier (DIBL) and improvement of subthreshold swing as the Negative Capacitance FETs scale down is also studied. At low voltage operation the improvement of SS results in linear increase of RDIBL.

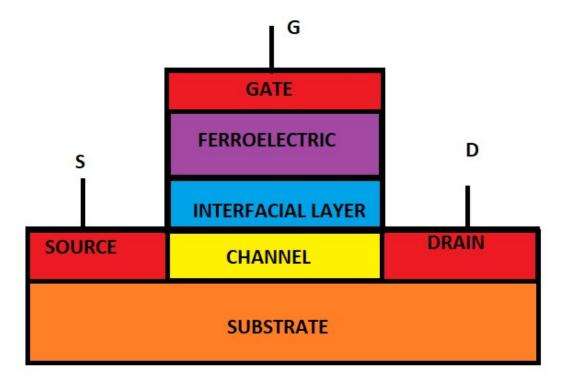

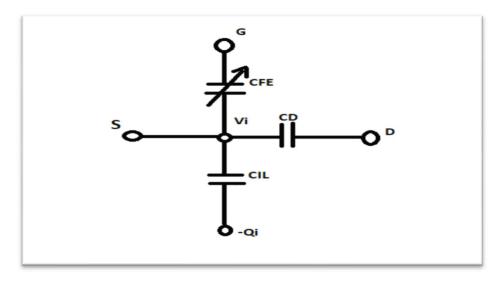

Figure 11: device structure of ncfet

Channel material used is Monolayer MoS2(2D semiconductor). To simulate the native oxide or intentionally induced dielectric a thin dielectric interfacial layer (IL) is included between the semiconductor channel and the FE oxide. Two ferroelectric materials are studied in this thesis.

- a. The FE oxide doped with Si having FE parameters of  $\alpha = -6 \times 10^8$  m/F,  $\beta = 5 \times 10^9$  m<sup>5</sup>/F/C<sup>2</sup>, and  $\gamma = 4 \times 10^{10}$  m<sup>9</sup>/F/C<sup>4</sup>(FE1)

- b. HfZrO( Hafnium Zirchonium Oxide) is used as the ferroelectric material with  $\alpha = -14 \times 10^8$  m/F,  $\beta = 4 \times 10^{12}$  m<sup>5</sup>/F/C<sup>2</sup>, and  $\gamma = 0$  m<sup>9</sup>/F/C<sup>4</sup>(FE2)

The thickness of FE is considered to be 10nm and is varied to analyze its effect on the operation of NCFET.

Further the channel length is taken as 10nm and to analyze the scaling effect it has been lowered to 7nm.

#### **MODEL DESCRIPTION**

In "charge-sheet approximation," the drain current normalized by width (I<sub>d</sub>/W) of a MOSFET can be given as the product of the charge density multiplied by the velocity of the carriers. This equation can be written at the position of the maximum energy barrier. This location is present between source and the channel and is called "virtual source"[38]

$$I_D = Q_i v_{sat}$$

-----(i)

For devices having channel length in nano-meters or less, the velocity at the virtual source, v<sub>sat</sub> is proportional to the thermal velocity [34], [35]. When the device is biased in saturation, weak dependence of velocity to the bias voltage is also observed. These bias voltages are V<sub>GS</sub> or V<sub>DS</sub>. These dependencies can therefore be neglected. Moreover, in [36] it has been proved that in saturation region, the velocity as well as the charge per unit area at the virtual source is independent of V<sub>DS</sub>. Thus, the V<sub>DS</sub> dependencies at the non-ballistic regions also negligible for charge density at the virtual source as well as the potential at that point. In contrast, with the increase in Vgsthe ballistic velocity increases as shown in [36]. In [34] with the help of Monte Carlo simulations it has been shown that the velocity at the virtual source is almost constant at high V<sub>GS</sub>this is because of the increase in carrier scattering. Empirical function in [35] can be used to describe the virtual-source charge density approximated. This expression is valid for the low and high inversion regions and in between as well. The form of the expression was first projected by Wright [37] as follows:

Charge density Qiat the top of the potential barrier is related to the potential Vi:

$$Q_i = C_i \left( nV_{kT} \ln \left[ 1 + \exp\left(\frac{V_i - (V_{T0} - \xi V_{kT} F_f)}{nV_{kT}}\right) \right] \right)$$

$$\dots (22)$$

where  $V_i$  is the potential at the vertical position of the IL-FE layer interface and the top of the barrier,  $C_i$  is the effective capacitance (dielectric IL capacitance,  $C_{IL}$  and series semiconductor capacitance),  $V_{kT}$  is the thermal voltage, n is the subthreshold coefficient.

As the ferroelectric material used is very thin the subthreshold coefficient is taken as 1.

The threshold voltage is given by:

$$V_T = V_{T0} - \xi V_{kT} F_f \qquad (23)$$

and

$$F_f = \left[\frac{1}{\left(1 + exp\left(\frac{\left(V_i - \left(V_{T0} - \frac{\xi V_{kT}}{2}\right)\right)}{\xi V_{kT}}\right)\right)}\right] \tag{24}$$

with  $\xi$  is fitting constant and has no unit.

The device structure can be represented by a capacitance model shown below:

Figure 12: Capacitance model of the structure shown in fig 11

According to L-K Theory(Landau-Khalatnikov) the electric field and the polarization in any ferroelectric material is related as:

$$E = \alpha P + \beta P^3 + \gamma P^5 \tag{25}$$

As

$$P \approx Q$$

so

$$E \approx \alpha Q + \beta Q^3 + \gamma Q^5 \qquad (26)$$

where  $\alpha$ ,  $\beta$ , and  $\gamma$  are FE parameters of the L–K theory. From the above we can find the voltage drop across the FE oxide with a thickness  $t_{FE}$  as

$$V_{FE} = \alpha t_{FE} Q_{FE} + \beta t_{FE} Q_{FE}^{3} + \gamma t_{FE} Q_{FE}^{5}$$

(27)

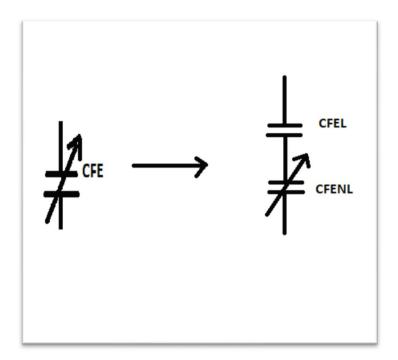

From the above equation we find that there is one term that shows the linear relation between charge and voltage. While the other terms show the non-linear relation. So, the FE capacitance can be viewed as the series combination of a linear and one non-linear capacitance

Figure 13: representation of fe capacitor as linear and non-linear capacitor in series

$$V_{FE} = \frac{Q_{FE}}{C_{FEl}} + V_{FEnl}(Q_{FE}).$$

(28)

Where the linear capacitance is given by

$$C_{FEl} = \frac{1}{\alpha t_{FE}}.$$

(29)

And a non-linear capacitance with voltage drop given by:

$$V_{FEnl}(Q_{FE}) = \beta t_{FE} Q_{FE}^{3} + \gamma t_{FE} Q_{FE}^{5}$$

....(30)

Drain capacitance Cd is used to model 2D electrostatic effect as shown in Fig.

$$Q_i = Q_{FE}(V_{FE}) + C_d \cdot (V_D - V_i)$$

.....(31)

where the voltage drop over the FE layer is  $V_{FE} = V'_{G} - V_{i}$ ,  $V'_{G}$  is the effective gate voltage,  $V_{D}$  is the applied drain voltage, and  $Q_{FE}(V_{FE})$  is the charge of the FE capacitor. For a given bias point, the unknowns  $Q_{FE}$  and  $V_{i}$  can be solved. The charge  $Q_{i}$  can then be computed.

To take into account non-saturation region operation, the velocity  $v_{sat}$  is multiplied by a "saturation function" F. After the charge is computed from the electrostatic model described above, the current can be expressed as

$$I = Qv_{sat}F \qquad (32)$$

where the unitless factor

$$F = \frac{\frac{V_D}{V_{Dsat}}}{((1 + (\frac{V_D}{V_{Dsat}})^{\beta})^{1/\beta})}$$

(33)

$$V_{Dsat} = (v_{sat}L_g)/\mu$$

.....(34)

$V_{\text{sat}}$  is the saturation velocity, and  $\mu$  is the carrier mobility. The above expression of the sourcedrain current can be applied to ballistic, quasi-ballistic, and diffusive transistors, if the saturation velocity and the mobility are expressed as

$$\frac{1}{v_{sat}} = \frac{1}{v_{satB}} + \frac{1}{v_s} \tag{35}$$

$$\frac{1}{\mu} = \frac{1}{\mu_{SB}} + \frac{1}{\mu_S} \tag{36}$$

where  $v_{satB}$  and  $\mu_B$  are the "apparent" saturation velocity and mobility at the ballistic limit, respectively,  $\mu_s$  is the effective mobility due to scattering, the velocity  $v_s = D/l = (kT/q)\mu_s/l$ , and l is the critical length of scattering at the top of the potential barrier.

The apparent carrier saturation velocity at the ballistic limit is

$$v_{satB} = \sqrt{\frac{2kT}{\pi m^*}} \frac{F_1(\eta_F')}{F_0(\eta_F')}$$

(37)

Where  $\eta'_F = (\frac{E_{F1} - E_{C0}}{kT})$  is defined at high  $V_D$  bias condition,  $E_{F1}$  is the source Fermi energy level and  $E_{C0}$  is the conduction band edge at the top of the potential barrier, kT is the thermal energy, and  $m^*$  is the effective mass of the channel material. The apparent mobility at the ballistic limit is determined by

$$\mu_B(L_g) = \frac{\sqrt{2kT/\pi m^*}}{(2kT/q)} \frac{F_{-1}^{-1}(\eta_F)}{F_0(\eta_F)} L_g \qquad (38)$$

$$\eta_F = \left(\frac{E_F - E_{c0}}{kT}\right) \tag{39}$$

is defined at the equilibrium condition at which  $V_D = 0$ .

The definitions of apparent mobility and saturation velocity are based on the ballistic transistor theory and allow descriptions of the ballistic transport limit. Equation indicates that the smaller value of  $\mu_B$  or  $\mu_s$  plays a more dominant role in determining  $\mu$ . Because  $\mu_B$  is proportional to the channel length, the mobility  $\mu$  approaches  $\mu_s$  at the long channel diffusive limit, and it approaches  $\mu_B$  at the short channel ballistic transport limit.

## CHAPTER 4

## RESULTS AND DISCUSSION

The model described in chapter 3 is validated in MATLAB. The results obtained is presented below:

The model is first validated with

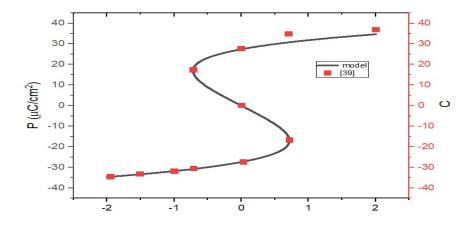

#### 1. POLARIZATION VS ELECTRIC FIELD OF FE OXIDE:

A. FE1: The FE oxide has a thickness of  $t_{FE} = 10$  nm, and FE parameters of  $\alpha = -6 \times 10^8$  m/F,  $\beta = 5 \times 10^9$  m<sup>5</sup>/F/C<sup>2</sup>, and  $\gamma = 4 \times 10^{10}$  m<sup>9</sup>/F/C<sup>4</sup>

For this material the polarization is plotted against electric field. The S type graph is obtained which shows a negative capacitance region.

figure 14: polarization variation wrt electric field for FE1

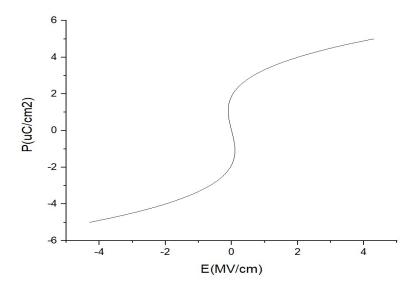

B. FE2: HfZrO is used as the ferroelectric material with  $\alpha = -14 \times 10^8$  m/F,  $\beta = 4 \times 10^{12}$  m<sup>5</sup>/F/C<sup>2</sup>, and  $\gamma = 0$  m<sup>9</sup>/F/C<sup>4</sup>

Similar graph is obtained for another Ferroelectric material. We find that for this ferroelectric material to operate as negative capacitance the voltage variation is very less.

figure 15: polarization variation wrt electric field for FE2

# C. Comparing both in one graph: From the below graph, FE1 is a better material for NCFET than FE2.

figure 16: comparing polarization variation wrt electric field of FE1(blue) and FE2(red)

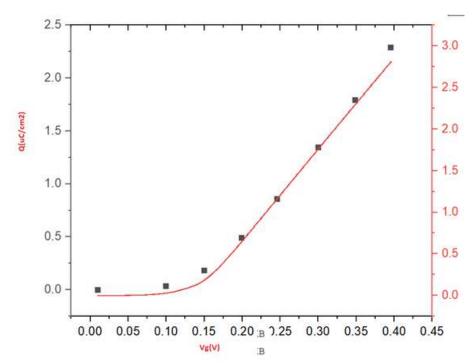

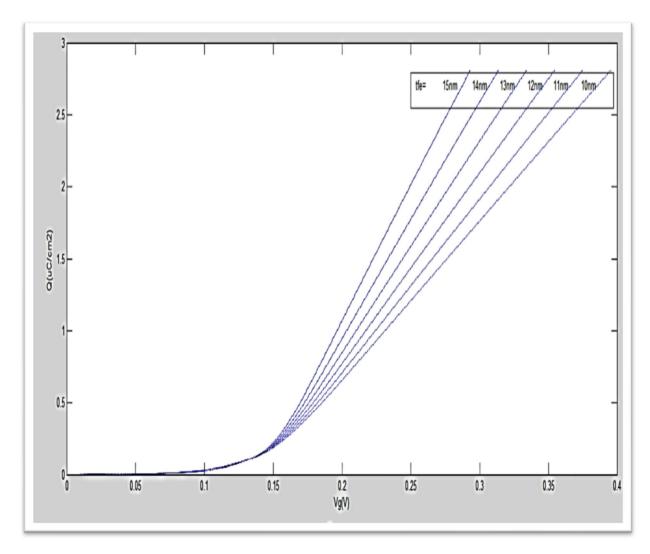

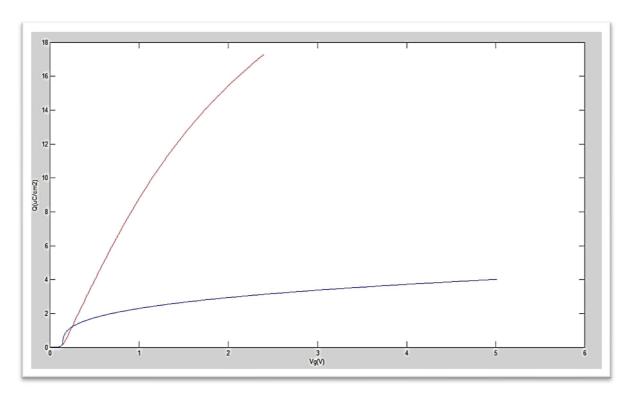

#### 2. CHARGE VERSUS GATE VOLTAGE:

The Charge is plotted against the gate voltage. It has been plotted for different ferroelectric materials with varying thickness of the ferroelectric as well. We find that as the thickness decreases the slope of the graph decreases.

#### a. For FE1

The charge vs gate voltage is plotted in the below figure and its compared with the results obtained in [39]

figure 17: charge variation wrt voltage comparing with [39] (symbol)

figure 18: charge variation wrt voltage at gate with varying tfe for FE1

From the above graph it is obtained that with decrease in the thickness of FE the rate at which the charge increases with voltage reduces.

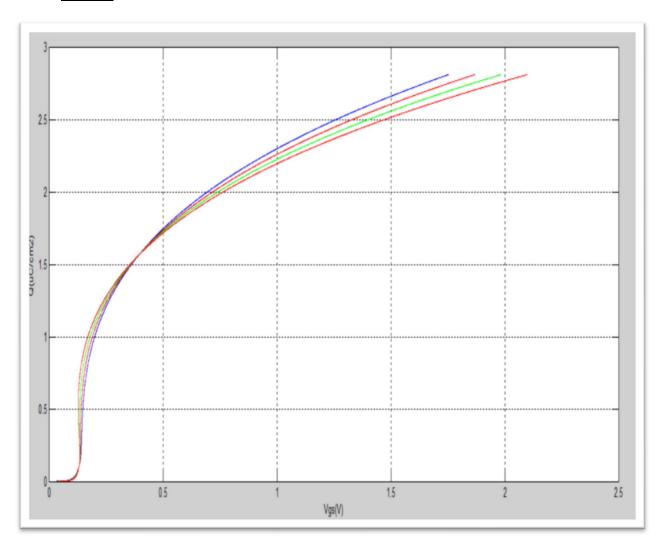

#### b. For FE2

figure 19: charge variation wrt gate voltage for FE2

FE2 shows a unique feature in which at lower gate voltage it mimics the FE1 but at higher gate voltage the properties are vice versa i.e. with decreasing  $t_{\rm FE}$ the slope increases.

## c. COMPARISON OF TWO FERROELCTRICS FOR $T_{FE}$ =10nm

The graph below signifies that the FE1 shows a stable capacitance than FE2 and hence is a better material for NCFETs.

figure 20: comparing charge variation wrt gate voltage for two ferroelectric (blue: FE2)(red: FE1)

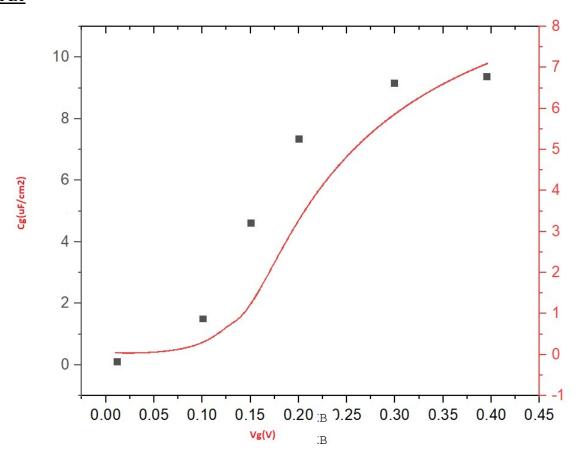

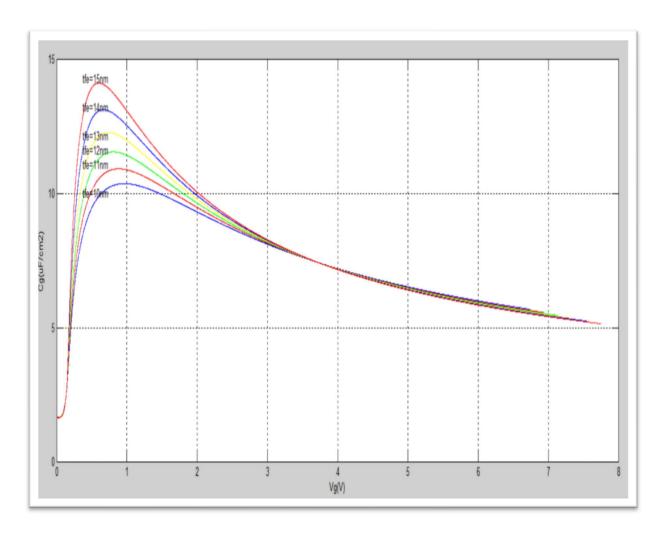

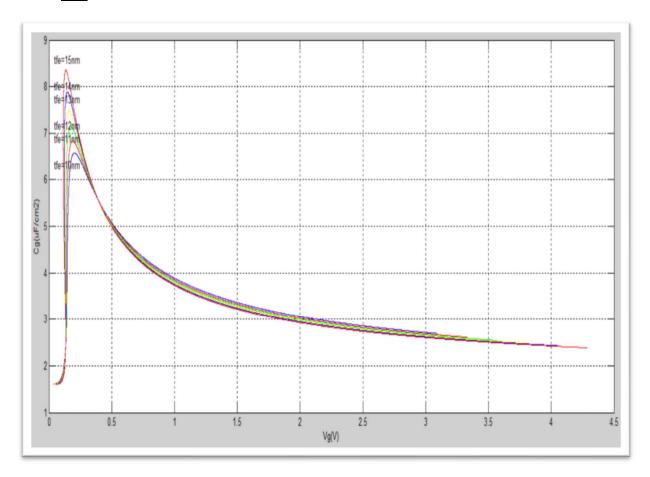

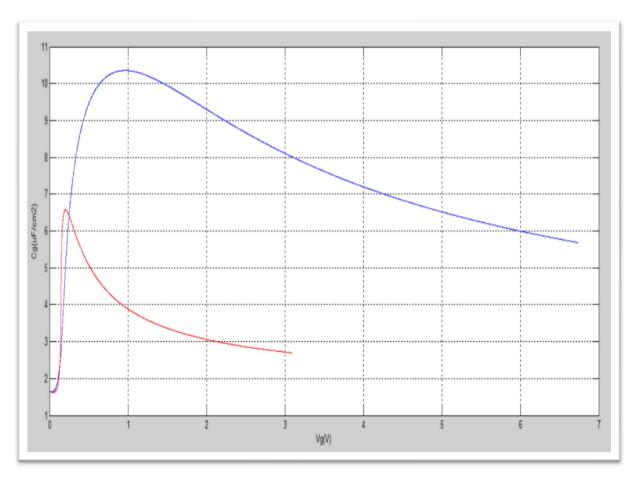

## 3. <u>CAPACITANCE VS VOLTAGE CHARACTERISTICS OF THE MODELED FE-IL-SEMICONDUCTOR GATE-STACK</u>

The capacitance of the gate stack is plotted against the voltage to show how the total capacitance varies with voltage as well as thickness of the FE materials. The total gate capacitance of  $C_G \approx 10.4 \,\mu\text{F/cm}^2$  at  $V_G = 1 \,\text{V}$ , which is the serial combination of the FE capacitance, IL dielectric capacitance, and the semiconductor capacitance, is larger than the IL dielectric capacitance of  $C_{IL} \approx 8.85 \,\mu\text{F/cm}^2$ , because of the negative FE capacitance.

#### a. <u>FE1</u>

figure 21: capacitance variation wrt voltage for FE1 wrt [39](symbols)

figure 22: capacitance variation wrt Vg for fe1 with varying  $t_{\rm fe}$

## b. <u>FE2</u>

figure 23: capacitance variation wrt gate voltage for FE2 for varying FE thickness

### c. **COMPARING TWO FE**

figure 24: charge variation wrt gate voltage characteristics and comparation for FE1(blue) and FE2(red)

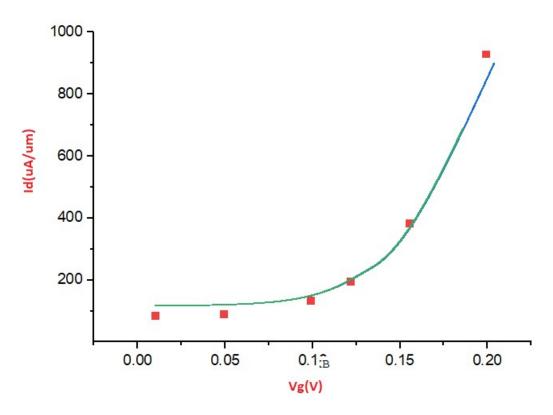

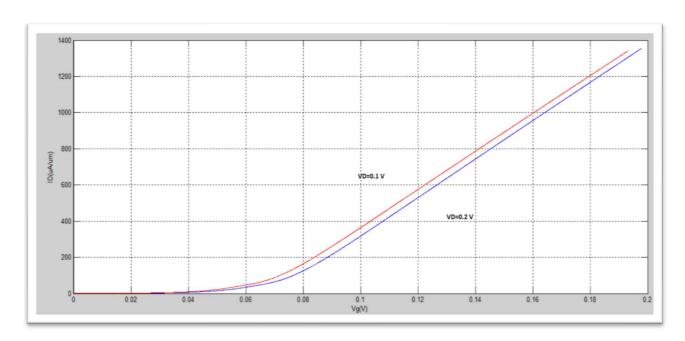

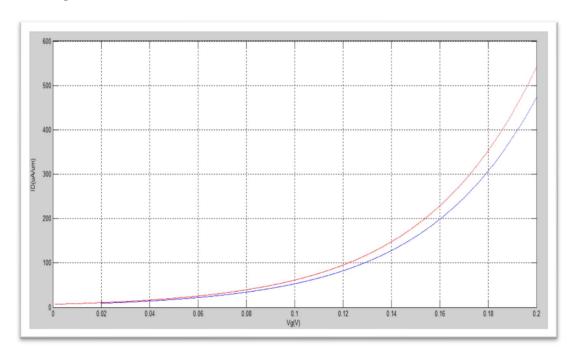

## 4. DRAIN CURRENT VS GATE VOLTAGE

## a. $FE1 L_g=10nm$

figure 25: drain current variation wrt gate voltage for FE1 and comparing with [39](symbols) for Vd=0.1 V

figure 26: drain current variation wrt gate voltage for FE1 varying Vd (drain voltage)

## b. <u>FE2 L<sub>g</sub>=10nm</u>

figure 27: drain current variation wrt gate voltage for FE2 (blue= Vg=0.2V; red= Vg=0.1V)

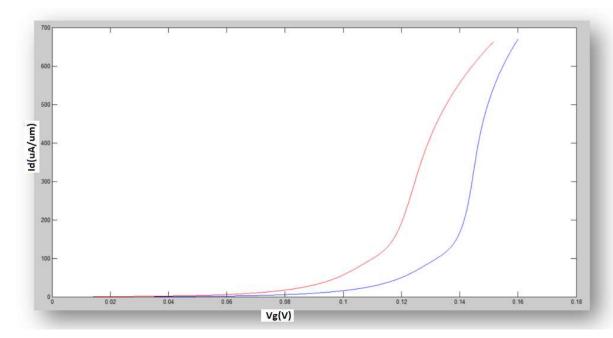

## c. $FE1 L_g=7nm$

figure~28: drain~current~variation~wrt~gate~voltage~for~FE1~at~channel~length~of~7nm~(blue=~Vg=0.2V;~red=~Vg=0.1V)

## d. FE2 Lg=7nm

figure 29: drain current variation wrt gate voltage for FE2 (blue= Vg=0.2V; red= Vg=0.1V)

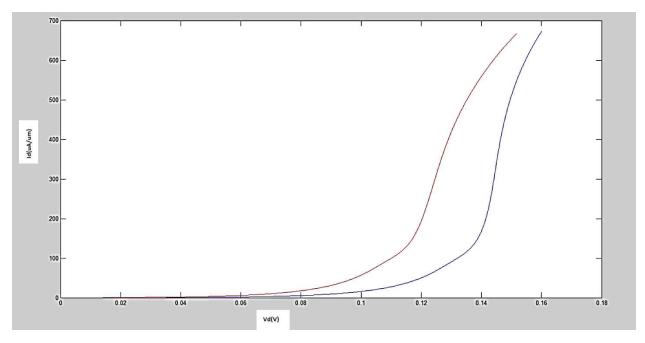

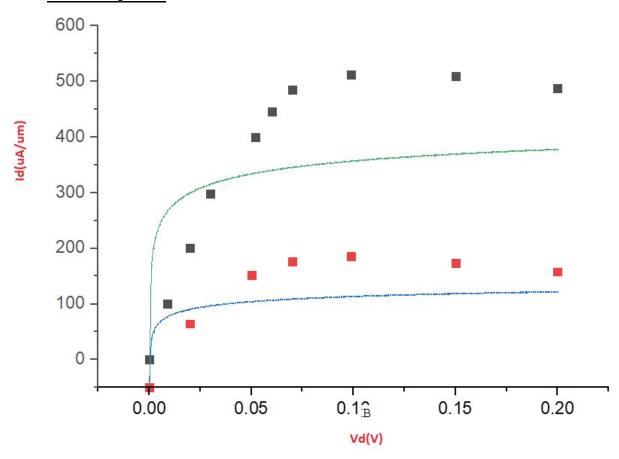

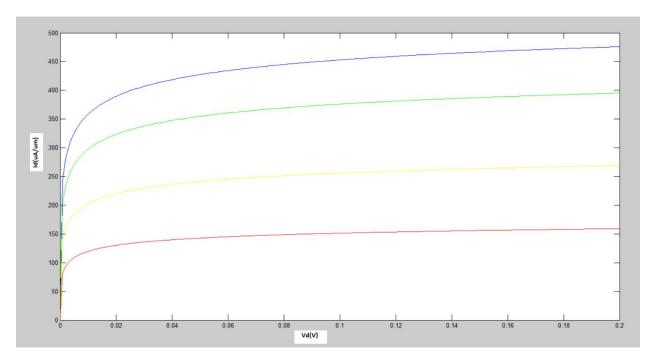

### 5. DRAIN CURRENT VS GATE VOLTAG FOR FE1

### a. FE1 with L<sub>g</sub>=10nm

figure 30: Id variation wrt Vd for FE1 and comparing with refernce [39] at vg=0.2v (black symbol and green line) and at Vg=0.16v (red symbols and blue line)

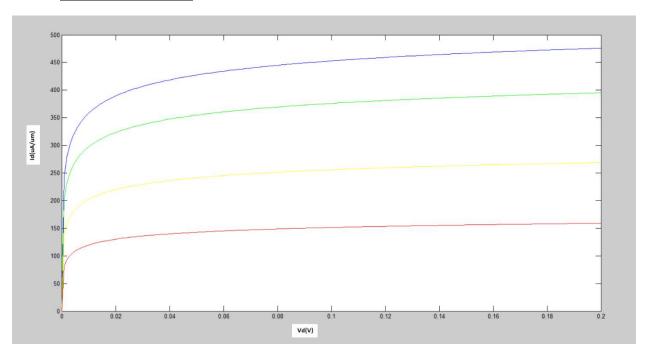

figure~31: Id~variation~wrt~Vd~for~different~Vg~(blue=~Vd=0.2V;~green=~Vd=0.18V;~yellow=~Vd=0.16V;~red=~Vd=0.14V)

#### b. FE2 WITH L<sub>g</sub>=10nm

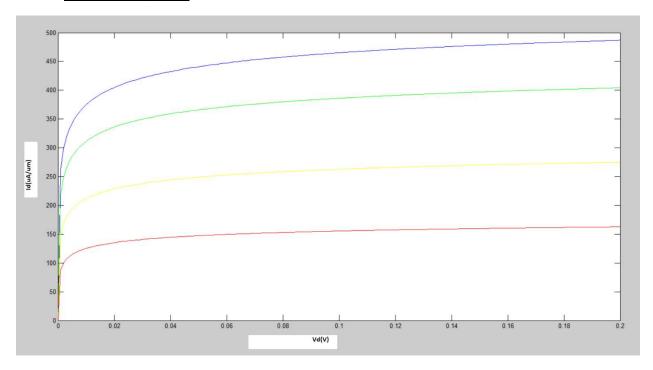

figure~32:: Id~variation~wrt~Vd~for~different~Vg~(blue=~Vd=0.2V;~green=~Vd=0.18V;~yellow=~Vd=0.16V;~red=~Vd=0.14V)

## c. FE1 WITH L<sub>g</sub>=7nm

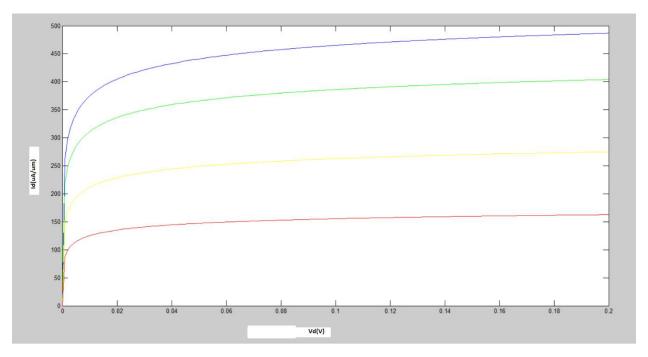

figure~33:: Id~variation~wrt~Vd~for~different~Vg~(blue=~Vd=0.2V;~green=~Vd=0.18V;~yellow=~Vd=0.16V;~red=~Vd=0.14V)

#### d. FE2 WITH L<sub>g</sub>=7nm

figure 34: : Id variation wrt Vd for different Vg (blue= Vd=0.2V; green= Vd=0.18V; yellow= Vd=0.16V; red= Vd=0.14V)

As we saw, scaling down the gate length in an NC MOSFETs helps in getting larger DIBL, and the smaller Subthreshold Swing.

Based on the model, discussed in Chapter 3, the effective gate voltage is

$$V'_G = V_G - V_{FB} = V_i + V_{FE} = V_i + V_{FEl} + V_{FEnl}$$

.....(44)

where  $V_{\rm FB}$  is the flat band voltage.

For the device operating at lower voltage, the potential drop across the FE layer is linearized as  $V_{\text{FE}} \approx V_{\text{FE}l}$ , provided the potential drop across the nonlinear one is smaller related to that of the linear one, i.e.,  $V_{\text{FE}n} + V_{\text{FE}l}$ . The effective gate voltage can be roughly expressed as

$$V_G - V_{FB} \approx V_i + \alpha t_{FE} Q_{FE} \approx V_i + \alpha t_{FE} (Q_i + C_d (V_i - V_D))$$

.....(45)

Let us consider an NCFET working in the subthresholdregion. Taking partial derivative on Vgin [45] with respect to  $V_i$  (45)

$$\frac{\partial vg}{\partial v_i} \approx 1 + \alpha t_{FE} C_d + \alpha t_{FE} C_{se}$$

.....(46)

where the capacitance  $C_{se} = (\partial Q_i / \partial V_i)$ , which can be calculated by differentiating equation.

The Subthreshold Swing is given by

$$s \approx \frac{\partial Vg}{\partial \log_{10} I_D} = S_0 [1 + \alpha t_{FE} C_d + \alpha t_{FE} C_{se}]....(47)$$

$S_0=(kT/q)\ln(10)$  is thermal limit of SS.

The value of DIBL can be stated as

$$DIBL = \frac{\partial Vg}{\partial Vd} \approx \alpha t_{FE} C_d.$$

(48)

Thus, DIBL can betaken as the shift of the threshold voltage in the subthreshold region as the drain voltage increases. Because of  $\alpha$  <0, the DIBL is negative, which is reverseof the conventional FETs.

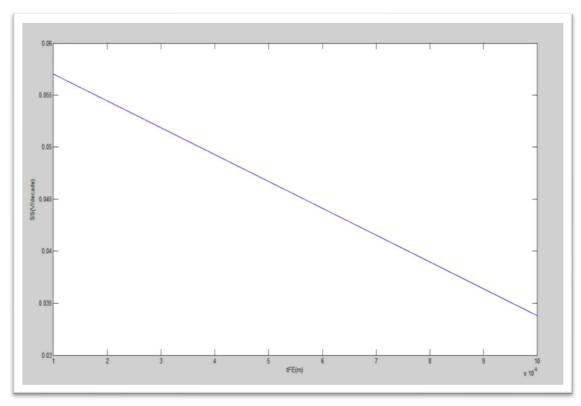

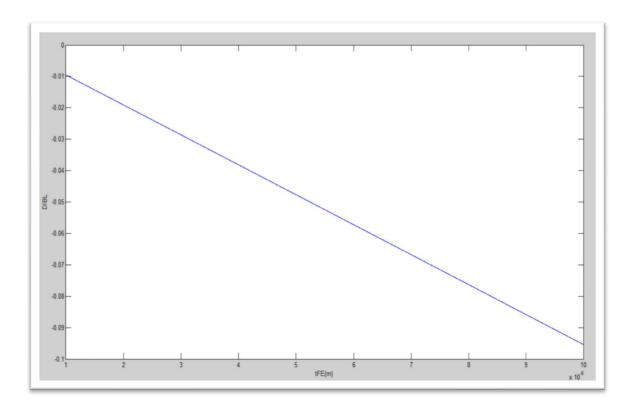

figure 35: subthreshold swing variation wrt FE thickness

figure 36: DIBL variation wrt FE thickness

#### **DISCUSSION**

Figure 14 shows the polarization vs electric field plot of the ferroelectric material that is Si doped. The graph shows comparison between the model and [39]. Figure 15 shows the same for FE2. Figure 16 compare the result for FE1 and FE2. The graph obtained is as S-shaped graph. It is seen that the operating voltage for FE1 is greater than FE2 and hence FE1 can be used as a better material for NCFET. The stability of the NCFET made with FE1 will be better than that made with FE2.

Figure 17 shows the charge vs gate voltage of the FE1 and comparison with [39]. Figure 18 shows the same for different ferroelectric material thickness. It depicts that with decrease in the thickness of FE the rate at which the charge increases with voltage reduces. Figure 19 shows it for FE2. FE2 shows a unique feature in which at lower gate voltage it mimics the FE1 but at higher gate voltage the properties are vice versa i.e. with decreasing t<sub>FE</sub> the slope increases. In figure 7 comparison of the two FE is made. The graph signifies that the FE1(blue) shows a stable capacitance than FE2 and hence is a better material for NCFETs.

Figure 22-24 shows the capacitance vs gate voltage plot. It is obtained that for lower gate voltage the charge increases and then at higher voltage, the charge is found to decrease. The graph is obtained for different ferroelectric thickness. We found that at lower thickness the maximum charge that can be stored is lesser than for higher thickness. Moreover, FE1 peak is higher and at higher voltage as well.

Figure 25-29 shows the current vs gate voltage. The result is analysed for two different channel length. We found that with the decrease in VD, current increases.

Figure 30-34 shows the current vs drain voltage. The result is analysed for two different channel length. The results show more pronounced 2-D electrostatic effects, with an increase magnitude of the DIBL. At the same time, the SS reduces.

Figure 35 shows that with the increase in ferroelectric material thickness, subthreshold slope decreases. In figure 36 shows that with the increase in ferroelectric material thickness, improvement of DIBL.

# CHAPTER 5

## **CONCLUSION AND FUTURE WORK**

A modest model of NCFET is offered, which takes into account the 2-D electrostatic short channel effects, and ballistic to diffusive transport regimes. Mathematicalmodel-based study for the NCFET structure is established. Further, no floating internal gate is considered. By applying the proposed model and numerical simulations to a ballistic NCFET with monolayer MoS2 as the channel material, it is revealed that the model can precisely describe the reverse DIBL, and development of the SS, for the NCFETs at the 10-nm scale and below.

The relations specify that as an NCFET —gages down, the relative enhancement of the SS over the thermionic limit due to 2-D electrostatic effects results in an equally large surge of the reverse DIBL.

Presenting a work opens more scope more future work. This is true in this case as well. Future work may include a new model and study of more physical properties. Till now the work in NCFET or more specifically the model is analysed in 1D and 2D. Thus, in future works complete 3D analysis can be done. This analysis should consider the anisotropic properties of FE materials and the direction of permanent polarization. Mechanical properties of the FE materials can also be studied. Stress and strain effects the FE properties heavily. As in Fabrication process lattice mismatch can induce large stress and strain so proper study needs to be done. Accordingly, Landau parameters alpha, beta and gamma depends on many external parameters like stress, temperature, etc.

## REFERENCES

- [1] J. E. Lilienfeld, "Methods and apparatus for controlling electric current," US Patent 1 745 175. Application filed Oct. 8, 1926, granted Jan. 18, 1930.

- [2] J. E. Lilienfeld, "Device for controlling electrical current," US Patent 1 900018. Application filed Mar. 28, 1928, granted Mar. 7, 1933.

- [3] O. Heil, "Improvements in or relating to electrical amplifiers and other control arrangements and devices," British Patent 439 457. Application filed Mar. 4, 1935, granted Dec. 6, 1935.

- [4] D.Kahng and M. M. Atalla, "Silicon-silicon dioxide field induced surface devices," IRE-AIEEE Solid-State Device Research Conference, Carnegie Institute of Technology, Pittsburgh, PA, 1960.

- [5] A. H. Wilson, Proc. Royal Soc., vol. 133A, p. 458, 1931.

- [6] R. S. Ohl, "Light-sensitive electrical device," US Patent 2 402 662. Application filed May 27, 1941, granted June 25, 1946.

- [7] M. Riordan and L. Hoddeson, "The origins of the p-n junction," IEEE Spectrum, vol. 34, pp. 46-51, June 1997.

- [8] W. H. Brattain, "Discovery of the transistor effect," Adventures in Experimental Phys., vol. 5, pp. 1-31, 1976.

- [9] W. B. Shockley, "The path to the conception of the junction transistor," IEEE Trans. Electron Dev., vol. ED-23, pp. 597-620, July 1976.Reprinted, vol. ED-31, pp. 1523-1546, Nov.1984.

- [10] J. Bardeen and W. H. Brattain, "Three-electrode circuit element utilizing semi-conductive materials," US Patent 2 524 035. Application filed June 17, 1948, granted Oct. 3, 1950.

- [11] J. Bardeen and W. H. Brattain, "The transistor, a semi-conductor triode," Phys. Rev., vol. 74, pp. 230-231, July 1948.

- [12] W. B. Shockley, "Electron and Holes in Semiconductors," Van Nostrand, NewYork, 1950.

- [13] W. B. Shockley, "Circuit element utilizing semi-conductive material," US Patent 2569347. Application filed June 26, 1948, granted Sept 25, 1951.

- [14] G.E. Moore, "Cramming more components onto integrated circuits," Electronics Vol. 38, no. 8, pp. 114-117, 1965.

- [15] S. Borkar, "Design Challenges of Technology Scaling," IEEE Micro, July-August 1999, pp 23-29.

- [16] Kish, L. End of Moore's law: thermal (noise) death of integration in micro and nano electronics. Phys. Lett.. A **2002**, 305, 144.

- [17] R. K Cavin.; V. Zhirnov V., Hutchby, J. A. Energy Barriers, Demons And Minimum Energy Operation Of Electronic Devices. Fluctuations Noise Lett. 2005, 5, C29.

- [18] V. Zhirnov.; , I. R. K Cavin.; J Hutchby.; G. Bourianoff, Limits to binary logic switch scaling a gedanken model. Proc. IEEE **2003**, 91, 1934.

- [19] Computer chips cut energy consumption. <a href="http://physicsweb.org/">http://physicsweb.org/</a> articles/news/11/1/25.

- [20] Landau, L. D.; Khalatnikov, I. M. "On the anomalous absorption of sound near a second order phase transition point," Dokl. Akad. Nauk, vol. 96, pp. 469-472, 1954.

- [21] Lo, V. C. "Simulation of thickness effect in thin ferroelectric films using Landau-Khalatnikov theory." J. Appl. Phys. **2003**, 93 (5), 3353-3359.

- [22] Zhang, W.; Bhattacharya, K. A computational model of ferroelectric domains. Part I: model formulation and domain switching. Acta Mater. **2005**, 53, 185-198.

- [23] Mistsui, T.; Tatsuzaki, I.; Nakamura, E. An Introduction to the Physicsof Ferroelectrics; Gordon and Breach Science Publishers: London,1976.

- [24] S. Salahuddin and S. Datta, "Use of negative capacitance to provide voltage amplification for low power nanoscale devices," Nano Lett., vol. 8, no. 2, pp. 405-410, 2008, pMID: 18052402. [Online]. Available: https://doi.org/10.1021/nl071804g

- [25] A. Jain and M. A. Alam, "Stability constraints define the minimum subthreshold swing of a negativecapacitance field-effect transistor, IEEE Trans. Electron Devices, vol. 61, no. 7, pp. 2235-2242, July 2014

- [26] "Proposal of a hysteresis-free zero subthreshold swing field-ffect transistor," IEEE Transactions on Electron Devices, vol. 61, no. 10, pp. 3546-3552, Oct 2014.

- [27] "Prospects of hysteresis-free abrupt switching (0 mv/decade) in landau switches," IEEETransactions on Electron Devices, vol. 60, no. 12, pp. 4269-4276, Dec 2013.

- [28] A. I. Khan, K. Chatterjee, B. Wang, S. Drapcho, L. You, C. Serrao, S. R. Bakaul, R. Ramesh, and S. Salahuddin, "Negative capacitance in a ferroelectric capacitor," Nature Mater., vol. 14,no. 2, p. 182, 2015.

- [29] M. H. Lee, S. T. Fan, C. H. Tang, P. G. Chen, Y. C. Chou, H. H. Chen, J. Y. Kuo, M. J. Xie, S. N. Liu, M. H. Liao, C. A. Jong, K. S. Li, M. C. Chen, and C. W. Liu, "Physical thickness 1.xnm ferroelectric hfzrox negative capacitance fets," in 2016 IEEE Int. Electron Devices Meeting (IEDM), pp. 12.1.1-12.1.4., Dec 2016

- [30] G. Pahwa, T. Dutta, A. Agarwal, and Y. S. Chauhan, "Compact model for ferroelectric negative capacitance transistor with mos structure," IEEE Trans. Electron Devices, vol. 64, no. 3, pp. 1366{1374, March 2017.

- [31] J. P. Duarte, S. Khandelwal, A. I. Khan, A. Sachid, Y. K. Lin, H. L. Chang, S. Salahuddin, and C. Hu, "Compact models of negative-capacitance finfets: Lumped and distributed chargemodels," in 2016 IEEE International Electron Devices Meeting (IEDM), pp. 30.5.1-30.5.4, Dec 2016.

- [32] A. I. Khan, U. Radhakrishna, K. Chatterjee, S. Salahuddin, and D. A. Antoniadis, "Negativecapacitance behavior in a leaky ferroelectric," IEEE Transactions on Electron Devices, vol. 63,no. 11, pp. 4416-4422, Nov 2016.

- [33] A. K. Saha, P. Sharma, I. Dabo, S. Datta, and S. K. Gupta, "Ferroelectric transistor modelbased on self-consistent solution of 2D Poisson's, non-equilibrium green's function and multi-domain landau khalatnikov equations," in 2017 IEEE International Electron Devices Meeting (IEDM), pp. 13.5.1-13.5. Dec 20174.

- [34] A. Khakifirooz and D. A. Antoniadis, "Transistor performance scaling: The role of virtual source velocity and its mobility dependence," in IEDM Tech. Dig., pp. 667–670, 2006.

- [35] M. S. Lundstrom, "Elementary scattering theory of the Si MOSFET," IEEE Electron Device Lett., vol. 18, no. 7, pp. 361–363, Jul. 1997.

- [36] M. S. Lundstrom and Z. Ren, "Essential physics of carrier transport in nanoscale MOSFETs," IEEE Trans. Electron Devices, vol. 49, no. 1, pp. 133–141, Jan. 2002.

- [37] G. T. Wright, "Threshold modelling of MOSFETs for CAD of CMOSVLSI," Electron Lett., vol. 21, no. 6, pp. 223–224, Mar. 1985.

- [38] A. Khakifirooz, O. M. Nayfeh, and D. A. Antoniadis, "A simple semiempirical short-channel MOSFET current-voltage model continuous across all regions of operation and employing only physical parameters," IEEE Trans. Electron Devices, vol. 56, no. 8, pp. 1674–1680, Aug. 2009.

- [39] Z. Dong and J. Guo, "A Simple Model of Negative Capacitance FET With Electrostatic Short Channel Effects" IEEE TRANSACTIONS ON ELECTRON DEVICES, vol.64, pp. 2927-2934, 2017.

- [40] A. Saeidi, F. Jazaeri, I. Stolichnov and A.M. lonescu, "Double-Gate Negative-Capacitance MOSFET with PZT Gate-Stack on Ultra Thin Body SOI: An Experimentally Calibrated Simulation Study of Device Performance," IEEE Transactions on Electron Devices, vol. 63 pp. 4678-4684, October 2016.

- [41] T. Kodaka, et al., "A Near-Future Prediction Method for Low Power Consumption on a Many-Core Processor" Conference Paper EDAA January 2013.

- [42] W- X. You and Pin Su"A Compact Subthreshold Model for Short-Channel Monolayer Transition Metal Dichalcogenide Field-Effect Transistors" IEEE Transactions on Electron Devices, vol. 63, no. 7, pp. 1-4, 2016.