# Optimisation and Analytical Modelling of Tunnel Field Effect Transistor Structures for Low Power Applications

Thesis Submitted in Partial Fulfilment of the Requirements for the Award of the Degree of

### Master of Engineering in Electronics and Tele-Communication Engineering

BY

#### **Rounak Dutta**

Roll No: 001710702009

**Examination Roll No: M4ETC19011**

Registration No: 140695 of 2017-18

Under the Esteemed Guidance of

#### **Prof. Subir Kumar Sarkar**

Department of Electronics and Tele-Communication Engineering

Jadavpur University, Kolkata-700032

West Bengal, India

**MAY 2019**

## Faculty of Engineering & Technology Jadavpur University

#### **CERTIFICATE OF EXAMINATION**

This is to certify that the thesis entitled "Optimisation and Analytical Modelling of Tunnel Field Effect Structures for Low Power Applications" has been carried out by ROUNAK DUTTA (Roll No: 001710702009, Examination Roll No: M4ETC19011 and Registration No: 140695 of 2017-18) under my guidance and supervision and can be accepted in partial fulfilment for the degree of Master of Engineering in Electronics and Tele-communication Engineering. In my opinion the work fulfils the requirement for which it is submitted. To the best of my knowledge, the matter embodied in the thesis has not been submitted to any other organization.

#### **Prof. Subir Kumar Sarkar**

**Project Supervisor**

Department of Electronics and Tele-Communication Engineering

Jadavpur University, Kolkata-700032

#### Prof. Sheli Sinha Chaudhuri

Head of the Department

Department of Electronics and

Tele-Communication Engineering

Jadavpur University, Kolkata-700032

#### **Prof. Chiranjib Bhattacharjee**

Dean

Faculty Council of Engineering and

Technology (FET)

Jadavpur University, Kolkata-700032

# Faculty of Engineering & Technology Jadavpur University

#### **CERTIFICATE OF APPROVAL\***

This is to certify that the Master Thesis entitled "Optimisation and Analytical Modelling of Tunnel Field Effect Transistor Structures for Low Power Applications" is hereby approved as a creditable study of an engineering subject carried out and presented in a manner satisfactory to warrant its acceptance as prerequisite to the degree for which it has been submitted. It is understood that by this approval the undersigned do not necessarily endorse or accept every statement made, opinion expressed, or conclusion drawn therein but approve the thesis only for the purpose for which it has been submitted.

| C | Committee on Final Examination |  |

|---|--------------------------------|--|

|   | For Evaluation of the Thesis   |  |

|   |                                |  |

|   |                                |  |

|   |                                |  |

|   |                                |  |

|   |                                |  |

|   | Examiners                      |  |

\*Only in case the thesis is approved.

## DECLARATION OF ORIGINALITY AND COMPLIANCE OF ACADEMIC ETHICS

I hereby declare that the M.E. thesis entitled submitted to Faculty of Engineering & Technology, Jadavpur University as part of fulfillment of degree of Master of Engineering in Electronics and Tele-communication Engineering is an original work carried out by undersigned. All information in this document have been obtained and presented in accordance with academic rules and ethical conduct. The matter embodied in this project is a genuine work done by the undersigned and has not been submitted to any other University/Institute for the fulfillment of the requirement of any course of study.

I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

NAME: ROUNAK DUTTA

EXAMINATION ROLL NUMBER: M4ETC19011

DEPARTMENT: Electronics and Tele-Communication Engineering (E.T.C.E.).

THESIS TITLE: Optimisation and Analytical Modelling of Tunnel Field Effect Structures for Low Power Applications.

(ROUNAK DUTTA)

Signature with Date

### **ACKNOWLEDGEMENT**

It gives me great joy to be able to express my gratitude for the fond memories that I have come to gather from the Electronics & Telecommunication Engineering Department at Jadavpur University. I feel very fortunate to be a part of the esteemed institution.

I would like to take this opportunity to thank my Project/Thesis supervisor *Prof. Subir Kumar Sarkar*, for his immense help in finalizing my final year thesis, and also for providing the study materials for the literature study required for the same. I am also thankful for all his suggestions and deep insights, which helped in overcoming the problems faced during the project.

I would like to thank *Prof. Sheli Sinha Chaudhuri*, H.O.D of Electronics and Telecommunication Engineering, for providing all the laboratory facilities required for completion of my project work.

Also, this work would not have been possible without the help that I have received from all my laboratory colleagues, especially *Mr. Bijoy Goswami, Mr. Dinesh kumar Dash, Mrs. Priyanka Saha, Ms. Pritha Banerjee, Mr. Anup Dey, Mr. Ayan Bhattacharya, Mr. Bikram Biswas, Ms. Sutanni Bhowmick* and *Ms. Debadipta Basak.*

Finally, I would like to thank my family for their immense support during the project work and also, for supporting me in almost all the biggest endeavours of my life.

#### **THANK YOU**

ROUNAK DUTTA

M.E. - ELECTRON DEVICE

Department of E.T.C.E., Jadavpur University

Kolkata-700032, West Bengal, India.

## **Contents**

| T   | opic        |         | Pag                                                     | e No.    |

|-----|-------------|---------|---------------------------------------------------------|----------|

| Ce  | rtificate o | of Exan | nination                                                | I        |

| Ce  | rtificate o | of Appr | oval                                                    | II       |

| De  | claration   | of Ori  | ginality and Compliance of Academic Ethics              | III      |

| Ac  | knowledg    | gemen   | t                                                       | IV       |

| Со  | ntents      |         |                                                         | V        |

| Lis | st of Figur | es      |                                                         | VII      |

| Ab  | breviatio   | ns      |                                                         | IX       |

| Ab  | stract      |         |                                                         | XI       |

| 1.  | Introdu     | ction   |                                                         | 1        |

|     |             | 1.1.    | A Dive into the History of Electronic Computing         | 1        |

|     |             | 1.2.    | The Tale of the Almighty MOSFET                         | 2        |

|     |             | 1.3.    | Nothing Lasts Forever: The Problems with MOSFET Scaling | g 4      |

|     |             | 1.4.    | The Motivation                                          | 6        |

|     |             | 1.5.    | Organisation of the Thesis                              | 8        |

|     |             | Refer   | rences                                                  | 9        |

| 2.  | Theory o    | of Tunr | nelling                                                 | 11       |

|     |             | 2.1.    | What is Quantum Mechanical Tunnelling?                  | 11       |

|     |             | 2.2.    | A Brief introduction to Band-to-Band Tunneling          | 13       |

|     |             | 2.3.    | Band-to-Band Tunnelling Models                          | 14       |

|     |             | 2.4.    | Kane's Local Tunnelling Model                           | 15       |

|     |             | 2.5.    | A Brief Overview of the Simulator Used                  | 18       |

|     |             | Refer   | rences                                                  | 22       |

|     |             |         |                                                         | Dogo I V |

| 3. The Tunnel Field Effect Transistor (TFET) |         | 23                                                    |    |

|----------------------------------------------|---------|-------------------------------------------------------|----|

|                                              | 3.1.    | Basic Construction of TFET                            | 23 |

|                                              | 3.2.    | Working Principle of TFET in Brief                    | 24 |

|                                              | 3.3.    | A Brief Literature Review on Various TFET Designs for |    |

|                                              |         | Performance Enhancement                               | 29 |

|                                              | Refe    | rences                                                | 40 |

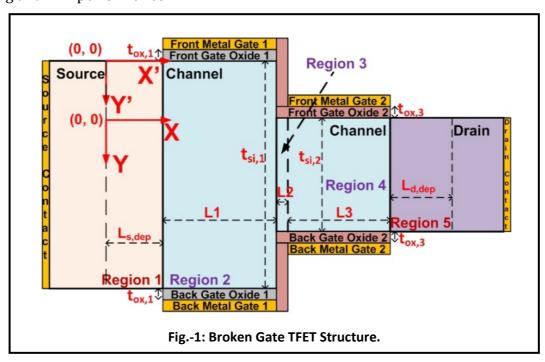

| 4. Analytic                                  | cal Mod | deling and Simulation based Optimization of Broken    |    |

| Gate TF                                      | ET Strı | acture for Low Power Applications                     | 44 |

|                                              | 4.1.    | Introduction                                          | 44 |

|                                              | 4.2.    | The Device Structure                                  | 45 |

|                                              | 4.3.    | Optimisation of the Device Structure                  | 47 |

|                                              | 4.4.    | Derivation of the Analytical Model                    | 51 |

|                                              | 4.5.    | Parasitic Capacitances in Broken Gate TFET Structure  | 62 |

|                                              | 4.6.    | Appendix                                              | 64 |

|                                              | Refe    | rences                                                | 65 |

| 5. Conclusion and Scope for Future Work      |         | 69                                                    |    |

|                                              | 5.1.    | Conclusion                                            | 69 |

|                                              | 5.2.    | Scope for Future Work                                 | 73 |

## **List of Figures**

| Figure No | . Figure Title                                                        | Page :  | No.  |

|-----------|-----------------------------------------------------------------------|---------|------|

|           | Chapter-1                                                             |         |      |

| 1.1.      | Intel's first Microprocessor C4004.                                   |         | 2    |

| 1.2.      | The transistor count per IC over 50 years, obeying                    |         |      |

|           | the Moore's Law.                                                      |         | 4    |

| 1.3.      | All the current leakages in MOSFET.                                   |         | 5    |

| 1.4.      | Transfer Characteristics comparison between TFET and N                | MOSFET. | 8    |

|           | Chapter-2                                                             |         |      |

| 2.1.      | Tunnelling through a rectangular potential barrier.                   |         | 12   |

| 2.2.      | Visualization of Band-to-band Tunnelling.                             |         | 13   |

| 2.3.      | Tunnelling under application of electric field.                       |         | 15   |

| 2.4.      | Comparison of the tunnelling models available in device simulator. 19 |         | . 19 |

| 2.5.      | Comparison between different tunnelling models support                | ted     |      |

|           | by the simulators.                                                    |         | 21   |

|           | Chapter-3                                                             |         |      |

| 3.1.      | Comparison between basic MOSFET and TFET Structure.                   |         | 24   |

| 3.2.      | Energy Band Diagram of n-TFET.                                        |         | 25   |

| 3.3.      | Visualization of Line and Point Tunnelling.                           |         | 26   |

| 3.4.      | Channel Pinning in N-TFET.                                            |         | 27   |

| 3.5.      | Energy Band Diagram along the surface of n-TFET during                |         |      |

|           | ambipolar conduction at positive drain bias.                          |         | 27   |

| 3.6.      | Transfer Characteristic of n-TFET, showing all the import             | ant     |      |

|           | regions of operation.                                                 |         | 28   |

|           | Chapter-4                                                             |         |      |

| 4.1.      | Broken Gate TFET Structure.                                           |         | 46   |

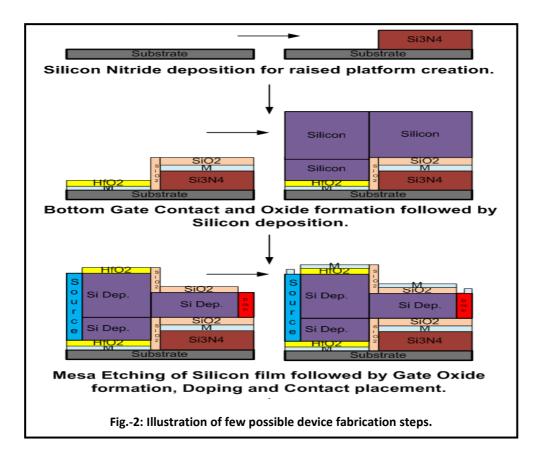

| 4.2.  | Illustration of few possible device fabrication steps.                  | 47 |

|-------|-------------------------------------------------------------------------|----|

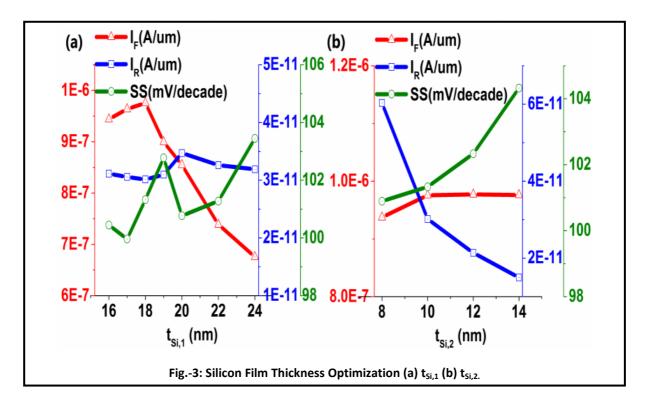

| 4.3.  | Silicon Film Thickness Optimization (a) $t_{Si,1}$ (b) $t_{Si,2}$ .     | 48 |

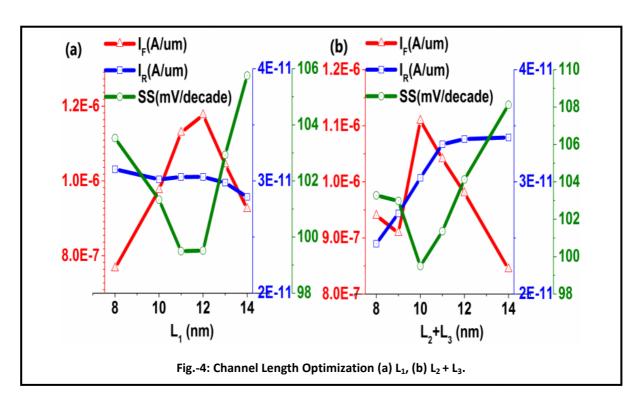

| 4.4.  | Channel Length Optimization (a) $L_1$ , (b) $L_2 + L_3$ .               | 48 |

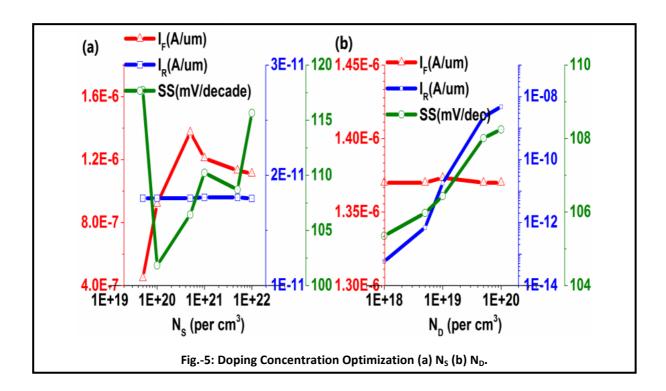

| 4.5.  | Doping Concentration Optimization (a) $N_S$ (b) $N_D$ .                 | 49 |

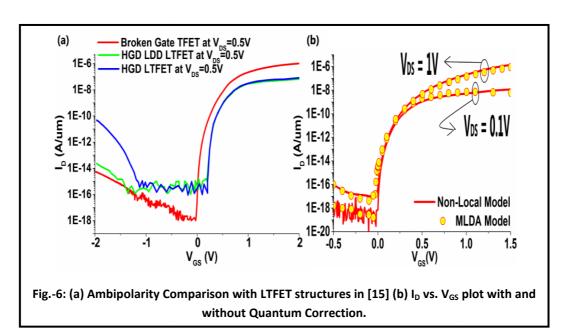

| 4.6.  | (a) Ambipolarity Comparison with LTFET structures                       |    |

|       | (b) $I_D$ vs. $V_{GS}$ plot with and without Quantum Correction.        | 50 |

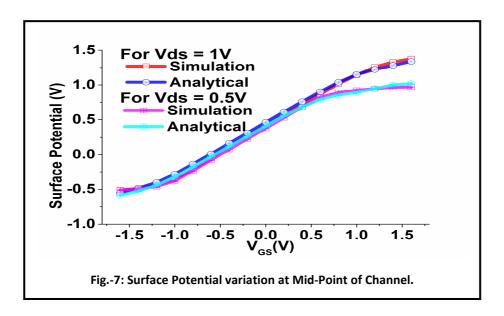

| 4.7.  | Surface Potential variation at Mid-Point of Channel.                    | 55 |

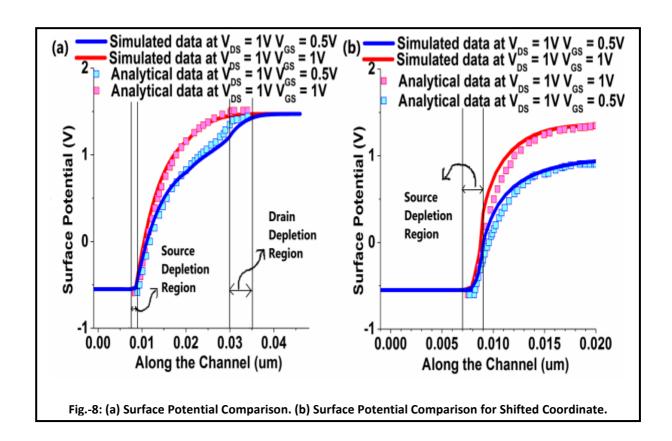

| 4.8.  | (a) Surface Potential Comparison. (b) Surface Potential                 |    |

|       | Comparison for Shifted Coordinate.                                      | 57 |

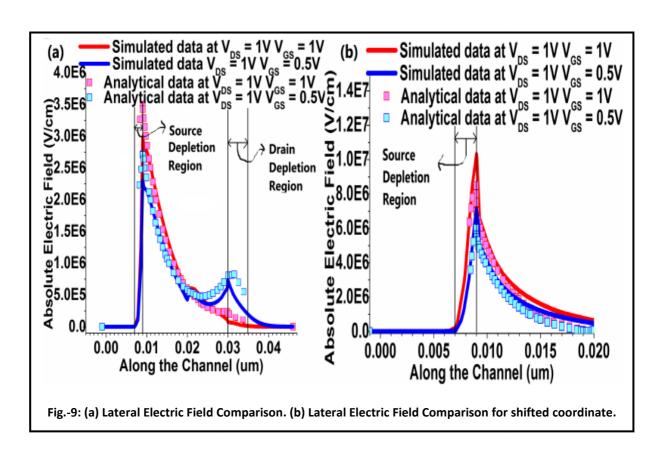

| 4.9.  | (a) Lateral Electric Field Comparison. (b) Lateral                      |    |

|       | Electric Field Comparison for shifted coordinate.                       | 57 |

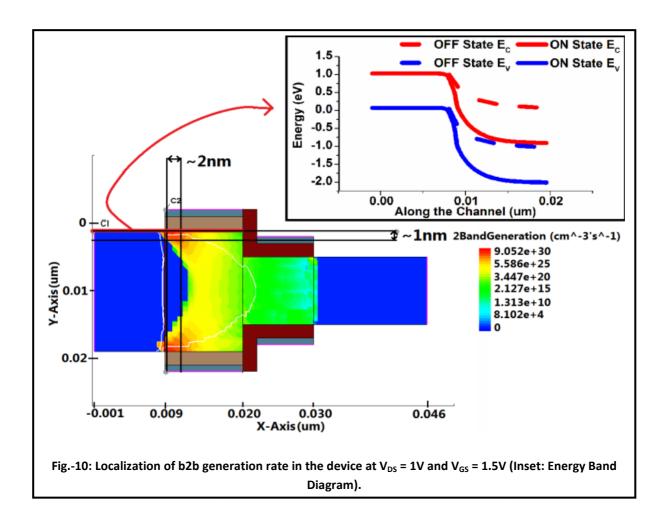

| 4.10. | Localization of b2b generation rate in the device                       |    |

|       | at $V_{DS}$ = 1V and $V_{GS}$ = 1.5V (Inset: Energy Band Diagram).      | 60 |

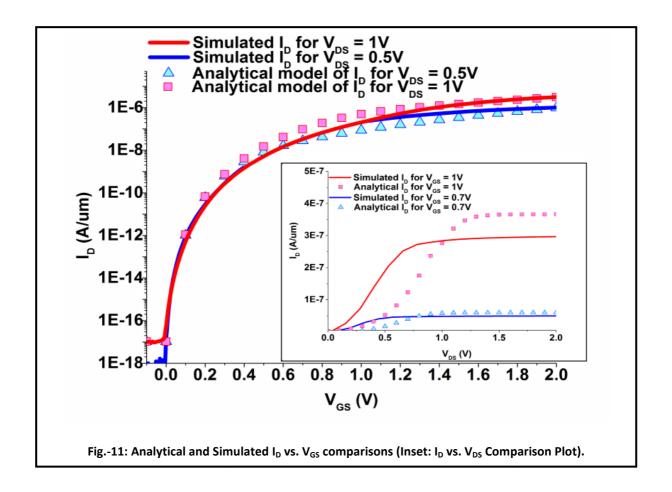

| 4.11. | Analytical and Simulated $I_{\text{D}}$ vs. $V_{\text{GS}}$ comparisons |    |

|       | (Inset: $I_D$ vs. $V_{DS}$ Comparison Plot).                            | 61 |

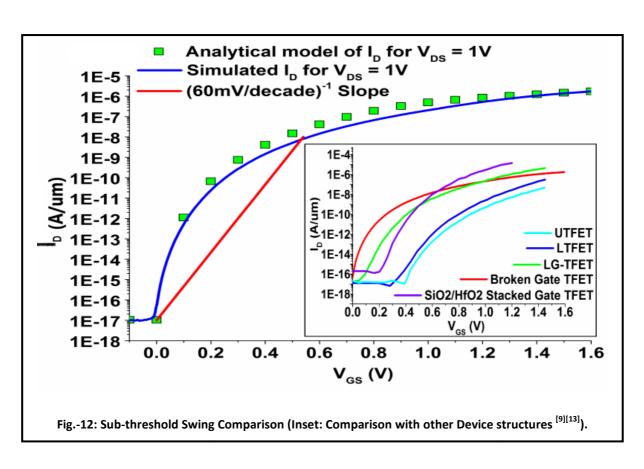

| 4.12. | Sub-threshold Swing Comparison (Inset: Comparison                       |    |

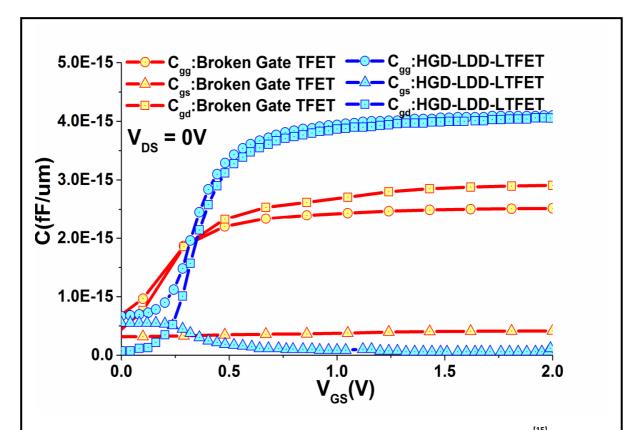

|       | with other Device structures).                                          | 61 |

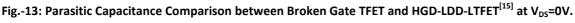

| 4.13. | Parasitic Capacitance Comparison between Broken                         |    |

|       | Gate TFET and HGD-LDD-LTFET at $V_{DS}$ =0V.                            | 63 |

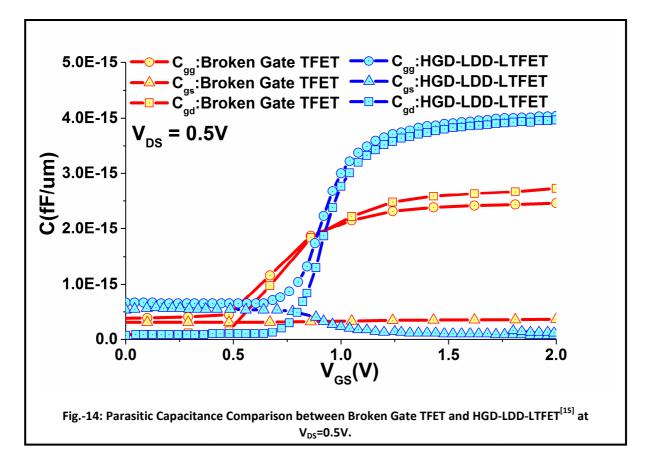

| 4.14. | Parasitic Capacitance Comparison between Broken                         |    |

|       | Gate TFET and HGD-LDD-LTFET at $V_{DS}$ =0.5V.                          | 63 |

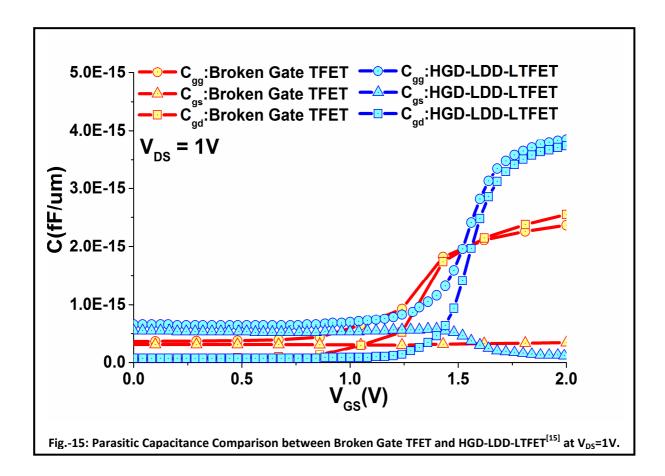

| 4.15. | Parasitic Capacitance Comparison between Broken                         |    |

|       | Gate TEFT and HGD-LDD-LTEFT at Vpc=1V                                   | 64 |

### **ABBREVIATIONS**

#### **Chapter-1**

SS: Sub-threshold Swing.

#### **Chapter-2**

**S.E.:** Schrödinger's Equation.

**TCAD:** Technology Computer Aided Design.

**T.I.S.E.:** Time Independent Schrödinger's Equation.

WKB: Wentzel, Kramers and Brillouin.

#### **Chapter-3**

ALD: Atomic Layer Deposition.

**CNT**: Carbon Nanotube.

**DIBT:** Drain Induced Barrier Tunnelling.

**DMG DGTFET:** Dual Metal Gate Double Gate TFET.

**GAA:** Gate All Around.

**HetJ:** Hetero-junction.

**HfO<sub>2</sub>:** Hafnium Dioxide.

**HGD:** Hetero Gate Dielectric.

**HomJ:** Homo-junction.

**LDD:** Lightly Doped Drain.

**LGTFET:** L-Shaped Gate TFET.

**LTFET:** L-Shaped TFET.

MIT: Metal-Insulator Transition.

NW: Nano Wire.

**PC-TFET:** Phase Change TFET.

**P(VDF-TrFe):** Poly-Vinylidene Fluoride Tri-Fluoro Ethylene.

**SiO<sub>2</sub>:** Silicon Dioxide.

**SMG DGTFET:** Single Metal Gate Double Gate TFET.

**TFET:** Tunnel Field Effect Transistor.

**TM DGTFET:** Triple Metal Double Gate TFET.

**UTFET:** U-Channel TFET.

**VaO<sub>2</sub>:** Vanadium Dioxide.

#### **Chapter-4**

**MLDA:** Modified Local-Density Approximation.

**SCE:** Short Channel Effect.

**SOI:** Silicon on Insulator.

#### **Chapter-5**

**HDL:** Hardware Description Language.

### **ABSTRACT**

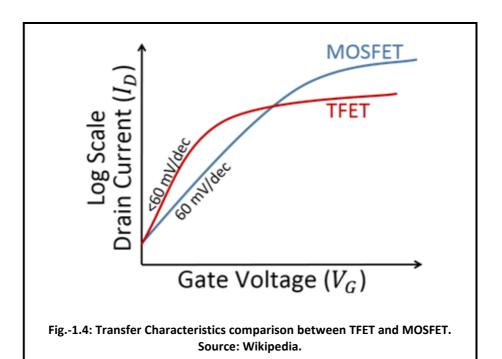

At present the MOSFET technology has almost bent the knee in front of the aggressive scaling, which is required in the electronics industry to be able to follow the Moore's law and integrate more and more functionality in ICs, without increasing the power consumption. The Tunnel Field Effect Transistors (TFETs) have gained much attention as the potential successor to the MOSFETs, due to its steeper sub-threshold swing than the MOSFETs (whose sub-threshold swing is limited to 60mV/decade) and also due to its similarity in construction. A plethora of TFET designs have been proposed earlier in the literature, for solving some of the disadvantages associated with the TFETs. We have also tried to suggest a renovated TFET structure, aimed towards low power applications.

In this work, we have emphasized on optimisation of device parameters and analytical modelling of the proposed Broken Gate TFET structure. We have also obtained the device parasitic capacitances through AC simulation. The TFET structure in this work is based on Silicon, as it would be easy to physically implement, due to availability of the already matured silicon based fabrication techniques.

The electrical performance of the proposed structure has been compared with that of other relevant and similar TFET structures which exist in the literature. The device showed significant reduction in ambipolar conduction, improvement in ON current and commendable sub-threshold swing at a short channel length of 21nm.

The work begins with a brief historical view of the evolution of electronic computing, followed by the discussion on the quantum mechanical tunnelling theory, along with its implementation on commercially available device simulators.

The obtained results establish the efficacy of the present structure, which are validated by simulation. As the device has extremely low leakages, faster ON-OFF transition and low parasitic capacitances, it can be implemented in low-power and high-speed electronic applications.

## Chapter-1: Introduction

- 1.1. A Dive into the History of Electronic Computing

- 1.2. The Tale of the Almighty MOSFET.

- 1.3. Nothing Lasts Forever: The Problems with MOSFET Scaling.

- 1.4. The Motivation.

- 1.5. Organisation of the Thesis.

References.

## 1.1 $\mathscr{Q}$ Dive into the History of Electronic Computing:

It was the year 1958, when Jack Kilby designed the first Integrated Circuit (IC) [1], as a newly employed engineer at Texas Instrument. After about six months of Jack Kilby's first Integrated Circuit design, Robert Noyce at Fairchild Semiconductor developed his own idea of an integrated circuit that solved many shortcomings of the Kilby's design. Robert Noyce designed the IC using Silicon, unlike Jack Kilby's chip which was made of Germanium. Robert Noyce credited Kurt Lehovec of Sprague Electric for the principle of p–n junction isolation, which was a key concept in the improvement of the IC design [1]. This isolation technique allowed each transistor to operate without any interference to and from the neighbouring transistor, despite being on the same silicon chip.

There is a difference in opinion on whom to be exactly credited for invention of the IC. In the 1960s, four people: Kilby, Lehovec, Noyce and Hoerni, were being recognised by the American press. But by the 1970s the list was curtailed to Kilby and Noyce only. In the year 2000 Jack Kilby was awarded the Nobel Prize in Physics "for his part in the invention of the integrated circuit". [1] In the 2000s, historians Leslie Berlin, Bo Lojek and Arjun Saxena has fallen back to the idea of multiple Integrated Circuit inventors and revised Jack Kilby's Contribution.

After a few years of the invention of Integrated circuit, i.e., in the late sixties, designers were trying to integrate all the components of a central processing unit (CPU)

in a handful of chips and were successful to a certain extent. Ted Hoff and Stanley Mazor, assisted by Masatoshi Shima and Federico Faggin (with his 1968 milestone achievement of designing Fairchild Child's first silicon gate IC, 3708 [3]) designed Intel's first microprocessor, 4004, which had almost all the components of a central processing unit integrated into it, except for the memories, in the year 1971 [4].

The commercialization of microprocessor ICs, led to the computer revolution which changed the future of mankind. The ripples of this major scientific achievement, the commercialization of micro-computers, manifested itself as a huge wave and washed humanity to the shores of the Information age. It is a long way from Charles Babbage's mechanical computer "The Difference Engine" to the Vacuum tube based computers like the Colossus, ENIAC and the commercially available IBM 650, etc., to transistorised ones like Harwell CADET, IBM 604 calculator, etc., and finally to integrated circuit based computers, we see in our everyday lives.

At present, microprocessors and microcontrollers have become an indispensible part of our life. Almost in all everyday items, starting from refrigerators, microwaves, modern toasters, washing machines, sewing machines, to smart-phones and high end digital cameras, etc., electronic computation is omnipresent [12]-[14]. With the gain in traction of Internet of things (IOT) and currently, the Internet of everything (IOE), integration of computers in our daily lives is inevitable.

## 1.2 The Tale of the Almighty MOSFET:

The Metal Oxide Field Effect Transistor abbreviated as MOSFET or MOS-FET or MOS FET, was conceptualized by Julius Edgar Lilienfeld in 1925. Dawon Kahng and Martin M.

(John) Atalla invented the first MOSFET at Bell laboratory in 1959, as a variation on the patented FET design [5].

As the name suggests, the MOSFET belongs to the category of Field Effect Transistors, like JFETs and unlike BJTs. The main advantages of MOSFETs are based on the facts that its fabrication and integration is simple and it requires negligible drive current at the gate for controlling the load current.

The use of "metal" in the name of MOSFET is not at all justified considering the current technology. The gate is formed using Polycrystalline Silicon (and not metal) due to the ease and accuracy of fabrication, because of its endurance to high temperatures. Also, different high-k dielectric materials are being used as the oxide instead of the more common Silicon Dioxide ( $SiO_2$ ) [5].

The MOSFET is prevalently used in the Digital circuit domain [5]. Almost all of the digital appliances that we use are primarily based on MOSFET. The MOSFET can be fabricated using n or p-type substrate, leading to p-channel and n-channel MOSFETs respectively. The devices thus formed, are complementary in nature and can be used in pairs to implement different Boolean-logic circuits. These circuits are collectively called as the Complementary MOSFET circuits or CMOS circuits [5], which are the work-horse of the industry to this day. Due to amazing scaling property of the MOSFET, unlike other transistors, the number of MOSFETs in a digital IC has reached billion [5].

The relentless shrinking in the size of the MOSFETs is only possible due to the advancement in the Silicon-CMOS fabrication technology. Only a decade or two back, the MOSFET channel lengths were in order of micrometers and now it is nearing a few nanometres.

The advantages of having a smaller device are many fold. The reduced device dimension means more number of transistors in a given silicon chip area, which directly translates to more functionality per chip, thus compact appliances [11]. Also, since the cost of fabrication and processing per silicon chip is almost constant, the overall price for a more functionally powerful device is reduced, and the history of prices on consumer electronics bears the proof to this statement. Smaller devices, especially MOSFETs tend to switch faster than it larger channel counterparts. This is because; the main dimensions that are scaled are channel length, channel width, and oxide thickness. When these dimensions are scaled down by an equal factor, the overall channel resistance of the device is not changed, but the gate capacitance is curtailed by a factor,

hence lower time delays and faster switching speeds. Thus scaling has led to faster devices [11].

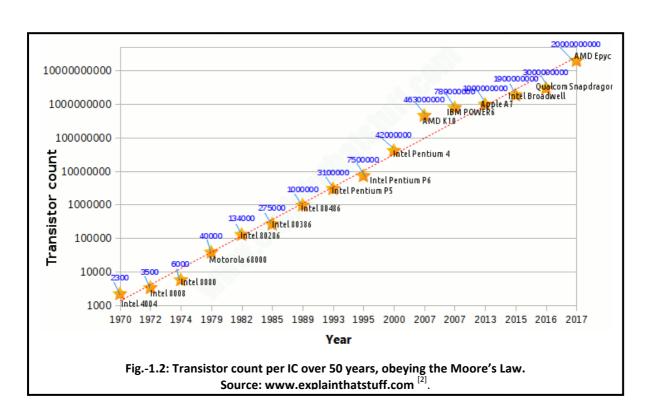

The aforementioned trend of increasing number of transistors per IC was observed earlier. This trend is popularly known as the Moore's Law. This law predicts that the number of transistors in an Integrated Circuit doubles every eighteen months (or two years as considered originally) [6], [7]. This observation was mentioned in a 1965 paper by Gordon E. Moore, who is also the co-founder of INTEL and Fairchild Semiconductor.

## 1.3 Nothing Lasts Forever: The Problems with MOSFET Scaling:

The famous Moore's have been very successful in predicting the exponential increase in the number of transistor in IC per unit area of silicon, thanks to excellent scalability of MOSFETs [11]. But like many things this might not last forever. The channel length reduction is soon to reach its limit and beyond which we might not be able to reduce the MOSFET's dimensions without the penalties for such reductions weighing out the advantages. Also, it would be unwise, not to mentions the optimistic cries in the electronic device community for "*More than Moore*" [9], [15], [16], [20] approach towards the

future of electronics. Hence, at the end of the day the fact that "nothing lasts forever" might turn out to be good news. We might get more than we bargained for with this new found optimism and zeal, and off-course with hard work, but only future will tell us. Thus, it should be our mission to find alternate devices that can replace MOSFET, just like it replaced it forerunners (BJTs, Vacuum tubes, relays, etc). Before we start looking for alternatives, it is only logical to know about the shortcomings of the MOSFET, which bore the brunt of the electronic industry for so long.

The problems associated with aggressive scaling of MOSFETs [8] can be described briefly as follows:

- 1. The fabrication of short channel length MOSFETs reliably have always been a problem. But in recent years with the help of Atomic Layer Deposition (ALD) technique, MOSFETs with channel lengths lower than 10s of nm have been fabricated.

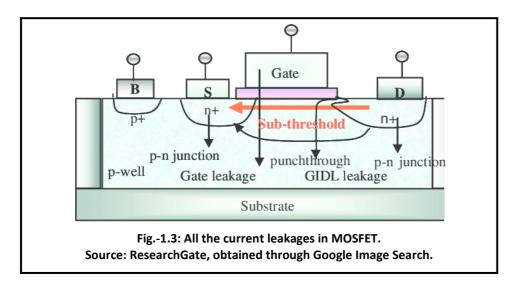

- 2. If the channel length goes down below tens of nanometre, the carriers can just directly tunnel between source and the drain, thus increasing the  $I_{OFF}$  current through leakage.

- 3. As the device dimensions keep on decreasing, the voltages have to be scaled accordingly to reduce the leakage and to reduce the power consumption, but after a while the voltage scaling might not be possible due to compatibility issues with the peripherals and increased delays associated with lower supply voltages.

- 4. The limited voltage scaling options lead to increased power dissipation per transistor in an IC.

- 5. Smaller devices are harder to fabricate with consistency and the variability of device performance increases; hence the overall performance of the IC becomes unpredictable, with reliability problems.

- 6. As, we know, the drain current of MOSFET is dependent on the overdrive voltage (V<sub>DS</sub>-V<sub>T</sub>), the threshold voltage needs to be reduced along with the supply voltage for better current drive.

- 7. The increase in overdrive voltage (through  $V_T$  reduction) not only increases the current drive but also increases the leakage current, increasing the OFF state current exponentially.

- 8. This exponential increase in OFF state current is due to the fact that the subthreshold swing (SS) of the MOSFET is not scalable, and has a fixed lower limit, i.e., 60mV/decade at room temperature.

- 9. Hence, by reducing the power supply voltage and keeping the overdrive constant, it is observed that the leakage increases to unacceptable amounts. Thus, making the option of achieving lower sub-threshold swings a necessity, which as we know is impossible for MOSFET.

## 1.4 The Motivation:

In a MOSFET, the sub-threshold swing (SS) is limited to a lower value because of the fundamental nature through which the carriers travel through the channel. The current-flow involves the thermionic injection of electrons (for n-channel device), over the source-channel energy barrier. The thermal dependence sets a fundamental limit to the slope of the OFF to ON transition and vice-versa. The sub-threshold swing, SS which determines the gate voltage required to change the drain current by an order of 10 (decade) can be written as [10]:  $SS = \frac{dV_G}{d\Psi_S} \frac{d\Psi_S}{d(\log I_D)} \approx (1 + \frac{C_d}{C_{ox}} (\ln 10) \frac{kT}{q})$  (1.1)

Where,  $a = \frac{dV_G}{d\Psi_S}$  is the transistor body factor and  $b = \frac{d\Psi_S}{d(\log I_D)}$  is the factor that relates surface potential  $\Psi_S$  with the drain current  $I_D$ . The  $C_d$  and  $C_{ox}$  are depletion region and oxide capacitances respectively, while 'k' is boltzman's constant, 'q' is magnitude of electronic charge and 'T' is the temperature in Kelvin.

Now, in the limiting case:

$$SS = (\ln 10) \frac{kT}{q} \approx 60 \text{mV} / \text{decade} @ 300 K$$

(1.2)

The above limit can only be reduced by using a physical phenomenon other than thermionic injection for carrier conduction. The solution thus can be broadly classified into two sections, depending upon the 'a' and 'b' factors mentioned in eqn. (1.1).

- i. The body factor "a" can be made less than unity by making the gate active in nature, unlike the passive gates employed in MOSFET. The active gate devices such as Negative Capacitance FET (NC-FET) [17], NEM-FET (Nano-Electromechanical FETs) [18] etc can achieve lower SS.

- ii. The factor "b" can be made less than (kT/q)ln10, by using different carrier injection mechanism in the channel, like band-to-band (B2B) tunnelling mechanism in Tunnel Field Effect Transistors (TFETs), Impact Ionization in Impact Ionization FETs (IFETs) [19]. Such devices are also capable of achieving less than60mV/decade SS, unlike the MOSFETs.

In this thesis we have concentrated on the Band-to-band tunnelling device, the TFET. This device uses the shortcoming of MOSFET, the leakage due to tunnelling to its advantage. The drain current in TFET is based on tunnelling phenomenon between the source and channel junction. The device easily achieves sub-threshold swings lower than 60mV/decade and have similar construction/structures to that of MOSFET. The similarity in construction ensures that the existing fabrication techniques, which took many years to develop, can be easily translated for fabricating TFET based ICs.

The Tunnel Filed Effect Transistors (TFET) does not suffer from the severity of short channel effects, as in MOSFETs, due to their fundamental difference in operating principles. The TFETs show extremely low OFF state currents when compared to MOSFETs, but at the cost of reduced ON currents (especially in case of Silicon TFETs) [10]. At lower drive voltages, and lower current operations, TFET show faster ON-OFF transitions and even higher ON currents than the MOSFETs as in Fig.-1.4, but if higher load currents are required, the MOSFET are clearly the device of choice.

The present demand for lower power and compact electronic devices is not going to disappear soon. The limitations in power storage of capacity of batteries and the desire of the consumers to stay connected to the network, has clearly marked the beginning of ultra-low power device design. In this scenario, the TFETs can prove to be the worthy successor to MOSFETs, especially in ultra-low power digital applications.

## 1.5 Organisation of the Thesis:

This thesis has been divided into five chapters. The chapter contents can be described in brief, as follows:

- 1. Chapter-1, discusses about the evolution of electronic computing, followed by problems associated with MOSFET scaling and why TFETs might be able to succeed MOSFET in the future generation of electronics.

- 2. In chapter-2, the discussion is concentrated on the quantum mechanical tunnelling concept, its models and finally the model's implementation in commercially available simulators for device simulation.

- 3. Chapter-3 begins with the discussion on the basic construction of TFET, followed by its working principle and a brief literature study on various TFET structures and designs.

- 4. In chapter-4, a Broken-Gate TFET structure has been proposed. The choice of such device structure is discussed and the device parameters are optimized. Analytical model for the electrical characteristics of the device is obtained, which is validated against Sentaurus TCAD simulation, followed by comparison with other similar structures available in literature.

- 5. Finally, the concluding remarks and the scope for future work are presented in chapter-5.

#### **References:**

- 1. "Integrated circuit," *Wikipedia*, 18-Apr-2019. [Online]. Available: https://en.wikipedia.org/wiki/Integrated\_circuit. [Accessed: 29-Apr-2019].

- 2. "How do integrated circuits work?," *Explain that Stuff*, 09-Jan-2019. [Online]. Available: https://www.explainthatstuff.com/integratedcircuits.html. [Accessed: 29-Apr-2019].

- 3. "1968: Silicon Gate Technology Developed for ICs," *Computer History Museum*. [Online]. Available: https://www.computerhistory.org/siliconengine/silicon-gate-technology-developed-for-ics/. [Accessed: 29-Apr-2019].

- 4. "1971: Microprocessor Integrates CPU Function onto a Single Chip," *Computer History Museum*. [Online]. Available: https://www.computerhistory.org/siliconengine/microprocessor-integrates-cpufunction-onto-a-single-chip/. [Accessed: 29-Apr-2019].

- 5. "MOSFET," *Wikipedia*, 27-Apr-2019. [Online]. Available: https://en.wikipedia.org/wiki/MOSFET. [Accessed: 29-Apr-2019].

- 6. "Moore's law," *Wikipedia*, 09-Apr-2019. [Online]. Available: https://en.wikipedia.org/wiki/Moore's\_law. [Accessed: 29-Apr-2019].

- 7. G. E. Moore, "Cramming more components onto integrated circuits," *Electronics*, vol. 38, no. 114, 1965.

- 8. S.-M. Kang, Y. Leblebici, and C. Kim, *CMOS digital integrated circuits: analysis and design*. New York, NY: McGraw-Hill Education, 2015.

- 9. W. Arden, "'More than Moore' White Paper." [Online]. Available: http://www.itrs2.net/uploads/4/9/7/7/49775221/irc-itrs-mtm-v2\_3.pdf. [Accessed: 30-Apr-2019].

- 10. M. J. Kumar, R. Vishnoi, and P. Pandey, *Tunnel field-effect transistors (TFET): modelling and simulations*. Hoboken: Wiley, 2016.

- 11. R. Dennard, F. Gaensslen, V. Rideout, E. Bassous, and A. LeBlanc, "Design of ionimplanted MOSFET's with very small physical dimensions," *IEEE J. Solid-State Circuits*, vol. 9, pp. 256–268, Oct. 1974.

- 12. J. Bag, R. R. Sahoo, P. K. Dutta, and S. K. Sarkar, "Design and VLSI implementation of power efficient processor for object localisation in large WSN," *International*

- *Journal of High Performance Systems Architecture*, vol. 4, no. 4, p. 204, 2013, doi: http://10.1504/ijhpsa.2013.058982.

- 13. J. Bag and S. K. Sarkar, "Development and VLSI implementation of a data security scheme for RFID system using programmable cellular automata," *International Journal of Radio Frequency Identification Technology and Applications*, vol. 4, no. 2, p. 197, 2013, doi: http://10.1504/ijrfita.2013.054687.

- 14. J. Bag and S. K. Sarkar, "VLSI Implementation of a Key Distribution Server Based Data Security Scheme for RFID System," 2015 Fifth International Conference on Advanced Computing & Communication Technologies, 2015, doi: http://10.1109/acct.2015.55.

- 15. A. Ghosh, A. Basu, T. S. Das, V. H. Mankar, D. Samanta, and S. K. Sarkar, "Single Spin Logic Realization of a Robust Spatial Domain Image Watermarking," *Advanced Science Letters*, vol. 2, no. 1, pp. 86–96, 2009, doi: http://10.1166/asl.2009.1040.

- 16. A. Sarkar, A. Ghosh, S. Halim, and S. Roy, "Spintronics device based low power RFID system: Design and implementation," 2016 International Conference on Microelectronics, Computing and Communications (MicroCom), 2016, doi: http://10.1109/microcom.2016.7522467.

- 17. X. Zhang, X. Gong, and G. Liang, "Analysis on Performance of Ferroelectric NC-FETs Based on Real-Space Gibbs-Free Energy With Atomic Channel Structure," *IEEE Transactions on Electron Devices*, vol. 66, no. 2, pp. 1100–1106, 2019, doi: http://10.1109/ted.2018.2888930.

- 18. D. Grogg, A. Lovera, and A. M. Ionescu, "Nano-Electro-Mechanical vibrating body FET resonator for high frequency integrated oscillators," *68th Device Research Conference*, 2010, doi: http://10.1109/drc.2010.5551898.

- 19. M. Kim, Y. Jeon, Y. Kim, and S. Kim, "Impact-Ionization and Tunneling FET Characteristics of Dual-Functional Devices With Partially Covered Intrinsic Regions," *IEEE Transactions on Nanotechnology*, vol. 14, no. 4, pp. 633–637, 2015, doi: http://10.1109/tnano.2015.2427453.

- 20. A. Ghosh, A. Jain, N. B. Singh, and S. K. Sarkar, "Stability aspects of single electron threshold logic based 4 bit carry look ahead adder," *Proceedings of the 2015 Third International Conference on Computer, Communication, Control and Information Technology (C3IT)*, 2015, doi: http://10.1109/c3it.2015.7060138.

## **Chapter-2: Theory of Tunnelling**

- 2.1. What is Quantum Mechanical Tunnelling?

- 2.2. A Brief introduction to Band-to-Band Tunneling.

- 2.3. Band-to-Band Tunnelling Models.

- 2.4. Kane's Local Tunnelling Model.

- 2.5. A Brief Overview of the Simulator used.

References.

\_\_\_\_\_

## 2.1 What is Quantum Mechanical Tunnelling?

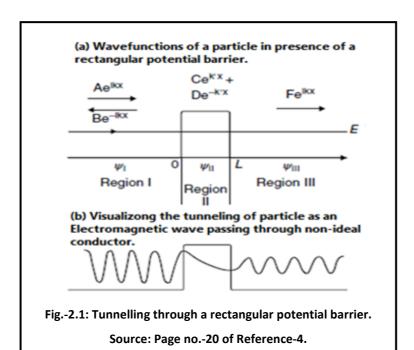

The phenomenon of Band to Band tunnelling is primarily responsible for the current flow in TFETs [7]-[9]. But before we jump in into band-to-band tunnelling, we should get an idea about quantum mechanical tunnelling in general. Unlike in classical mechanics, quantum mechanical particles can tunnel through an energy barrier, even if the energy of the particle is lower than the energy required for overcoming it [1]. The tunnelling phenomenon through a rectangular potential barrier can be described using probability of finding the particle before, inside and after the energy/ potential barrier and can visualized, as in Fig.-2.1.

The probability of a particle tunnelling through a rectangular potential barrier is fairly easy to obtain. By solving the 1-D time independent Schrödinger's equation [10], with the potential term varying as per the region concerned, and using the continuity of wavefunction across the regions, the wave-functions ( $\Psi_i$ ) can be obtained. The tunnelling probability can be obtained as the ration of the magnitude of the wave-functions after the potential barrier and before it, in the direction of particle's trajectory.

The 1-D time independent Schrödinger's equation in general can be written as [1], [4]:

$$\frac{\hbar^2}{2m} \frac{\partial^2 \Psi_i}{\partial x^2} = (V - E) \Psi_i \tag{2.1}$$

$\partial x^2$  Where, subscript 'i' is for representing regions I, II and III. The potential profiles for each region can be written as:  $V(x) = \begin{cases} 0, x \le 0 \\ V, x \in (0, L) \\ 0, x \ge L \end{cases}$  (2.2)

After solving the 1-D T.I.S.E. (time independent Schrödinger's equation) using the boundary conditions and spatially varying potential profile (rectangular in our case) as in eqn. (2.2), we get the region dependent wave-functions, and finally the tunnelling probability as follows:  $T = \frac{|F|^2}{|A|^2} = \frac{1}{1 + \frac{V^2 \sinh^2 k' L}{4 E G V - E}}$  (2.3)

Where,

$$k' = \sqrt{\frac{2m(V - E)}{\hbar^2}}$$

(2.4)

Similar calculations can be performed for triangular potential barrier.

Now, it should be noted that the solution here became easy because of the simplicity of the barrier, in reality; the potential barriers may or may not be in a regular shape. The results thus obtained can be used for random barriers which can be approximated as regular one.

Another popular way of calculating tunnelling probability for general potential barrier is by using the WKB (Wentzel, Kramers and Brillouin) approximation [1], which is a mathematical approach, where we obtain approximated solutions for certain types of

differential equations. The tunnelling probability obtained from WKB approximation is  $|E|^2$

as follows:

$$T = \frac{|F|^2}{|A|^2} = e^{-2\gamma}$$

(2.5)

Where,

$$\frac{|F|}{|A|} \approx e^{-\int_{0}^{L} |k'(x)| dx}$$

(2.6)

And

$$\gamma = \int_{0}^{L} \left| \sqrt{\frac{2m(V - E)}{\hbar^2}} \right| dx \tag{2.7}$$

With the help of eqn. (2.5), tunnelling probability of any particle through a general potential profile can be found for any band structure or material.

## $2.2~\mathcal{C}$ Brief Introduction to Band-to-Band Tunnelling:

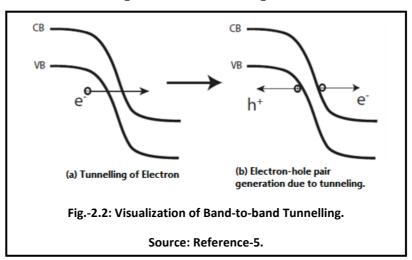

Now, that we have established a basic understanding of how the tunnelling through a general barrier can be predicted, we can concentrate on how the tunnelling is useful in the view of TFETs. In simple words, the band-to-band tunnelling occurs when electrons from the valence band tunnels across the energy band gap to the conduction band. The band-gap is considered as the equivalent to the potential barrier. The band-to-band tunnelling can be shown as in Fig.-2.2. The tunnelling can be direct or indirect in nature.

(a) *Direct Tunnelling:* This occurs in direct band-gap semiconductors, where the maxima of the valence band is aligned with the minima of conduction band at the same 'k' value. The tunnelling phenomenon does not require the help of phonon (or photon depending on the case) or traps to occur. Also, the tunnelling does not cause a change in momentum, especially in the direction perpendicular to the

- direction of tunnelling. This type of tunnelling can be seen in gallium Arsenide (GaAs) and not in Silicon (Si) and Germanium (Ge).

- **(b)** *Indirect Tunnelling:* This is observed in semiconductors like Silicon and Germanium, where the top of the valence band doesn't align with the bottom of the conduction band at the same 'k'. The tunnelling process requires change in momentum, which is achieved by absorbing and releasing phonons (or photons depending on the case).

## 2.3 Band-to-Band Tunnelling Models:

The band-to-band tunnelling models can be broadly classified into two types: i. Non-Local Tunnelling models and ii. Local Tunnelling models.

- (a) Non-local Tunnelling Models: In these models, the Schrödinger's equation (S.E.) is solved with respect to the spatial dependence of the parameters. When external voltage/ bias are applied in semiconductors, the shape of the potential barrier is varied, and the variation might not be simple. Thus, in case of Non-local models the solutions might not always end up in a closed form. The band-structure of the semiconductor must be included with the potential (V(x)) while solving for the Schrödinger's equation. All these spatial complications makes the analytical solution to the S.E. almost impossible, hence these types of model are highly dependent on the Numerical Solutions. Hence, such models are mostly used in simulators for accurate results.

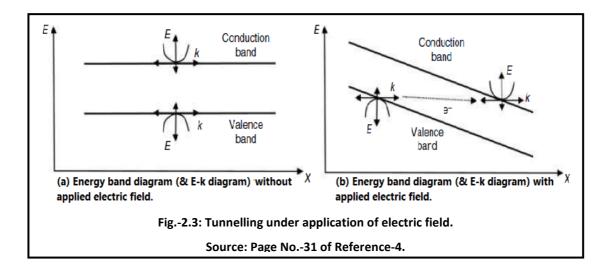

- **(b)** *Local Tunnelling Models:* The band structure in semiconductors is product of the proximity periodic arrangement of the atoms in the crustal lattice. The energy bands can be viewed in E-k diagram with the bands representing allowed energy states in which the electrons can reside. The band gap separates the valence and conduction bands, acting like a potential barrier. It requires a large amount of energy for an electron through tunnel through this energy gap, in equilibrium conditions.

If a strong enough electric field is applied, the band structure/ shape would be modified in such a way that the electrons can tunnel through much easily. The application of electric filed aligns the filled valence bands with empty conduction band states in such a way that the potential barrier is thin enough for the electrons to tunnel through, as in Fig.-2.3. If the tunnelling probability is sufficiently large, we can get an appreciable amount of current flow. While deriving the expressions for the local tunnelling models, one of the most important approximations that we have to consider is that the electric field is constant near the region of tunnelling, which is not always true practically. Hence, the local tunnelling model although can arrive at an analytical or closed form expression, the current predicted by such model can vary in accuracy, depending on how cautiously the model is applied to the device under consideration <sup>[5]</sup>. In these models, the generation and recombination of carriers are not considered, hence the entire tunnelling current is assumed to be dependent on the rate of tunnelling or the tunnelling probability.

## 2.4 Kane's Local Tunnelling Model:

One of the most important tunnelling models, and probably the most widely used model is Kane's tunnelling model [11]. The popularity of this model is probably due to its simplicity, although the derivation might not be simple. No TFET report is complete

without a discussion on this model. In the upcoming chapter, where we have obtained an analytical expression for our proposed device structure, this model has been used.

The model was originally proposed by *E.O. Kane* in the year **1959** [2], [3]. Since the model is local in nature, it deals in E-k diagram rather than spatial coordinates. The derivative terms and the potential profile in the 1-D T.I.S.E. are spatial in nature, hence cannot be directly used for the derivation. The crystal structure in the semiconductor is periodic and the potential distribution is also thus periodic in nature. Hence, the S.E. for such case can be written as follows:

$$-\frac{\hbar^2}{2m}\frac{\partial^2 \Psi_i}{\partial x^2} + V_{per}\Psi = E_n\Psi$$

(2.8)

Where,  $V_{per}$  represents the periodic potential and  $E_n$  represents different energies of the energy bands.

The solution for the eqn. 2.8 is known as Bloch function [1] and can be written as follows:

$$\Psi_{n,k} = e^{ikx} u_{n,k}(x) \tag{2.9}$$

Where,  $u_{n,k}(x)$  is a function with same periodicity as that of the crystal lattice under consideration. The subscript 'n' is for representing the  $n^{th}$  energy band and 'k' the momentum vector for associated wave-function. Finally, a general wave-function for the particle in the crystal can be written as follows:

$$\Psi = \sum a_n(k)\Psi_{n,k} \tag{2.10}$$

Where,  $a_n(k)$  is a complex coefficient. Now, if an external field is applied to the device, the S.E. in eqn. (2.8) can be written as:

$$-\frac{\hbar^2}{2m}\frac{\partial^2 \Psi_i}{\partial x^2} + (V_{per} - qE_{ext}x)\Psi = E\Psi$$

(2.11)

To convert eqn. (2.11) into a function of 'k' instead of spatial coordinate, we need to replace the wave-functions by the Bloch's general wave-function, as in eqn. (2.10). The new form of S.E. thus obtained is a linear combination of Bloch functions, which is as follows:  $\sum a_n(k)(\frac{\hbar^2}{2m}\frac{\partial^2\Psi_{n,k}}{\partial x^2}+V_{per}\Psi_{n,k})-\sum a_n(k)qE_{ext}x\Psi_{n,k}=\sum a_n(k)E\Psi_{n,k} \tag{2.12}$

If, we compare eqn. (2.12) with eqn. (2.8), we can find the analogy between the bracketed terms in eqn. (2.12) and the energy band term  $E_n$ . Also, it should be noted that in eqn. (2.12), the there are two energy terms,  $E_n$  representing the energy band

energies and E representing the electron energy. The eqn. (2.12) can be written for a single energy, as follows:  $a_n(k)E_n - a_n(k)qE_{ext}x = a_n(k)E$  (2.13)

Eqn. (2.13) still contains 'x', a spatial operator. To completely free the equation from this operator, we introduce an "intra-band operator" ( $i\delta/\delta k$ ) and an "inter-band operator" ( $X_{nn'}(k)$ ) in place of 'x'. The  $X_{nn'}(k)$  operator works on an energy band n and other energy band n'. The new S.E. can thus be written as:

$$[E_n(k) - iqE_{ext} \frac{\partial}{\partial k} - E]a_n(k) - \sum_{n'} qE_{ext} X_{nn'} a_{n'}(k) = 0$$

(2.14)

Eqn. (2.14) represents that the electron's position is dependent on the energy band to which it belongs and also on the interaction of the other energy bands with the current one. The intra-band operator deals with spatial interactions inside the energy band, while the inter-band operator deals with the spatial interaction encompassing other energy bands, i.e. it bridges the interaction of electron with multiple energy bands and this soon disappears if the external electric field is removed.

The equation in (2.14), is very tough to solve as it is, hence, we only consider the eigenfunctions of the equation, ignoring the  $\sum_{n'} qE_{ext}X_{nn'}a_{n'}(k)$  part, as an approximation. This approximation has the consequence of including only the intra-band effects, ignoring the contributions of other bands. After obtaining the eigen-functions in above mentioned manner, they are coupled with inter-band operator  $X_{nn'}$ , to obtain the tunnelling rates between bands n and n'.

The Kane's model can now be derived for any semiconductor by modelling the periodic potential  $V_{per}$  as two interacting bands via k-p perturbation. The band-to-band generation rate thus obtained from the above procedure is as follows:

$$G_{b2b} = \frac{E_{ext}^{2} m_{r}^{1/2}}{18\pi\hbar^{2} E_{G}^{1/2}} \exp\left\{\frac{-\pi m_{r}^{1/2} E_{G}^{3/2}}{2\hbar |E_{ext}|}\right\} = A \frac{E_{ext}^{2}}{E_{G}^{1/2}} \exp\left\{-B \frac{E_{G}^{3/2}}{|E_{ext}|}\right\}$$

(2.15)

Where, " $m_{r''}$  represents the reduced mass of the charge carrier. The equation presented here is only applicable for direct tunnelling. To incorporate the indirect tunnelling, we should consider the change in momentum associated with it. The generation rate for indirect tunnelling, incorporating the momentum change (i.e. phonon interactions) can be written as follows:

$$G_{b2b} = \frac{E_{ext}^{-5/2} m_r^{1/2}}{18\pi\hbar^2 E_G^{-1/2}} \exp\left\{\frac{-\pi m_r^{-1/2} E_G^{-3/2}}{2\hbar |E_{ext}|}\right\} = A \frac{E_{ext}^{-5/2}}{E_G^{-1/2}} \exp\left\{-B \frac{E_G^{-3/2}}{|E_{ext}|}\right\}$$

(2.16)

Thus, we can observe that the model can be used for either direct or indirect tunnelling by just changing the power to which the externally applied electric field is raised, i.e. 2 for direct tunnelling and 2.5 for indirect tunnelling.

We had begun this section by stating, how popular the Kane's model is, but this model fails to include few important aspects related to the tunnelling phenomenon, such as effects of traps and density of states. Hence, many other tunnelling models (e.g. Hurkx Model, Schenk's Model, etc) have been developed to incorporate what Kane's model has failed to but it has still remained the basis on which these new models are developed.

## 2.5 @ Brief Overview of the Simulator Used:

For our device simulations, in the upcoming chapter, we have used Synopsys Sentaurus TCAD. Here we will briefly discuss about the models that were used during simulations. Although many models were included during simulation of the device, we will concentrate on the tunnelling models. The details of other models such as electron mobility models, quantum correction models, etc can be easily obtained from the simulator manual [6]. Also, it should be noted that, another similar device simulator is commercially available from Silvaco, the ATLAS TCAD.

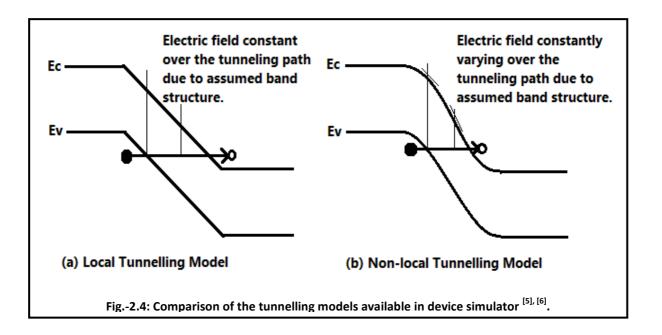

The simulators available, models the band-to-band tunnelling under the case of generation-recombination. The device simulator considers the device as an interconnection/ mesh of nodes and meshes. During the simulation for TFET, the simulator calculates tunnelling rates at each node, using Kane's model or some variation of it. The band-structure at the specific mesh point under consideration is analysed and taken into account. The different models in simulator mainly differ from each by how they treat the band structures and this adversely affects the TFETs predicted ON current. As discussed before, the models available in the simulators can also be classified into local and non-local models.

The local models, as can be seen form Fig.-2.4 (a), approximates the band diagram to be triangular in nature, making the electric field constant at each point in the tunnelling path, as it is the gradient of the energy band. In reality the electric field in the tunnelling path is not uniform and the non-local model incorporates this non-uniformity by considering the band diagram in more detail without linear approximation, as in Fig.-2.4(b). Also, in case of local models, as discussed as the shortcoming in Kane's model, the simulator considers the electron and hole generation profiles to be same. But in case of non-local model the electrons are considered to be generated at the end of the tunnelling path, while the holes at the beginning of the tunnelling path, as in Fig.-2.2 (right). The Sentaurus TCAD, used for our simulations has the capability to simulate both two dimensional and three dimensional device structures. For two dimensional simulation cases, the width of the device is considered to 1um thick by default, and the simulation is done on one negligibly thin slice of the thickness [6]. The simulator contains many Local and Non-local models; here we will discuss a few models belonging to the two main types, which are related to the simulations presented in this report. For detailed information on all the other models and the models discussed here, the "sdevice" part of the Sentaurus manual [6] must be consulted.

#### 2.5.1: Sentaurus Local Tunnelling Models:

The Sentaurus Simulator supports a basic local tunnelling model based on the Kane's model. The band-to-band generation rate for this model is very similar to the expression in eqn. (2.15) derived using Kane's theory and is represented as follows [6]:

$$G_{b2b} = A_{path} |F|^{p} \exp(-\frac{B_{path}}{E_{G}})$$

(2.17)

The parameter "P" in the above equation can be set to 1, 1.5 and 2. The generation rate is solely dependent on electric field "F", hence the current at zero drain-to-source voltage ( $V_{DS}$ =0V) is non-zero, which is undesirable. The problem of non-zero current is solved in Hurkx model [6], whose generation rate expression is as follows:

$$G_{b2b}^{net} = A_{path} D \left| \frac{F}{1V/cm} \right|^{P} \exp\left(-\frac{B_{path} E_{G}(T)^{3/2}}{E_{G}^{3/2}}\right)$$

(2.18)

Where,

$$D = \frac{n \cdot p - n_{i,eff}^2}{(n + n_{i,eff})(p + n_{i,eff})} (1 - |\alpha|) + \alpha$$

(2.19)

The Hurkx model is useful since, it incorporates the temperature dependence of the energy band gap. Hence, once the model is calibrated at a certain temperature, device currents at other temperatures can be predicted. Not only that, the model can show zero generation rates at zero drain-to-source voltage ( $V_{DS}$ =0V). Schenk's band-to-band model is another similar model to the ones discussed here. Still, the local models consider uniform electric field at the tunnelling path, thus largely over-predicting the tunnelling currents.

#### 2.5.2: Sentaurus Non-Local Tunnelling Model:

The simulator also supports non-local tunnelling model. The application of such model requires construction of non-local meshes in the regions in which the tunnelling is expected to occur. The addition of non-local mesh is little more time consuming and sensitive. Thus for most of the simulations performed in this report, we have used the Dynamic Non-local Tunnelling which does not require construction of these extra meshes. The model dynamically locates the tunnelling path with the help of energy band structure instead of using the pre-constructed non-local meshes. Thus the model can be used for almost any device structure which is not of conventional planar design.

Unlike the local models, this model incorporates both direct and phonon assisted generation of electron and holes, at the end and beginning of the tunnelling path respectively. The model determines the electric field according to the energy band edge profile at each point in the tunnelling path; hence the electric field thus obtained is dynamically changing. One drawback of this model is that it is not fully compatible with AC analysis and most of the Quantum correction models.

The net recombination rates for the model with non-local electric field assume a very large expression, which is available in the simulator's manual. *Under consideration of "uniform electric field" the net recombination rate for non-local model* reduces to:

$$R_{net} = A \left(\frac{F}{F_0}\right)^P \exp\left(-\frac{B}{F}\right) \tag{2.20}$$

The expression is similar to the Kane and Keldysh models which are local in nature. The value of 'P' can be 2 for direct tunnelling (for hetero-structure devices) and 2.5 for phonon-assisted tunnelling, as in Silicon and Germanium devices. The value of  $F_0$  is 1V/cm. Also, the expressions for A and B can be found in the manual, which will be useful for calibration. The default values of 'A' and 'B' are  $4x10^{14}$  cm<sup>-3</sup>s<sup>-1</sup> and  $1.9x10^7$  V/cm respectively <sup>[6]</sup>. The simulator supports up to three non-local tunnelling paths, the default values of 'A' and 'B' for other two paths are zero.

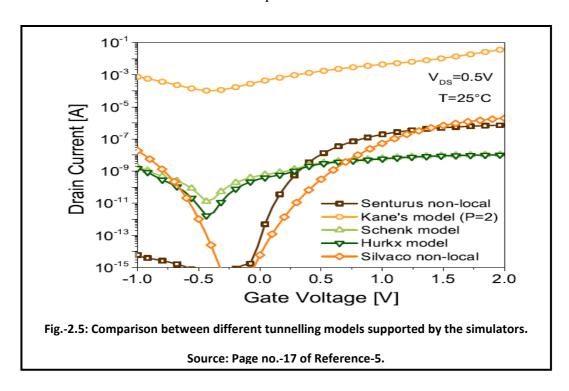

Fig.-2.5 shows the  $I_D$  vs.  $V_{GS}$  plots for a 100nm channel length DG-TFET, with different simulation models available in Sentaurus TCAD and also compares the non-local tunnelling model with ATLAS TCAD. All the simulations performed with default parameters. It should be noted that the SILVACO TCAD always predicts the drain current more generously than the Synopsys TCAD.

#### **References:**

- 1. D. J. Griffiths, *Introduction to Quantum Mechanics*, 2nd edn, Pearson Education, 2005

- 2. E. O. Kane, "Theory of Tunnelling", *Journal of Applied Physics*, vol. 32, no. 83, 1961.

- 3. E. O. Kane, "Zener Tunneling in Semiconductors", *J. Phys. Chem. Solids*, vol. 12, no. 2, pp. 181–188, January 1960.

- 4. M. J. Kumar, R. Vishnoi, and P. Pandey, *Tunnel field-effect transistors (TFET): modelling and simulations.* Hoboken: Wiley, 2016.

- 5. A. Biswas, "Tunnel Field Effect Transistors: from Steep-Slope Electronic Switches to Energy Efficient Logic Applications," *infoscience.epfl.ch.* [Online]. Available: https://infoscience.epfl.ch/record/212724/files/EPFL\_TH6802.pdf. [Accessed: 30-Apr-2019].

- 6. Synopsys, "Sentaurus TCAD user guide Ver: I2014.09".

- 7. N. Bagga, S. Sarkhel, and S. K. Sarkar, "Recent research trends in gate engineered tunnel FET for improved current behavior by subduing the ambipolar effects: A review," *International Conference on Computing, Communication & Automation*, 2015, doi: http://10.1109/ccaa.2015.7148569.

- 8. S. Sarkhel, N. Bagga, and S. K. Sarkar, "Compact 2D modeling and drain current performance analysis of a work function engineered double gate tunnel field effect transistor," *Journal of Computational Electronics*, vol. 15, no. 1, pp. 104–114, 2015, doi: http://10.1007/s10825-015-0772-3.

- 9. T. Kumari, P. Saha, D. K. Dash, and S. K. Sarkar, "Modeling of Dual Gate Material Hetero-dielectric Strained PNPN TFET for Improved ON Current," *Journal of Materials Engineering and Performance*, vol. 27, no. 6, pp. 2747–2753, 2018, doi: http://10.1007/s11665-018-3144-x.

- T. D. Malakar, P. Bhattacharyya, and S. K. Sarkar, "Quantum analytical modelling of threshold voltage for linearly graded alloy material gate recessed S/D SOI MOSFET," 2017 Devices for Integrated Circuit (DevIC), 2017, doi: http://10.1109/devic.2017.8074056.

- 11. N. Bagga and S. K. Sarkar, "An Analytical Model for Tunnel Barrier Modulation in Triple Metal Double Gate TFET," *IEEE Transactions on Electron Devices*, vol. 62, no. 7, pp. 2136–2142, 2015, doi: http://10.1109/ted.2015.2434276.

## Chapter-3: The Tunnel Field Effect Transistor (TFET).

- 3.1. Basic Construction of TFET.

- 3.2. Working Principle of TFET in Brief.

- 3.3. A Brief Literature Review on Various TFET Designs for Performance Enhancement.

References.

## 3.1 Basic Construction of TFET:

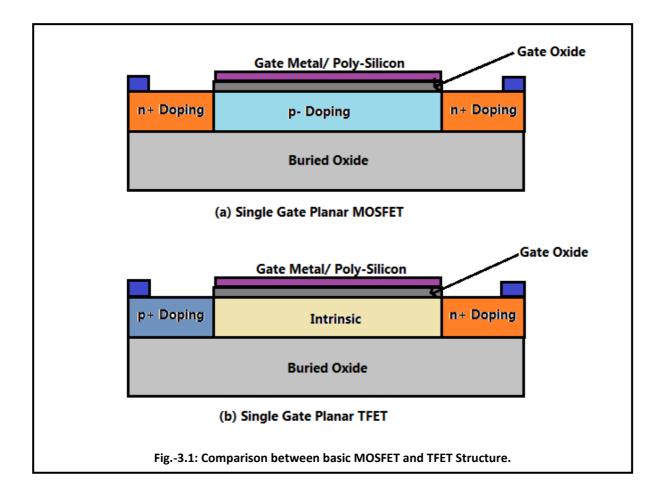

The most important reason for the popularity of TFET as a replacement of MOSFET is the similarity in construction. If the doping in the source region of a MOSFET is reversed, we obtain a basic TFET. Also, the channel region in TFET is made intrinsic or very lightly doped in nature, unlike MOSFET, where the channel is mostly lightly doped. The basic single MOSFET and TFET structures are shown in Fig.-3.1.

For an n-channel TFET, the source is p-type doped and the drain is n-type doped. The doping is just reversed for p-channel TFET. Similar construction is followed for Double gate structure [35], [36]. Almost all of the MOSFET structures [31], [34] can be converted to TFET, just by alternating the source doping.

## 3.2 Working Principle of TFET in Brief:

The Tunnel Field Effect Transistor (TFET) belongs to a section of devices known as steep sub-threshold devices. The basic working principle of TFET is based on quantum mechanical tunnelling. The carriers tunnel through the band-gap, which acts as a potential barrier in the source channel junction. Due to the fundamental difference in carrier generation/ transport phenomenon from the MOSFET [37], the TFETs can achieve sub-threshold slopes lower than 60mV/decade. The tunnelling theory is briefly described in Chapter-2.

The tunnel field effect transistors can be visualized as gated PIN diodes. The potential at the gate is used to control the tunnelling barrier height, thus effectively controlling the device current. The device has extremely low OFF state current, as the leakage current is mostly due to a reverse biased diode. The ON current of the device is comparatively

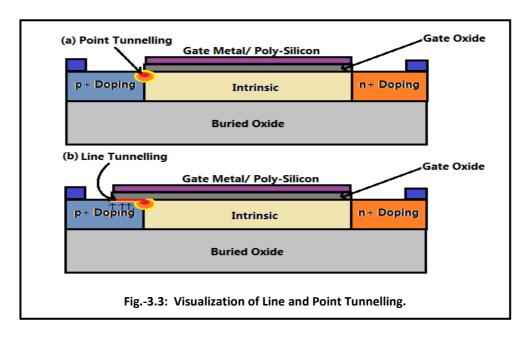

lower than MOSFET, but the situation can be improved by using high-k dielectrics and a method called line-tunnelling. In the TFET structure presented in Fig.3.1 and also in similar double gate structures, the band-to-band generation is confined to a small circular region or a point at the source-channel interface, near the gate oxide-semiconductor interface only. Thus the volume over which the carrier generation takes place is small, leading to small ON currents. Such type of tunnelling is aptly called Point tunnelling.

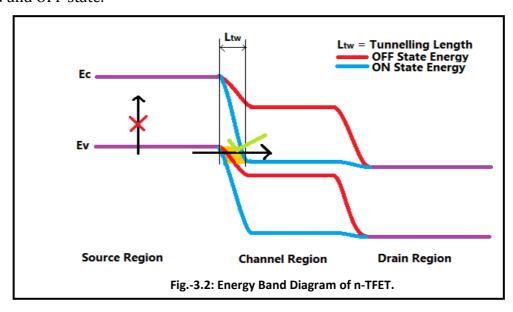

a. **Point Tunnelling:** This is the most common type of carrier generation method. The maximum carrier generation rate is almost confined to a point. The barrier in OFF state is too large for the electrons to overcome or tunnel. But as the gate potential is increased (assuming n-TFET), the conduction band in channel region aligns with the valence band of source region. The valence of p-type source is full of electrons but the intrinsic channels conduction band has no free states for the electrons to tunnel. With sufficient drain voltage, the conduction band at the channel starts to get Free states and hence the electrons now can tunnel and contribute as device current. Thus, unlike MOSFETs, there is no ON state without current flow. Also, the TFET has two threshold voltages, one for the gate bias and another for drain bias. Fig.-3.2 shows the energy band structure for n-TFET in ON and OFF state.

**Line Tunnelling:** In order to increase the ON current in TFET, often the method of line tunnelling is applied. Here a gate overlap is created over the source region. The electric

field thus formed has to in a direction that aids tunnelling. The electrons from the inner parts of the source tunnel to the inversion region formed near the surface of the source (for n-TFET). The carrier generation takes place in a line, near the source-gate oxide interface, hence the name. Since the carrier generation area/ dimension is larger than point tunnelling, the ON current increases. The phenomenon of point and line tunnelling are illustrated in Fig.-3.3.

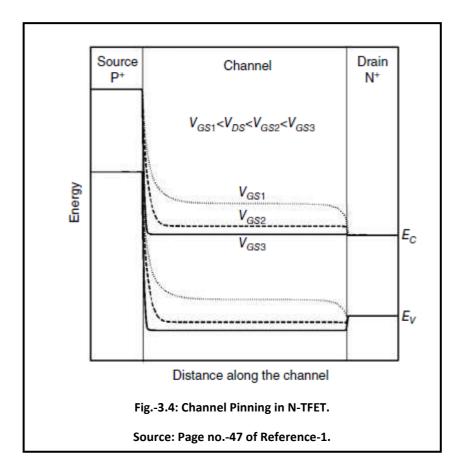

### 3.2.1: Pinning of Channel Potential:

As discussed earlier, the gate bias causes the energy band in the channel to modulate, thus enabling or disabling tunnelling of carriers. However, for very high gate voltages ( $V_{GS} > V_{DS}$ ), the inversion charges generated at the semiconductor-gate oxide interface becomes comparable to the electron density in the n-type drain region (assuming n-TFET). In such case the channel can be considered to be effectively shorted or pinned to the drain, this phenomenon is known as channel pinning. The pinning of the channel potential does not occur precisely at  $V_{GS} = V_{DS}$ , but near to that value, as the inversion charge varies constantly. Due to pinning, the drain current becomes less responsive to the change in applied gate voltage. After a certain value of gate voltage, the increase in drain current, corresponding to the change in gate voltage reduces. The reduction in drain current is due to the fact that the conduction band does not dip further to place more unoccupied states for electrons to tunnel from the valence band in source region. The pinning of channel potential is demonstrated in Fig.-3.4.

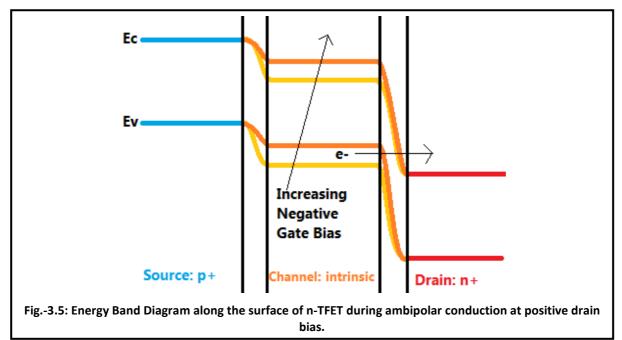

### 3.2.1: Ambipolarity in TFETs:

The characteristic curve of a basic TFET reveals that they conduct for negative values of gate voltage in case of n-TFET and vice-versa for p-TFET. The energy band diagram in case of ambipolar conduction is illustrated in Fig.-3.5.

With a certain amount of negative gate bias, the valence band in the channel region starts to align with the conduction band in the drain region. The positive drain bias causes the electrons to tunnel across the channel-drain junction, which results in drain current conduction. This behaviour is known as ambipolarity in TFET. The problem with ambipolarity is that it degrades performance when TFETs are used in digital circuit applications. The reverse conducting behaviour of TFETs make to them harder to use in applications running on bi-polar or even uni-polar power supplies. Any amount of reverse voltage on gate during the supposedly OFF state of the device will make it conduct and increase leakage and affect the voltage level of the logic circuit. Thus a plethora of solutions for reducing the ambipolar nature of the TFET have been proposed with varying degree of success. A few of the solutions/ modifications done to TFET structure for reduction of reverse conduction is discussed in the upcoming section.

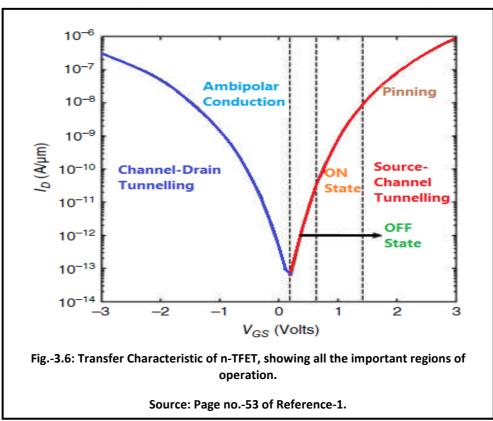

Fig.-3.6 shows the transfer characteristic of n-TFET, highlighting the ambipolar conduction and channel pinning.

# 3.3 @ Brief Literature Review on various TFET Designs for Performance Enhancement:

**3.3.1. Using multiple Gate Oxide Materials:** The use of high-k dielectric is desirable in TFETs as their ON current is inherently smaller than MOSFETs. With high-k dielectrics, the gate to source electric field can be enhanced, leading higher band-to-band generation rate and hence, higher ON currents. Unfortunately, the same is also true for the channel-drain junction, thus the reverse conduction current also increases with the use of high-k dielectric. The solution to this problem is to use separate dielectrics near the source-channel and channel-drain junctions. The high-k gate oxide should be placed near the source and the low-k dielectric near the drain, in order to maintain the high ON current and reduce the reverse gate voltage current. The device structure is available in [2]. The single gate structures are mostly outdated and currently only Double Gate TFETs are of interest in research.

The lengths of the high-k and low-k dielectrics can be optimized to obtain the least ambipolar nature and highest ON current. The optimization for high-k dielectric length for the dual material gate oxide structure has been performed in the work of R. Narang et al [2] where it is referred as the hetero-gate (HG) TFET. The result thus obtained can also be found in page no.-5 of reference-2. The doping at source and drain are p+ and n+ respectively with concentration of  $10^{20}$  cm<sup>-3</sup>. The high-k dielectric is HfO<sub>2</sub> with k= $21\epsilon_0$  and low-k is SiO<sub>2</sub> with k= $3.9\epsilon_0$ . The channel length is kept at 45nm, with silicon thickness of 10nm and oxide thickness of 3nm.

It is observed that the  $I_{ON}$  degrades for both the extreme case of high-k dielectric length  $^{[2]}$ . The ambipolarity and gate capacitance increases with increasing length of high-k dielectric.

**3.3.2. Using Multiple Materials as Gate Metal:** To enhance the drain current and make it comparable to MOSFET and at the same time subdue the inherent ambipolar nature of the TFET, two different materials can be used over the channel with different work function [3]. Basically the variation in work function is made such that there is an increase in the electric field at the source channel junction so as to effectively increase the tunnelling of the carriers, and at the same time just the opposite at the drain end is achieved. Thus, there is a boost in the ON current and reduction in ambipolar current. If looked closely, the principle is very similar to dual material gate oxide implementation. The construction of Dual Material Gate Metal TFET is shown in page no.-2 of reference-3. The length of auxiliary gate and tunnelling gate can be optimized to obtain highest possible ON currents and lowest possible ambipolar current. The gate length optimization curves are presented in page no.-3 of reference-3. All the data presented here are borrowed from the work of S. Saurabh et al [3].

The basic idea for such device (n-TFET) is to place the metal with lower work-function (known as the tunnel gate) near the source-channel interface and metal with higher work-function (known as the auxiliary gate) at the channel-drain interface. The work-function of the tunnelling gate can also be optimized, given the metal with the required work-function is available and compatible with the fabrication procedure.

From the work-function variation curve in page no.-3 of reference-3, it is clear that the ON current increases with lower work-functions. Finally, we need to compare the Dual metal gate with our conventional single metal gate TFET. The comparison is again performed by S. Saurabh et al [3], and available in page no.-3 of reference-3. The comparison between conventional and dual metal gate TFET clearly shows that the DMG DGTFET is better than SMG DGTFET with lowest leakage currents and comparable ON currents.

The improvement over the Dual Metal Gate TFET was proposed by N. Bagga et al [4]. The renovated device is provided with triple metal at the gate, instead of two. The gate work-function engineering possibilities are greater with more number of metals, as the effectiveness of work-function control over channel improves due to more spatial resolution. The paper under consideration [4], also includes analytical modelling of the device, but here we will only concentrate on the qualitative behaviour of the device.

The transfer characteristics of the TM-DGTFET for varying silicon film thickness are shown in page no.-6 of reference-4. The oxide thickness for the device is 2nm, with overall channel length of 60nm with different metal lengths:  $L_1$ ,  $L_2$ ,  $L_3$  values of 10nm, 20nm and 30nm respectively. The doping concentrations are  $2x10^{20}$  cm<sup>-3</sup> p-type at source and n-type at drain.

**3.3.3. Lightly Doped Drain:** The ambipolar nature of TFET is caused by channel-drain tunnelling. The ambipolarity in TFET becomes prominent when the channel length goes below 10nm [5], both the OFF current and sub-threshold swing increases, because of source-drain tunnelling. The tunnelling of electrons is possible only if filled valence band aligns with empty conduction band states, which can easily occur in degenerated semiconductors. Thus, to reduce channel-drain tunnelling, the doping in the drain can be reduced, as the channel is already very lightly doped. This reduced drain doping effectively lowers the ambipolar current.

The TFET used for simulation in reference-5, is a Hetero-TFET, with Source of AlGaAsSb and Channel of InAs. The plot in page no.-2 of [5] shows that with decrease in drain doping, the sub-threshold swing, OFF current and ambipolar conduction reduces.

The reduced drain doping has the disadvantage of increasing the contact resistance at the drain. Thus, in most cases a lightly doped pocket region is formed before the drain of same type of doping as that of the drain. The drain can now be highly doped for maintaining low contact resistance without affecting the OFF state leakage or ambipolarity.

**3.3.4. PNPN or NPNP TFET Structure:** One way of increasing the drain current is to introduce a small but highly doped region near the source of opposite doping type to that of the source. The pocket doping causes an augmented dip in the conduction band near the valence band in the source (considering PNPN device) even at  $V_{GS}$ =0V. This increases the tunnelling probability as the number of aligned states for electrons to tunnel increases. Due to such doping, the lateral electric field also increases, meaning more current due to higher band-to-band generation. According to [6], the optimum

pocket doping length is around 4nm. If the pocket doping created is too long, the region might not be fully depleted causing the device to lose Gate control, thus curtailing the sub-threshold swing. Also, fabricating devices with very narrow pocket doping is difficult. Even if by implantation a thin doping is introduced, the dopants diffuse during other high temperature fabrication steps and thus increasing the overall pocket doping length. For a basic PNPN structure, the Source is p+-doped, a pocket doping of n+ type is introduced, followed by very light p-type doped channel, ending with n+ doped Drain region.

**3.3.5. Raised Germanium Source Structure:** The band-to-band generation rate increases with use of lower band gap materials, as Germanium (Ge) [7]. Thus, using lower band gap semiconductor at the source increases the ON state current. As an improvement to this concept S.H. Kim, et al [7] proposed the raised germanium source TFET. The proposed structure increases the overlap of gate with the source, thus increasing the chance of line tunnelling.

The proposed structure is illustrated in page no.-2 of reference-7. The Ge-Source region is doped p-type with concentration of  $1x10^{19}$  cm<sup>-3</sup>. Drain is doped n-type with concentration of  $1x10^{19}$  cm<sup>-3</sup>. The silicon thickness is 100nm, with effective  $SiO_2$  thickness of 1nm. The channel region is moderately doped at  $1x10^{18}$  cm<sup>-3</sup> p-type. The gate length is kept at 30nm and the buried oxide thickness at 200nm. The Germanium layer thickness of 25nm for partially elevated and 65nm thick for fully elevated structure is grown in-situ over the initially present silicon source. The simulation is performed with calibrated TCAD model. The calibration curve and the transfer characteristics are shown in page no.-2 of [7]. The calibrated local band-to-band tunnelling model's coefficients are:  $A = 1.46 \times 10^{17}$  cm<sup>-3</sup>s<sup>-1</sup> and  $B = 3.59 \times 10^6$  Vcm<sup>-1</sup>. The raised source structures provide good amount of ON current. The current can

**3.3.6. Si-Ge Source UTFET:** The device structure was proposed by W. Wang et al [8]. The device has a U-shaped channel, due to which an effectively longer channel can be contained in a smaller dimension. Because of the longer channel, the leakage current is reduced. On a basic UTFET structure with p+ doped source followed by p+ doped Si-Ge

further be increased by using pocket doping, as mentioned in the previous section.

layer, an n+ doped delta layer with doping concentration of  $5x10^{19}$  cm<sup>-3</sup> is introduced. This delta layer reduces the band-to-band tunnelling length, hence effectively increasing the ON current. The basic UTFET structure and the delta doped structures are presented in page no.-1 of reference-8. The depth of the TFET gate is 120nm, length of the gate is 16nm and the oxide thickness is 1.2nm.

The U-Gate TFET can achieve relatively high ON/ OFF ration of current, with a value of  $10^8$ , as observed from the figure in pageno.-2of [8]. The mentioned ON/ OFF ratio can be achieved at relatively low voltages,  $V_{GS}$ =0.7V and  $V_{DS}$ =0.7V. The results are better than similar planar-TFET with 16nm channel length.

**3.3.7.L-Shaped TFET (LTFET):** The device was proposed and fabricated by S.W. Kim et al in the year 2012 [9]. The device is called L-Shaped TFET, because the channel region of the TFET resembles the letter 'L'. The LTFET is fabricated using Mesa etching technology, especially the elevated source region. The gate oxide is SiO<sub>2</sub> with a thickness of 2nm. High-k dielectric (like HfO<sub>2</sub>) can be added by Atomic Layer Deposition (ALD) technique for enhanced ON currents. The elevated source region makes line tunnelling possible, as the gate region is directly over/ side by side with the source, increasing the region over which the tunnelling is possible. The source, drain and channel region are doped p+, n+ and p- with concentrations  $1x10^{20}$ ,  $1x10^{18}$  and  $1x10^{15}$  cm<sup>-3</sup> respectively. The device structure is provided in page no.-2 of reference-9.