# A Comprehensive Study on Different Structures of TFET: Analytical Modeling and Simulation Based Validation

Thesis submitted in partial fulfillment of the requirements for the award of the degree

of

Master of Technology in

VLSI Design and Microelectronics Technology

by

Ayan Bhattacharya

Roll No: 001610703006

**Examination Roll No: M6VLS19014**

Registration No: 137278 of 2016-17

**Under the Esteemed Guidance of**

# **Prof. Subir Kumar Sarkar**

**Department of Electronics and Tele-Communication Engineering**

Jadavpur University, Kolkata-700032

West Bengal, India

**MAY 2019**

# Faculty of Engineering & Technology Jadavpur University CERTIFICATE OF EXAMINATION

This is to certify that the thesis entitled "A comprehensive study on different structures of TFET: Analytical modeling and simulation based validation" has been carried out by AYAN BHATTACHARYA (Roll No: 001610703006, Examination Roll No: M6VLS19014 and Registration No:137278 of 2016-17) under my guidance and supervision and can be accepted in partial fulfilment for the degree of Master of Technology in VLSI Design and Microelectronics Technology. In my opinion the work fulfils the requirement for which it is submitted. To the best of my knowledge, the matter embodied in the thesis has not been submitted to any other organization.

Prof. Subir Kumar Sarkar

**Project Supervisor**

Prof. Sheli Sinha Chaudhuri

Head of the Department,

Department of Electronics and

Tele-Communication Engineering,

Jadavpur University,

Kolkata-700032

Prof. Chiranjib Bhattacharjee

Dean,

Faculty Council of Engineering

and Technology (FET),

Jadavpur University,

Kolkata-700032

# Faculty of Engineering & Technology Jadavpur University CERTIFICATE OF APPROVAL\*

This is to certify that the Master Thesis entitled "A comprehensive study on different structures of TFET: Analytical modeling and simulation based validation" is hereby approved as a creditable study of an engineering subject carried out and presented in a manner satisfactory to warrant its acceptance as pre-requisite to the degree for which it has been submitted. It is understood that by this approval the undersigned do not necessarily endorse or accept every statement made, opinion expressed, or conclusion drawn therein but approve the thesis only for the purpose for which it has been submitted.

| Committee on Final Examination |

|--------------------------------|

| For Evaluation of the Thesis   |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

|                                |

| Examiners                      |

<sup>\*</sup>Only in case the thesis is approved.

# DECLARATION OF ORIGINALITY AND COMPLIANCE OF ACADEMIC ETHICS

I hereby declare that the M.Tech. thesis entitled submitted to Faculty of Engineering & Technology, Jadavpur University as part of fulfillment of degree of Master of Technology in VLSI design and Microelectronics Technology studies, is an original work carried out by undersigned. All information in this document have been obtained and presented in accordance with academic rules and ethical conduct. The matter embodied in this project is a genuine work done by the undersigned and has not been submitted to any other University/Institute for the fulfillment of the requirement of any course of study.

I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

NAME: AYAN BHATTACHARYA

**EXAMINATION ROLL NUMBER: M6VLS19014**

**DEPARTMENT: Electronics and Tele-Communication Engineering (ETCE)**

Thesis Titles: "A comprehensive study on different structures of TFET: Analytical modeling and simulation based validation"

(AYAN BHATTACHARYA)

Signature with Date

# **ACKNOWLEDGEMENT**

I feel myself fortunate in having the privilege to express my deep sense of gratitude and indebtedness to my project guide **Prof. Subir Kumar Sarkar**, Department of Electronics & Tele-Communication Engineering, Jadavpur University, Kolkata for providing me the opportunity to carry out research under his guidance and developing the concepts related to my thesis topic. I am grateful to him for the valuable insights and suggestions that he gave me throughout my M.Tech. project.

I would also like to express sincere gratitude to all my professors of Jadavpur University for their consent and providing necessary information whenever required. I am grateful to Mr. Bijoy Goswami, Mr. Dinesh Kumar Dash, Mr. Anup Dey, Mr. Subhashis Roy, Ms. Pritha Banerjee, Ms. Priyanka Saha for their suggestions & enormous encouragement. I specially thank my classmates and friends Bikram Biswas, Debadipta Basak, Sutanni Bhowmick, Koelgeet Kaur, Rounak Dutta who have made valuable comment suggestion on this proposal which gave an inspiration to improve my report and knowledge. I would like to offer my sincere gratitude to them for sharing the ups and downs during the development and bearing inconvenience. The words of thanks are only a token of my true appreciation for all they have done to make my project in the present shape.

I would like to thank **Prof. Sheli Sinha Chaudhuri,** H.O.D, Department of Electronics & Tele-Communication Engineering, Jadavpur University for providing me all the facilities for carrying out the entire project work. I would like to express my sincere appreciation to all the teaching and non-teaching staff of the department for providing necessary support and aids.

Last but not the least, this work would not have been possible without the love, support and encouragement of my family and near and dear ones. Without them, I would not have achieved anything in life.

Ayan Bhattacharya

M. Tech in VLSI Design and Microelectronics Technology

Department of ETCE, Jadavpur University

Kolkata-700032, West Bengal, India

# CONTENT

| Certificate of Examination                                                   | I     |

|------------------------------------------------------------------------------|-------|

| Certificate of Approval                                                      | II    |

| Declaration of Originality and Compliance of Academic Ethics                 | III   |

| Acknowledgement                                                              | IV    |

| Content                                                                      | V     |

| List of Figures                                                              | IX    |

| List of Tables                                                               | XII   |

| Abbreviations                                                                | XIII  |

| Abstract                                                                     | XIV   |

| Chapter 1: Introduction and Objective                                        | 01-08 |

| 1.1. Introduction                                                            | 2     |

| 1.2. A brief overview of TFET                                                | 3     |

| 1.3. Motivation of Current Research                                          | 4     |

| 1.4. Objective                                                               | 5     |

| 1.5. Organization of Thesis                                                  | 5     |

| References                                                                   | 6     |

| Chapter 2: Background study prior to the research work and Literature Review | 09-38 |

| 2.1. Introduction                                                            | 10    |

| 2.2. Evolution of transistor                                                 | 10    |

| 2.3. Timeline of electronics from 1947                                       | 11    |

| 2.4. Technological Limitations of MOSFETs                                    | 11    |

| 2.4.1. Drain-induced barrier lowering                                        | 11    |

| 2.4.2. Threshold voltage roll off                                            | 13    |

| 2.4.3. Surface scattering,                                  | 14    |

|-------------------------------------------------------------|-------|

| 2.4.4. Velocity saturation                                  | 15    |

| 2.4.5. Hot electron effect                                  | 16    |

| 2.5. Introduction to TFET                                   | 17    |

| 2.6. Major shortcoming of TFET                              | 19    |

| 2.6.1. Low on current                                       | 19    |

| 2.6.2. Ambipolar current conduction                         | 20    |

| 2.7. Structural difference of MOSFET and TFET               | 20    |

| 2.8. Performance dependence on several parameters of device | 21    |

| 2.8.1. Doping                                               | 21    |

| 2.8.2. Gate work function                                   | 22    |

| 2.8.3. Gate Oxide                                           | 23    |

| 2.9. Different types of existing TFET                       | 24    |

| 2.9.1. Planar TFET                                          | 24    |

| 2.9.2. Three dimensional TFET                               | 28    |

| 2.10. Drain engineered TFET                                 | 29    |

| 2.10.1. Device structure and parameter                      | 29    |

| 2.10.2. Observations                                        | 31    |

| 2.11. Literature review                                     | 33    |

| 2.12. Next footstep                                         | 34    |

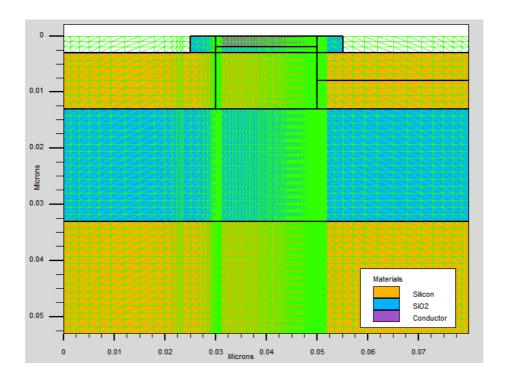

| 2.13. Simulation software                                   | 34    |

| 2.14. Quantum simulation                                    | 35    |

| References                                                  | 35    |

| CHAPTER 3: Impact of source engineering in                  | 39-50 |

| Split-Drain TFET                                            |       |

| 3.1. Introduction and Proposed Work                         | 40    |

| 3.2. Device Structure and Parameters                        | 41    |

| 3.3. Simulation Setup                                                                           |       |

|-------------------------------------------------------------------------------------------------|-------|

| 3.4. Results and Discussion                                                                     | 43    |

| (a) Electron Mobility                                                                           | 43    |

| (b)Drain Output Characteristics                                                                 | 44    |

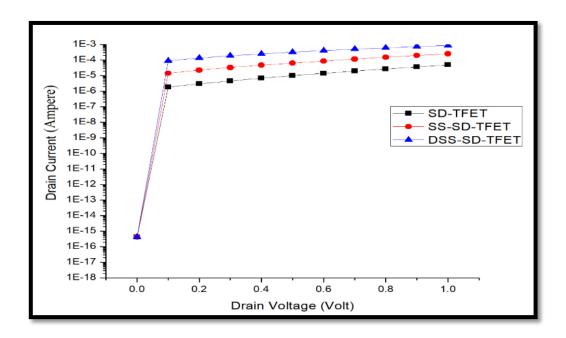

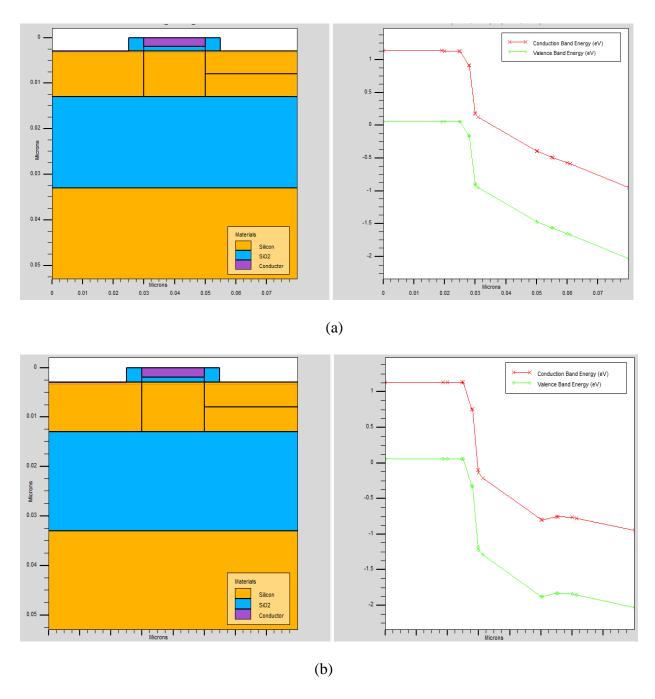

| (c) Band Diagram Analysis                                                                       | 44    |

| (d) Transfer Characteristics                                                                    | 48    |

| References                                                                                      | 49    |

| CHAPTER 4: Analytical Modeling and Simulation of Low Power Salient Source Double Gate TFET      | 51-65 |

| 4.1. Introduction and Proposed Work                                                             | 52    |

| 4.2. Device Structure and Optimized Parameters                                                  | 52    |

| 4.3. Results and Discussion                                                                     | 55    |

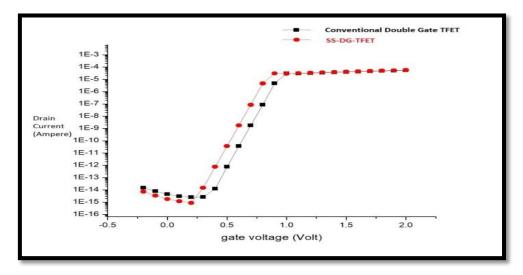

| (a) Study of Gate Voltage-Drain Current Characteristics                                         | 55    |

| (b) Band Diagram Analysis                                                                       | 56    |

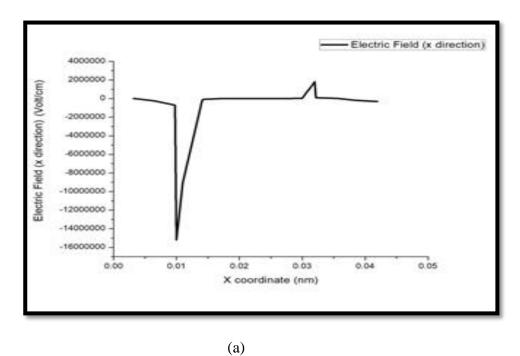

| (c) Electric Field Study                                                                        | 57    |

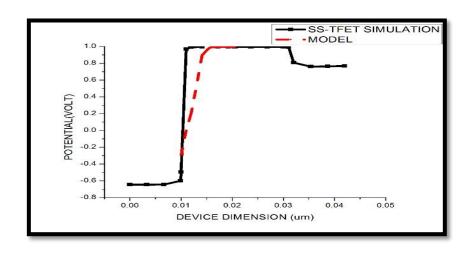

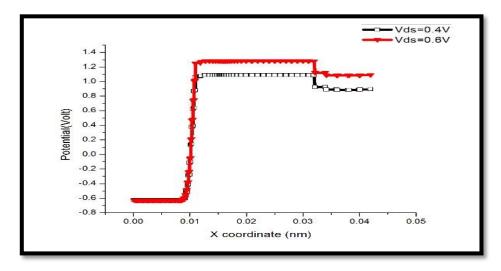

| (d)Surface Potential                                                                            | 58    |

| (e) Comparison with already existing structure                                                  | 62    |

| References                                                                                      | 63    |

| CHAPTER 5: Double Source TFET:  A comprehensive analysis considering quantum mechanical effects | 66-82 |

| 5.1. Introduction and Proposed Work                                                             | 67    |

| 5.2. Device structures and optimized parameters                                                 | 67    |

| 5.3. Description of the model                                                                   | 71    |

| (a) Non-local BTBT model                                                                        | 71    |

| (b) Schrodinger-Poisson model                                            | 72    |

|--------------------------------------------------------------------------|-------|

| (c) Limitation of the models                                             | 73    |

| 5.4. Results and Discussion                                              | 73    |

| 5.4.1 Comparison of transfer characteristics for different channel lengt | h 73  |

| 5.4.2 Comparison of transconductance                                     | 73    |

| 5.4.3 Variation of oxide thickness                                       | 74    |

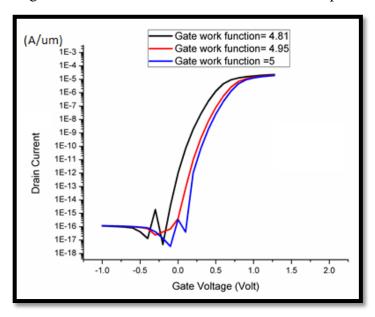

| 5.4.4 Variation of Gate work function                                    | 76    |

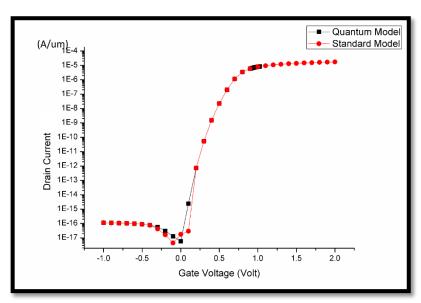

| 5.4.5 Difference with semi classical model                               | 76    |

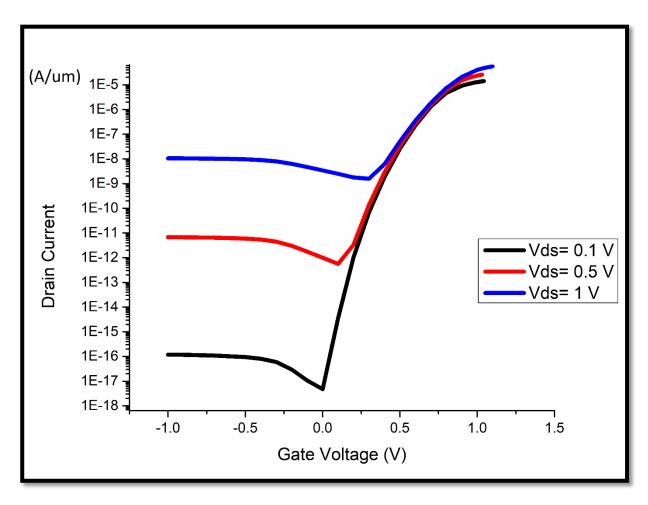

| 5.4.6 Effect of drain voltage on output characteristics                  | 77    |

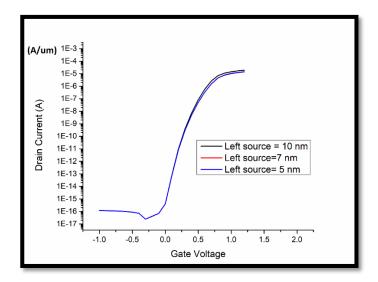

| 5.4.7 Source length variation                                            | 78    |

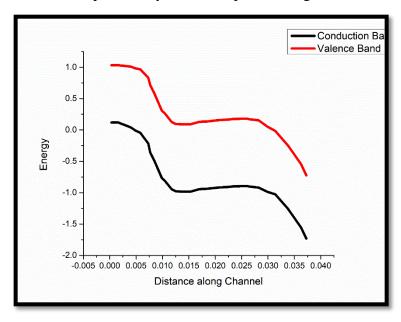

| 5.4.8 Band diagram analysis                                              | 79    |

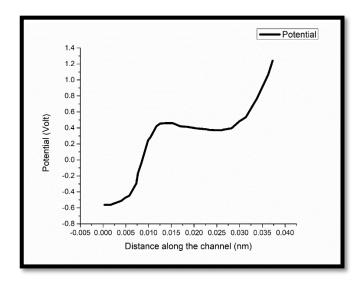

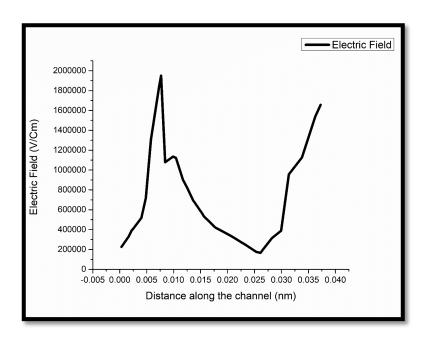

| 5.4.9 Potential and electric field                                       | 79    |

| References                                                               | 80    |

|                                                                          |       |

| Chapter 6: Concluding Remarks and Future scope                           | 83-85 |

| 6.1 Conclusion                                                           | 83    |

| 6.2 Scopes for Future Work                                               | 84    |

| Research publications of Ayan Bhattacharya relevant                      | 86-87 |

# **LIST OF FIGURES**

| Fig. No.   | Figure Name                                                                         | Page No. |

|------------|-------------------------------------------------------------------------------------|----------|

|            | Chapter 1                                                                           |          |

| Fig. 1.1.  | Moore's Law                                                                         | 3        |

|            | Chapter 2                                                                           |          |

| Fig. 2.1.  | Evolution of transistor                                                             | 10       |

| Fig. 2.2.  | Surface potential along the position in channel for VDS = 0.1 V and 1.5 V           | 12       |

| Fig. 2.3.  | Three mechanisms determining SCEs                                                   | 12       |

| Fig. 2.4.  | Threshold voltage shift with channel length                                         | 14       |

| Fig. 2.5.  | Threshold voltage roll-off for nano scale FinFET                                    | 14       |

| Fig. 2.6.  | Cross section view of MOSFET                                                        | 15       |

| Fig. 2.7.  | Mobility dependence on gate voltage                                                 | 15       |

| Fig. 2.8.  | Velocity Saturation                                                                 | 16       |

| Fig. 2.9.  | Hot electron effect                                                                 | 17       |

| Fig. 2.10. | Band diagram of a n-channel TFET at zero bias                                       | 18       |

| Fig. 2.11. | Band diagram of a TFET in the OFF-state at $V_{gs}$ = 0 V.                          | 18       |

| Fig. 2.12. | Band diagram along the surface of the                                               | 19       |

|            | TFET for (Vgs= 0, 0.4, 0.5, 0.6) in the ON-state.                                   |          |

| Fig. 2.13. | Band diagram along the surface of a TFET                                            | 20       |

|            | for a negative gate voltage (Vgs) and a                                             |          |

|            | positive drain voltage (Vds)                                                        |          |

| Fig.2.14.  | N-channel TFET                                                                      | 20       |

| Fig.2.15.  | N-channel MOSFET                                                                    | 21       |

| Fig.2.16.  | Band diagrams along the surface of an                                               | 21       |

|            | n-channel TFET with different values of                                             |          |

|            | source doping concentration.                                                        |          |

| Fig.2.17.  | Transfer characteristics of an n-channel TFET                                       | 22       |

|            | with different drain doping concentrations                                          |          |

|            | for a fixed drain voltage (VDS).                                                    |          |

| Fig.2.18.  | Band diagram along the surface                                                      | 22       |

|            | of an n-channel TFET for different values                                           |          |

|            | of the gate work function.                                                          |          |

| Fig.2.19.  | Transfer characteristics of an n-channel                                            | 23       |

|            | TFET with different values of the                                                   |          |

|            | gate work function.                                                                 |          |

| Fig. 2.20. | Gate leakage in a TFET through (a) SiO2 and                                         | 23       |

|            | (b) HfO2/SiO2 gate stack                                                            |          |

| Fig. 2.21. | p-channel SOI TFET                                                                  | 24       |

| Fig. 2.22. | p-channel double gate TFET                                                          | 24       |

| Fig. 2.23. | p-channel dual material gate TFET                                                   | 25       |

| Fig. 2.24. | p-n-p-n TFET                                                                        | 25       |

| Fig. 2.25. | Schematic of (a) planar, (b) partially raised and (c) fully raised Ge-source TFETs. | 26       |

| Fig. No.   | Figure Name                                                                                                                                                                                                                                       | Page No. |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            |                                                                                                                                                                                                                                                   |          |

| Fig. 2.26. | <ul><li>(a) Schematic view of an n-channel heterojunction TFET.</li><li>(b) Band diagram of the heterojunction TFET shown in (a)</li></ul>                                                                                                        | 26       |

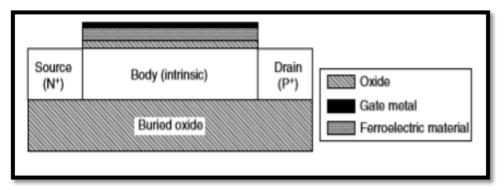

| Fig. 2.27  | p-channel ferroelectric TFET                                                                                                                                                                                                                      | 27       |

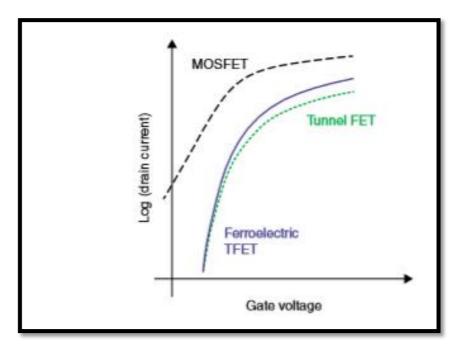

| Fig. 2.28. | Comparison of the ID–VGS curves of a ferroelectric TFET with that of a MOSFET and a conventional TFET                                                                                                                                             | 27       |

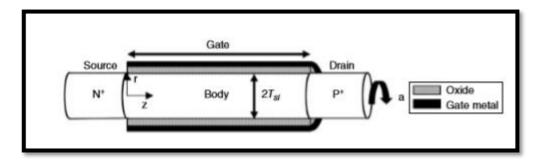

| Fig. 2.29. | Gate all around nanowire TFET                                                                                                                                                                                                                     | 28       |

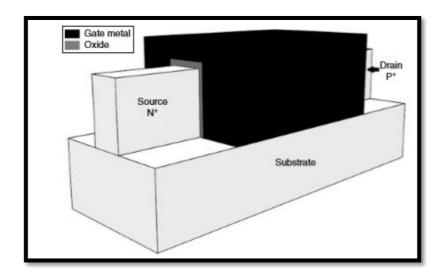

| Fig. 2.30. | Tri-Gate TFET                                                                                                                                                                                                                                     | 28       |

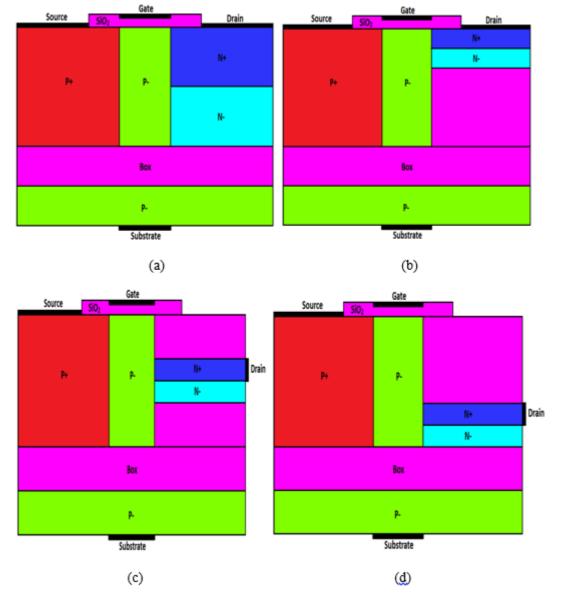

| Fig. 2.31. | Device Structure of (a) Splitted-Drain Single-Gate TFET (SD-SG TFET), (b) Top-Splitted-Drain Single-Gate TFET (TSD-SG TFET), (c) Mesial-Splitted-Drain Single-Gate TFET (MSD-SG TFET) and (d) Basal-Splitted-Drain Single-Gate TFET (BSD-SG TFET) | 31       |

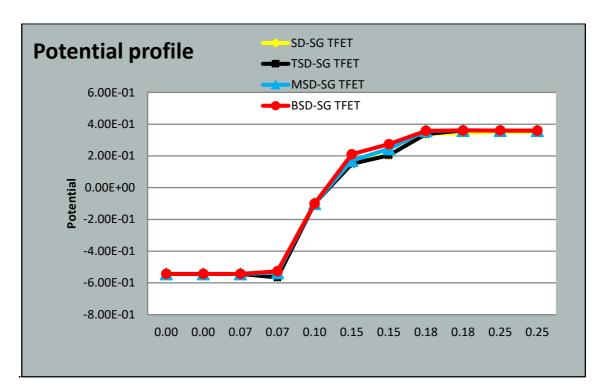

| Fig. 2.32. | Comparison of potential profile                                                                                                                                                                                                                   | 32       |

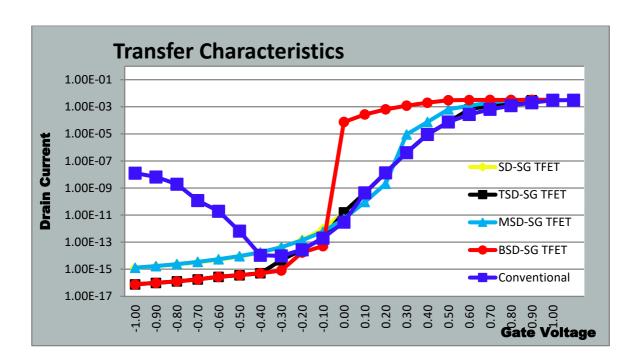

| Fig. 2.33. | Comparison of transfer characteristics                                                                                                                                                                                                            | 32       |

|            | Chapter 3                                                                                                                                                                                                                                         |          |

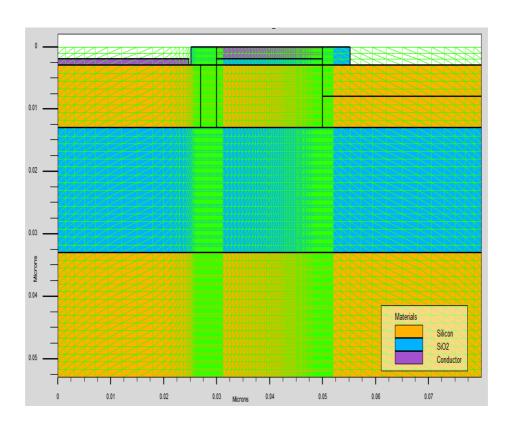

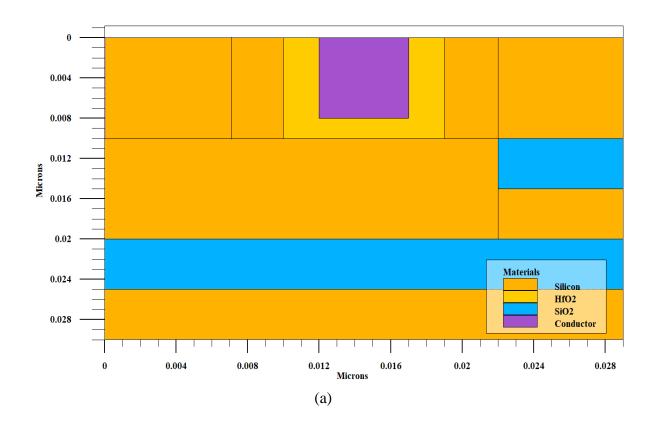

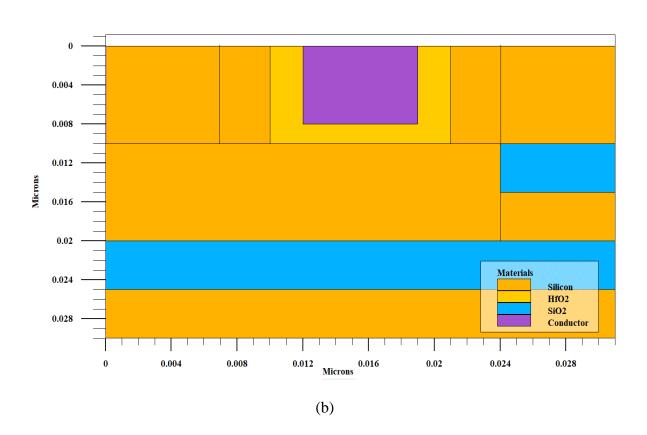

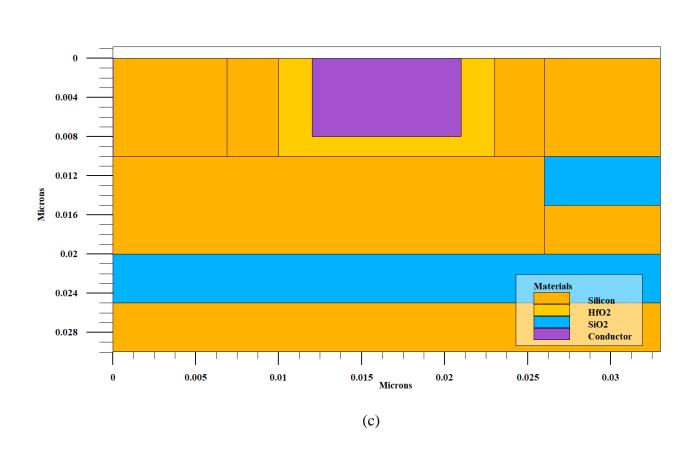

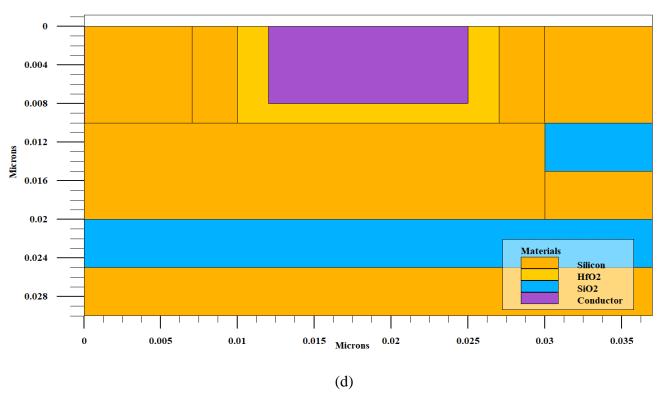

| Fig. 3.1.  | Structures along with corresponding doping profiles of  (a) Split Drain TFET (SD TFET), (b) Split Source Split Drain  TFET (SS-SD TFET) (c) Double Split Source Split Drain  TFET (DSS-SD TFET)                                                   | 41-42    |

| Fig. 3.2.  | Electron Mobility profile of the carriers for the DSS-SD-TFET structure                                                                                                                                                                           | 43       |

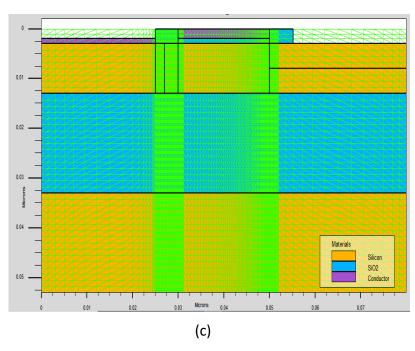

| Fig. 3.3.  | Comparison of Drain current vs Vds characteristics for three structures such as SD-TFET, SS-SD TFET and DSS-SD TFET.                                                                                                                              | 44       |

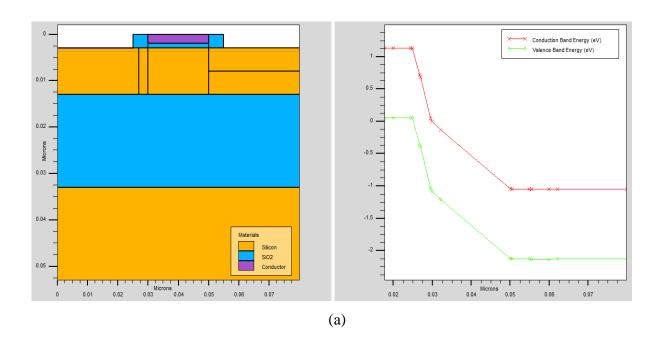

| Fig. 3.4.  | Band diagram of the SD TFET structure for (a) Vgs = Vds (Just ON) and (b) Vgs > Vds (ON).                                                                                                                                                         | 45       |

| Fig. 3.5.  | Band diagram of the SS-SD TFET structure for (a) Vgs = Vds (Just ON) and (b) Vgs > Vds (ON).                                                                                                                                                      | 46       |

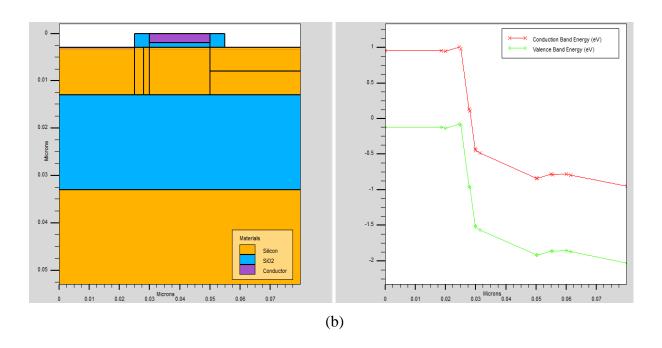

| Fig. 3.6.  | Band diagram of the DSS-SD TFET structure for (a) Vgs = Vds (Just ON) and (b) Vgs > Vds (ON).                                                                                                                                                     | 47       |

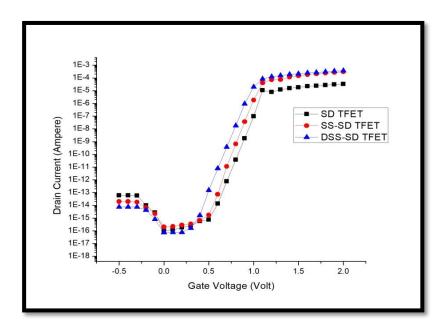

| Fig. 3.7.  | Transfer characteristics of SD TFET, SS-SD TFET and DSS-SD TFET structures.                                                                                                                                                                       | 48       |

|            | Chapter 4                                                                                                                                                                                                                                         |          |

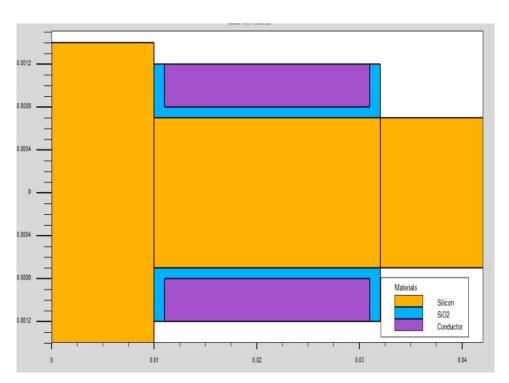

| Fig. 4.1.  | 2D cross sectional view of salient source DG-TFET                                                                                                                                                                                                 | 53       |

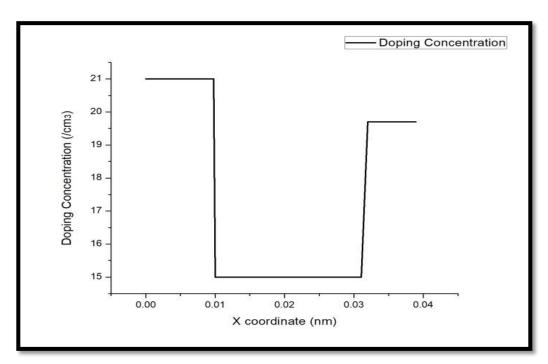

| Fig. 4.2.  | Doping concentration along the device                                                                                                                                                                                                             | 54       |

| Fig. No.   | Figure Name                                                                                                      | Page No. |

|------------|------------------------------------------------------------------------------------------------------------------|----------|

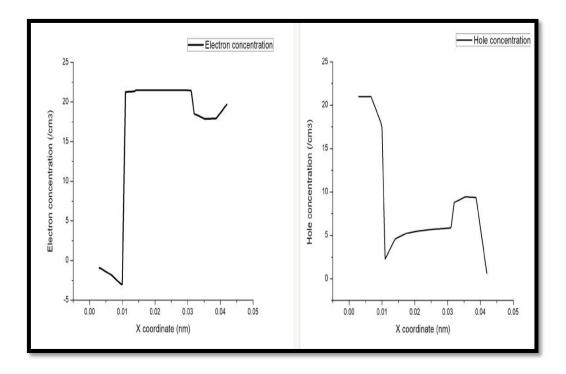

| Fig. 4.3.  | Electron and hole concentration in SS-DG-TFET                                                                    | 54       |

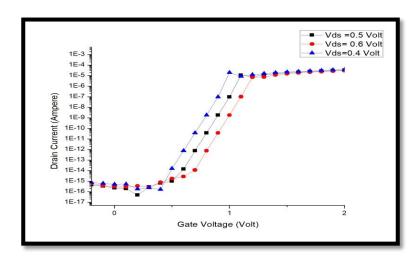

| Fig. 4.4.  | $I_{ds}$ – $V_{gs}$ characteristic at $V_{ds}$ =0.4V, 0.5V and 0.6V                                              | 56       |

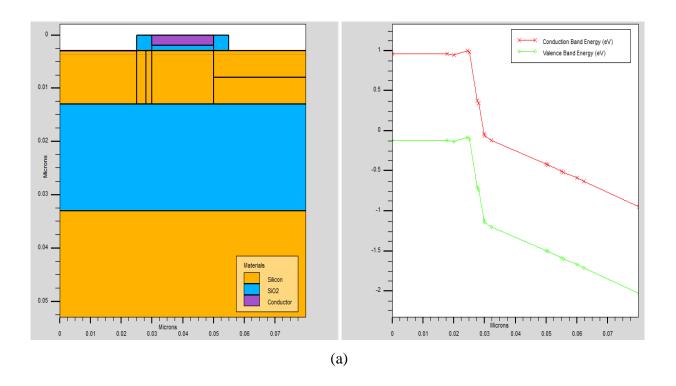

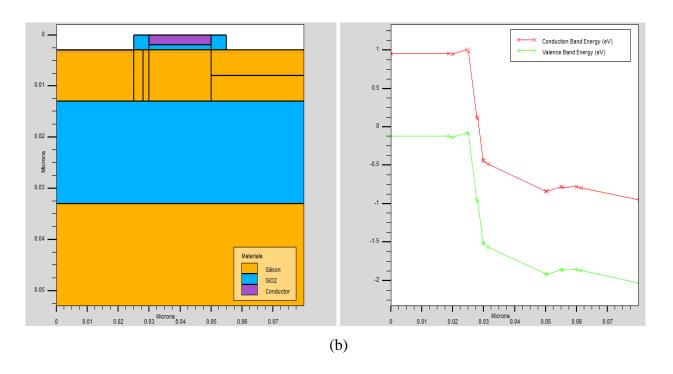

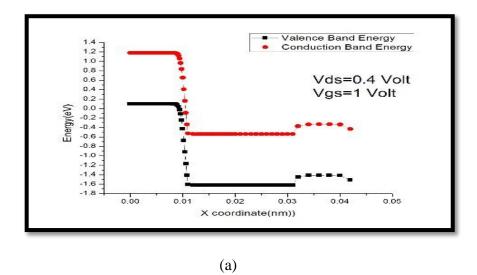

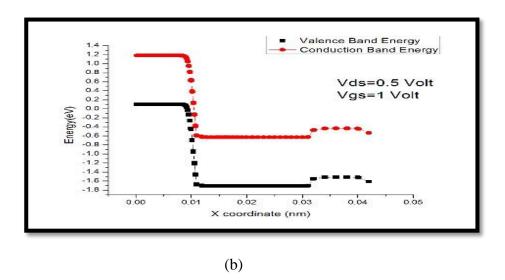

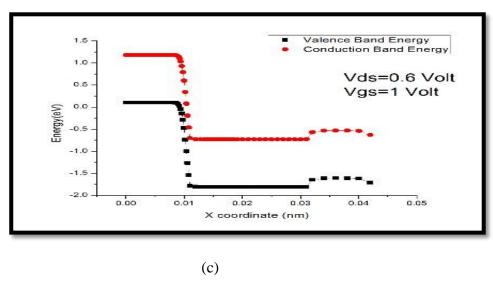

| Fig. 4.5.  | Band diagram of SS- DG-TFET structure for (a) $V_{ds}$ =0.4V, (b) $V_{ds}$ =0.5V and (c) $V_{ds}$ =0.6V.         | 56-57    |

| Fig. 4.6.  | Electric field along (a) X and (b) Y direction                                                                   | 58       |

| Fig. 4.7.  | Surface potential of SS-DG-TFET                                                                                  | 61       |

| Fig. 4.8.  | Comparison of surface potential for $V_{ds}$ =0.4V and $V_{ds}$ =0.6V                                            | 62       |

| Fig. 4.9.  | Comparison of gate-voltage drain-current characteristic                                                          | 62       |

| Ü          | of SS-DG-TFET and conventional double gate TFET at Vds=0.4 volt                                                  |          |

|            | Chapter 5                                                                                                        |          |

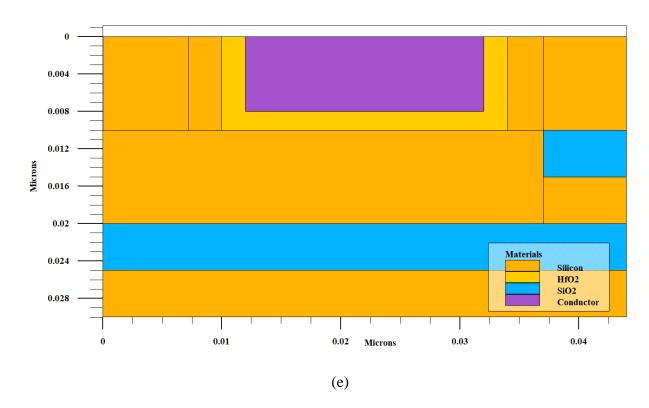

| Fig.5.1.   | 2D cross sectional view of DS-TFET with effective channel length (a) 5nm (b) 7nm (c) 9nm (d) 13 nm and (e) 20 nm | 68-70    |

| Fig.5.2.   | Transfer characteristics comparison for different effective channel length                                       | 73       |

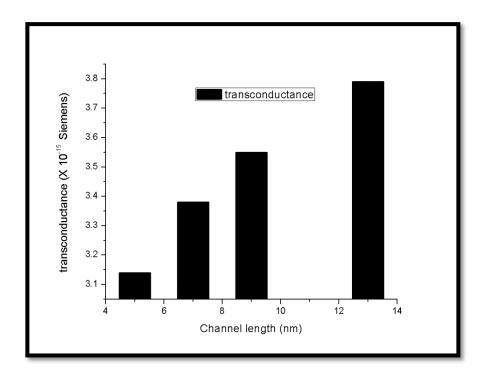

| Fig.5.3.   | Comparison of transconductance                                                                                   | 74       |

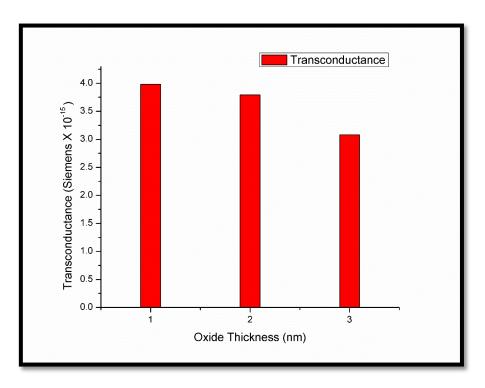

| Fig. 5.4.  | Comparison of transconductance for different oxide thickness                                                     | 75       |

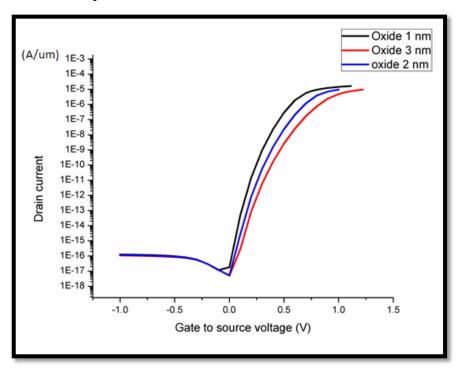

| Fig. 5.5.  | Comparison of transfer characteristics for different gate oxide thickness                                        | 75       |

| Fig. 5.6.  | Gate work function variation in DS-TFET                                                                          | 76       |

| Fig. 5.7.  | Comparison of quantum model with standard semi-classical model                                                   | 76       |

| Fig. 5.8.  | Effect on output characteristics for Drain voltage variation                                                     | 77       |

| Fig. 5.9.  | Effect on output characteristics for left source length variation                                                |          |

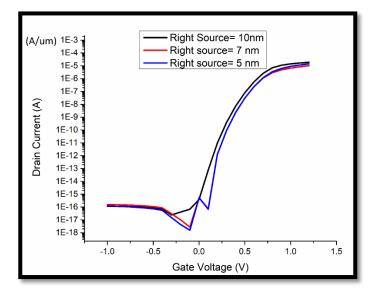

| Fig. 5.10. | Effect on output characteristics for right source length variation                                               | n 78     |

| Fig. 5.11. | Band diagram for Vds = 0.1 volt                                                                                  | 79       |

| Fig. 5.12. | Potential curve of DS-TFET                                                                                       | 79       |

| Fig. 5.13. | Electric Field of DS-TFET                                                                                        | 80       |

# **LIST OF TABLES**

# **CHAPTER 2**

| Table 2.1 | Device Parameters                                           | 30 |

|-----------|-------------------------------------------------------------|----|

|           | CHAPTER 3                                                   |    |

| Table 3.1 | Comparison of On-Off Current Ratio from Simulation          | 48 |

|           | CHAPTER 4                                                   |    |

| Table 4.1 | Values of sub-threshold slope corresponding to $V_{\rm ds}$ | 55 |

| Table 4.2 | Values of different parameters                              | 61 |

|           | CHAPTER 5                                                   |    |

| Table 5.1 | Doping concentration of different regions                   | 70 |

| Table 5.2 | Dimensions of different regions of DS-TFET                  | 71 |

| Table 5.3 | Comparison of transconductance                              | 74 |

| Table 5.4 | Comparison of SS                                            | 77 |

# **ABBREVIATIONS**

# **CHAPTER 1**

MOSFET- Metal Oxide Semiconductor Field Effect Transistor

**TFET- Tunnel Field Effect Transistor**

AMD - Advanced Micro Devices

## **CHAPTER 2**

LSI- Large Scale Integration

**VLSI-** Very Large Scale Integration

**ULSI-** Ultra Large Scale Integration

CMOS- Complementary Metal Oxide Semiconductor

SCE- Short Channel Effect

**DIBL- Drain Induced Barrier Lowering**

**SD-SG TFET- Splitted-Drain Single-Gate TFET**

TSD-SG TFET - Top- Splitted-Drain Single-Gate TFET

MSD-SG TFET- Mesial- Splitted-Drain Single-Gate TFET

BSD-SG TFET- Basal- Splitted-Drain Single-Gate TFET

# **CHAPTER 3**

SD TFET- Splitted-Drain TFET

SS-SD TFET- Split Source Split Drain TFET

**DSS-SD TFET- D**ouble **S**plit **S**ource **S**plit **D**rain **TFET**

# **CHAPTER 4**

SS-DG-TFET- Salient Source Double Gate TFET

# **CHAPTER 5**

**DS-TFET –D**ouble Source **TFET**

# **ABSTRACT**

The work focuses on new alternative or successor to CMOS or MOS device which can combat their disadvantages. Researchers are aiming to achieve better performing devices than MOSFET in terms of sub-threshold slope, power consumption and scalability. This work is an approach towards exploring one of such alternatives, the Tunnel Field Effect Transistor (TFET). Some application specific structures of TFET are analytically modeled and validated with the help of available simulation software during this work.

In first work the effect of source splitting in already drain splitted TFET is explored. Two different source splitted TFET geometries are critically analyzed and performance based comparison is done. During this work, the effect of source engineering in this drain engineered TFET is extensively investigated. Due to differential doping in source region, a changed behavior is expected in the modified TFET. This design modification is aimed towards achieving better performance in terms of ON/OFF current ratio.

In second work a salient source TFET structure is inquired into along with analytical expressions and simulation based results. The utility in low power application is the most striking feature of this device. In this work an attempt has been made to establish the proposed device as a better performing device than conventional double gate TFET.

The third work primarily aims to incorporate quantum mechanical models in the analysis of DS-TFET. At the age of vigorous scaling, the inclusion of quantum mechanical models are being obligatory in research works. An attempt has been made to do so to analyze the behavior of the device more accurately. In this work, quantum confinement based on non-local tunneling model along with self-consistent Schrodinger-Poisson quantum model is included.

In this work, the primary focus is on studying the effect of source engineering in TFET technology. In all three works, the geometries of source region of proposed devices are modified through engineering.

# **CHAPTER 1**

**Introduction and Objective**

#### 1.1. Introduction:

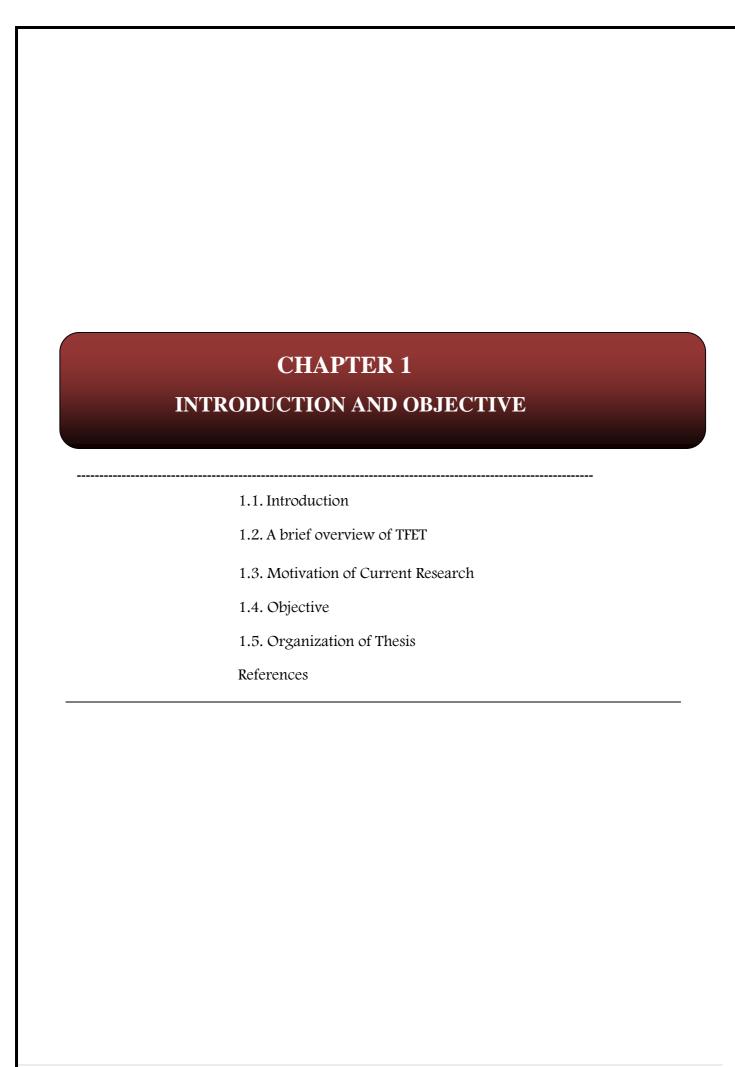

The drawbacks of the conventional MOSFET technology influence researchers to develop numerous experimental FETs which are remolding the nanoscale industry thoroughly. Reducing dimension in nano-regime is no more able to uphold Moore's law without degrading device performances. Moreover, scaled MOSFET structures with sufficiently low threshold voltage cannot be realized due to emergence of short channel effects. The swift technological advancement till date has only been possible through continuous betterment of electronic products in terms of power consumption, speed, cost, compactness, functionality and integration level. Miniaturization of device feature has been the principal impetus behind these trends and it has led to substantial improvement of quality as well as economic admissibility [1]. As enumerated by the Gordon Moore in 1965, the number of transistors per integrated chip would be roughly doubled in every 2 years. Fabrication of cheaper, faster and smaller Integrated Circuits (ICs) has been continued since last four decades to accomplish inevitable hunger for better device performance. In the early 1980's, dimension of minimum feature size in IC traversed the sub-micron limit; whereas by early 2010s, both Intel and AMD announced their commercial microchips using transistors with 32nm process. To keep pace with this implausible pace of growth, generous financial support are being invested in research and development programs. Fig 1.1 is depicting the advancement of technology in last few decades. The transistor count was exponentially increased in integrated circuits as predicted by Moore's Law. But there exists a fundamental geometrical limit which cannot be violated. At present time, semiconductor industry is facing tough challenges. With each technology node, it is getting clear that after a certain period of time, fundamental geometrical limits will be reached [2].

Therefore, to retain the performance trend, alternation of materials and innovation in geometrical structures in the field of Nanotechnology are the need of the hour. In this context the emergence of TFET took place in the field of electronics. TFETs can exhibit sub-threshold slope below 60 mV/decade due to a fundamental difference in the mechanism of current control as compared to MOSFETs. In MOSFETs, the current depends on the thermionic emission of free carriers across the potential barrier between the source and the channel. On the other hand, the current in TFETs depends on the charge carriers tunneling through a potential barrier between the source valence band and the channel conduction band. As this potential barrier is very wide in the OFF-state of the device, TFETs exhibit very low OFF-state current.

Figure 1.1: Moore's Law

Moreover TFETs have a greater immunity to these short channel effects. It may be pointed out that TFETs differ from the MOSFET only in the type of source doping. Therefore, the integration of the TFET fabrication process with the current MOSFET fabrication process would be easy.

# 1.2. A brief overview of TFET

Tunnel FETs use quantum-mechanical tunneling of electrons from the source to the channel as the primary carrier transport mechanism, allowing for sub-60 mV/dec subthreshold slopes.

# History

The origins of three-terminal devices come from the band-to-band tunneling component in a Trench Transistor Cell [3]. A three-terminal tunnel device using this effect was proposed by Sanjay Banerjee at Texas Instruments in 1987 [4]. This device required gate overlap of the source, a situation later known as line tunneling. Later in 1992, Toshio Baba at NEC proposed a surface tunnel transistor using GaAs and AlGaAs that utilized point tunneling [5]. In 1995, William Reddick at Cambridge proposed a Silicon device using point tunneling [6]. All of these devices showed low currents and no subthreshold slope under 60 mV/dec. In 2004, Jorge Appenzeller at IBM showed experimental characteristics less than 60 mV/dec with carbon nanotube based devices [7].

# **Device Principles**

Tunnel Field Effect Transistors (TFETs) use the tunneling of electrons as the carrier transport method for device operation. They are generally designed as gated pin diodes, where the gate is used to modulate an effective tunneling barrier height [8].

Ideally, these devices would have a very low off-state current (proportional to reverse biased diode leakage), a very low subthreshold slope, and acceptable on-current. TFETs can be generally classified as point and/or line tunneling devices [9]. In a point tunneling device, the source does not appreciably deplete, but the gate causes the channel region to invert, resulting in tunneling from the source to the channel. In a line tunneling device, the source is inverted (generally by engineering an overlapped gate with an optimized source doping profile), resulting in tunneling into the inversion layer, similar to Gate-Induced Drain Leakage (GIDL) [10-13].

#### Drawbacks

TFET is a relatively new technology. It is still evolving. So naturally there are some challenges and researchers are combatting it relentlessly. The primary concerns for researchers are low ON current and ambipolar conduction in TFETs. These drawbacks will be discussed elaborately in the following chapter.

#### 1.3. Motivation of Current Research

Some of the drawbacks of TFET technology is mentioned in the previous section of this introductory chapter. The motivation behind the present research work is to overcome these drawbacks [14]. Several transistor structures are explored to achieve

- (a) Better on current or better ON/OFF current ratio .

- (b) Reduced ambipolar conduction

The effect of source engineering in a drain engineered TFET is analyzed in this research work. Apart from this, an attempt has been made to establish a TFET structure as a very low power consuming device. It is shown that – lower the  $V_{ds}$ , better the performance .So it may be a solution for continuous degrading nano device performance in terms of power. And finally quantum mechanical characteristics are incorporated to perform the simulation in a double source single gate TFET [15-16] .As channel length is shrinked below 20 nm and source or drain thickness is scaled down to the range of 10 nm, it is important to incorporate quantum mechanical Schrodinger-Poisson model in simulation as well as analytical calculation [17-18]. An attempt has been made to do so in this research work.

# 1.4. Objective

The objective of this thesis work is to establish TFET as an application specific device. The present generation of low power electronics is awaiting a potential technological giant and TFET is a promising candidate to fill up the blank space [19-20]. But there are some challenges those are already mentioned. Once we can solve these issues, TFET may also be applied in commercial products. This thesis work is an attempt to demonstrate several geometrical TFET structures and their operating conditions so that it can fulfil the requirements of modern day low power electronics.

# 1.5. Organization of Thesis

The thesis is divided into five chapters and its outline is described as given below:

- Chapter I is an introductory chapter. In this chapter it is investigated that how the present work is relevant to other modern contemporary research works all around the globe. A very brief overview of TFET is provided here. Challenges of TFET technology are mentioned. Finally, the motivation and objective of the present work is discussed in this chapter.

- Chapter II presents the trends of various TFET technology in modern times and the theoretical background studies related to present research work in details. The drawbacks of MOSFETs are speculated and hence the emergence of TFETs are justified in this chapter. Different kind of existing TFETs are discussed. A brief literature review is presented too. A concise study of drain engineered TFET is conducted. Based on these background studies, the next footsteps are suggested in this chapter.

- ❖ In Chapter III the effect of source engineering in a drain engineered TFET is studied. This work is based on simulation in Silvaco Atlas. This is extension of the work that was already done by splitting the drain region of a TFET into two horizontal parts. In that case the ambipolar conduction is reduced. During this work, the effect of source engineering in this drain engineered TFET is extensively investigated. Due to differential doping in source region, a changed behavior is expected in the modified TFET. This design modification is aimed towards achieving better performance in terms of ON/OFF current ratio.

- Chapter IV contains analytical modeling and simulation based result of salient source double gate TFET structure. This salient source double gate TFET is an application specific device. Better SS is found when drain voltage is lower. Hence it is better for low power application. Moreover analytical surface potential model is verified by the help of simulation during this work. In this chapter, the proposed TFET is established as a better performing device than conventional double gate TFET.

- ❖ In Chapter V an attempt has been made to incorporate quantum confinement in DS-TFET (Double Source TFET) based on non-local tunneling model along with self-consistent Schrodinger-Poisson quantum model. Quantum confinement is considered in 1-D. As a result effective band gap and subsequent tunneling barrier width is increased. Hence the results obtained through quantum approach are more practical than semi-classical ones.

- Chapter VI is concluding chapter. Here the findings of all the works are summed up.

Conclusion of the works are discussed in this chapter. The relevance of the thesis work is once again analyzed. The utility of proposed structures are justified in this chapter.

#### References

- [1]. J. E. Lilienfeld, "Method and apparatus for controlling electric currents," U.S. Patent 1 745 175, 1930.

- [2]. Pritha Banerjee, Aman Mahajan and Subir Kumar Sarkar,"3-D Analytical Modeling of Gate Engineered Tri-gate SON MOSFET", IEEE International Conference on Devices for Integrated Circuits (DEVIC-17), Kalyani Govt. Engg. College, 23-24 March, 2017

- [3]. Banerjee, S., Richardson, W., Coleman, J., & Chatterjee, A. "A new three-terminal tunnel device." Electron Device Letters, IEEE, 8 347 349 (1987).

- [4]. Baba, T. "Proposal for Surface Tunnel Transistors." Japanese Journal of Applied Physics, 31 http://jjap.jsap.jp/link?JJAP/31/L455/L455-L457 (1992).

- [5]. Reddick, W. M. & Amaratunga, G. A. J. "Silicon surface tunnel transistor." Applied Physics Letters, 67 http://link.aip.org/link/?APL/67/494/1 494-496 (1995).

- [6]. Appenzeller, J., Lin, Y.-M., Knoch, J., & Avouris, P. "Band-to-Band Tunneling in Carbon Nanotube Field-Effect Transistors." Phys. Rev. Lett., 93 196805 (2004).

- [7]. Nayfeh, O. M., Chleirigh, C. N., Hennessy, J., Gomez, L., Hoyt, J. L., & Antoniadis, D. A. "Design of Tunneling Field-Effect Transistors Using Strained- Silicon/Strained-Germanium Type-II Staggered Heterojunctions." Electron Device Letters, IEEE, 29 1074 -1077 (2008).

- [8]. Vandenberghe, W., Verhulst, A. S., Groeseneken, G., Soree, B., & Magnus, W. "Analytical model for point and line tunneling in a tunnel field-effect transistor." Simulation of Semiconductor Processes and Devices, 2008. SISPAD 2008. International Conference on, 137-140 (2008).

- [9]. Lu, Y., Bangsaruntip, S., Wang, X., Zhang, L., Nishi, Y., & Dai, H. "DNA Functionalization of Carbon Nanotubes for Ultrathin Atomic Layer Deposition of High κ Dielectrics for Nanotube Transistors with 60 mV/Decade Switching." Journal of the American Chemical Society, 128 http://pubs.acs.org/doi/abs/10.1021/ja058836v 3518- 3519 (2006).

- [10]. J.Bag,Rashmi Ranjan Sahoo, P.K.Dutta and Subir Kumar Sarkar, "Design and VLSI Implementation of Power Efficient Processor for object localization in Large WSN," Int. J. High Performance Systems Architecture, Inderscience Journal, Vol 4, No. 4, pp-204-217, 2013.

- [11]. Priyanka Saha, Dinesh Kumar Dash, Subhramita Basak and Subir Kumar Sarkar, "Asymmetric Junctionless Double Gate (JLDG) Silicon on Nothing (SON) MOSFET Modified with the Concept of Work Function Engineering: A Comparative Performance Study", in 1st 'International Conference on VLSI Device, Circuit and System' (VLSI DCS 2016), 19th-20th October,2016, Meghnad Saha Institute of Technology, Kolkata, India.

- [12]. B. Davari, R. H. Dennard, and G. G. Shahidi, "CMOS scaling for high-performance and low-power—the next ten years," Proc. IEEE, vol. 89, pp. 595–606, Apr. 1995.

- [13]. Joyashree Bag and Subir Kumar Sarkar, "Development and VLSI implementation of a data security scheme for RFID system using programmable cellular automata" International Journal Radio Frequency Identification Technology and Applications, Vol. 4, No. 2, Pp. 197-211, 2013.

- [14]. Navjeet Bagga, Saheli Sarkhel and Subir Kumar Sarkar" Exploring the Asymmetric Characteristics of a Double Gate MOSFET with Linearly Graded Binary Metal Alloy Gate Electrode for Enhanced Performance ",IETE Journal Of Research, DOI 10.1080/03772063.2016.1176542, April, 2016

- [15]. E. M. Conwell, "High Field Transport in Semiconductors", Solid State Physics Supplement 9 (Academic Press, New York, 1967).

- [16]. Suman Basu, Samir Kumar Sarkar and Subir Kumar Sarkar, "Exploring Novel Characteristics of Strain Compensated SiGeC Nanoscale MOSFET," Indian Journal of Physics, Volume 87, Issue 4, pp 333-338, April 2013.

- [17]. Ankush Ghosh, J. Gope, T. Datta, Biplab Roy and Subir Kumar Sarkar, "Spintronic Device Based Power Efficient VLSI Chip Design for Universal Code Converter", Canadian Journal of Pure and Applied Sciences, Vol. 2, No. 3, pp. 469-474, 2008

- [18]. Sudip Dogra, Joyashree Bag, Subir Kumar Sarkar, "Development & VLSI Implementation of a new scheme for Traffic Management using RFID with least stoppage time facility to Priority Cars." International Journal on Recent Trends in Engineering & Technology, Association of computer Electronics and Electrical Engineering. ACEEE; pages 177-181); 2011.

- [19]. V. H. Mankar, T. S. Das and Subir Kumar Sarkar,, "Cellular Automata based Robust Watermarking Architecture towards the VLSI realization" International Journal of Computer Science, VOL.2 No.3, 2008.

- [20]. Navjeet Bagga, Saheli Sarkhel and Subir Kumar Sarkar, "Recent Research Trends in Gate Engineered Tunnel FET for Improved Current Behavior by subduing the Ambipolar Effects: A Review", IEEE International conference on computing, communication and automation (ICCCA2015), Galgotias University, Noida, 15th -16th May 2015.

# **CHAPTER 2**

# BACKGROUND STUDY PRIOR TO THE RESEARCH WORK AND LITERATURE REVIEW

- 2.1. Introduction

- 2.2. Evolution of transistor

- 2.3. Timeline of electronics from 1947

- 2.4. Technological Limitations of MOSFETs

- 2.4.1. Drain-induced barrier lowering

- 2.4.2. Threshold voltage roll off,

- 2.4.3. Surface scattering,

- 2.4.4. Velocity saturation

- 2.4.5. Hot electron effect

- 2.5. Introduction to TFET

- 2.6. Major shortcoming of TFET

- 2.6.1. Low on current

- 2.6.2. Ambipolar current conduction

- 2.7. Structural difference of TFET and MOSFET

- 2.8. Performance dependence on several parameters of device

- 2.8.1. Doping

- 2.8.2. Gate work function

- 2.8.3. Gate Oxide

- 2.9. Different types of existing TFET

- 2.9.1. Planar TFET

- 2.9.2. Three dimensional TFET

- 2.10. Drain engineered TFET

- 2.10.1. Device structure and parameter

- 2.10.2. Observations

- 2.11. Literature review

- 2.12. Next footstep

- 2.13. Simulation software

- 2.14. Quantum simulation

References

# **CHAPTER 2**

# BACKGROUND STUDY PRIOR TO THE RESEARCH WORK AND LITERATURE REVIEW

## 2.1 Introduction

In previous chapter we mentioned the problem statements of TFET technology. Primarily researchers have three objectives

- (a) To increase ON current

- (b) To reduce ambipolar conduction.

- (c) To minimize sub-threshold slope of the transfer characteristics.

In this chapter we will learn the prerequisites to conduct this research work.

# 2.2. Evolution of transistor

John Bardeen, William Shockley and Walter Brattain created history in 1947 at Bell Telephone Laboratories when they invented transistor. Hence an unprecedented milestone was set in the field of semiconductor industry. Thereafter we gradually entered into the era of LSI (Large–Scale–Integration), VLSI (Very–Large–Scale–Integration) and ULSI (Ultra–Large–Scale–Integration) to compensate the ungratified demand of more compact, cheaper and faster electronic devices. Incessant downscaling has made this progress possible and sustained Moore's Law till now. But currently, the semiconductor industry has reached a dipping point as further progress in traditional CMOS technology is hindered due to a bunch of challenges. These challenges will be discussed in the following sections of this chapter. Fig 2.1. indicates versatile application specific aspects of down sized transistors.

Fig.2.1. Evolution of Transistor

## 2.3. Timeline of electronics since 1947

- 1947 First point contact transistor was invented.

- 1952 Transistor was commercially used for the first time

- 1954 First mass produced transistors were demonstrated.

- 1954 Transistor radio was invented.

- 1955 Silicon dioxide was discovered.

- 1958 Integrated circuit was invented.

- 1962 MOSFET was invented.

- 1966 Self-aligned gate process was invented for fabrication of FETs.

- 1967 First handheld calculator.

- 1968- Molecular beam epitaxy was developed at Bell lab.

- 1971- Computer on a chip was introduced by Intel.

- 1972- Home video games are commercially available.

- 1974- TMS 1000 was introduced by Texas Instruments.

- 1980- Built in self-testing technology in circuit board.

- 1998- Plastic transistors was invented.

# 2.4. Technological Limitations of MOSFETs

As device channel length is continuously decreased, gate control over channel deteriorates due to enhanced nearness of MOSFET's source and drain. As a result, Short–Channel–Effects (SCEs) become a serious challenge associated with downscaled MOSFETs. When the channel length is shrunk to the order of source and drain depletion-layer width SCE s emerges. SCEs lead to several reliability issues as the basic device parameters (such as threshold voltage), become dependent on channel length[3-10].

Five different short-channel effects are:

- 1. Drain-induced barrier lowering

- 2. Threshold voltage roll off,

- 3. Surface scattering,

- 4. Velocity saturation and

- 5. Hot electron effect

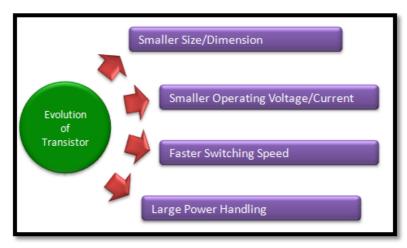

# **2.4.1.** Drain-Induced Barrier-Lowering (DIBL):

The drain voltage is able to impact strongly on the channel region as the dimensions of a MOSFET transistor are reduced. This undesirable effect is called Drain –Induced – Barrier – Lowering (DIBL). DIBL effect takes place when the barrier height for carriers at the source end reduces due to influence

of drain electric field, upon application of a high  $V_{ds}$  (as shown in Fig. 2.2). As a result the number of charge carriers injected into channel region from the source increases leading to an enhanced off-current. Thus the drain current is not controlled only by  $V_{gs}$ , but also by  $V_{ds}$ .

Fig 2.2. Surface potential along the position in channel for  $V_{DS} = 0.1 \text{ V}$  and 1.5 V [1]

Fig 2.3. Three mechanisms determining SCEs [1]

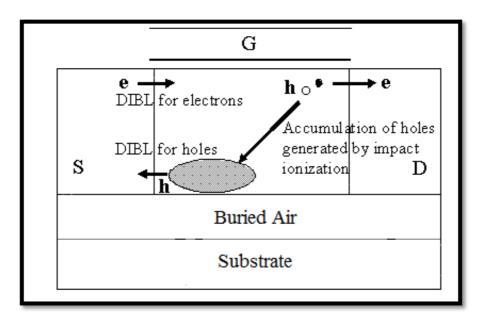

Apart from DIBL, there are two features determining short channel effects in thin-film SON devices viz. (a) positive bias effect to device body due to accumulation of holes. These holes are generated through impact ionization near drain and (b) the DIBL effect on barrier for holes at the source edge near the bottom, as illustrated in Fig. 2.3. [1]

DIBL can be calculated as follows:

$$DIBL = \frac{V_{th}^{dd} - V_{th}^{low}}{V_{td} - V_{td}^{low}}$$

$$\tag{2.1}$$

Where,  $V_{th}^{dd}$  is the threshold voltage measured for high drain bias (the supply voltage), and  $V_{th}^{low}$  is the threshold voltage measured for low drain bias, typically 0.05 Volt or 0.1 Volt.

$V_{dd}$  is the supply voltage and  $V_{dd}^{low}$  is low drain voltage (for linear part of I-V characteristics).

Another process for measuring DIBL, called the Voltage-Doping Transformation model (VDT) [38] is used to evaluate the dependence of DIBL on the transistor parameters like oxide thickness, gate length or drain to source voltage. According to this model, DIBL is expressed as [39]:

$$DIBL = 0.80 \frac{\varepsilon_{Si}}{\varepsilon_{ox}} \left[ 1 + \frac{x_j^2}{L_{el}^2} \right] \frac{t_{ox}}{L_{el}} \frac{t_{dep}}{L_{el}} V_{DS}$$

(2.2)

Where Lel is the effective (electrical) channel length,

V<sub>bi</sub> =built-in potential,

$t_{ox}$  = oxide thickness,

$x_i$  = source or drain junction width

$t_{dep}$  = penetration depth of gate field in channel.

However, transistor normally does not work at a low drain bias. Hence DIBL is not a parameter, directly related to circuit operation, but rather it depicts the degradation of device characteristics such as strong threshold voltage roll-off (V<sub>th</sub> roll-off) and high off current (I<sub>OFF</sub>) in subthreshold region. Typically, DIBL is measured in mV/V.

# 2.4.2. Threshold Voltage Roll-Off

The expression of Short-Channel Effect (SCE) can be derived from the above mentioned VDT model [39]:

$$SCE = 0.64 \frac{\varepsilon_{Si}}{\varepsilon_{ox}} \left[ 1 + \frac{x_j^2}{L_{el}^2} \right] \frac{t_{ox}}{L_{el}} \frac{t_{dep}}{L_{el}} V_{bi}$$

(2.3)

From the expressions of (2.2) and (2.3), the threshold voltage ( $V_{th}$ ) of MOSFET can be deduced as:

$$V_{th} = V_{th\infty} - DIBL - SCE \tag{2.4}$$

This is typically measured in mV/nm. [39]

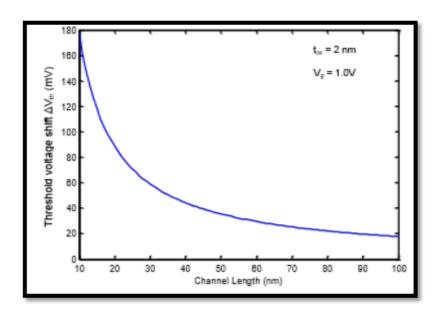

Fig. 2.4. Threshold voltage shift with channel length

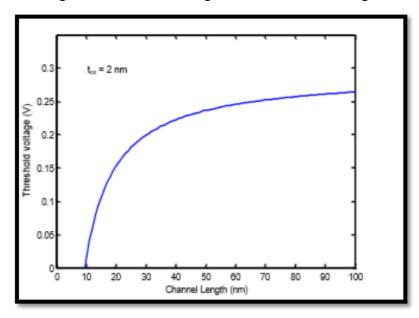

Fig. 2.5. Threshold voltage roll-off for nano scale FinFET

# 2.4.3. Surface scattering

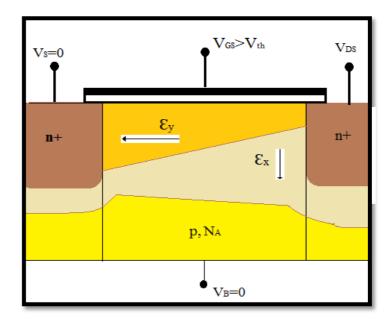

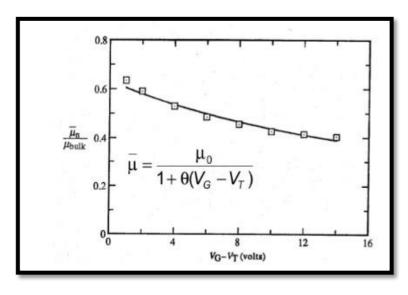

Electric field's longitudinal component ( $\epsilon_y$ ) increases as the channel length shrinks as a result of lateral extension of depletion layer into channel region, and at the same time the mobility becomes electric field-dependent.[1] The collisions encountered by the electrons those are accelerated towards interface primarily due to influence of the electric field's horizontal component ( $\epsilon_x$ ), is called *surface scattering*. This phenomenon causes reduction of mobility [1]. As the carrier transport in MOSFET is confined within narrow inversion layer, the electrons face greater trouble in moving parallel to the interface. Therefore, even for small  $\epsilon_y$ , the average surface mobility is roughly half of the bulk mobility. We can get an idea of the mutual dependence of mobility, gate voltage and the threshold voltage from Fig 2.7.

Fig. 2.6. Cross section view of MOSFET

Fig. 2.7. Mobility dependence on gate voltage

# 2.4.4. Velocity saturation

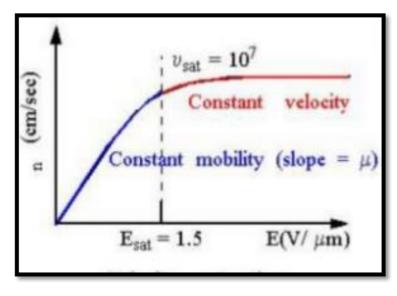

The next important SCE that we will cover in this chapter is "velocity saturation" which is the consequence of a high lateral electric field ( $\varepsilon_y$ ) along the scaled channel. At low  $\varepsilon_y$ , the drift velocity of mobile carriers in the channel region varies linearly with the intensity of electric field. However, as  $\varepsilon_y$  raises above  $10^4$  V/cm, the drift velocity increases more slowly, and approaches to the saturation limit of  $10^7$  cm/s around  $\varepsilon_y=10^5$  V/cm at 300 K. Here, the drain current is limited by velocity saturation

leading to reduction of the transconductance in saturation mode. After incorporating velocity saturation, the maximum transconductance  $(g_m)$  achievable by a MOSFET is given as

$$g_m = WC_{ox}V_{de(sat)} \tag{2.5}$$

Fig. 2.8. Velocity Saturation

#### 2.4.5. Hot Electron Effect

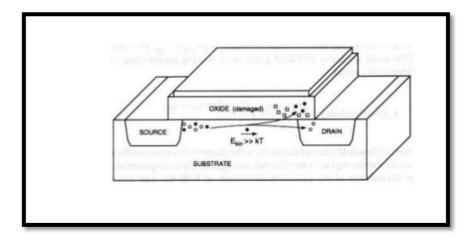

Another problem originated from the high electric field and short channel, that degrades the behavior of MOSFET devices is called "hot electron effect" (Fig. 2.9). Electrons acquire a large amount of energy from that electric field and they forcefully enter the oxide. In this oxide region the electrons can be trapped; hence the charge density is increased. These charges can accumulate with time. Moreover these charges can degrade the performance of the device by increasing threshold voltage and reducing the gate's control on drain current. In case of semiconductor devices, the *hot electron effect* occurs where the electrons can rise above the conduction band. Instead of being conducted to a collector through the material or recombining with holes, these 'hot' electrons can penetrate the semiconductor material. These electrons generally give away their excess energy as phonons. Also, in MOSFETs, the hot electrons may jump from the drain to the gate or the substrate. Therefore, consequent effects of this phenomenon include heating of the device, and increased leakage current.

Apart from short channel effects MOSFET has limitation in terms of Sub-threshold swing. Maximum SS achievable in MOSFET is 60 mV/decade. To overcome these shortcomings researchers carried on their research vigorously and as a result Tunneling Field Effect Transistor came into the picture. In the next section, we will look into basics of TFET.

Fig. 2.9. Hot electron effect

#### 2.5. Introduction to TFET

Researchers' relentless efforts made us move towards the era of low power and high-speed with enhanced device packing density [1] This introduces devices with dimensions in nano metre range as well as better RF performance. In previous section we studied that MOSFET s have major disadvantages like high leakage, more power dissipation, various short channel effects and threshold voltage roll off when we move towards nano-regime . Hence emergence of technologies like TFET was inevitable. It is found that TFET devices performs better than MOSFET devices when channel length is scaled down. The predominant advantage of TFET is current conduction through modulation of quantum mechanical Band-to-Band Tunneling (BTBT), which is a result of finite, but non-zero, probability of tunneling through a potential barrier, a process in which electrons tunnel from the valence band through the semiconductor bandgap to the conduction band or vice versa without any trap assistance. This merit carries forward the advantages over the thermionic injection across an energy barrier for carrier transport in MOSFET. Thus, due to its built-in tunnel barrier, where the channel current in TFET is controlled by tunneling mechanism from the source, the TFET device is immuned to short channel effect and the subthreshold swing of conventional TFET is usually under 60 mV/decade at 300 K, allowing TFETs to have SS as low as 20 mv/decade, which is the main reason to design low voltage, less power consuming operating devices in this technology.

# **Basic Operation of TFET**

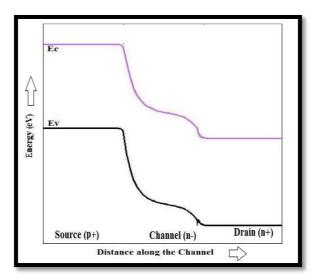

# (i) Thermal Equilibrium

Band diagram of a TFET with no external bias (i.e Vgs=Vds=0) in thermal equilibrium is shown in Figure 2.10. Two depletion regions are formed in this case, one each at the source–channel junction and the channel–drain junction [1].

Figure 2.10. Band diagram of a n-channel TFET at zero bias[1].

# (ii) Off State

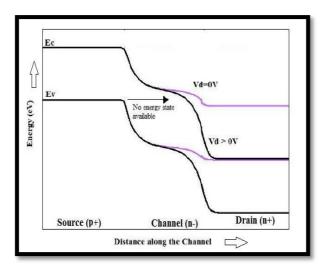

The TFET stays OFF when  $V_{ds}>0$  and  $V_{gs}=0$ . The energy band diagram for OFF state is shown in Figure 2.11. Current is generated in off state due to the existence of carriers in the conduction band. These carriers drift towards drain and hence current is generated. But in n-channel TFET the source is p-type. Therefore, very few free electrons is present in conduction band unlike MOSFET s. This causes negligible OFF current.

Figure 2.11. Band diagram of a TFET in the OFF-state at  $V_{gs}$ = 0 V [1].

# (iii) On State

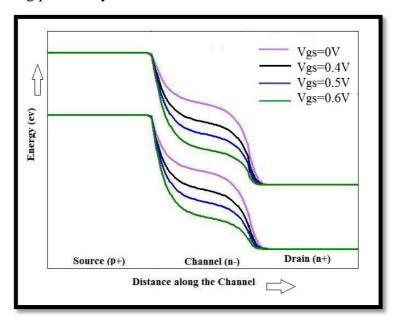

As *Vgs* is increased the energy band level varies as shown in Fig. 2.12. At a certain value of the gate voltage *Vgs*, the valence band in the source gets aligned with the conduction band in the channel. Now the electrons can conduct tunneling from valence band to conduction band through the barrier caused by the band gap. As *Vgs* is further increased, the bands present in the channel region are further lowered in energy resulting more electrons to tunnel. This leads to a steep increase in the current because of the increase of tunneling probability.

Figure 2.12. Band diagram along the surface of the TFET for (Vgs= 0, 0.4, 0.5, 0.6) in the ON-state [1].

# 2.6. Major shortcomings of TFET

There are several shortcomings in TFET technology. Two of them are most predominant and are the area of interest for present day researcher scholars. Those are following

- 2.6.1. Low on current

- 2.6.2. Ambipolar current conduction

# 2.6.1. Low on current in TFET

In n channel TFET the source is of p type. Hence the carriers present in conduction band is much less than MOSFET s. As a result lesser number of current carriers are injected into the channel. This phenomenon leads to low on current in TFET devices.

In MOSFET devices current is achievable in milli-ampere range whereas in TFET devices normally current is achieved in microampere range that is thousand times smaller.

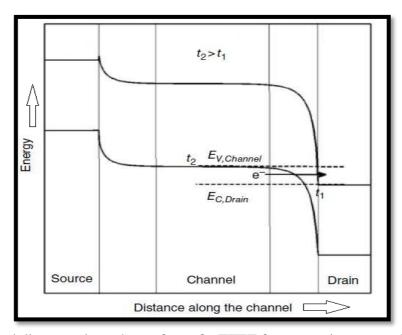

# 2.6.2 Ambipolar current conduction

As *Vgs* is decreased below 0 V, the valence band of the channel is aligned with the conduction band of the drain, and the electrons from the valence band of the channel tunnels into the conduction band of the drain, resulting in a current flow. The electrons tunnel in same direction as in the case of positive gate bias. This phenomenon results in the device current having the same polarity even at a negative gate bias. This is called ambipolar conduction and is shown in Figure 2.13.

Figure 2.13. Band diagram along the surface of a TFET for a negative gate voltage (Vgs) and a positive drain voltage (Vds) [1].

## 2.7. Structural difference of TFET and MOSFET

As shown in Fig.2.14 and Fig. 2.15, N- channel MOSFET has n-type source and n-type drain unlike TFET. This is why carrier injection rate is higher in MOSFET than in TFET. Consequently, both leakage current and operating on current is much less in TFET than in MOSFET. Moreover, carrier transport mechanism is different in MOSFET and TFET. In MOSFETs current is generated through thermionic emission mechanism whereas in TFET tunneling takes place [1].

Figure 2.14. N-channel TFET

Figure 2.15. N-channel MOSFET

# 2.8. Performance dependence on several parameters of device

Device parameters like doping, gate work function, gate oxide permittivity etc. cause variation in TFET performance. Researchers have to optimize these parameters. Now, we will study these performance dependences briefly.

# **2.8.1 Doping**

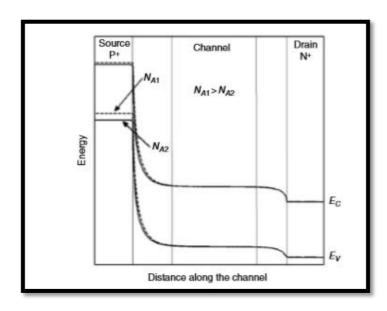

If we dope source region heavily, a narrower depletion region is formed in the source side. Hence tunneling width is lesser than in the case of low doped source region as shown in Fig. 2.16. This is the reason why larger on current is achievable in case of heavily doped source region. Similarly drain region should be doped moderately to curb ambipolar conduction as tunneling in the channel-drain junction is an unwanted phenomena in TFET.

Figure 2.16. Band diagrams along the surface of an n-channel TFET with different values of source doping concentration. [1]

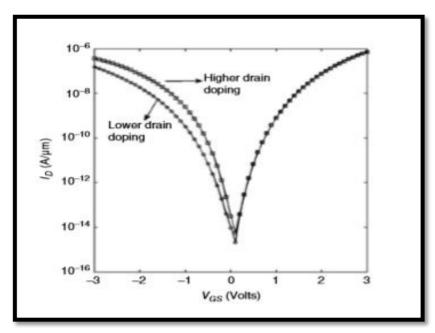

Figure 2.17. Transfer characteristics of an n-channel TFET with different drain doping concentrations for a fixed drain voltage (VDS). [1]

### 2.8.2. Gate work function

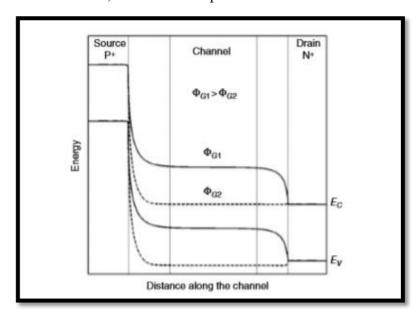

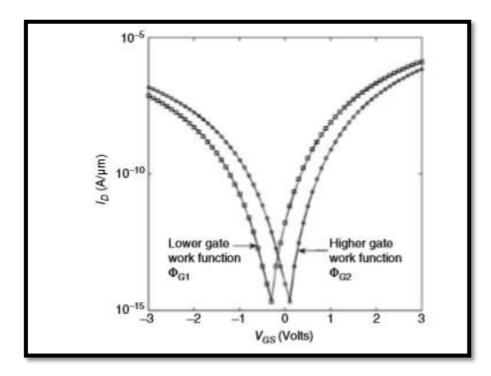

From fig. 2.18 and 2.19. we can understand that if we decrease the gate work function, source channel tunneling is increased and channel drain tunneling is decreased. Consequently right hand curve of the transfer characteristics is raised whereas the left hand curve of the transfer characteristics is lowered along current-axis. Hence, curve's central point is shifted towards left.

Figure 2.18. Band diagram along the surface of an n-channel TFET for different values of the gate work function.

Figure 2.19. Transfer characteristics of an n-channel TFET with different values of the gate work function.

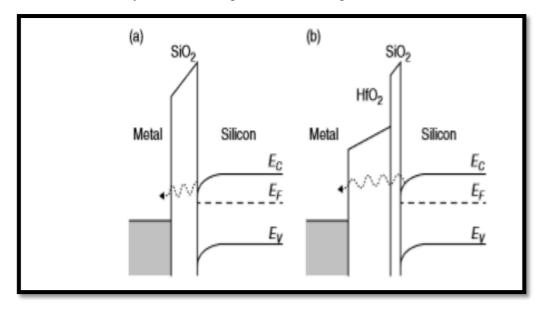

### 2.8.3. Gate Oxide

We know  $C_{ox} = \mathcal{E}_{ox}/t_{ox}$ . More the oxide capacitance, more the gate-control over channel. To increase oxide capacitance we can use oxides with higher permittivity and also we can reduce the thickness of the oxide layer. But in latter case, more leakage current will be present as tunneling probability is more due to the thin oxide layer. Gate leakage is shown in Fig. 2.20.

Figure 2.20. Gate leakage in a TFET through (a) SiO2 and (b) HfO2/SiO2 gate stack [2].

### 2.9. Different types of existing TFET

Broadly we can classify TFET in two categories

- (a) Planar TFET Here current carrying surface is planar.

- (b) Three dimensional TFET In this case current carrying surface is three dimensional.

### 2.9.1 Planar TFET

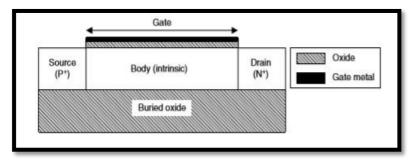

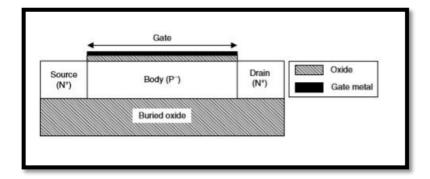

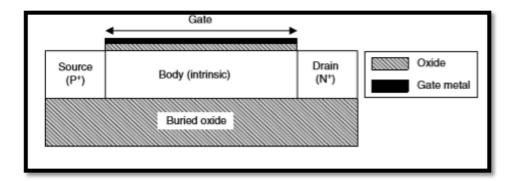

Generally in SOI TFET a thin silicon layer (in order of 10 nm) is grown on a thick buried oxide layer (in order of 100 nm). This buried oxide layer blocks leakage currents through the bulk region.

Figure 2.21. P-channel SOI TFET

Different types of already existing planar TFETs are as follows

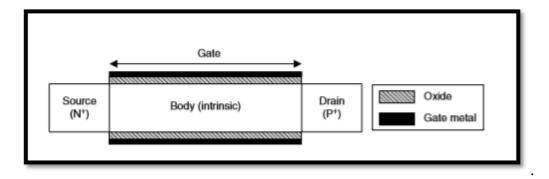

### (a) Double gate TFET

This TFET structure consists of two gates. One at the top end and is known as front gate .Other one is at the bottom end and is called back gate. The presence of two gates increases the controllability over the channel

Figure 2.22. P-channel double gate TFET

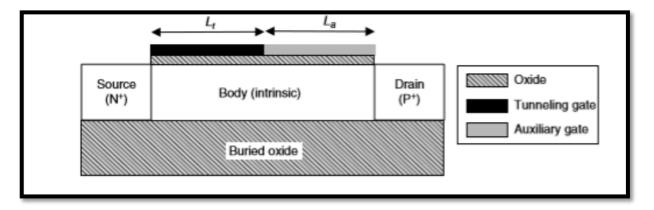

### (b) Dual material gate TFET

A schematic of dual material gate TFET is shown in fig. 2.23 In this structure gate consists of two materials. Gate near the source end is called tunneling gate and the gate near the drain end is called auxiliary gate. The fabrication of this device is possible using sidewall spacer technique. [3]-[5]

Figure 2.23. P-channel dual material gate TFET

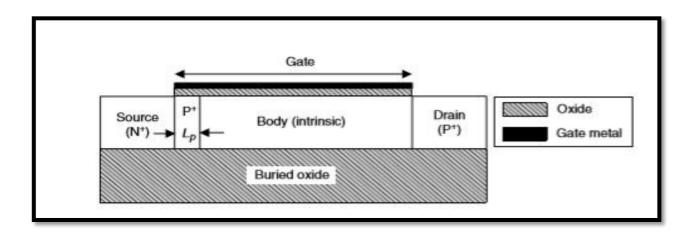

### (c) p-n-p-n TFET

A schematic of p-n-p-n TFET structure is shown in figure 2.24. The narrow P+ pocket near the source-channel junction results to narrower tunneling width. Hence, this structure can provide larger ON current than the conventional one.

Figure 2.24. p-n-p-n TFET

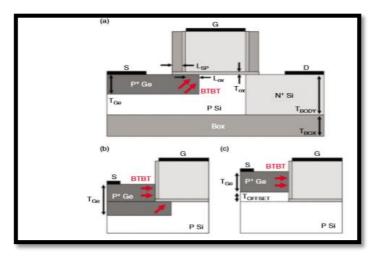

### (d) Raised Ge-source TFET

Silicon TFETs have a limitation of low on current . To overcome this limitation low bandgap material germanium is used. Moreover the advantage of raised source structure is that more tunneling area is provided. Hence, more on current can be achieved. Apart from that,this structure provides steeper subthreshold swing than the conventional TFET.

Figure 2.25. Schematic of (a) planar, (b) partially raised and (c) fully raised Ge-source TFETs.

Directions of tunneling in each case are shown by arrows [6].

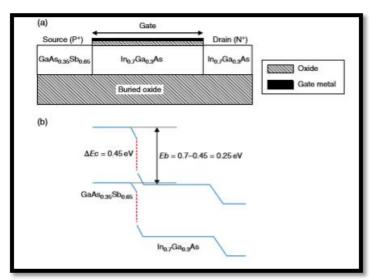

### (e) Heterojunction TFET

Heterojunction TFET consists of III-V materials instead of silicon. As shown in fig. 2.26. (b) band diagram is staggered near the source-channel junction. Consequently tunneling width becomes less and large on current is achievable.

Figure 2.26. (a) Schematic view of an n-channel heterojunction TFET. (b) Band diagram of the heterojunction TFET shown in (a) [7].

### (f) Ferroelectric TFET

In ferroelectric TFET a ferroelectric stack material is used between gate metal and oxide. When Gate voltage is applied ,effective gate voltage is increased due to the polarization of ferroelectric material [8] .Hence on current is increased in this type of TFET than conventional ones.

Figure 2.27. P-channel ferroelectric TFET

Moreover, ferroelectric TFET also gives better performance in terms of subthreshold swing. This is depicted in figure 2.28.

Figure 2.28. Comparison of the ID–VGS curves of a ferroelectric TFET with that of a MOSFET and a conventional TFET [8]

### 2.9.2 Three dimensional TFET

In three dimensional TFET s current carrying surface exists along three dimension. Most popular 3D TFET s are gate all around nano-wire TFET and tri-gate TFET.

### (a) Gate all around nano-wire TFET

In this structure 2 nm thick gate oxide surrounds silicon nanowire of radius 10 nm .And oxide is covered all around by gate metal. This TFET achieves better gate control over channel than double gate TFET [9]-[15].

Figure 2.29. Gate all around nanowire TFET

### (b) Tri-gate TFET

Tri-gate TFET s are being produced commercially by Intel. It is simpler to fabricate than gate all around nanowire TFET. Short channel effects are done away with in this structure. It also performs better in terms of on current and subthreshold swing.

Figure 2.30. Tri-gate TFET

### 2.10. Drain Engineered TFET

Splitted drain structure displays considerable reduction in ambipolar conduction due to increase of the tunneling width at the channel-drain junction [17]. Based on this a research work was conducted .[18]. In this extended work four TFET structures are considered.

- (a) Splitted-Drain Single-Gate TFET (SD-SG TFET: total drain is splitted),

- (b) Top-Splitted-Drain Single-Gate TFET (TSD-SG TFET: splitted-drain in upper location),

- (c) Mesial-Splitted-Drain Single-Gate TFET (MSD-SG TFET: splitted-drain in middle location),

- (d) Basal-Splitted-Drain Single-Gate TFET (BSD-SG TFET: splitted-drain in bottom location).

### 2.10.1 Device structure and parameter

The 2-D cross-sectional view of the p-channel TFET structures are given in Fig. 2.31. (a) Splitted-Drain Single-Gate TFET (SD-SG TFET), (b) Top-Splitted-Drain Single-Gate TFET (TSD-SG TFET), (c) Mesial-Splitted-Drain Single-Gate TFET (MSD-SG TFET) and (d) Basal-Splitted-Drain Single-Gate TFET (BSD-SG TFET). The structures contain two separate drain regions of different concentration instead of a single doped drain region present in a conventional TFET. The highly-doped drain region is above the lightly doped region. The Doping specification of the TFET models are: P+ type source region  $(1\times10^{20}\text{cm}^{-3})$  and P channel region  $(1\times10^{17}\text{ cm}^{-3})$ , which are kept constant for all the simulations. Such doping concentration create a tunnel junction between source and channel where the phenomenon of inter-band tunneling occur for the TFET to conduct in N-mode. The doping specification of the upper N+ doped drain region is  $5\times10^{18}$  cm<sup>-3</sup>, drain electrode has the Ohmic contact with this higher doped drain region. The lower N doped drain region is  $1 \times 10^{17}$  cm<sup>-3</sup>. Both disparate drain regions are variably doped to attain an optimal doping profile after analyzing the simulated graphs of all the characteristics. The device is simulated with lateral dimensions of 70nm, 50nm, 70nm for source, gate and drain respectively and a total device length of 250nm. A 30nm oxide overlapped depletion region is present in both side of source and drain, this region is to reduce impact ionization and improve ON current. The vertical dimensions of Si ground plane and SiO<sub>2</sub> spacer is 20 nm and 20nm respectively. The length of the both parted drain regions D1 and D2 are varied to get the optimal dimensions for better characterizations and in these structures, both drain parts vertical lengths are 30nm each for SD-SG TFET and 5nm for other three TSD-SG TFET, MSD-SG TFET, BSD-SG TFET. The dielectric used for gate electrode is  $SiO_2$ , which has a thickness of  $t_{ox} = 1$ nmand dielectric constant is 3.9. Table 2.1 summarizes all the parameters for all the structures [19]-[26].

**Table 2.1 Device Parameters**

| Parameters                 | Symbol            | SD-SG              | TSD-               | MSD-SG             | <b>BSD-SG</b>      |

|----------------------------|-------------------|--------------------|--------------------|--------------------|--------------------|

| name/unit                  |                   | TFET               | SG                 | TFET               | TFET               |

|                            |                   |                    | TFET               |                    |                    |

| Source doping              | $N_s$             | $1 \times 10^{20}$ | $1 \times 10^{20}$ | $1 \times 10^{20}$ | $1 \times 10^{20}$ |

| $(cm^{-3})$                |                   |                    |                    |                    |                    |

| Channel                    | $N_{ch}$          | 1×10 <sup>17</sup> | 1×10 <sup>17</sup> | 1×10 <sup>17</sup> | $1 \times 10^{17}$ |

| doping(cm <sup>-3</sup> )  | <b>&gt;</b> 7     | z 1018             | <b>5</b> 1018      | <b>5</b> 1018      | <b>5</b> 1018      |

| Drain doping               | N <sub>D1</sub>   | 5×10 <sup>18</sup> | 5×10 <sup>18</sup> | 5×10 <sup>18</sup> | 5×10 <sup>18</sup> |

| (cm <sup>-3</sup> )        | $N_{D2}$          | 1×10 <sup>17</sup> | 1×10 <sup>17</sup> | 1×10 <sup>17</sup> | $1 \times 10^{17}$ |

| Substrate                  | $n_{\rm i}$       | $1 \times 10^{17}$ | $1 \times 10^{17}$ | 1×10 <sup>17</sup> | $1 \times 10^{17}$ |

| doping (cm <sup>-3</sup> ) |                   |                    |                    |                    |                    |

| source length              | $X_s$             | 100                | 100                | 100                | 100                |

| (nm)                       |                   | <b>50</b>          | 70                 | 70                 | <b>5</b> 0         |

| Channel Length             | L                 | 50                 | 50                 | 50                 | 50                 |

| (nm)<br>Effective          | Т                 | 50                 | 50                 | 60                 | 70                 |

| Channel Length             | Leff              | 30                 | 30                 | 00                 | 70                 |

| (nm)                       |                   |                    |                    |                    |                    |

| Drain Length               | X <sub>d</sub>    | 100                | 100                | 100                | 100                |

| (nm)                       | 7 <b>L</b> u      | 100                | 100                | 100                | 100                |

| source width               | Ys                | 60                 | 60                 | 60                 | 60                 |

| (nm)                       |                   |                    |                    |                    |                    |

| Channel width              | W                 | 60                 | 60                 | 60                 | 60                 |

| (nm)                       |                   |                    |                    |                    |                    |

| Drain width                | $Y_{d1}, Y_{d2}$  | 30, 30             | 5,5                | 5,5                | 5,5                |

| (nm)                       | _                 |                    |                    |                    |                    |

| Length of                  | $L_{\mathrm{ED}}$ | 70                 | 5                  | 5                  | 5                  |

| electrical drain           |                   |                    |                    |                    |                    |

| (nm)                       | Т.                | 60                 | 60                 | 60                 | 60                 |

| Silicon body thickness     | $T_{si}$          | UU                 | UU                 | 00                 | UU                 |

| Oxide thickness            | T <sub>ox</sub>   | 1                  | 1                  | 1                  | 1                  |

| (nm)                       | ± OX              | 1                  | 1                  | 1                  | 1                  |

| Work function              | Øms               | 4.1                | 4.1                | 4.1                | 4.1                |

| of control gate            |                   |                    |                    |                    |                    |

| (eV)                       |                   |                    |                    |                    |                    |

| Substrate, box             | T <sub>box</sub>  | 20                 | 20                 | 20                 | 20                 |

| thickness (nm)             |                   |                    |                    |                    |                    |

Figure 2.31. Device Structure of (a) Splitted-Drain Single-Gate TFET (SD-SG TFET), (b) Top-Splitted-Drain Single-Gate TFET (TSD-SG TFET), (c) Mesial-Splitted-Drain Single-Gate TFET (MSD-SG TFET) and (d) Basal-Splitted-Drain Single-Gate TFET (BSD-SG TFET)

### 2.10.2. Observations