## B. Sc. Physics (Honours) Examination, 2023

(2nd Year, 1st Semester)

## DIGITAL SYSTEMS AND APPLICATIONS

## Paper - CORE 07

Time: Two hours Full Marks: 40

Answer question 1 and *any three* from the rest.

## 1. Answer any eight questions:

$8 \times 2$

- (a) (1) 010011.11 + (0) 010111.11 =

- (i) (0) 110100.11

- (ii) (1) 001100.01

- (iii) (1) 010100.10

- (iv) (0) 010110.10

- (b) The arithmetic operations  $(\sqrt{44})_r = (6)_r$  is correct for r =

- (i) 6

- (ii) 8

- (iii) 7.5

(iv) 12

- (c) Hexadecimal equivalent of 171.875 is

- (i) AB.7

- (ii) AB.E

- (iii)AA.7

(iv) AA.E

- (d)  $A + \overline{A}B + \overline{A}\overline{B}C + \overline{A}\overline{B}\overline{C}D + \dots =$

- (i)  $\overline{A} + \overline{B} + \overline{C} + \overline{D} + \dots$  (ii)  $A + B + C + \dots$

- (iii) 1

- (iv) 0

- (e) If  $A \oplus B = C$ , then  $A\overline{C} + \overline{A}C =$

- (i) C

- (ii) B

- (iii) AB

- (iv) A+B

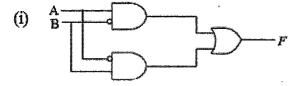

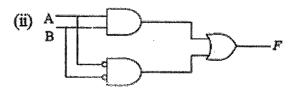

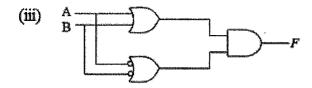

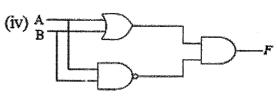

(f) Which of the following circuit does not satisfy the Boolean expression  $A\overline{B} + \overline{A}B = F$

- (g) A MUX has 200 input lines. No. of switches it has.

- (i) 9

- (ii) 7

- (iii) 8

- (iv)10

[ Turn Over

(h) A counter using 4 flip flop can be configured to use as divide by N signal. What are the realizable values of N?

- (i) 7, 13,19

- (ii) 4,8,12

- (iii) 8,16,24

- (iv) 5,13,21

- (i) Shift registers cannot be used to

- (i) convert serial data to parallel data

- (ii) transmit serial data

(iii) divide its content by 4

- (iv) convert data to its 2's complement.

- (j)The control signals that control the direction of data bus are

- (i) IO/M, RD

- (ii) ALE, WR

- (iii) RD, WR

- (iv) ALE, IO/M

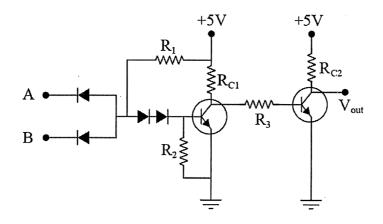

2. (a) Show that a particular digital logic gate is mimicked by the silicon diode and silicon transistor circuit given in the figure below.

- (b) A Boolean expression is given by  $F = A.\bar{B}.\bar{C}.\bar{D} + \bar{A}.B.\bar{C}.D + \bar{A}.\bar{B}.\bar{C}.D + \bar{A}.\bar{B}.\bar{C}.D + \bar{A}.\bar{B}.\bar{C}.D$  +  $\bar{A}.\bar{B}.\bar{C}.D$  +  $\bar{A}.\bar{B}.\bar{C}.D$  +  $\bar{A}.\bar{B}.\bar{C}.D$  +  $\bar{A}.\bar{B}.\bar{C}.D$  Find minimal expression of F in SOP and implement it using NAND logic.

- 3. (a) Define and write down the truth table of an octal to binary encoder. Obtain the logics expression of its output in terms of inputs and draw the logic circuit of it.

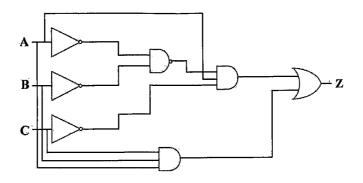

- (b) Obtain the simplified Boolean logic expression for output (Z) of the logic circuit shown in the figure below and implement the same circuit by using minimum number of logic gates.

- 4. Derive the characteristic equations of the J-K latch. Convert an S-R latch into a J-K latch. Given that the characteristic equations of S-R latch are  $Q_{n+1} = S + \overline{R}$ .  $Q_n$  and  $\overline{Q_{n+1}} = R + \overline{S} \overline{Q_n}$  4+4

- 5. Explain with a circuit diagram the operation of a 4-bit synchronous counter. Discuss its main difference and advantage over ripple counter.

4+4

- 6. What are the sizes and direction of address bus and data bus of 8085 microprocessor? How address bus and data bus of 8085 microprocessor are demultiplexed? Explain with a timing diagram of opcode fetch.

2+3+3