## B. E.T.C.E. 4<sup>th</sup> year 2<sup>nd</sup> Sem EXAM (old) -2017

(4th year 2nd Sem)

## **ELECTRONIC DESIGN AUTOMATION -- Elective -II**

Time: Three Hours Full Marks: 100

## Answer any five questions.

1.

- a. What is delta delay in VHDL? How Transport and inertial delays are described? 4+6= 10

- b. Write a program of serial adder using structural model. Design the memory by using flip flop.

2.

- a. What is test bench? Write test bench program to verify AND gate . 2+10=12

- b. Write a program of n input OR gate?

3.

- a. Design a 8:1 MUX using suitable MUX tree. Write the code using structural model. Use

process for input sensitivity list

- b. What is the difference between signal and variable? Describe it with an example. 6

- c. Write a program of Single bit magnitude comparator by using NAND gate 6

4.

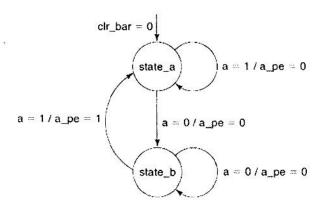

a. Write the VHDL code of Mealy FSM state diagram for a positive edge detector.

b. What is resolution function and explain it's operation by an example. What is the calling function type associated with resolution function in terms of VHDL code?

2+4+4=10

| 5. |    |                                                                                            |      |  |

|----|----|--------------------------------------------------------------------------------------------|------|--|

|    | a. | Explain the MOS small signal model and describe each terms.                                | 10   |  |

|    | b. | What is SPICE Level -1 what are the primary net-list parameters?                           | 5    |  |

|    | c. | scribe the operation of MOS capacitor and their behavior in different operational zone     |      |  |

|    |    |                                                                                            | 5    |  |

| 6. |    |                                                                                            |      |  |

|    | a. | What is the requirement of scaling? What is constant field scaling and constant voltage    |      |  |

|    |    | scaling?                                                                                   | +4=7 |  |

|    | b. | Describe the condition of Cox, Id(linear), Id(Sat), power dissipation, power density, gate |      |  |

|    |    | delay for both constant field and constant voltage scaling                                 | 8    |  |

|    | c. | Find the drain current and transconductance for an NMOS transistor operating               | 5    |  |

|    |    | with $V_{GS} = 2.5 \text{ V}$ , $V_T = 1 \text{ V}$ , and $K' = 1 \text{ mA/V}^2$ .        |      |  |

|    |    |                                                                                            |      |  |

| 7. |    |                                                                                            |      |  |

|    | a. | What is design for manufacturability? What is different process variation and how it       |      |  |

|    |    | changes the device, circuit and system?                                                    | 10   |  |

|    | b. | What are the designable and noise parameters and how the distribution function of noise    |      |  |

|    |    | behaves?                                                                                   | 6    |  |

|    | c. | What is parametric yield and variability?                                                  | 2    |  |

|    |    |                                                                                            |      |  |